# **Quad-Core Intel® Xeon® Processor** 5400 Series

**Thermal/Mechanical Design Guidelines**

November 2007

Reference Number: 318611 Revision: 001

IINFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Quad-Core Intel® Xeon® 5400 Series may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available upon request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling1-800-548-4725, or by visiting Intel's website at http://www.intel.com.

Intel, Intel Inside, Xeon, Intel Core and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\* Other brands and names may be claimed as the property of others.

Copyright © 2007, Intel Corporation. All rights reserved.

# Contents

| 1 | Intro |                  | ۱<br>ve                                                                                 |    |

|---|-------|------------------|-----------------------------------------------------------------------------------------|----|

|   | 1.1   |                  | ve                                                                                      |    |

|   | 1.2   |                  | nces                                                                                    |    |

|   | 1.4   |                  | on of Terms                                                                             |    |

| 2 |       |                  | chanical Reference Design                                                               |    |

|   | 2.1   |                  | nical Requirements                                                                      |    |

|   |       | 2.1.1<br>2.1.2   | Processor Mechanical Parameters<br>Quad-Core Intel® Xeon® Processor 5400 Series Package |    |

|   |       | 2.1.2            | Quad-Core Intel® Xeon® Processor 5400 Series Package                                    |    |

|   | 2.2   |                  | sor Thermal Parameters and Features                                                     |    |

|   | 212   | 2.2.1            | Thermal Control Circuit and TDP                                                         |    |

|   |       | 2.2.2            | Digital Thermal Sensor                                                                  |    |

|   |       | 2.2.3            | Platform Environmental Control Interface (PECI)                                         |    |

|   |       | 2.2.4            | Multiple Core Special Considerations                                                    | 21 |

|   |       | 2.2.5            | Thermal Profile                                                                         |    |

|   |       | 2.2.6            | TCONTROL Definition                                                                     | 25 |

|   |       | 2.2.7            | Thermal Profile Concepts for the Quad-Core Intel® Xeon®                                 | 20 |

|   |       | 2 2 0            | Processor 5400 Series                                                                   |    |

|   | 2.3   | 2.2.8<br>Fan Fai | Performance Targets                                                                     |    |

|   | 2.3   |                  | terizing Cooling Solution Performance Requirements                                      |    |

|   | 2.7   | 2.4.1            | Fan Speed Control                                                                       |    |

|   |       | 2.4.2            | Processor Thermal Characterization Parameter Relationships                              |    |

|   |       | 2.4.3            | Chassis Thermal Design Considerations                                                   |    |

|   | 2.5   | Therma           | al/Mechanical Reference Design Considerations                                           |    |

|   |       | 2.5.1            | Heatsink Solutions                                                                      |    |

|   |       | 2.5.2            | Thermal Interface Material                                                              |    |

|   |       | 2.5.3            | Summary                                                                                 |    |

|   |       | 2.5.4            | Assembly Overview of the Intel Reference Thermal Mechanical Design                      |    |

|   |       | 2.5.5<br>2.5.6   | Thermal Solution Performance Characteristics                                            |    |

|   |       | 2.5.0            | Thermal Profile Adherence<br>Components Overview                                        |    |

|   |       | 2.5.8            | Boxed Active Thermal Solution for the Quad-Core Intel®                                  | 45 |

|   |       | 2.5.0            | Xeon® Processor 5400 Series Thermal Profile                                             | 49 |

| Α | 1U AI | ternativ         | ve Heatsink Thermal/Mechanical Design                                                   | 53 |

|   | A.1   | Compo            | nent Overview                                                                           | 53 |

|   | A.2   |                  | al Solution Performance Characterics                                                    |    |

|   | A.3   |                  | al Profile Adherence                                                                    |    |

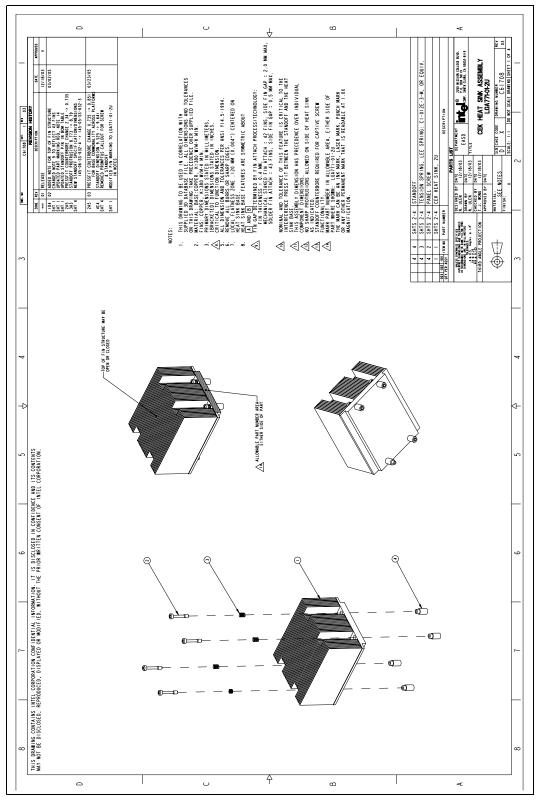

| В |       |                  | Drawings                                                                                |    |

| С | Heats | •                | p Load Methodology                                                                      |    |

|   | C.1   |                  | 2W                                                                                      |    |

|   | C.2   |                  | eparation                                                                               |    |

|   |       | C.2.1            | Heatsink Preparation                                                                    |    |

|   |       | C.2.2<br>C.2.3   | Typical Test Equipment<br>Test Procedure Examples                                       |    |

|   |       | C.2.3<br>C.2.4   | Time-Zero, Room Temperature Preload Measurement                                         |    |

|   |       | C.2.4<br>C.2.5   | Preload Degradation under Bake Conditions                                               |    |

|   |       | 5                |                                                                                         |    |

| Safet | ty Requ              | Jirements                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|----------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Quali | ity and              | Reliability Requirements                                                                    | 91                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |                      |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | E.1.1                | Reference Heatsink Thermal Verification                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | E.1.2                | Environmental Reliability Testing                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |                      |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Enab  | led Sup              | ppliers Information                                                                         | 95                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| F.1   | Supplie              | er Information                                                                              | 95                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | F.1.1                | Intel Enabled Suppliers                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | F.1.2                | Additional Suppliers                                                                        | 96                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | Quali<br>E.1<br>Enab | Quality and<br>E.1 Intel V<br>E.1.1<br>E.1.2<br>E.1.3<br>Enabled Sup<br>F.1 Suppli<br>F.1.1 | Safety Requirements         Quality and Reliability Requirements         E.1 Intel Verification Criteria for the Reference Designs         E.1.1 Reference Heatsink Thermal Verification         E.1.2 Environmental Reliability Testing         E.1.3 Material and Recycling Requirements         Enabled Suppliers Information         F.1 Supplier Information         F.1.1 Intel Enabled Suppliers         F.1.2 Additional Suppliers |

## **Figures**

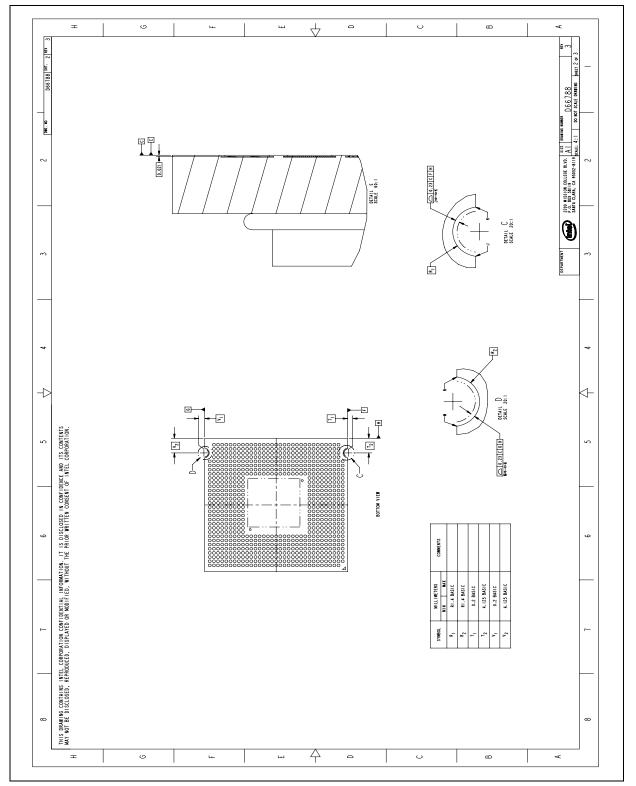

| 2-1        | Quad-Core Intel® Xeon® Processor 5400 Series Mechanical Drawing (1 of 3)                                      | .15 |

|------------|---------------------------------------------------------------------------------------------------------------|-----|

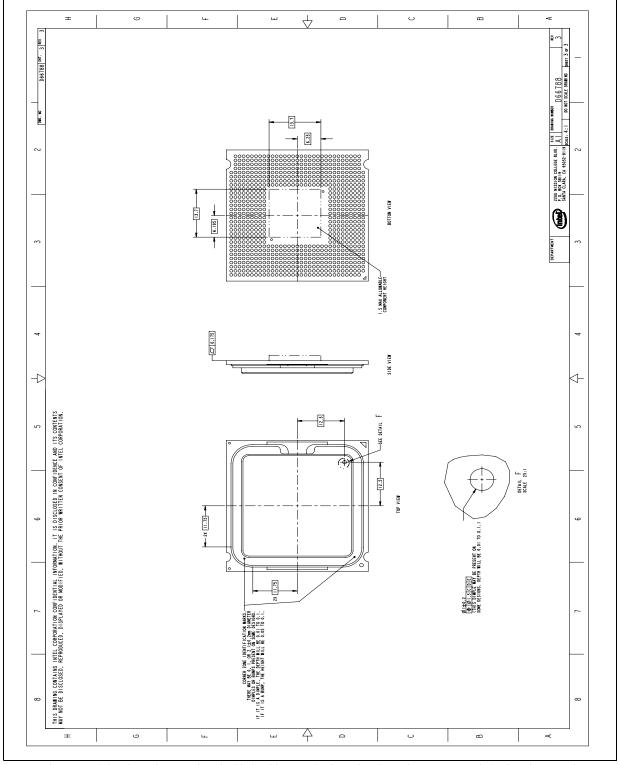

| 2-2        | Quad-Core Intel® Xeon® Processor 5400 Series Mechanical Drawing (2 of 3)                                      | .16 |

| 2-3        | Quad-Core Intel® Xeon® Processor 5400 Series Mechanical Drawing (3 of 3)                                      | .17 |

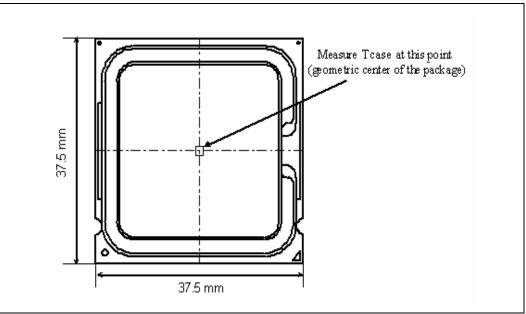

| 2-4        | Processor Case Temperature Measurement Location                                                               | .19 |

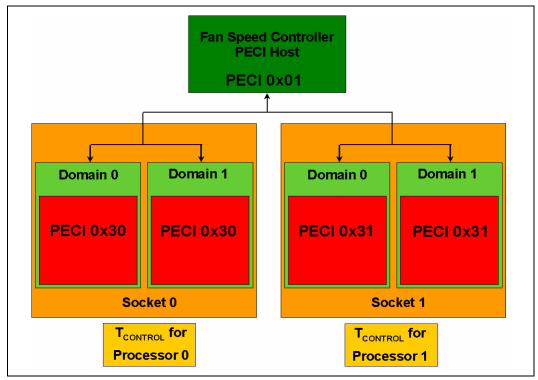

| 2-5        | DTS Domain for Quad-Core Intel® Xeon® Processor 5400 Series                                                   | .21 |

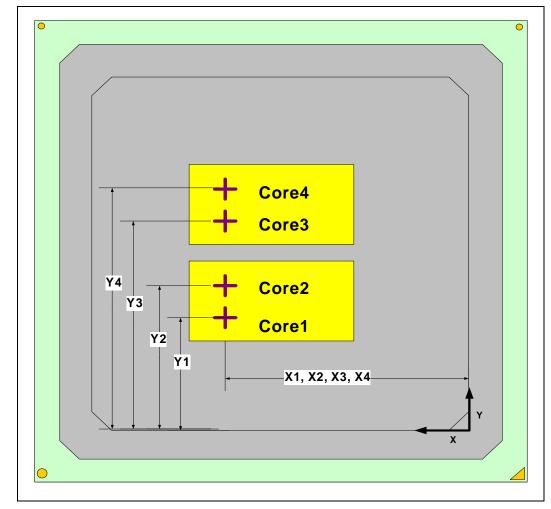

| 2-6        | Processor Core Geometric Center Locations                                                                     | .23 |

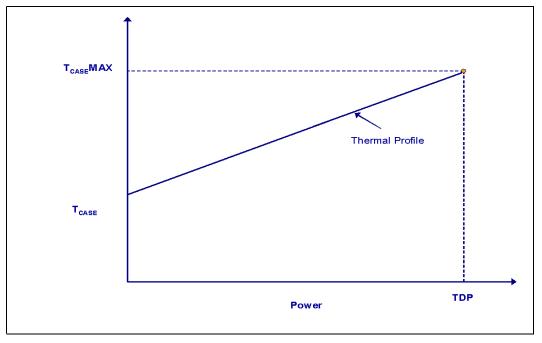

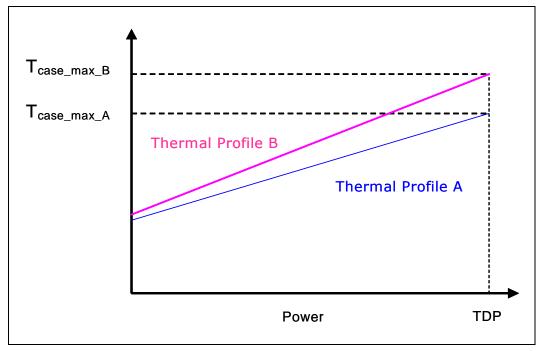

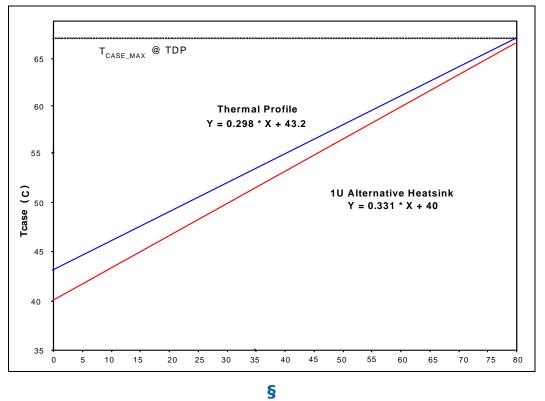

| 2-7        | Thermal Profile Diagram                                                                                       | .24 |

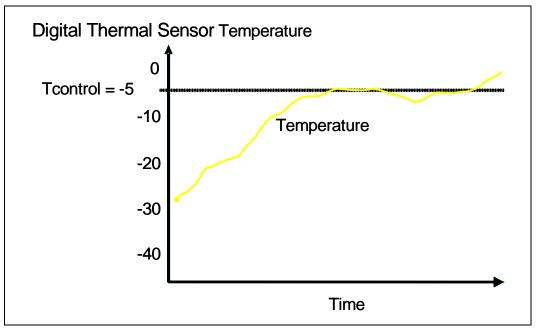

| 2-8        | TCONTROL Value and Digital Thermal Sensor Value Interaction                                                   | .25 |

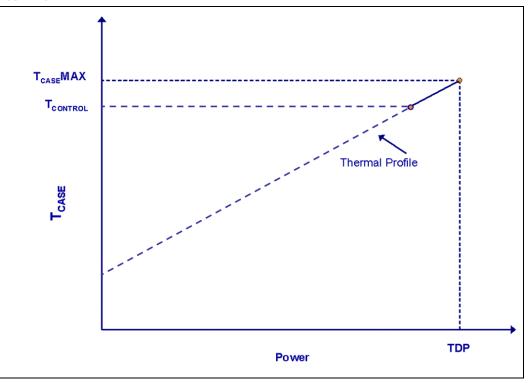

| 2-9        | TCONTROL and Thermal Profile Interaction                                                                      | .26 |

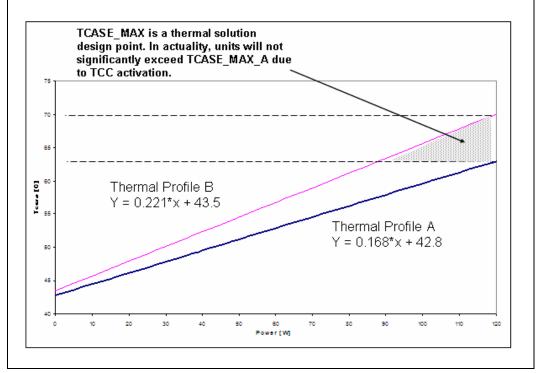

| 2-10       | Dual Thermal Profile Diagram                                                                                  | .27 |

| 2-11       | Thermal Profile for the Quad-Core Intel® Xeon® Processor X5400 Series                                         | .29 |

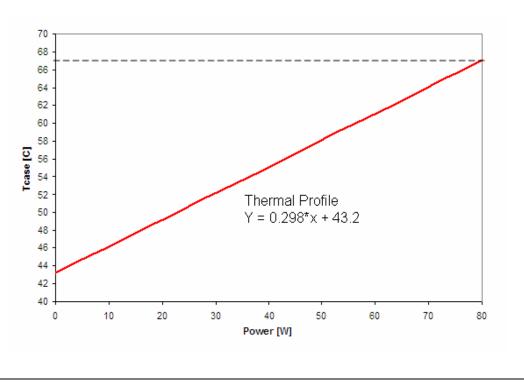

| 2-12       | Thermal Profile for Quad-Core Intel® Xeon® Processor E5400 Series                                             | .30 |

| 2-13       | Thermal Profile for Quad-Core Intel® Xeon® Processor X5482 Series                                             |     |

| 2-14       | TCONTROL and Fan Speed Control                                                                                | .33 |

| 2-15       | Processor Thermal Characterization Parameter Relationships                                                    | .35 |

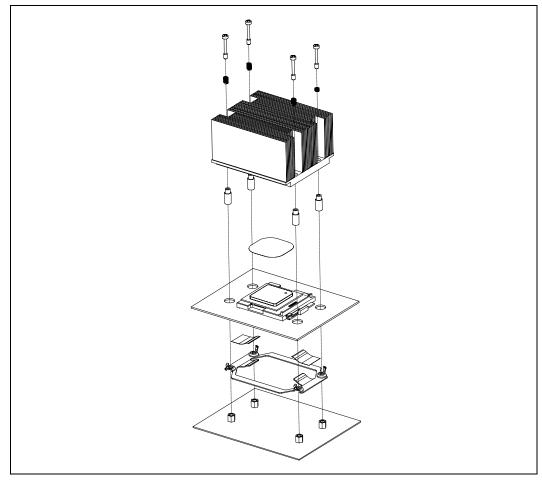

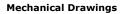

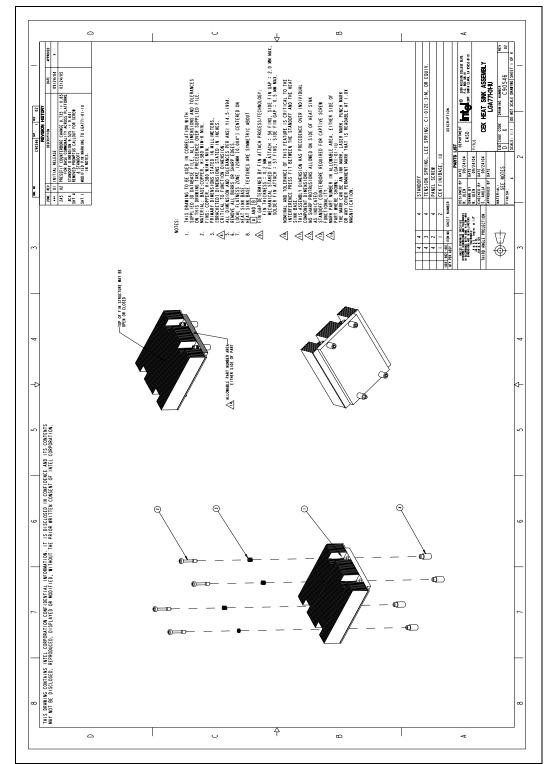

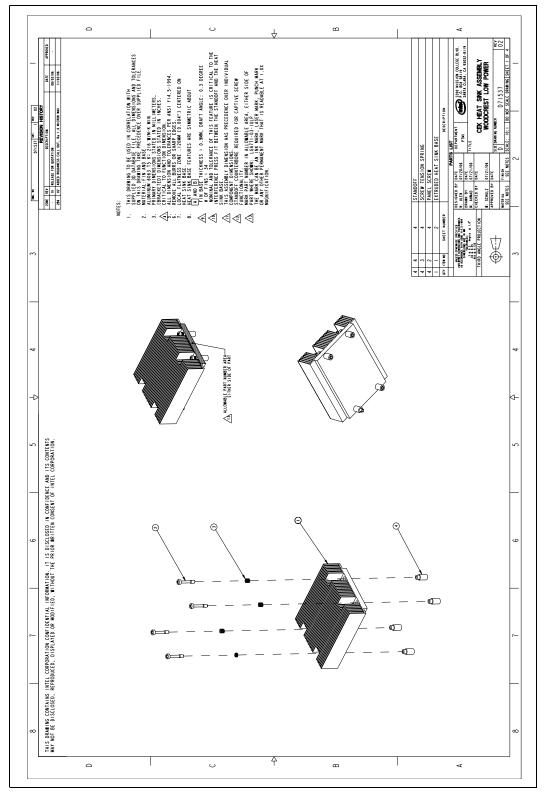

| 2-16       | Exploded View of CEK Thermal Solution Components                                                              | .39 |

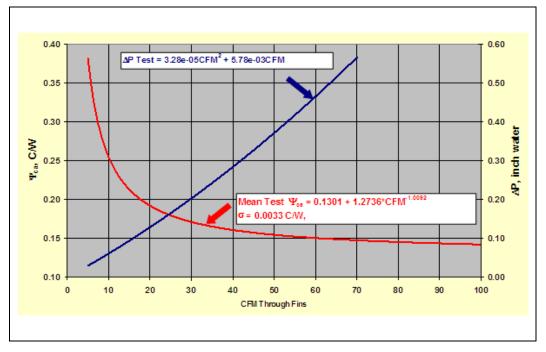

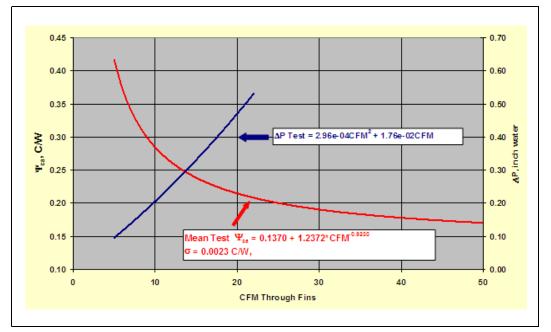

| 2-17       | 2U+ CEK Heatsink Thermal Performance                                                                          | .41 |

| 2-18       | 1U CEK Heatsink Thermal Performance                                                                           | .42 |

| 2-19       | 2U+CEK Thermal Adherence to Quad-Core Intel® Xeon® Processor X5400                                            |     |

|            | Series Thermal Profile A                                                                                      | .43 |

| 2-20       | 1U CEK Thermal Adherence to Quad-Core Intel® Xeon® Processor X5400                                            |     |

|            | Series Thermal Profile B                                                                                      | .44 |

| 2-21       | 1U CEK Thermal Adherence to Quad-Core Intel® Xeon® Processor E5400                                            |     |

|            | Series Thermal Profile                                                                                        |     |

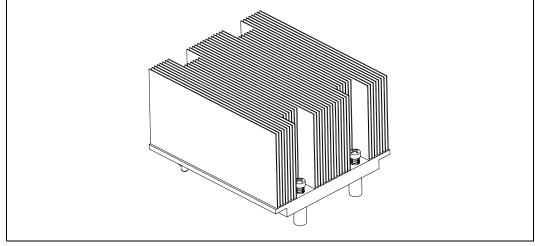

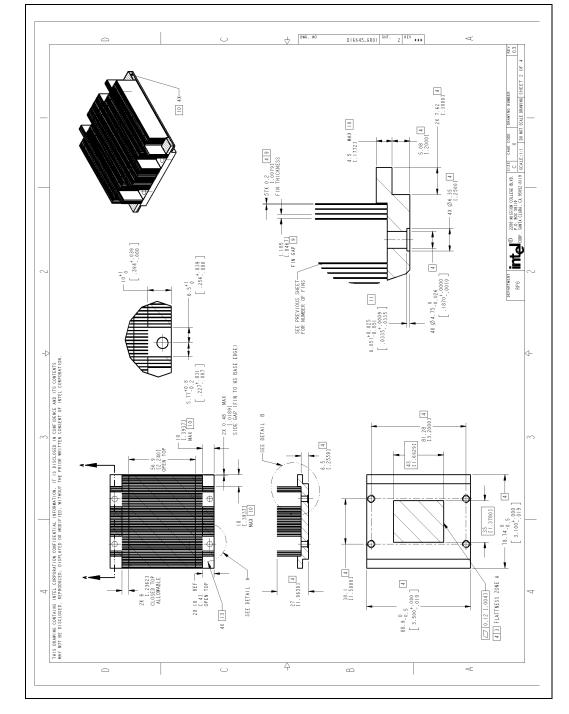

| 2-22       | Isometric View of the 2U+ CEK Heatsink                                                                        |     |

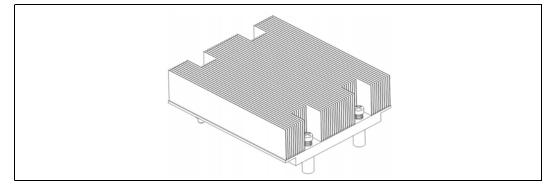

| 2-23       | Isometric View of the 1U CEK Heatsink                                                                         |     |

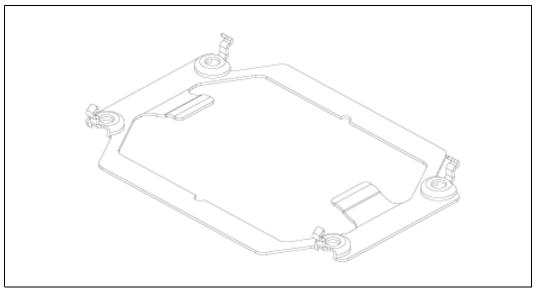

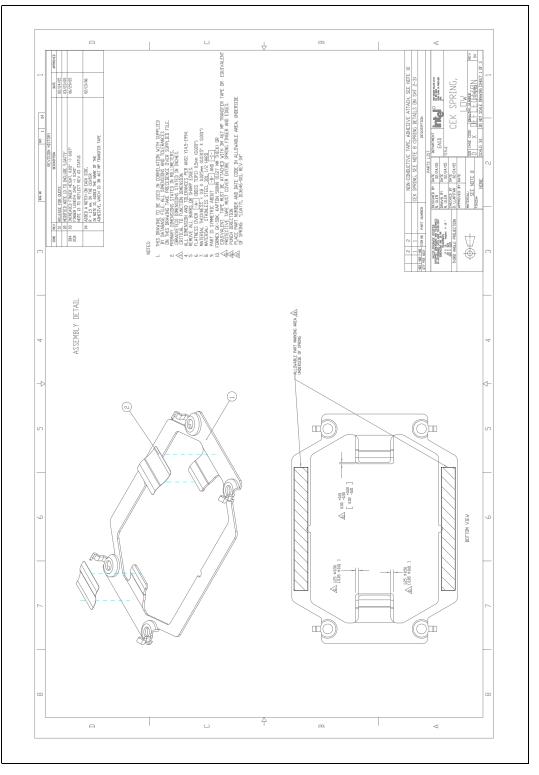

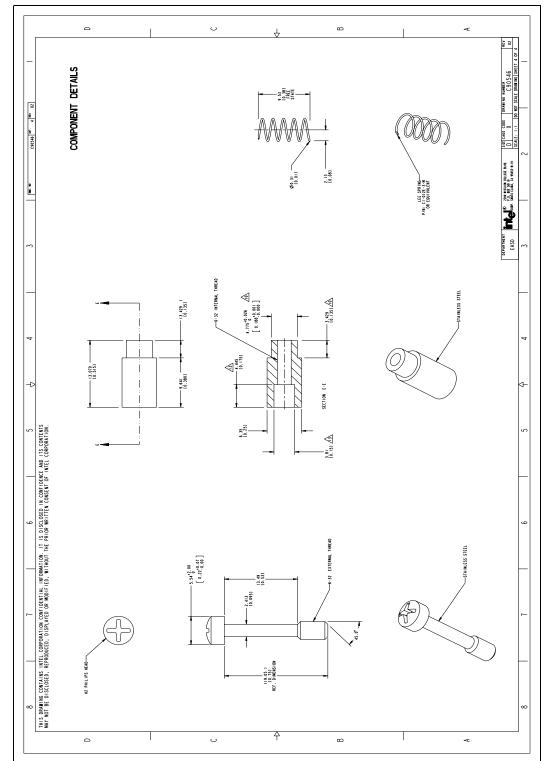

| 2-24       | CEK Spring Isometric View                                                                                     |     |

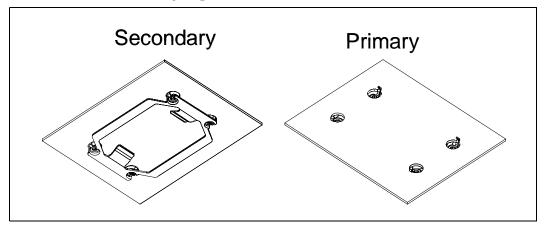

| 2-25       | Isometric View of CEK Spring Attachment to the Base Board                                                     | .48 |

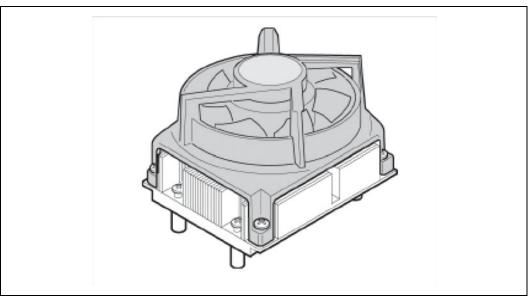

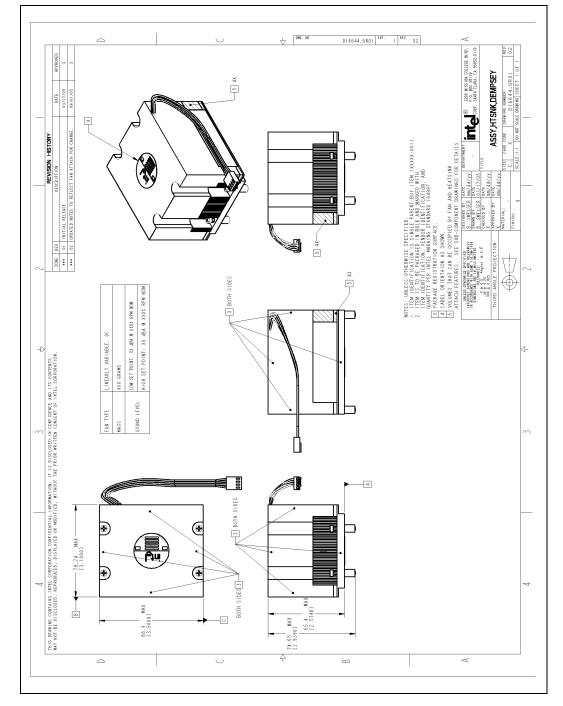

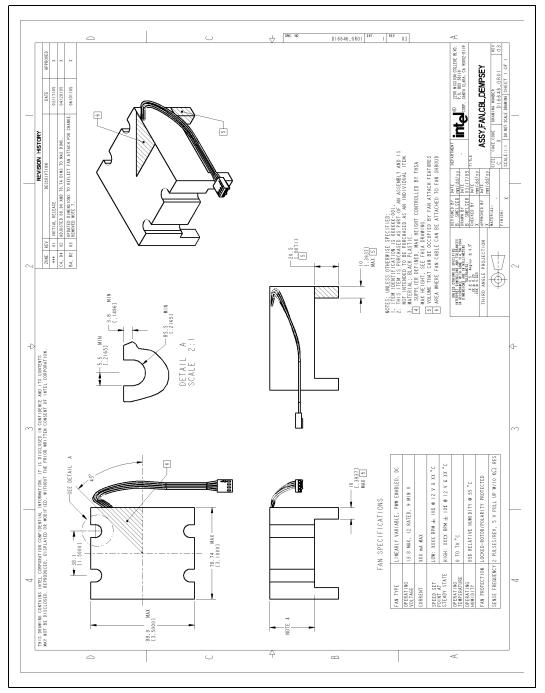

| 2-26       | Boxed Active CEK Heatsink Solutions with PWM/DTS Control                                                      | 40  |

| 2 27       | (Representation Only)                                                                                         |     |

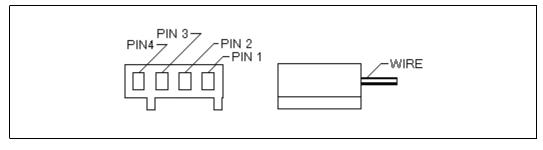

| 2-27       | Fan Cable Connection (Active CEK)                                                                             |     |

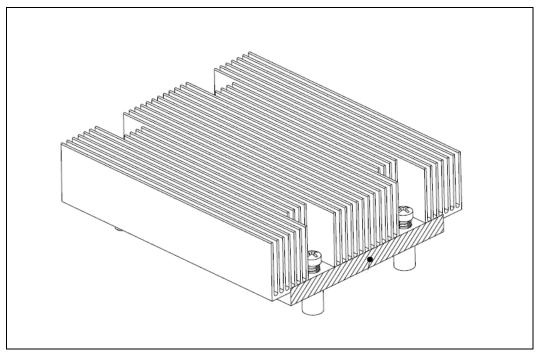

| A-1        | Isometric View of the 1U Alternative Heatsink                                                                 |     |

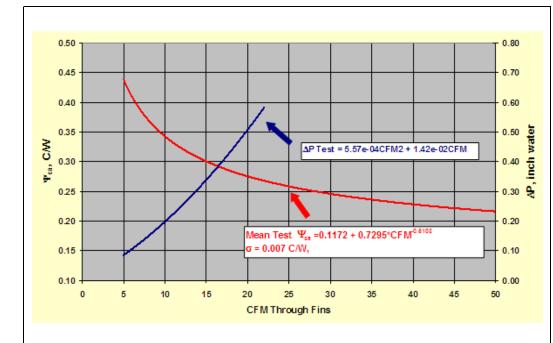

| A-2        | 1U Alternative Heatsink Thermal Performance                                                                   | .54 |

| A-3        | 1U Alternative Heatsink Thermal Adherence to Quad-Core Intel® Xeon®<br>Processor L5400 Series Thermal Profile | FF  |

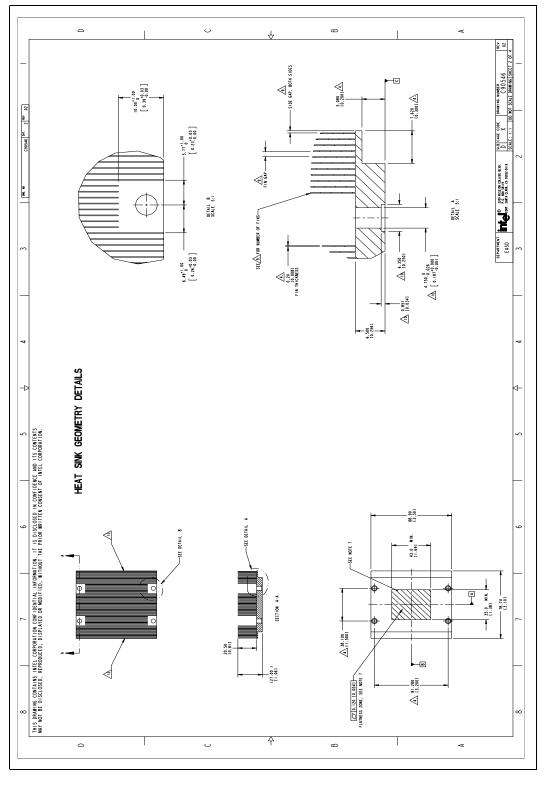

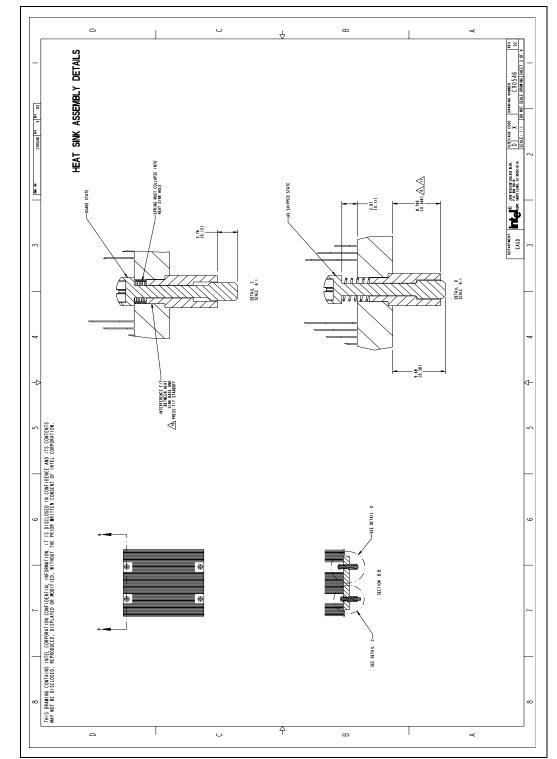

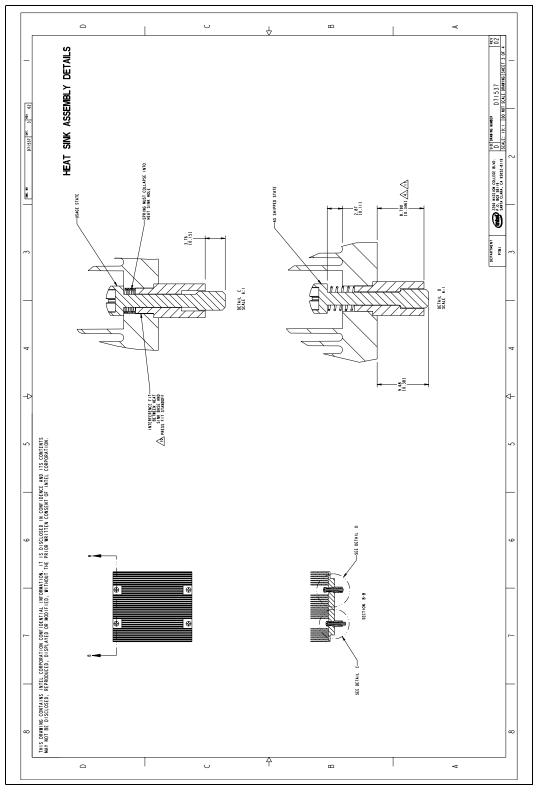

| B-1        |                                                                                                               |     |

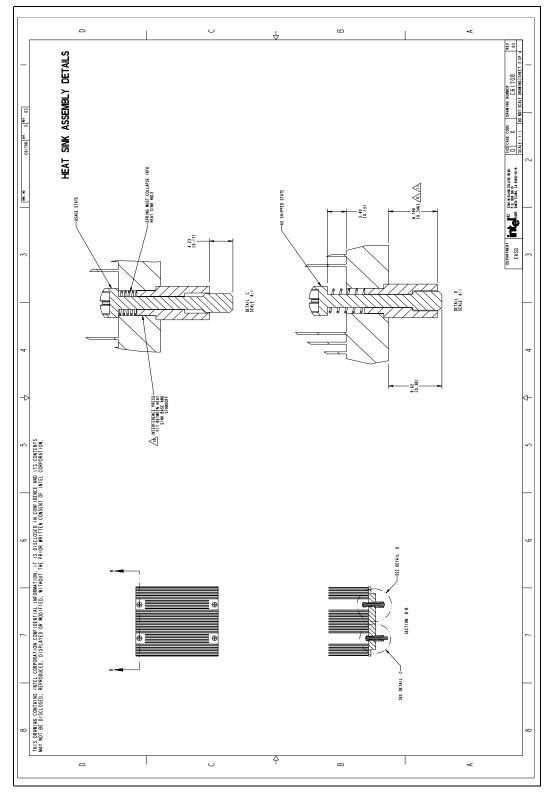

| в-1<br>В-2 | 2U CEK Heatsink (Sheet 1 of 4)<br>2U CEK Heatsink (Sheet 2 of 4)                                              |     |

| в-2<br>В-3 |                                                                                                               |     |

|            | 2U CEK Heatsink (Sheet 3 of 4)                                                                                |     |

| B-4        | 2U CEK Heatsink (Sheet 4 of 4)                                                                                | .01 |

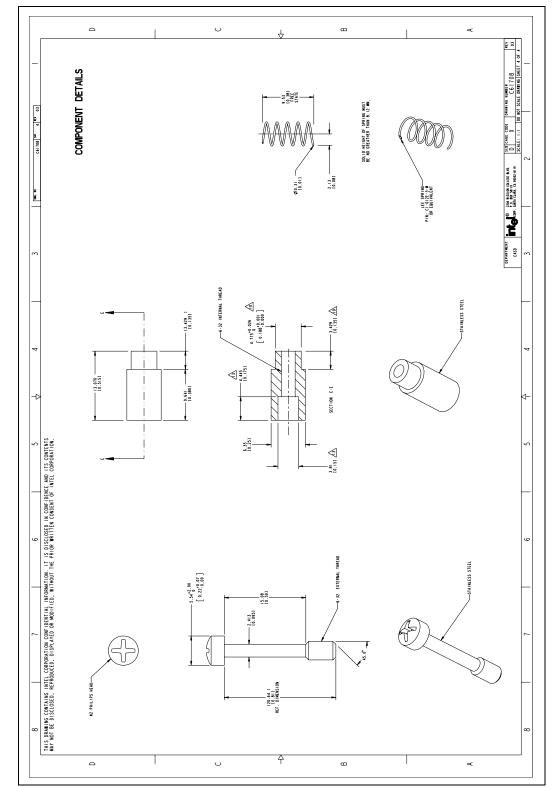

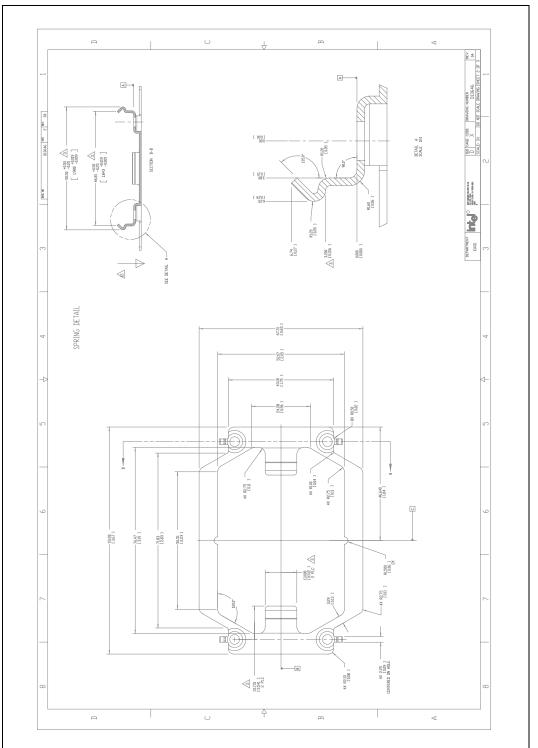

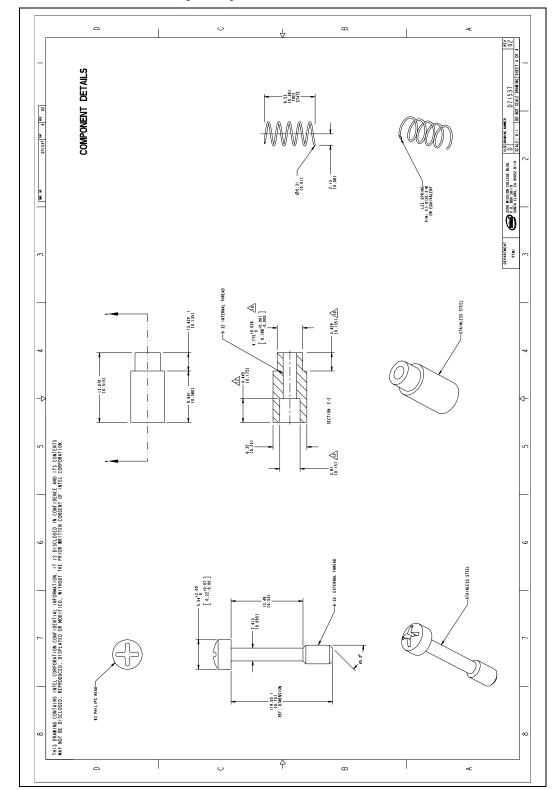

| B-5          | CEK Spring (Sheet 1 of 3)                                             | 62 |

|--------------|-----------------------------------------------------------------------|----|

| B-6          | CEK Spring (Sheet 2 of 3)                                             | 63 |

| B-7          | CEK Spring (Sheet 3 of 3)                                             | 64 |

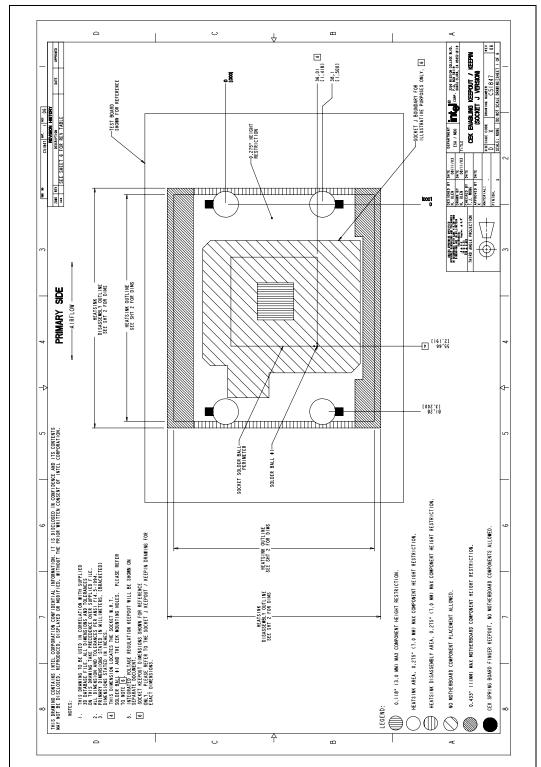

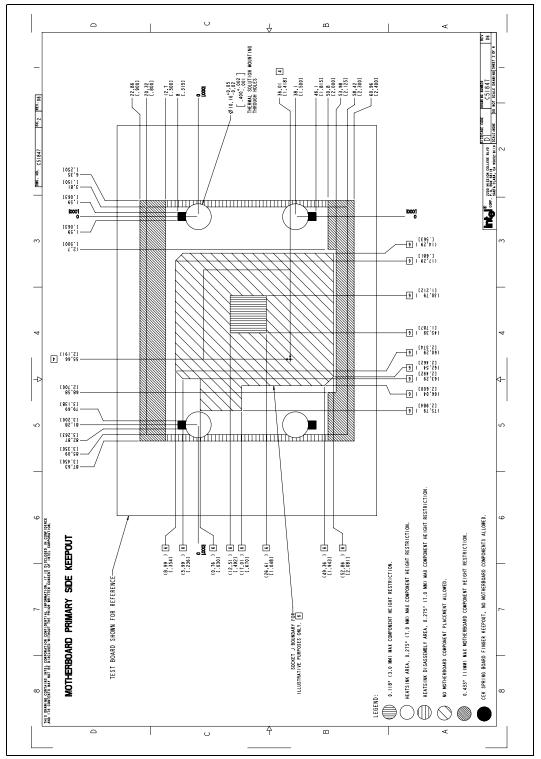

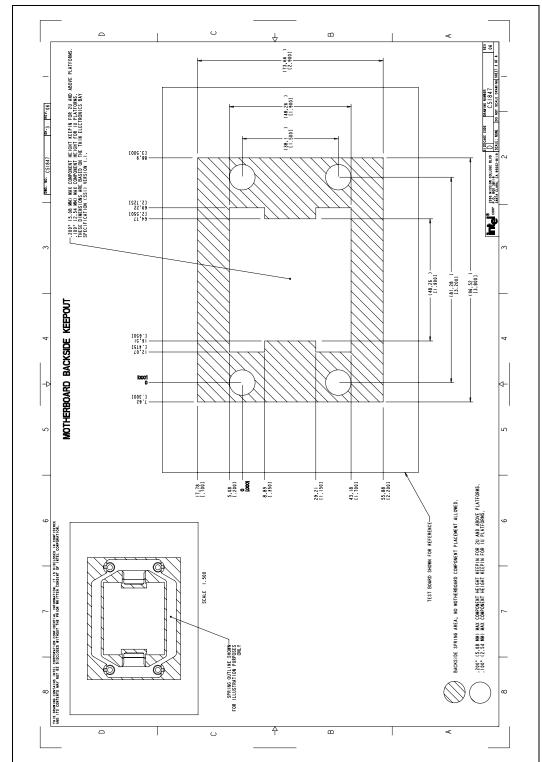

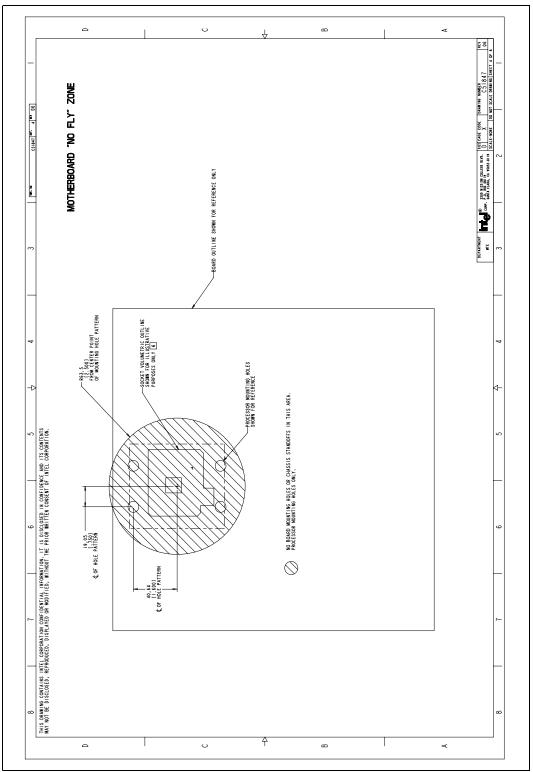

| B-8          | Baseboard Keepout Footprint Definition and Height Restrictions for    |    |

|              | Enabling Components (Sheet 1 of 6)                                    | 65 |

| B-9          | Baseboard Keepout Footprint Definition and Height Restrictions for    |    |

|              | Enabling Components (Sheet 2 of 6)                                    | 66 |

| B-10         | Baseboard Keepout Footprint Definition and Height Restrictions for    |    |

|              | Enabling Components (Sheet 3 of 6)                                    | 67 |

| B-11         | Baseboard Keepout Footprint Definition and Height Restrictions for    |    |

|              | Enabling Components (Sheet 4 of 6)                                    | 68 |

| B-12         | Baseboard Keepout Footprint Definition and Height Restrictions for    | ~~ |

| D 10         | Enabling Components (Sheet 5 of 6)                                    | 69 |

| B-13         | Baseboard Keepout Footprint Definition and Height Restrictions for    | 70 |

| B-14         | Enabling Components (Sheet 6 of 6)                                    |    |

| в-14<br>В-15 | 1U CEK Heatsink (Sheet 1 of 4)                                        |    |

|              | 1U CEK Heatsink (Sheet 2 of 4)                                        |    |

| B-16         | 1U CEK Heatsink (Sheet 3 of 4)                                        |    |

| B-17         | 1U CEK Heatsink (Sheet 4 of 4)                                        |    |

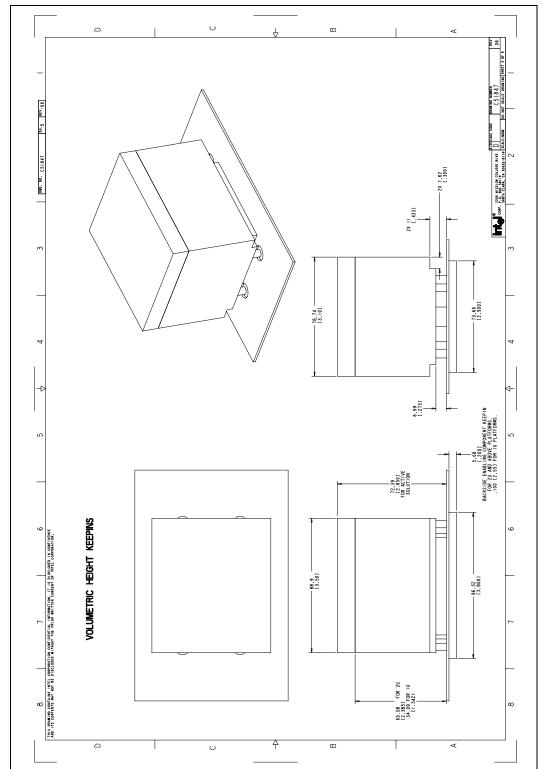

| B-18         | Active CEK Thermal Solution Volumetric (Sheet 1 of 3)                 |    |

| B-19         | Active CEK Thermal Solution Volumetric (Sheet 2 of 3)                 |    |

| B-20         | Active CEK Thermal Solution Volumetric (Sheet 3 of 3)                 |    |

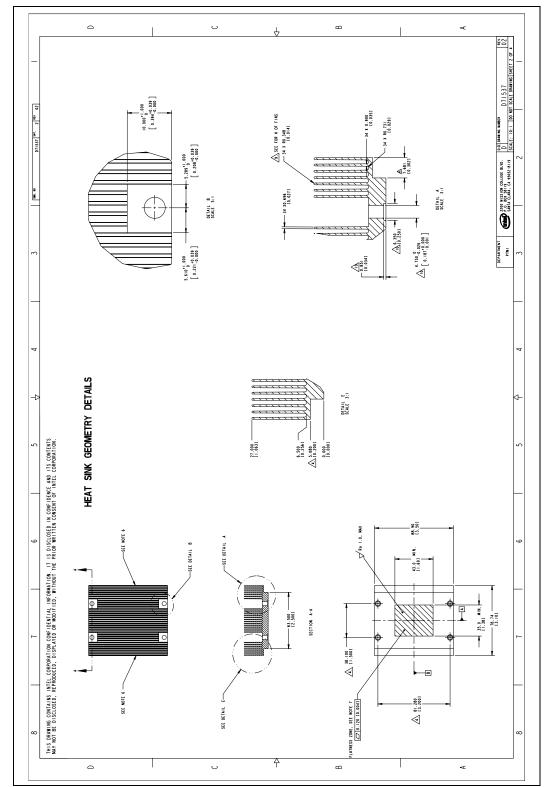

| B-21         | 1U Alternative Heatsink (1 of 4)                                      |    |

| B-22         | 1U Alternative Heatsink (2 of 4)                                      |    |

| B-23         | 1U Alternative Heatsink (3 of 4)                                      |    |

| B-24         | 1U Alternative Heatsink (4 of 4)                                      |    |

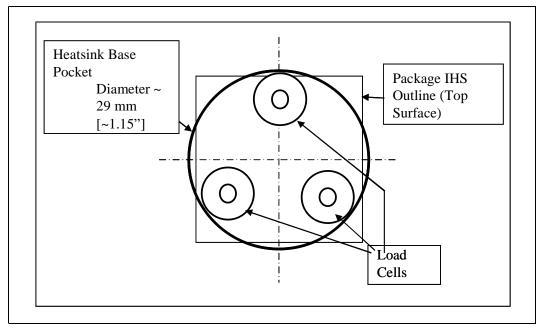

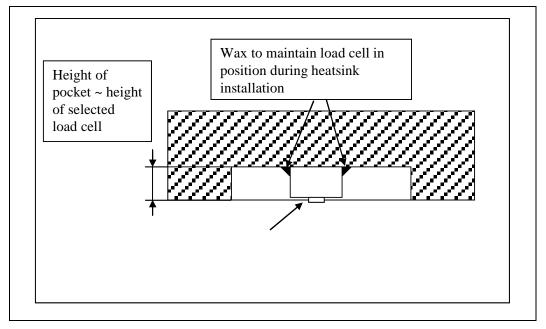

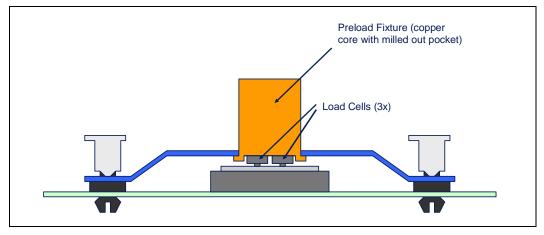

| C-1          | Load Cell Installation in Machined Heatsink Base Pocket - Bottom View |    |

| C-2          | Load Cell Installation in Machined Heatsink Base Pocket - Side View   |    |

| C-3          | Preload Test Configuration                                            | 85 |

## **Tables**

| 1-1  | Reference Documents                                                                                             | 9  |

|------|-----------------------------------------------------------------------------------------------------------------|----|

| 1-2  | Terms and Descriptions                                                                                          | 10 |

| 2-1  | Processor Mechanical Parameters Table                                                                           | 13 |

| 2-2  | Input and Output Conditions for the Quad-Core Intel® Xeon® Processor 5400<br>Series Thermal Management Features | 22 |

| 2-3  | Processor Core Geometric Center Dimensions                                                                      | 23 |

| 2-4  | Intel Reference Heatsink Performance Targets for the Quad-Core Intel ${ m I}$                                   |    |

|      | Xeon® Processor X5400 Series                                                                                    | 31 |

| 2-5  | Intel Reference Heatsink Performance Targets for the Quad-Core Intel ${ m I}$                                   |    |

|      | Xeon® Processor E5400 Series                                                                                    | 32 |

| 2-6  | Fan Speed Control, TCONTROL and DTS Relationship                                                                | 34 |

| 2-7  | CEK Heatsink Thermal Mechanical Characteristics                                                                 | 47 |

| 2-8  | Recommended Thermal Grease Dispense Weight                                                                      | 47 |

| 2-9  | Fan Specifications (Boxed 4-wire PWM/DTS Heatsink Solution)                                                     | 50 |

| 2-10 | Fan Cable Connector Pin Out (Active CEK)                                                                        | 51 |

| A-1  | 1U Alternative Heatsink Thermal Mechanical Characteristics                                                      | 54 |

| B-1  | Mechanical Drawing List                                                                                         | 57 |

| C-1  | Typical Test Equipment                                                                                          | 86 |

| E-1  | Use Conditions Environment                                                                                      | 92 |

| F-1  | Suppliers for the Quad-Core Intel® Xeon® Processor 5400 Series Intel<br>Reference Solution                      | 95 |

| F-2  | Additional Suppliers for the Quad-Core Intel® Xeon® Processor 5400 Series<br>Intel Reference Solution           | 97 |

|      |                                                                                                                 |    |

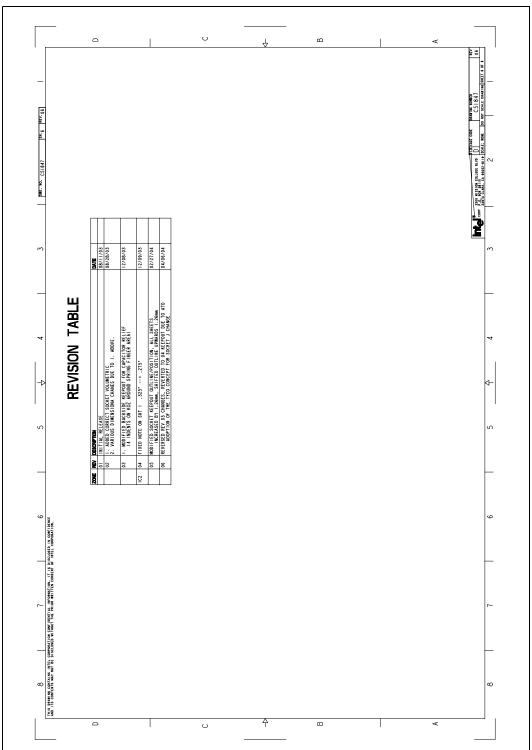

# **Revision History**

| Reference<br>Number | Revision<br>Number | Description                      | Date          |

|---------------------|--------------------|----------------------------------|---------------|

| 318611              | 001                | Initial release of the document. | November 2007 |

## §

# **1** Introduction

## 1.1 Objective

The purpose of this guide is to describe the reference thermal solution and design parameters required for the Quad-Core Intel® Xeon® Processor 5400 Series.

It is also the intent of this document to comprehend and demonstrate the processor cooling solution features and requirements. Furthermore, this document provides an understanding of the processor thermal characteristics, and discusses guidelines for meeting the thermal requirements imposed over the entire life of the processor. The thermal/mechanical solutions described in this document are intended to aid component and system designers in the development and evaluation of processor compatible thermal/mechanical solutions.

## 1.2 Scope

The thermal/mechanical solutions described in this document pertain to a solution(s) intended for use with the Quad-Core Intel® Xeon® Processor 5400 Series in 1U, 2U, 2U+ and workstation form factors systems. This document contains the mechanical and thermal requirements of the processor cooling solution. In case of conflict, the data in the *Quad-Core Intel*® *Xeon*® *Processor 5400 Series Datasheet* supersedes any data in this document. Additional information is provided as a reference in the appendices.

## **1.3 References**

Material and concepts available in the following documents may be beneficial when reading this document.

### Table 1-1. Reference Documents (Sheet 1 of 2)

| Document                                                                                                                       | Comment                    |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| European Blue Angel Recycling Standards                                                                                        | http://www.blauer-engel.de |

| Intel^ $^{(\!8\!)}$ Xeon $^{(\!8\!)}$ Dual- and Multi- Processor Family Thermal Test Vehicle User's Guide                      | See Note at bottom table.  |

| LGA771 Socket Mechanical Design Guide                                                                                          | See Note following table.  |

| LGA771 SMT Socket Design Guidelines                                                                                            | See Note following table.  |

| LGA771 Daisy Chain Test Vehicle User Guide                                                                                     | See Note following table.  |

| Stoakley Platform Design Guide (PDG)                                                                                           | See Note following table.  |

| Dual-Core Intel <sup>®</sup> Xeon <sup>®</sup> Processor-Based Servers Platform Design<br>Guide (PDG)                          | See Note following table.  |

| $\textit{Dual-Core Intel}^{\texttt{R}}$ Xeon $^{\texttt{R}}$ Processor-Based Workstation Platform Design Guide (PDG)           | See Note following table.  |

| Clovertown, Harpertown & Wolfdale-DP Processors Compatibility Design<br>Guide for Bensley, Bensley-VS, and Glidewell Platforms | See Note following table.  |

| PECI Feature Set Overview                                                                                                      | See Note following table   |

| Platform Environment Control Interface(PECI) Specification                                                                     | See Note following table   |

| Quad-Core Intel® Xeon® Processor 5400 Series Datasheet                                                                         | See Note following table.  |

| Clovertown_Harpertown_Wolfdale-DP Processor Enabled CEK and Package Mechanical Models (in IGES and ProE* format)               | Available electronically   |

Quad-Core Intel® Xeon® Processor 5400 Series TMDG

### Table 1-1. Reference Documents (Sheet 2 of 2)

| Document                                                                                                             | Comment                   |

|----------------------------------------------------------------------------------------------------------------------|---------------------------|

| Clovertown_Harpertown_Wolfdale-DP Processor Enabled Components<br>CEK Thermal Models (in Flotherm* and Icepak*)      | Available electronically  |

| Clovertown_Harpertown_Wolfdale-DP Processor Package Thermal<br>Models (in Flotherm and Icepak)                       | Available electronically  |

| RS - Wolfdale Processor Family BIOS Writers Guide (BWG)                                                              | See Note following table. |

| Thin Electronics Bay Specification (A Server System Infrastructure (SSI)<br>Specification for Rack Optimized Servers | www.ssiforum.com          |

Note: Contact your Intel field sales representative for the latest revision and order number of this document.

## **1.4 Definition of Terms**

### Table 1-2. Terms and Descriptions (Sheet 1 of 2)

| Term                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                   |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bypass                                                                                                                                                                                      | Bypass is the area between a passive heatsink and any object that can act to form a duct. For this example, it can be expressed as a dimension away from the outside dimension of the fins to the nearest surface.                                                                                                                            |  |

| DTS                                                                                                                                                                                         | Digital Thermal Sensor replaces the Tdiode in previous products and uses the same sensor as the PROCHOT# sensor to indicate the on-die temperature. The temperature value represents the number of degrees below the TCC activation temperature.                                                                                              |  |

| MSR                                                                                                                                                                                         | The processor provides a variety of model specific registers that are used to control and report on processor performance. Virtually all MSRs handle system related functions and are not accessible to an application program.                                                                                                               |  |

| FMB                                                                                                                                                                                         | Flexible Motherboard Guideline: an estimate of the maximum value of a processor specification over certain time periods. System designers should meet the FMB values to ensure their systems are compatible with future processor releases.                                                                                                   |  |

| FSC                                                                                                                                                                                         | Fan Speed Control                                                                                                                                                                                                                                                                                                                             |  |

| IHS                                                                                                                                                                                         | Integrated Heat Spreader: a component of the processor package used to enhance the thermal performance of the package. Component thermal solutions interface with the processor at the IHS surface.                                                                                                                                           |  |

| LGA771 Socket                                                                                                                                                                               | The Quad-Core Intel® Xeon® Processor 5400 Series interfaces to the baseboard through this surface mount, 771 Land socket. See the <i>LGA771 Socket Mechanical Design Guide</i> for details regarding this socket.                                                                                                                             |  |

| P <sub>MAX</sub>                                                                                                                                                                            | The maximum power dissipated by a semiconductor component.                                                                                                                                                                                                                                                                                    |  |

| PECI                                                                                                                                                                                        | A proprietary one-wire bus interface that provides a communication channel between<br>Intel processor and chipset components to external thermal monitoring devices, for u<br>in fan speed control. PECI communicates readings from the processors Digital Therm<br>Sensor. PECI replaces the thermal diode available in previous processors. |  |

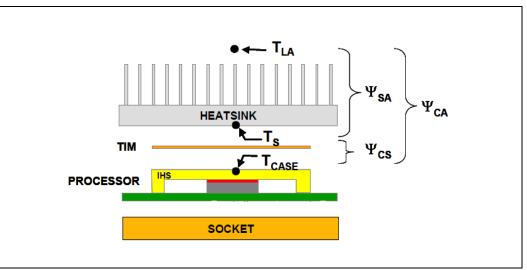

| $\Psi_{CA}$                                                                                                                                                                                 | Case-to-ambient thermal characterization parameter (psi). A measure of thermal solution performance using total package power. Defined as ( $T_{CASE} - T_{LA}$ ) / Total Package Power. Heat source should always be specified for $\Psi$ measurements.                                                                                      |  |

| $\Psi_{CS}$                                                                                                                                                                                 | Case-to-sink thermal characterization parameter. A measure of thermal interface material performance using total package power. Defined as ( $T_{CASE} - T_S$ ) / Total Package Power.                                                                                                                                                        |  |

| $\Psi_{SA}$ Sink-to-ambient thermal characterization parameter. A measure of heatsink performance using total package power. Defined as (T <sub>S</sub> – T <sub>LA</sub> ) / Total Package |                                                                                                                                                                                                                                                                                                                                               |  |

| T <sub>CASE</sub>                                                                                                                                                                           | The case temperature of the processor, measured at the geometric center of the topside of the IHS.                                                                                                                                                                                                                                            |  |

| T <sub>CASE_MAX</sub>                                                                                                                                                                       | The maximum case temperature as specified in a component specification.                                                                                                                                                                                                                                                                       |  |

| TCC                                                                                                                                                                                         | Thermal Control Circuit: Thermal monitor uses the TCC to reduce the die temperature by using clock modulation and/or operating frequency and input voltage adjustment when the die temperature is very near its operating limits.                                                                                                             |  |

## Table 1-2. Terms and Descriptions (Sheet 2 of 2)

| T <sub>CONTROL</sub> | A processor unique value for use in fan speed control mechanisms. $T_{CONTROL}$ is a temperature specification based on a temperature reading from the processor's Digital Thermal Sensor. $T_{CONTROL}$ can be described as a trigger point for fan speed control implementation. $T_{CONTROL} = -T_{OFFSET}$ .            |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>OFFSET</sub>  | An offset value from the TCC activation temperature value programmed into each processor during manufacturing and can be obtained by reading the IA_32_TEMPERATURE_TARGET MSR. This is a static and a unique value. Refer to the <i>RS</i> - <i>Wolfdale Processor Family BIOS Writers Guide (BWG)</i> for further details. |

| TDP                  | Thermal Design Power: Thermal solution should be designed to dissipate this target power level. TDP is not the maximum power that the processor can dissipate.                                                                                                                                                              |

| Thermal Monitor      | A feature on the processor that can keep the processor's die temperature within factory specifications under normal operating conditions.                                                                                                                                                                                   |

| Thermal Profile      | Line that defines case temperature specification of a processor at a given power level.                                                                                                                                                                                                                                     |

| TIM                  | Thermal Interface Material: The thermally conductive compound between the heatsink<br>and the processor case. This material fills the air gaps and voids, and enhances the<br>transfer of the heat from the processor case to the heatsink.                                                                                 |

| T <sub>LA</sub>      | The measured ambient temperature locally surrounding the processor. The ambient temperature should be measured just upstream of a passive heatsink or at the fan inlet for an active heatsink.                                                                                                                              |

| T <sub>SA</sub>      | The system ambient air temperature external to a system chassis. This temperature is usually measured at the chassis air inlets.                                                                                                                                                                                            |

| U                    | A unit of measure used to define server rack spacing height. 1U is equal to 1.75 in, 2U equals 3.50 in, etc.                                                                                                                                                                                                                |

§

# 2 Thermal/Mechanical Reference Design

This chapter describes the thermal/mechanical reference design for Quad-Core Intel® Xeon® Processor 5400 Series. Both Quad-Core Intel® Xeon® Processor X5400 Series and Quad-Core Intel® Xeon® Processor E5400 Series are targeted for the full range of form factors (2U, 2U+ and 1U). The Quad-Core Intel® Xeon® Processor X5482 sku is an ultra performance version of the Quad-Core Intel® Xeon® Processor 5400 Series with 150W TDP and is use only in workstation platforms.

## 2.1 Mechanical Requirements

The mechanical performance of the processor cooling solution must satisfy the requirements described in this section.

## 2.1.1 **Processor Mechanical Parameters**

#### Table 2-1. Processor Mechanical Parameters Table

| Parameter                            | Minimum | Maximum    | Unit          | Notes |

|--------------------------------------|---------|------------|---------------|-------|

| Volumetric Requirements and Keepouts |         |            |               | 1     |

| Static Compressive Load              |         |            |               | 3     |

| Static Board Deflection              |         |            |               | 3     |

| Dynamic Compressive Load             |         |            |               | 3     |

| Transient Bend                       |         |            |               | 3     |

| Shear Load                           |         | 70<br>311  | lbf<br>N      | 2,4,5 |

| Tensile Load                         |         | 25<br>111  | lbf<br>N      | 2,4,6 |

| Torsion Load                         |         | 35<br>3.95 | in*lbf<br>N*m | 2,4,7 |

#### Notes:

- 1. Refer to drawings in Appendix B.

- In the case of a discrepancy, the most recent Quad-Core Intel® Xeon® Processor 5400 Series Datasheet and LGA771 Socket Mechanical Design Guide supersede targets listed in Table 2-1 above.

These socket limits are defined in the LGA771 Socket Mechanical Design Guide.

4. These package handling limits are defined in the *Quad-Core Intel*® *Xeon*® *Processor 5400 Series* Datasheet.

- 5. Shear load that can be applied to the package IHS.

- 6. Tensile load that can be applied to the package IHS.

- 7. Torque that can be applied to the package IHS.

## 2.1.2 Quad-Core Intel® Xeon® Processor 5400 Series Package

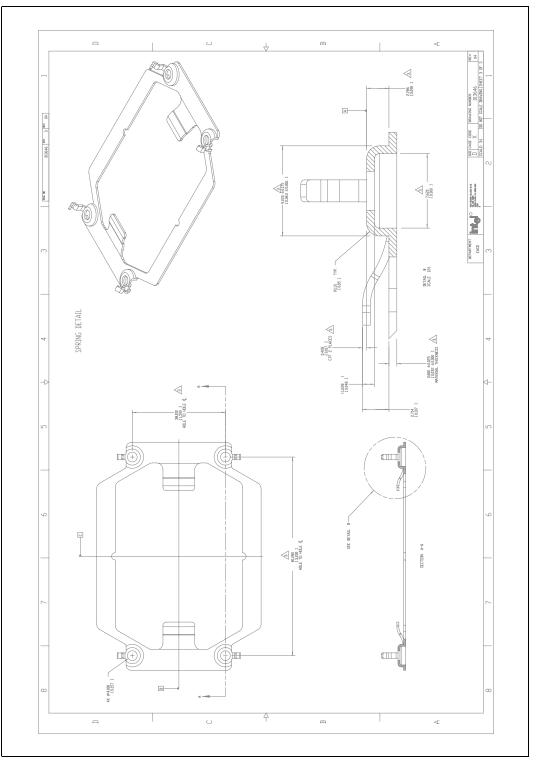

The Quad-Core Intel® Xeon® Processor 5400 Series is packaged using the flip-chip land grid array (FC-LGA) package technology. Please refer to the *Quad-Core Intel® Xeon® Processor 5400 Series Datasheet* for detailed mechanical specifications. The Quad-Core Intel® Xeon® Processor 5400 Series mechanical drawing shown in Figure 2-1, Figure 2-2, and Figure 2-3 provide the mechanical information for the Quad-Core Intel® Xeon® Processor 5400 Series. The drawing is superseded with the drawing in the processor datasheet should there be any conflicts. Integrated package/ socket stackup height information is provided in the *LGA771 Socket Mechanical Design Guide*.

Figure 2-1. Quad-Core Intel® Xeon® Processor 5400 Series Mechanical Drawing (1 of 3)

**Note:** Guidelines on potential IHS flatness variation with socket load plate actuation and installation of the cooling solution are available in the processor Thermal/Mechanical Design Guidelines.

Figure 2-2. Quad-Core Intel® Xeon® Processor 5400 Series Mechanical Drawing (2 of 3)

Figure 2-3. Quad-Core Intel® Xeon® Processor 5400 Series Mechanical Drawing (3 of 3)

**Note:** The optional dimple packing marking highlighted by Detail F from the above drawing may only be found on initial processors.

The package includes an integrated heat spreader (IHS). The IHS transfers the nonuniform heat from the die to the top of the IHS, out of which the heat flux is more uniform and spreads over a larger surface area (not the entire IHS area). This allows more efficient heat transfer out of the package to an attached cooling device. The IHS is designed to be the interface for contacting a heatsink. Details can be found in the *Quad-Core Intel*® Xeon® Processor 5400 Series Datasheet.

The processor connects to the baseboard through a 771-land surface mount socket. A description of the socket can be found in the *LGA771 Socket Mechanical Design Guide*.

The processor package and socket have mechanical load limits that are specified in the *Quad-Core Intel*® *Xeon*® *Processor 5400 Series Datasheet* and the *LGA771 Socket Mechanical Design Guide*. These load limits should not be exceeded during heatsink installation, removal, mechanical stress testing, or standard shipping conditions. For example, when a compressive static load is necessary to ensure thermal performance of the Thermal Interface Material (TIM) between the heatsink base and the IHS, it should not exceed the corresponding specification given in the *LGA771 Socket Mechanical Design Guide*.

The heatsink mass can also add additional dynamic compressive load to the package during a mechanical shock event. Amplification factors due to the impact force during shock must be taken into account in dynamic load calculations. The total combination of dynamic and static compressive load should not then exceed the processor/socket compressive dynamic load specified in the *LGA771 Socket Mechanical Design Guide* during a vertical shock. It is not recommended to use any portion of the processor substrate as a mechanical reference or load-bearing surface in either static or dynamic compressive load conditions.

## 2.1.3 Quad-Core Intel® Xeon® Processor 5400 Series Considerations

An attachment mechanism must be designed to support the heatsink since there are no features on the LGA771 socket to directly attach a heatsink. In addition to holding the heatsink in place on top of the IHS, this mechanism plays a significant role in the robustness of the system in which it is implemented, in particular:

- Ensuring thermal performance of the TIM applied between the IHS and the heatsink. TIMs, especially ones based on phase change materials, are very sensitive to applied pressure: the higher the pressure, the better the initial performance. TIMs such as thermal greases are not as sensitive to applied pressure. Refer to Section 2.5.2 and Section 2.5.7.2 for information on tradeoffs made with TIM selection. Designs should consider possible decrease in applied pressure over time due to potential structural relaxation in enabled components.

- Ensuring system electrical, thermal, and structural integrity under shock and vibration events. The mechanical requirements of the attach mechanism depend on the weight of the heatsink and the level of shock and vibration that the system must support. The overall structural design of the baseboard and system must be considered when designing the heatsink attach mechanism. Their design should provide a means for protecting LGA771 socket solder joints as well as preventing package pullout from the socket.

- **Note:** The load applied by the attachment mechanism must comply with the package and socket specifications, along with the dynamic load added by the mechanical shock and vibration requirements, as identified in Section 2.1.1.

A potential mechanical solution for heavy heatsinks is the direct attachment of the heatsink to the chassis pan. In this case, the strength of the chassis pan can be utilized rather than solely relying on the baseboard strength. In addition to the general guidelines given above, contact with the baseboard surfaces should be minimized during installation in order to avoid any damage to the baseboard.

The Intel reference design for Quad-Core Intel® Xeon® Processor 5400 Series is using such a heatsink attachment scheme. Refer to Section 2.5 for further information regarding the Intel reference mechanical solution.

## 2.2 **Processor Thermal Parameters and Features**

## 2.2.1 Thermal Control Circuit and TDP

The operating thermal limits of the processor are defined by the Thermal Profile. The intent of the Thermal Profile specification is to support acoustic noise reduction through fan speed control and ensure the long-term reliability of the processor. This specification requires that the temperature at the center of the processor IHS, known as ( $T_{CASE}$ ) remains within a certain temperature specification. For illustration, Figure 2-4 shows the measurement location for the Quad-Core Intel® Xeon® Processor 5400 Series package. Compliance with the  $T_{CASE}$  specification is required to achieve optimal operation and long-term reliability (See the Intel<sup>®</sup> Xeon<sup>®</sup> Dual- and Multi- Processor Family Thermal Test Vehicle User's Guide for Case Temperature definition and measurement methods).

To ease the burden on thermal solutions, the Thermal Monitor feature and associated logic have been integrated into the silicon of the processor. One feature of the Thermal Monitor is the Thermal Control Circuit (TCC). When active, the TCC lowers the processor temperature by reducing power consumption. This is accomplished through a combination of Thermal Monitor and Advanced Thermal Monitor (TM2). Thermal Monitor modulates the duty cycle of the internal processor clocks, resulting in a lower effective frequency. When active, the TCC turns the processor clocks off and then back on with a predetermined duty cycle. Thermal Monitor 2 activation adjusts both the

processor operating frequency (via the bus multiplier) and input voltage (via the VID signals). Please refer to the *Quad-Core Intel*® *Xeon*® *Processor 5400 Series Datasheet* for further details on TM and TM2.

PROCHOT# is designed to assert at or a few degrees higher than maximum  $T_{CASE}$  (as specified by the thermal profile) when dissipating TDP power, and can not be interpreted as an indication of processor case temperature. This temperature delta accounts for processor package, lifetime, and manufacturing variations and attempts to ensure the Thermal Control Circuit is not activated below maximum  $T_{CASE}$  when dissipating TDP power. There is no defined or fixed correlation between the PROCHOT# assertion temperature and the case temperature. However, with the introduction of the Digital Thermal Sensor (DTS) on the *Quad-Core Intel*® Xeon® Processor 5400 Series, the DTS reports a relative offset below the PROCHOT# assertion (see Section 2.2.2 for more details on the Digital Thermal Sensor). Thermal solutions must be designed to the processor specifications (i.e Thermal Profile) and can not be adjusted based on experimental measurements of  $T_{CASE}$ , PROCHOT#, or Digital Thermal Sensor on random processor samples.

By taking advantage of the Thermal Monitor features, system designers may reduce thermal solution cost by designing to the Thermal Design Power (TDP) instead of maximum power. TDP should be used for processor thermal solution design targets. TDP is not the maximum power that the processor can dissipate. TDP is based on measurements of processor power consumption while running various high power applications. This data set is used to determine those applications that are interesting from a power perspective. These applications are then evaluated in a controlled thermal environment to determine their sensitivity to activation of the thermal control circuit. This data set is then used to derive the TDP targets published in the processors datasheet. The Thermal Monitor can protect the processors in rare workload excursions above TDP. Therefore, thermal solutions should be designed to dissipate this target power level. The thermal management logic and thermal monitor features are discussed in extensive detail in the *Quad-Core Intel*® *Xeon*® *Processor 5400 Series Datasheet*.

In addition, on-die thermal management features called THERMTRIP# and FORCEPR# are available on the Quad-Core Intel® Xeon® Processor 5400 Series. They provide a thermal management approach to support the continued increases in processor frequency and performance. Please see the *Quad-Core Intel*® *Xeon*® *Processor 5400 Series Datasheet* for guidance on these thermal management features.

## 2.2.2 Digital Thermal Sensor

The Quad-Core Intel® Xeon® Processor 5400 Series include on-die temperature sensor feature called Digital Thermal Sensor (DTS). The DTS uses the same sensor utilized for TCC activation. Each individual processor is calibrated so that TCC activation occurs at a DTS value of 0. The temperature reported by the DTS is the relative offset in PECI counts below the onset of the TCC activation and hence is negative. Changes in PECI counts are roughly linear in relation to temperature changes in degrees Celsius. For example, a change in PECI count by '1' represents a change in temperature of approximately 1°C. However, this linearity cannot be guaranteed as the offset below TCC activation exceeds 20-30 PECI counts. Also note that the DTS will not report any values above the TCC activation temperature, it will simply return 0 in this case.

The DTS facilitates the use of multiple thermal sensors within the processor without the burden of increasing the number of thermal sensor signal pins on the processor package. Operation of multiple DTS will be discussed in more detail in Section 2.2.4. Also, the DTS utilizes thermal sensors that are optimally located when compared with thermal diodes available with legacy processors. This is achieved as a result of a

smaller foot print and decreased sensitivity to noise. These DTS benefits will result in more accurate fan speed control and TCC activation. The DTS application in fan speed control will be discussed in more detail in Section 2.4.1.

## 2.2.3 Platform Environmental Control Interface (PECI)

The PECI interface is designed specifically to convey system management information from the processor (initially, only thermal data from the Digital Thermal Sensor). It is a proprietary single wire bus between the processor and the chipset or other health monitoring device. The PECI specification provides a specific command set to discover, enumerate devices, and read the temperature. For an overview of the PECI interface, please refer to *PECI Feature Set Overview*. For more detailed information on PECI, please refer to *Platform Environment Control Interface (PECI) Specification* and *Quad-Core Intel*® Xeon® Processor 5400 Series Datasheet.

## 2.2.4 Multiple Core Special Considerations

## 2.2.4.1 Multiple Digital Thermal Sensor Operation

Each Quad-Core Intel® Xeon® Processor 5400 Series can have multiple Digital Thermal Sensors located on the die. Each die within the processor currently maps to a PECI domain. The Quad-Core Intel® Xeon® Processor 5400 Series contains two cores per die (domain) and two domains (die) per socket. BIOS will be responsible for detecting the proper processor type and providing the number of domains to the thermal management system. An external PECI device that is part of the thermal management system polls the processor domains for temperature information and currently receives the highest of the DTS output temperatures within each domain. Figure 2-5 provides an illustration of the DTS domains for the Quad-Core Intel® Xeon® Processor 5400 Series.

#### Figure 2-5. DTS Domain for Quad-Core Intel® Xeon® Processor 5400 Series

Quad-Core Intel® Xeon® Processor 5400 Series TMDG

## 2.2.4.2 Thermal Monitor for Multiple Core Products

The thermal management for multiple core products has only one  $T_{CONTROL}$  value per processor. The  $T_{CONTROL}$  for processor 0 and  $T_{CONTROL}$  for processor 1 are independent from each other. If the DTS temperature from any domain within the processor is greater than or equal to  $T_{CONTROL}$ , the processor case temperature must remain at or below the temperature as specified by the thermal profile. See Section 2.2.6 for information on  $T_{CONTROL}$ . The PECI signal is available through CPU pin (G5) on each LGA771 socket for the Quad-Core Intel® Xeon® Processor 5400 Series. Through this pin, the two domains provide the current hottest value received from all the temperature sensors, to an external PECI device such as a thermal management system.

### 2.2.4.3 PROCHOT#, THERMTRIP#, and FORCEPR#

The PROCHOT# and THERMTRIP# outputs will be shared by all cores on a processor. The first core to reach TCC activation will assert PROCHOT#. A single FORCEPR# input will be shared by every core. Table 2-2 provides an overview of input and output conditions for the Quad-Core Intel® Xeon® Processor 5400 Series thermal management features.

# Table 2-2. Input and Output Conditions for the Quad-Core Intel® Xeon® Processor 5400 Series Thermal Management Features

| Item                                              | Processor Input                                               | Processor Output                            |  |  |

|---------------------------------------------------|---------------------------------------------------------------|---------------------------------------------|--|--|

| TM1/TM2DTSCore $x \ge$ TCC Activation Temperature |                                                               | All Cores TCC Activation                    |  |  |

| PROCHOT#                                          | DTS <i>core</i> $x \ge$ TCC Activation Temperature            | PROCHOT# Asserted                           |  |  |

| THERMTRIP#                                        | DTS <i>Core X</i> $\geq$ THERMTRIP # Assertion<br>Temperature | THERMTRIP# Asserted,<br>all cores shut down |  |  |

| FORCEPR#                                          | FORCEPR# Asserted                                             | All Cores TCC Activation                    |  |  |

Note:

1. X=1,2,3,4; represents any one of the core1, core2, core3 and core4 in the Quad-Core Intel® Xeon® Processor 5400 Series.

2. For more information on PROCHOT#, THERMTRIP#, and FORCEPR# see the *Quad-Core Intel® Xeon® Processor 5400* Series Datasheet.

### 2.2.4.4 Heatpipe Orientation for Multiple Core Processors

Thermal management of multiple core processors can be achieved without the use of heatpipe heatsinks, as demonstrated by the Intel Reference Thermal Solution discussed in Section 2.5.

To assist customers interested in designing heatpipe heatsinks, processor core locations have been provided. In some cases, this may influence the designer's selection of heatpipe orientation. For this purpose, the core geometric center locations, as illustrated in Figure 2-6, are provided in Table 2-3. Dimensions originate from the vertical edge of the IHS nearest to the pin 1 fiducial as shown in Figure 2-6.

#### Figure 2-6. Processor Core Geometric Center Locations

#### Table 2-3. Processor Core Geometric Center Dimensions

| Feature | X Dimension | Y Dimension |

|---------|-------------|-------------|

| Core 1  | 18.15 mm    | 6.15 mm     |

| Core 2  | 18.15 mm    | 10.35 mm    |

| Core 3  | 18.15 mm    | 18.85 mm    |

| Core 4  | 18.15 mm    | 23.05 mm    |

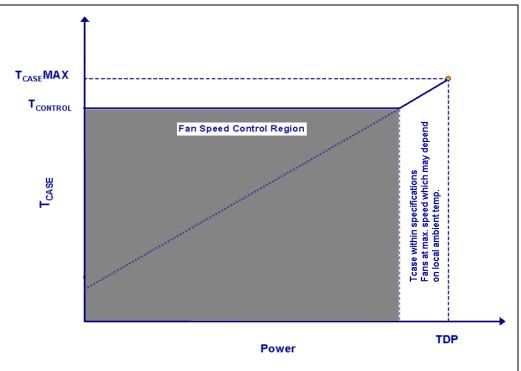

## 2.2.5 Thermal Profile

The thermal profile is a line that defines the relationship between a processor's case temperature and its power consumption as shown in Figure 2-7. The equation of the thermal profile is defined as:

#### Equation 2-1.y = ax + b

Where:

| y = Processor case temperature, $T_{CAS}$ | = (°C) |

|-------------------------------------------|--------|

|-------------------------------------------|--------|

- x = Processor power consumption (W)

- a = Case-to-ambient thermal resistance,  $\Psi CA$  (°C/W)

- b = Processor local ambient temperature, TLA (°C)

#### Figure 2-7. Thermal Profile Diagram

The high end point of the Thermal Profile represents the processor's TDP and the associated maximum case temperature ( $T_{CASE\_MAX}$ ) and the lower end point represents the local ambient temperature at P = 0W. The slope of the Thermal Profile line represents the case-to-ambient resistance of the thermal solution with the y-intercept being the local processor ambient temperature. The slope of the Thermal Profile is constant, which indicates that all frequencies of a processor defined by the Thermal Profile will require the same heatsink case-to-ambient resistance.

In order to satisfy the Thermal Profile specification, a thermal solution must be at or below the Thermal Profile line for the given processor when its DTS temperature is greater than  $T_{CONTROL}$  (refer to Section 2.2.6). The Thermal Profile allows the customers to make a trade-off between the thermal solution case-to-ambient resistance and the processor local ambient temperature that best suits their platform implementation (refer to Section 2.4.3). There can be multiple combinations of thermal solution case-to-ambient resistance and processor local ambient temperature that can meet a given Thermal Profile. If the case-to-ambient resistance and the local ambient temperature are known for a specific thermal solution, the Thermal Profile of that solution can easily be plotted against the Thermal Profile specification. As explained

above, the case-to-ambient resistance represents the slope of the line and the processor local ambient temperature represents the y-axis intercept. Hence the T<sub>CASE MAX</sub> value of a specific solution can be calculated at TDP. Once this point is determined, the line can be extended to Power (P) = 0W representing the Thermal Profile of the specific solution. If that line stays at or below the Thermal Profile specification, then that particular solution is deemed as a compliant solution.

#### 2.2.6 **T**<sub>CONTROL</sub> Definition

T<sub>CONTROL</sub> can be described as a trigger point for fan speed control implementation. The processor T<sub>CONTROL</sub> value provided by the Digital Thermal Sensor is relative and no longer absolute. The T<sub>CONTROL</sub> value is now defined as a relative value to the TCC activation set point (i.e. PECI Count = 0), as indicated by PROCHOT#. Figure 2-8 depicts the interaction between the T<sub>CONTROL</sub> value and Digital Thermal Sensor value.

#### T<sub>CONTROL</sub> Value and Digital Thermal Sensor Value Interaction Figure 2-8.

The value for  $T_{CONTROL}$  is calibrated in manufacturing and configured for each processor individually. For the Quad-Core Intel® Xeon® Processor 5400 Series, the T<sub>CONTROL</sub> value is obtained by reading the processor model specific register (IA32\_TEMPERATURE\_TARGET MSR).

There is no  $T_{CONTROL}_{BASE}$  value to sum as previously required on legacy processors. The fan speed control device only needs to read the  $T_{OFFSET}$  MSR and compare this to Note: the DTS value from the PECI interface. The equation for calculating T<sub>CONTROL</sub> is:

### Equation 2-2.T<sub>CONTROL</sub> = -T<sub>OFFSET</sub>

#### Where:

**T**OFFSET = A DTS-based value programmed into each processor during manufacturing that can be obtained by reading the IA32\_TEMPERATURE\_TARGET MSR. This is a static and a unique value. Refer to the RS - Wolfdale Processor Family BIOS Writer's Guide (BWG) for further details.

Figure 2-9 depicts the interaction between the Thermal Profile and  $T_{CONTROL}$ .

Figure 2-9. T<sub>CONTROL</sub> and Thermal Profile Interaction

If the DTS temperature is less than  $T_{CONTROL}$ , then the case temperature is permitted to exceed the Thermal Profile, but the DTS temperature must remain at or below  $T_{CONTROL}$ . The thermal solution for the processor must be able to keep the processor's  $T_{CASE}$  at or below the Thermal Profile when operating between the  $T_{CONTROL}$  and  $T_{CASE}$  max at TDP under heavy workload conditions.

Refer to Section 2.4.1 for the implementation of the  $T_{CONTROL}$  value in support of fan speed control (FSC) design to achieve better acoustic performance.

## 2.2.7 Thermal Profile Concepts for the Quad-Core Intel® Xeon® Processor 5400 Series

# 2.2.7.1 Dual Thermal Profile Concept for the Quad-Core Intel® Xeon® Processor X5400 Series

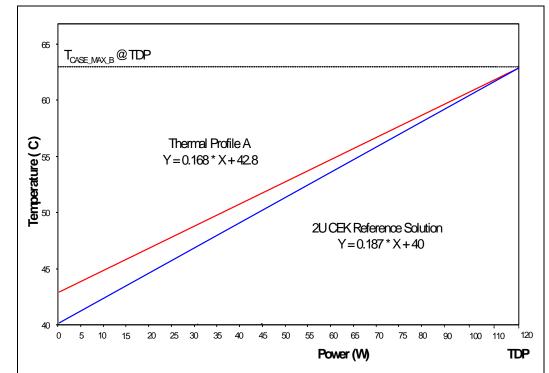

The Quad-Core Intel® Xeon® Processor X5400 Series is designed to go into various form factors, including the volumetrically constrained 1U and custom blade form factors. Due to certain limitations of such form factors (i.e. airflow, thermal solution height), it is very challenging to meet the thermal requirements of the processor. To mitigate these form factor constraints, Intel has developed a dual Thermal Profile specification, shown in Figure 2-10.

The Thermal Profile A is based on Intel's 2U+ air cooling solution. Designing to Thermal Profile A ensures that no measurable performance loss due to Thermal Control Circuit (TCC) activation is observed in the processor. It is expected that TCC would only be activated for very brief periods of time when running a worst-case real world application in a worst-case thermal condition. These brief instances of TCC activation are not expected to impact the performance of the processor. A worst case real world application is defined as a commercially available, useful application which dissipates a power equal to, or above, the TDP for a thermally relevant timeframe. One example of a worst-case thermal condition is when a processor local ambient temperature is at or above 42.8°C for Quad-Core Intel® Xeon® Processor X5400 Series Thermal Profile A.

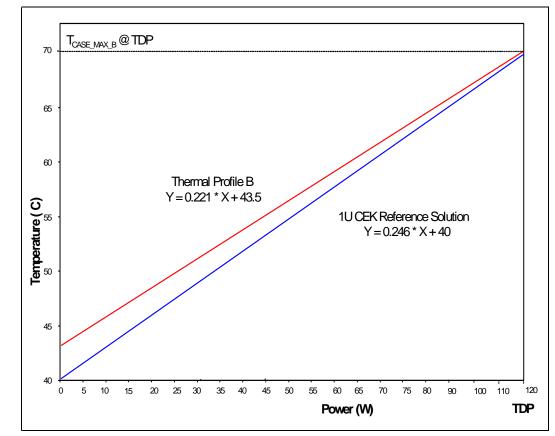

Thermal Profile B supports volumetrically constrained platforms (i.e. 1U, blades, etc.), and is based on Intel's 1U air cooling solution. Because of the reduced capability represented by such thermal solutions, designing to Thermal Profile B results in an increased probability of TCC activation and an associated measurable performance loss. Measurable performance loss is defined to be any degradation in the processor's performance greater than 1.5%. The 1.5% number is chosen as the baseline since the run-to-run variation in a given performance benchmark is typically between 1 and 2%.

Although designing to Thermal Profile B results in increased  $T_{CASE}$  temperatures compared to Thermal Profile A at a given power level, both of these Thermal Profiles ensure that Intel's long-term processor reliability requirements are satisfied. In other words, designing to Thermal Profile B does not impose any additional risk to Intel's long-term reliability requirements. Thermal solutions that exceed Thermal Profile B specification are considered incompliant and will adversely affect the long-term reliability of the processor.

Refer to the *Quad-Core Intel*® *Xeon*® *Processor 5400 Series Datasheet* or Section 2.2.8 for the Thermal Profile A and Thermal Profile B specifications. Section 2.5 of this document also provides details on the 2U+ and 1U Intel reference thermal solutions that are designed to meet the Quad-Core Intel® Xeon® Processor X5400 Series Thermal Profile A and Thermal Profile B respectively.

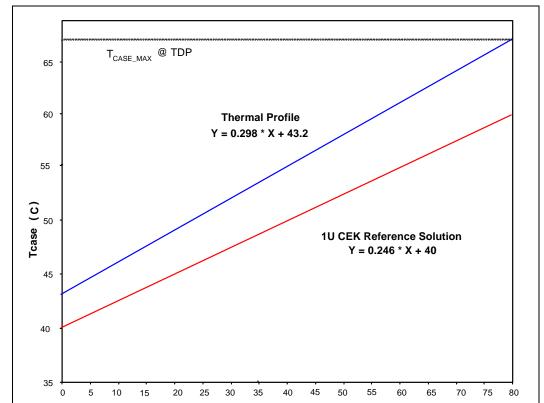

#### 2.2.7.2 Thermal Profile Concept for the Quad-Core Intel® Xeon® Processor E5400/X5482 Series

The Quad-Core Intel® Xeon® Processor E5400 Series is designed to go into various form factors, including the volumetrically constrained 1U and custom blade form factors. The Quad-Core Intel® Xeon® Processor X5482 is designed to go into volumetrically unconstrained workstation platforms only. Intel has developed single thermal profile for E5400/X5482 Series.

Designing to the Thermal Profile ensures that no measurable performance loss due to Thermal Control Circuit (TCC) activation is observed in the processor. It is expected that TCC would only be activated for very brief periods of time when running a worstcase real world application in a worst-case thermal condition. These brief instances of TCC activation are not expected to impact the performance of the processor. A worst case real world application is defined as a commercially available, useful application which dissipates a power equal to, or above, the TDP for a thermally relevant timeframe. One example of a worst-case thermal condition is when a processor local ambient temperature is at or above 43.2°C for Quad-Core Intel® Xeon® Processor E5400 Series Thermal Profile.

Thermal solutions that exceed the Thermal Profile specification are considered incompliant and will adversely affect the long-term reliability of the processor.

Refer to the *Quad-Core Intel*® *Xeon*® *Processor 5400 Series Datasheet* or Section 2.2.8 for the Quad-Core Intel® Xeon® Processor 5400 Series Thermal Profile specifications. Section 2.5 and Appendix A of this document provide details on 1U Intel reference thermal solutions that are designed to meet the Quad-Core Intel® Xeon® Processor E5400 Series Thermal Profile.

## 2.2.8 Performance Targets

The Thermal Profile specifications for this processor are published in the *Quad-Core Intel*® *Xeon*® *Processor 5400 Series Datasheet.* These Thermal Profile specifications are shown as a reference in the subsequent discussions.

28

#### Notes:

- 1.

- The The thermal specifications shown in this graph are for Quad-Core Intel® Xeon® Processor X5400 Series except the Quad-Core Intel® Xeon® Processor X5482 sku. Refer to the Quad-Core Intel® Xeon® Processor 5400 Series Datasheet for the Thermal Profile specifications. In case of conflict, the data information in the datasheet supersedes any data in this figure. 2.

#### Figure 2-12. Thermal Profile for Quad-Core Intel® Xeon® Processor E5400 Series

#### Thermal Profile (2U) Tcase [C] **Thermal Profile** Y = 0.187 \* x + 35100 110 120 130 Power [W]

Figure 2-13. Thermal Profile for Quad-Core Intel® Xeon® Processor X5482 Series

Table 2-4 and Table 2-5 describe the thermal performance target for the Quad-Core Intel® Xeon® Processor 5400 Series cooling solution enabled by Intel.

## Table 2-4. Intel Reference Heatsink Performance Targets for the Quad-Core Intel® Xeon® Processor X5400 Series

| Parameter               | Maximum       | Unit                             | Notes                             |

|-------------------------|---------------|----------------------------------|-----------------------------------|

| Altitude                | Sea-level     | m                                | Heatsink designed at 0 meters     |

| T <sub>LA</sub>         | 40            | °C                               |                                   |

| TDP                     | 120           | W                                |                                   |

|                         | 2U+ CEK       | , Thermal Profile                | Α                                 |

| T <sub>CASE_MAX_A</sub> | 63            | °C                               |                                   |

| Airflow                 | 27<br>45.9    | CFM<br>m <sup>3</sup> / hr       | Airflow through the heatsink fins |

| Pressure Drop           | 0.182<br>45.3 | Inches of H <sub>2</sub> O<br>Pa |                                   |

| ΨCA                     | 0.187         | °C/W                             | Mean + 3 $\sigma$                 |

|                         | 1U CEK,       | Thermal Profile                  | В                                 |

| T <sub>CASE_MAX_B</sub> | 70            | °C                               |                                   |

| Airflow                 | 15<br>25.5    | CFM<br>m <sup>3</sup> / hr       | Airflow through the heatsink fins |

| Pressure Drop           | 0.331<br>82.4 | Inches of H <sub>2</sub> O<br>Pa |                                   |

| ΨCA                     | 0.246         | °C/W                             | Mean + 3σ                         |

Quad-Core Intel® Xeon® Processor 5400 Series TMDG

# Table 2-5. Intel Reference Heatsink Performance Targets for the Quad-Core Intel® Xeon® Processor E5400 Series

| Parameter             | Maximum       | Unit                             | Notes                             |

|-----------------------|---------------|----------------------------------|-----------------------------------|

| Altitude              | Sea-Level     | m                                | Heatsink designed at 0 meters     |

| T <sub>LA</sub>       | 40            | °C                               |                                   |

| TDP                   | 80            | W                                |                                   |

|                       | ·             | 1U CEK                           |                                   |

| T <sub>CASE_MAX</sub> | 67            | °C                               |                                   |

| Airflow               | 15<br>25.5    | CFM<br>m <sup>3</sup> / hr       | Airflow through the heatsink fins |

| Pressure Drop         | 0.331<br>82.4 | Inches of H <sub>2</sub> O<br>Pa |                                   |

| ΨCA                   | 0.246         | °C/W                             | Mean + 3σ                         |

|                       | 1U Alte       | ernative Heatsin                 | K                                 |

| T <sub>CASE_MAX</sub> | 67            | °C                               |                                   |

| Airflow               | 15<br>25.5    | CFM<br>m <sup>3</sup> / hr       | Airflow through the heatsink fins |

| Pressure Drop         | 0.331<br>82.4 | Inches of H <sub>2</sub> O<br>Pa |                                   |

| ΨCA                   | 0.331         | °C/W                             | Mean + 3 $\sigma$                 |

Intel does not enable reference heatsink for the Quad-Core Intel® Xeon® Processor X5482 with 150W TDP. The Intel 2U CEK is capable of meeting the thermal specification when local ambient temperature (T<sub>LA</sub>) is maintained at or below 35°C.

## 2.3 Fan Fail Guidelines