# Intel<sup>®</sup> 80200 Processor based on Intel<sup>®</sup> XScale<sup>™</sup> Microarchitecture

**Developer's Manual**

March, 2003

Order Number: 273411-003

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel® products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® 80200 Processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright© Intel Corporation, 2003

\*Other brands and names are the property of their respective owners.

ARM and StrongARM are registered trademarks of ARM, Ltd.

| 1   | In                    | troduction         | on                                                     |                                        | 1      |

|-----|-----------------------|--------------------|--------------------------------------------------------|----------------------------------------|--------|

| 1.1 | Intel <sup>®</sup> 80 | 200 Proces         | ssor based on Intel <sup>®</sup> XScale <sup>™</sup> N | Microarchitecture High-Level Overview1 | 1      |

|     | 1.1.1                 |                    |                                                        | 1                                      |        |

|     | 1.1.2                 | Features           |                                                        |                                        |        |

|     |                       | 1.1.2.1            | Multiply/Accumulate (MAC)                              |                                        | 2      |

|     |                       | 1.1.2.2            |                                                        |                                        |        |

|     |                       | 1.1.2.3            |                                                        |                                        |        |

|     |                       | 1.1.2.4            |                                                        |                                        |        |

|     |                       | 1.1.2.5<br>1.1.2.6 |                                                        |                                        |        |

|     |                       | 1.1.2.0            |                                                        |                                        |        |

|     |                       | 1.1.2.8            |                                                        |                                        |        |

|     |                       | 1.1.2.9            |                                                        |                                        |        |

|     |                       | 1.1.2.10           |                                                        |                                        |        |

|     |                       | 1.1.2.11           |                                                        |                                        |        |

| 1.2 |                       |                    |                                                        |                                        |        |

|     | 1.2.1                 |                    |                                                        |                                        |        |

|     | 1.2.2                 |                    |                                                        |                                        |        |

| 1.3 | Other Re              | elevant Doc        | uments                                                 | 6                                      | 3      |

| 2   | Р                     | rogramm            | ing Model                                              | 1                                      | I      |

| 2.1 | ARM* Ar               | chitecture         | Compliance                                             | 1                                      | 1      |

| 2.2 | ARM* Ar               | chitecture         | mplementation Options                                  | 1                                      | 1      |

|     | 2.2.1                 | Big Endia          | an versus Little Endian                                | 1                                      | 1      |

|     | 2.2.2                 | 26-Bit Co          | ode                                                    | 1                                      | 1      |

|     | 2.2.3                 | Thumb* .           |                                                        | 1                                      | 1      |

|     | 2.2.4                 |                    |                                                        | 2                                      |        |

|     | 2.2.5                 |                    | •                                                      | 2                                      |        |

| 2.3 |                       |                    |                                                        |                                        |        |

|     | 2.3.1                 |                    |                                                        |                                        |        |

|     |                       | 2.3.1.1            |                                                        | nulate Format                          |        |

|     |                       | 2.3.1.2            |                                                        | s Format                               |        |

|     | 2.3.2                 |                    |                                                        |                                        |        |

|     | 2.3.3                 |                    |                                                        | 11                                     |        |

|     | 2.3.4                 |                    |                                                        | 12                                     |        |

|     |                       | 2.3.4.1<br>2.3.4.2 |                                                        |                                        |        |

|     |                       | 2.3.4.2<br>2.3.4.3 |                                                        |                                        |        |

|     |                       | 2.3.4.4            | Data Aborts                                            | 14                                     | ر<br>4 |

|     |                       | 2.3.4.5            |                                                        | tions16                                |        |

|     | 2                     | 2.3.4.6            |                                                        | 16                                     |        |

| 3   | M                     | emory N            | anagement                                              |                                        | l      |

| 3.1 |                       | -                  | <u> </u>                                               | 1                                      |        |

| 3.2 |                       |                    |                                                        | 2                                      |        |

|     | 3.2.1                 |                    |                                                        |                                        |        |

|     | 3.2.2                 | Memory             | Attributes                                             |                                        | 2      |

|             |          | 3.2.2.1     | Page (P) Attribute Bit                                | 2 |

|-------------|----------|-------------|-------------------------------------------------------|---|

|             |          | 3.2.2.2     | Cacheable (C), Bufferable (B), and eXtension (X) Bits |   |

|             |          | 3.2.2.3     | Instruction Cache                                     | 2 |

|             |          | 3.2.2.4     | Data Cache and Write Buffer                           |   |

|             |          | 3.2.2.5     | Details on Data Cache and Write Buffer Behavior       |   |

|             |          | 3.2.2.6     | Memory Operation Ordering                             |   |

|             | 3.2.3    |             | ns                                                    |   |

| 3.3         |          |             | MU, Instruction Cache, and Data Cache                 |   |

| 3.4         |          |             |                                                       |   |

|             | 3.4.1    |             | e (Flush) Operation                                   |   |

|             | 3.4.2    | _           | ı/Disabling                                           |   |

|             | 3.4.3    |             | Entries                                               |   |

|             | 3.4.4    | Round-F     | Robin Replacement Algorithm                           | 9 |

| 4           | Ir       | nstructio   | n Cache                                               | 1 |

| 4.1         | Overvie  | 14/         |                                                       | 4 |

| 4.2         |          |             |                                                       |   |

| 4.2         | 4.2.1    |             | n When Instruction Cache is Enabled                   |   |

|             | 4.2.1    |             | on When The Instruction Cache Is Disabled             |   |

|             |          | •           |                                                       |   |

|             | 4.2.3    |             | Dicy                                                  |   |

|             | 4.2.4    |             | Robin Replacement Algorithm                           |   |

|             | 4.2.5    | -           | otection                                              |   |

|             | 4.2.6    |             | on Fetch Latency                                      |   |

|             | 4.2.7    |             | on Cache Coherency                                    |   |

| 4.3         |          |             | Control                                               |   |

|             | 4.3.1    |             | on Cache State at RESET                               |   |

|             | 4.3.2    |             | ı/Disabling                                           |   |

|             | 4.3.3    |             | ing the Instruction Cache                             |   |

|             | 4.3.4    |             | Instructions in the Instruction Cache                 |   |

|             | 4.3.5    | Unlockin    | g Instructions in the Instruction Cache               | 9 |

| 5           | В        | Branch Ta   | arget Buffer                                          | 1 |

| 5.1         | Branch i | Target Buff | er (BTB) Operation                                    | 1 |

| 0           | 5.1.1    | •           | (5.5) opolalo                                         |   |

|             | 5.1.2    |             | Policy                                                |   |

| 5.2         | _        |             | olioy                                                 |   |

| J. <u>L</u> | 5.2.1    |             | g/Enabling                                            |   |

|             | 5.2.2    | •           | ion                                                   |   |

| c           |          |             | ne                                                    | - |

| 6           |          |             |                                                       |   |

| 6.1         |          | -           |                                                       |   |

|             | 6.1.1    |             | che Overview                                          |   |

|             | 6.1.2    |             | a Cache Overview                                      |   |

|             | 6.1.3    |             | ffer and Fill Buffer Overview                         |   |

| 6.2         |          |             | ni-Data Cache Operation                               |   |

|             | 6.2.1    |             | n When Caching is Enabled                             |   |

|             | 6.2.2    | •           | n When Data Caching is Disabled                       |   |

|             | 6.2.3    |             | olicies                                               |   |

|             |          | 6.2.3.1     | Cacheability                                          |   |

|             |          | 6.2.3.2     | Read Miss Policy                                      | 6 |

|     | 6.2.         |                                                     |    |

|-----|--------------|-----------------------------------------------------|----|

|     | 6.2.         |                                                     |    |

|     |              | lound-Robin Replacement Algorithm                   |    |

|     |              | arity Protection                                    |    |

|     |              | tomic Accesses                                      |    |

| 6.3 |              | and Mini-Data Cache Control                         |    |

|     |              | ata Memory State After Reset                        |    |

|     |              | nabling/Disabling                                   |    |

|     |              | nvalidate & Clean Operations                        |    |

|     | 6.3.         |                                                     |    |

| 6.4 | •            | ing the Data Cache as Data RAM                      |    |

| 6.5 | Write Buffer | /Fill Buffer Operation and Control                  | 16 |

| 7   | Con          | figuration                                          | 1  |

| 7.1 | Overview     |                                                     | 1  |

| 7.2 | CP15 Regis   | ters                                                | 2  |

|     | 7.2.1 R      | legister 0: ID and Cache Type Registers             | 5  |

|     |              | Register 1: Control and Auxiliary Control Registers |    |

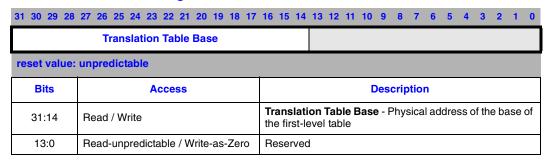

|     |              | legister 2: Translation Table Base Register         |    |

|     |              | Register 3: Domain Access Control Register          |    |

|     |              | legister 4: Reserved                                |    |

|     | 7.2.6 R      | legister 5: Fault Status Register                   | 10 |

|     | 7.2.7 R      | legister 6: Fault Address Register                  | 10 |

|     |              | Register 7: Cache Functions                         |    |

|     |              | legister 8: TLB Operations                          |    |

|     |              | Register 9: Cache Lock Down                         |    |

|     |              | legister 10: TLB Lock Down                          |    |

|     | 7.2.12 R     | legister 11-12: Reserved                            | 15 |

|     | 7.2.13 R     | legister 13: Process ID                             | 16 |

|     | 7.2.         | 13.1 The PID Register Affect On Addresses           | 16 |

|     | 7.2.14 R     | legister 14: Breakpoint Registers                   | 17 |

|     | 7.2.15 R     | Register 15: Coprocessor Access Register            | 18 |

| 7.3 |              | ters                                                |    |

|     | 7.3.1 R      | Registers 0-3: Performance Monitoring               | 20 |

|     |              | legister 4-5: Reserved                              |    |

|     | 7.3.3 R      | legisters 6-7: Clock and Power Management           | 21 |

|     | 7.3.4 R      | Registers 8-15: Software Debug                      | 22 |

| 8   | Syst         | tem Management                                      | 1  |

| 8.1 | Clocking     |                                                     | 1  |

| 8.2 |              | Reset                                               |    |

|     |              | leset Sequence                                      |    |

|     |              | Reset Effect on Outputs                             |    |

| 8.3 |              | agement                                             |    |

|     |              | nvocation                                           |    |

|     |              | ignals Associated with Power Management             |    |

| 9   | Inter        | rrupts                                              | 1  |

| 9.1 | Introduction | •                                                   | 1  |

| 9.2 |              | errupts                                             |    |

|     |              |                                                     |    |

| 9.3  |          | mer Model                                                                 |   |

|------|----------|---------------------------------------------------------------------------|---|

|      | 9.3.1    | INTCTL                                                                    | 3 |

|      | 9.3.2    | INTSRC                                                                    | 4 |

|      | 9.3.3    | INTSTR                                                                    | 5 |

| 10   | E        | xternal Bus                                                               | 1 |

| 10.1 | General  | Description                                                               | 1 |

| 10.2 |          | escription                                                                |   |

|      | 10.2.1   | Request Bus                                                               |   |

|      |          | 10.2.1.1 Intel <sup>®</sup> 80200 Processor Use of the Request Bus        |   |

|      | 10.2.2   | Data Bus                                                                  |   |

|      | 10.2.3   | Critical Word First                                                       |   |

|      | 10.2.4   | Configuration Pins                                                        |   |

|      | 10.2.5   | Multimaster Support                                                       |   |

|      | 10.2.6   | Abort                                                                     |   |

|      | 10.2.7   | ECC                                                                       |   |

|      | 10.2.8   | Big Endian System Configuration                                           |   |

| 10.3 | Example  | • •                                                                       |   |

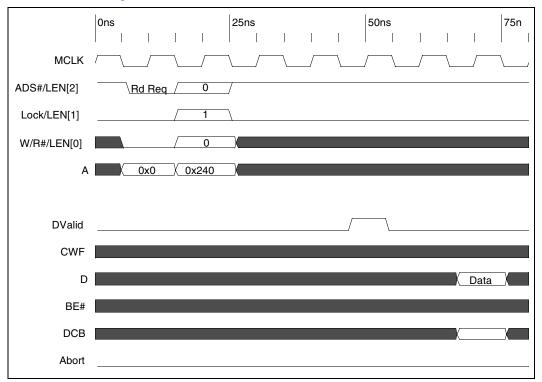

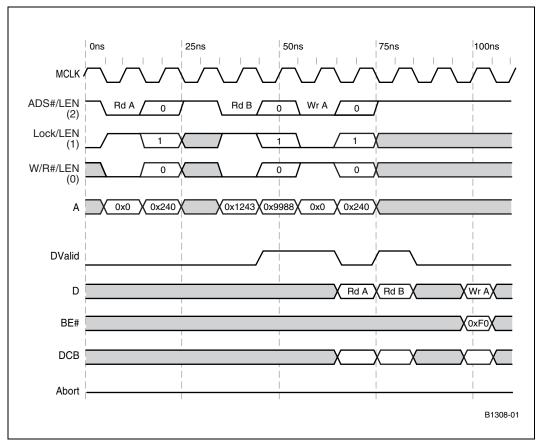

| 10.0 | 10.3.1   | Simple Read Word                                                          |   |

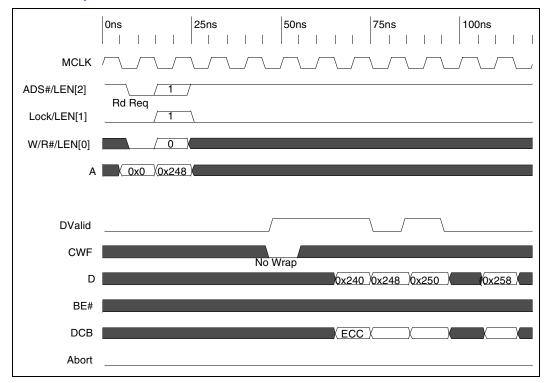

|      | 10.3.2   | Read Burst, No Critical Word First                                        |   |

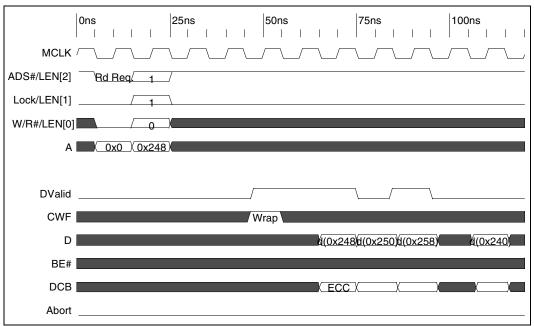

|      | 10.3.3   | Read Burst, Critical Word First Data Return                               |   |

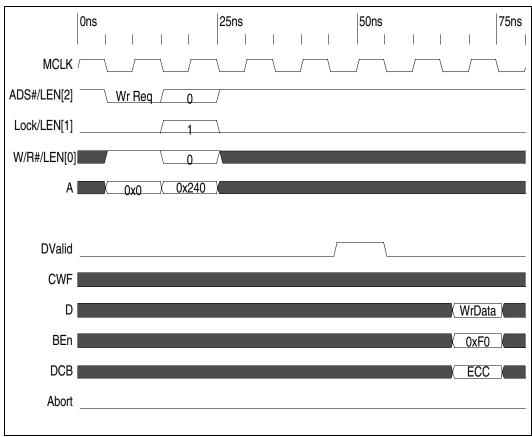

|      | 10.3.4   | Word Write                                                                |   |

|      | 10.3.5   | Two Word Coalesced Write                                                  |   |

|      |          | 10.3.5.1 Write Burst                                                      |   |

|      | 10.3.6   | Write Burst, Coalesced                                                    |   |

|      | 10.3.7   | Pipelined Accesses                                                        |   |

|      | 10.3.8   | Locked Access                                                             |   |

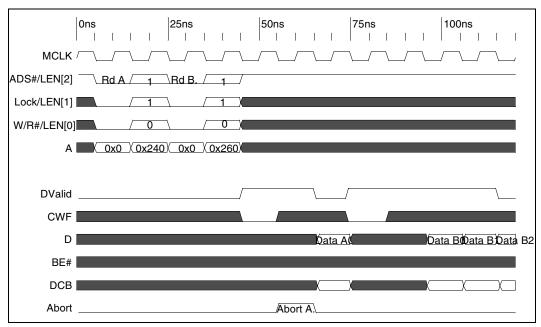

|      | 10.3.9   | Aborted Access.                                                           |   |

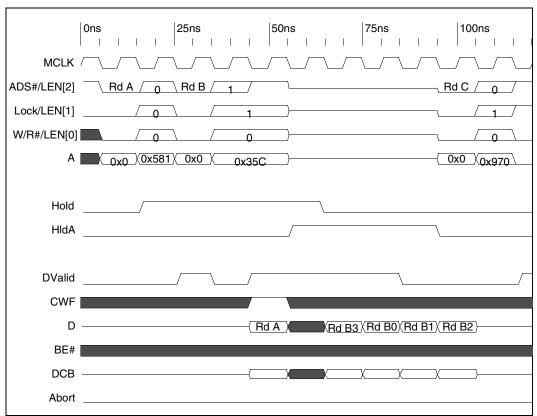

|      | 10.3.10  | Hold                                                                      |   |

|      |          |                                                                           |   |

| 11   | В        | us Controller                                                             | 1 |

| 11.1 | Introduc | tion                                                                      | 1 |

| 11.2 |          |                                                                           |   |

| 11.3 |          | ndling                                                                    |   |

|      | 11.3.1   | Bus Aborts                                                                |   |

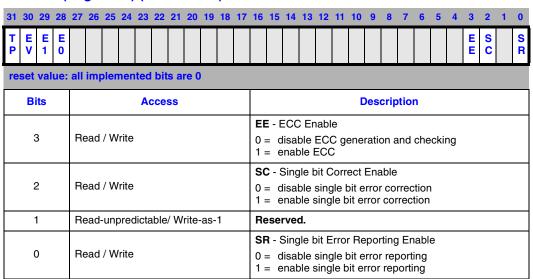

|      | 11.3.2   | ECC Errors                                                                |   |

| 11.4 | Program  | mer Model                                                                 |   |

|      | 11.4.1   | BCU Control Registers                                                     |   |

|      | 11.4.2   | ECC Error Registers                                                       |   |

|      |          | · ·                                                                       |   |

| 12   |          | erformance Monitoring                                                     |   |

| 12.1 |          | N                                                                         |   |

| 12.2 |          | ounter (CCNT; CP14 - Register 1)                                          |   |

| 12.3 | Performa | ance Count Registers (PMN0 - PMN1; CP14 - Register 2 and 3, Respectively) |   |

|      | 12.3.1   | Extending Count Duration Beyond 32 Bits                                   | 3 |

| 12.4 | Performa | ance Monitor Control Register (PMNC)                                      |   |

|      | 12.4.1   | Managing PMNC                                                             |   |

| 12.5 | Performa | ance Monitoring Events                                                    |   |

|      | 12.5.1   | Instruction Cache Efficiency Mode                                         |   |

|      | 12.5.2   | Data Cache Efficiency Mode                                                | 8 |

|       | 12.5.3     |             | Fetch Latency Mode            |    |

|-------|------------|-------------|-------------------------------|----|

|       | 12.5.4     | Data/Bus F  | Request Buffer Full Mode      | 9  |

|       | 12.5.5     | Stall/Write | back Statistics               | 9  |

|       | 12.5.6     | Instruction | TLB Efficiency Mode           | 10 |

|       | 12.5.7     | Data TLB I  | Efficiency Mode               | 10 |

| 12.6  | Multiple I |             | Monitoring Run Statistics     |    |

| 12.7  |            |             |                               |    |

| 13    | •          |             | ebug                          |    |

|       |            |             | <u> </u>                      |    |

| 13.1  |            |             |                               |    |

| 13.2  |            |             |                               |    |

| 13.3  |            |             |                               |    |

|       | 13.3.1     |             |                               |    |

|       | 13.3.2     |             | ode                           |    |

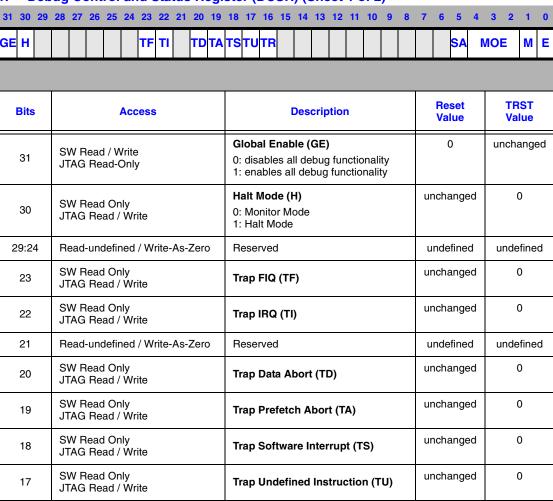

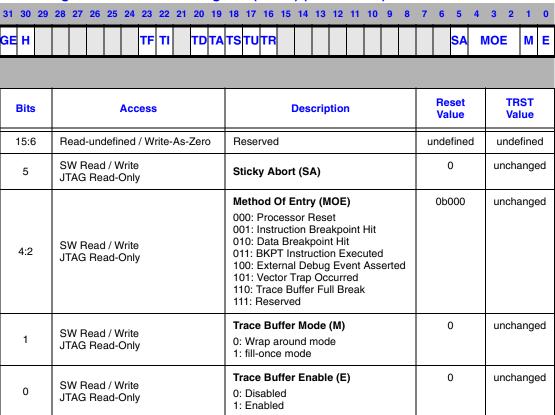

| 13.4  |            |             | tatus Register (DCSR)         |    |

|       | 13.4.1     |             | able Bit (GE)                 |    |

|       | 13.4.2     |             | Bit (H)                       |    |

|       | 13.4.3     |             | p Bits (TF,TI,TD,TA,TS,TU,TR) |    |

|       | 13.4.4     |             | rt Bit (SA)                   |    |

|       | 13.4.5     | Method of   | Entry Bits (MOE)              | 5  |

|       | 13.4.6     | Trace Buff  | er Mode Bit (M)               | 5  |

|       | 13.4.7     |             | er Enable Bit (E)             |    |

| 13.5  | Debug E    | xceptions   |                               | 6  |

|       | 13.5.1     | Halt Mode   |                               | 6  |

|       | 13.5.2     | Monitor Mo  | ode                           | 8  |

| 13.6  | HW Brea    | kpoint Reso | urces                         | 9  |

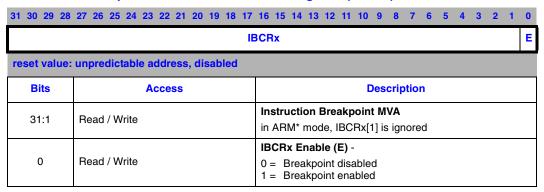

|       | 13.6.1     | Instruction | Breakpoints                   | 9  |

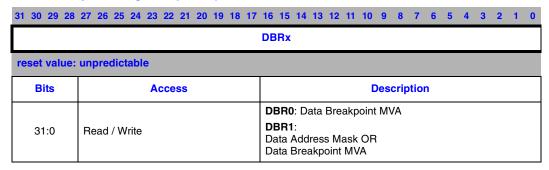

|       | 13.6.2     |             | rpoints                       |    |

| 13.7  | Software   | Breakpoints |                               | 11 |

| 13.8  | Transmit   | Receive Co  | ntrol Register (TXRXCTRL)     | 12 |

|       | 13.8.1     |             | er Ready Bit (RR)             |    |

|       | 13.8.2     |             | lag (OV)                      |    |

|       | 13.8.3     |             | Flag (D)                      |    |

|       | 13.8.4     |             | er Ready Bit (TR)             |    |

|       | 13.8.5     |             | I Execution Using TXRXCTRL    |    |

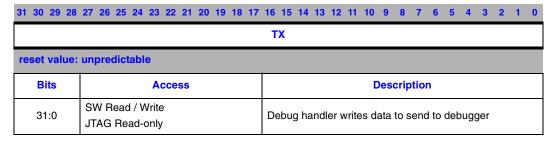

| 13.9  | Transmit   |             | <)                            |    |

| 13.10 |            | •           | ()                            |    |

| 13.11 |            | •           | ,                             |    |

|       | 13.11.1    |             | JTAG Command                  |    |

|       | 13.11.2    |             | JTAG Register                 |    |

|       | _          | 3.11.2.1    | DBG.HLD RST                   |    |

|       |            | 3.11.2.2    | DBG.BRK                       |    |

|       |            | 3.11.2.3    | DBG.DCSR                      |    |

|       | 13.11.3    |             | AG Command                    |    |

|       | 13.11.4    |             | AG Register                   |    |

|       | 13.11.5    |             | AG Command                    |    |

|       | 13.11.6    |             | AG Register                   |    |

|       |            | 3.11.6.1    | RX Write Logic                |    |

|       |            | 3.11.6.2    | DBGRX Data Register           |    |

|       |            | 3.11.6.3    | DBG.RR                        |    |

|       |            |             |                               |    |

|       | 13.11.6.4         | DBG.V                                    |    |

|-------|-------------------|------------------------------------------|----|

|       | 13.11.6.5         | DBG.RX                                   |    |

|       | 13.11.6.6         | DBG.D                                    |    |

|       | 13.11.6.7         | DBG.FLUSH                                |    |

|       |                   | ΓAG Data Register Reset Values           |    |

| 13.12 |                   |                                          |    |

|       |                   | ffer CP Registers                        |    |

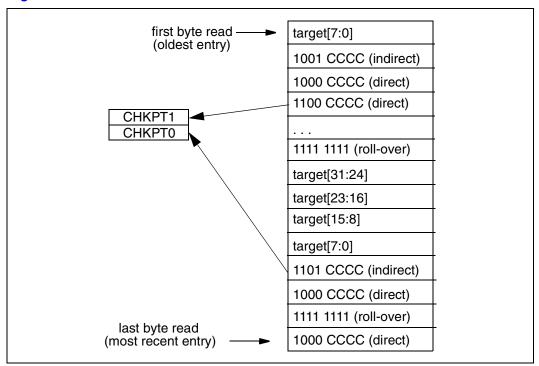

|       | 13.12.1.1         | Checkpoint Registers                     |    |

|       | 13.12.1.2         | Trace Buffer Register (TBREG)            |    |

| 13.13 |                   | S                                        |    |

|       | _                 | Byte                                     |    |

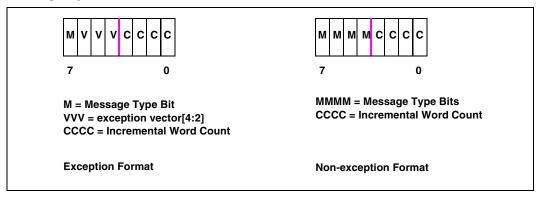

|       | 13.13.1.1         | Exception Message Byte                   |    |

|       | 13.13.1.2         | Non-exception Message Byte               |    |

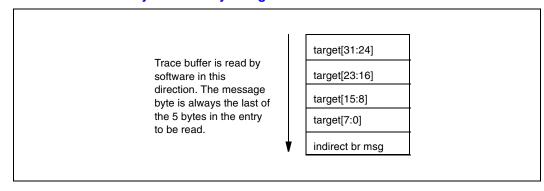

|       | 13.13.1.3         | Address Bytes                            |    |

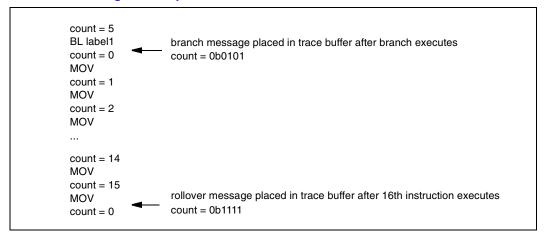

|       |                   | ffer Usage                               |    |

| 13.14 |                   | in the ICache                            |    |

|       |                   | AG Command                               |    |

|       |                   | AG Data Register                         |    |

|       |                   | che Functions                            |    |

|       | •                 | IC During Reset                          |    |

|       | 13.14.4.1         | Loading IC During Cold Reset for Debug   |    |

|       | 13.14.4.2         | Loading IC During a Warm Reset for Debug |    |

|       |                   | ally Loading IC After Reset              |    |

|       | 13.14.5.1         | Dynamic Code Download Synchronization    |    |

|       |                   | ruction Cache Overview                   |    |

| 13.15 |                   | Protocol                                 |    |

|       |                   | a Debug Session                          |    |

|       | 13.15.1.1         | Setting up Override Vector Tables        |    |

|       | 13.15.1.2         | Placing the Handler in Memory            |    |

|       | •                 | nting a Debug Handler                    |    |

|       | 13.15.2.1         | Debug Handler Entry                      |    |

|       | 13.15.2.2         | Debug Handler Restrictions               |    |

|       | 13.15.2.3         | Dynamic Debug Handler                    |    |

|       | 13.15.2.4         | High-Speed Download                      |    |

|       |                   | Debug Session                            |    |

| 13.16 | Software Debug No | tes/Errata                               | 54 |

| 14    | Performan         | ce Considerations                        |    |

| = =   |                   |                                          |    |

| 14.1  |                   |                                          |    |

| 14.2  |                   |                                          |    |

| 14.3  |                   |                                          |    |

| 14.4  |                   | S                                        |    |

|       |                   | ince Terms                               |    |

|       |                   | nstruction Timings                       |    |

|       |                   | cessing Instruction Timings              |    |

|       |                   | nstruction Timings                       |    |

|       |                   | d Arithmetic Instructions                |    |

|       |                   | egister Access Instructions              |    |

|       |                   | re Instructions                          |    |

|       | •                 | ore Instructions                         |    |

|       | 14.4.9 Coproces   | ssor Instructions                        | 9  |

|     | 14.4.10<br>14.4.11 | <b>9</b>                                                     |    |

|-----|--------------------|--------------------------------------------------------------|----|

| A   | (                  | Compatibility: Intel <sup>®</sup> 80200 Processor vs. SA-110 | 1  |

| A.1 |                    | ction                                                        |    |

| A.2 |                    | ary                                                          |    |

| A.3 |                    | cture Deviations                                             |    |

| •   | A.3.1              | Read Buffer                                                  |    |

|     | A.3.2              | 26-bit Mode                                                  |    |

|     | A.3.3              | Cacheable (C) and Bufferable (B) Encoding                    |    |

|     | A.3.4              | Write Buffer Behavior                                        |    |

|     | A.3.5              | External Aborts                                              |    |

|     | A.3.6              | Performance Differences                                      |    |

|     | A.3.7              | System Control Coprocessor                                   |    |

|     | A.3.8              | New Instructions and Instruction Formats                     |    |

|     | A.3.9              | Augmented Page Table Descriptors                             |    |

|     |                    | ·                                                            |    |

| В   |                    | Optimization Guide                                           |    |

| B.1 | Introdu            | ction                                                        |    |

|     | B.1.1              | About This Guide                                             |    |

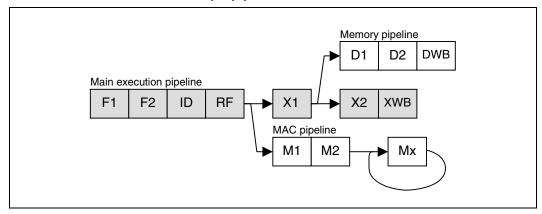

| B.2 | Intel® 8           | 0200 Processor Pipeline                                      |    |

|     | B.2.1              | General Pipeline Characteristics                             |    |

|     |                    | B.2.1.1. Number of Pipeline Stages                           |    |

|     |                    | B.2.1.2. Intel® 80200 Processor Pipeline Organization        |    |

|     |                    | B.2.1.3. Out Of Order Completion                             |    |

|     |                    | B.2.1.4. Register Scoreboarding                              |    |

|     | B.2.2              | B.2.1.5. Use of Bypassing                                    |    |

|     | D.Z.Z              | Instruction Flow Through the Pipeline                        |    |

|     |                    | B.2.2.2. Pipeline Stalls                                     |    |

|     | B.2.3              | Main Execution Pipeline                                      |    |

|     | D.Z.0              | B.2.3.1. F1 / F2 (Instruction Fetch) Pipestages              |    |

|     |                    | B.2.3.2. ID (Instruction Decode) Pipestage                   |    |

|     |                    | B.2.3.3. RF (Register File / Shifter) Pipestage              |    |

|     |                    | B.2.3.4. X1 (Execute) Pipestage                              |    |

|     |                    | B.2.3.5. X2 (Execute 2) Pipestage                            |    |

|     |                    | B.2.3.6. WB (write-back)                                     | 7  |

|     | B.2.4              | Memory Pipeline                                              |    |

|     |                    | B.2.4.1. D1 and D2 Pipestage                                 | 8  |

|     | B.2.5              | Multiply/Multiply Accumulate (MAC) Pipeline                  | 8  |

|     |                    | B.2.5.1. Behavioral Description                              | 8  |

| B.3 | Basic C            | Optimizations                                                |    |

|     | B.3.1              | Conditional Instructions                                     | 9  |

|     |                    | B.3.1.1. Optimizing Condition Checks                         | 9  |

|     |                    | B.3.1.2. Optimizing Branches                                 | 10 |

|     |                    | B.3.1.3. Optimizing Complex Expressions                      |    |

|     | B.3.2              | Bit Field Manipulation                                       |    |

|     | B.3.3              | Optimizing the Use of Immediate Values                       |    |

|     | B.3.4              | Optimizing Integer Multiply and Divide                       |    |

|     | B.3.5              | Effective Use of Addressing Modes                            |    |

| B.4 | Cache              | and Prefetch Optimizations                                   | 17 |

|     | B.4.1       | Instruction Cache                                             | 17 |

|-----|-------------|---------------------------------------------------------------|----|

|     |             | B.4.1.1. Cache Miss Cost                                      | 17 |

|     |             | B.4.1.2. Round Robin Replacement Cache Policy                 | 17 |

|     |             | B.4.1.3. Code Placement to Reduce Cache Misses                |    |

|     |             | B.4.1.4. Locking Code into the Instruction Cache              |    |

|     | B.4.2       | Data and Mini Cache                                           |    |

|     | D. 1.L      | B.4.2.1. Non Cacheable Regions                                |    |

|     |             | B.4.2.2. Write-through and Write-back Cached Memory Regions   |    |

|     |             | B.4.2.3. Read Allocate and Read-write Allocate Memory Regions |    |

|     |             | B.4.2.4. Creating On-chip RAM                                 |    |

|     |             | B.4.2.5. Mini-data Cache                                      |    |

|     |             | B.4.2.6. Data Alignment                                       |    |

|     |             | B.4.2.7. Literal Pools                                        |    |

|     | D 4 0       |                                                               |    |

|     | B.4.3       | Cache Considerations                                          |    |

|     |             | B.4.3.1. Cache Conflicts, Pollution and Pressure              |    |

|     |             | B.4.3.2. Memory Page Thrashing                                |    |

|     | B.4.4       | Prefetch Considerations                                       | 25 |

|     |             | B.4.4.1. Prefetch Distances in the Intel® 80200 Processor     |    |

|     |             | B.4.4.2. Prefetch Loop Scheduling                             |    |

|     |             | B.4.4.3. Prefetch Loop Limitations                            |    |

|     |             | B.4.4.4. Compute vs. Data Bus Bound                           |    |

|     |             | B.4.4.5. Low Number of Iterations                             |    |

|     |             | B.4.4.6. Bandwidth Limitations                                |    |

|     |             | B.4.4.7. Cache Memory Considerations                          |    |

|     |             | B.4.4.8. Cache Blocking                                       |    |

|     |             | B.4.4.9. Prefetch Unrolling                                   |    |

|     |             | B.4.4.10.Pointer Prefetch                                     |    |

|     |             | B.4.4.11.Loop Interchange                                     | 33 |

|     |             | B.4.4.12.Loop Fusion                                          |    |

|     |             | B.4.4.13.Prefetch to Reduce Register Pressure                 |    |

| B.5 | Instruc     | tion Scheduling                                               | 35 |

|     | B.5.1       | Scheduling Loads                                              |    |

|     |             | B.5.1.1. Scheduling Load and Store Double (LDRD/STRD)         |    |

|     |             | B.5.1.2. Scheduling Load and Store Multiple (LDM/STM)         |    |

|     | B.5.2       | Scheduling Data Processing Instructions                       |    |

|     | B.5.3       | Scheduling Multiply Instructions                              |    |

|     | B.5.4       | Scheduling SWP and SWPB Instructions                          |    |

|     |             |                                                               |    |

|     | B.5.5       | Scheduling the MRA and MAR Instructions (MRRC/MCRR)           |    |

|     | B.5.6       | Scheduling the MIA and MIAPH Instructions                     |    |

|     | B.5.7       | Scheduling MRS and MSR Instructions                           |    |

|     | B.5.8       | Scheduling CP15 Coprocessor Instructions                      | 44 |

| B.6 | Optimi      | zing C Libraries                                              | 45 |

| B.7 | Optimi      | zations for Size                                              | 45 |

|     | ь.<br>В.7.1 | Space/Performance Trade Off                                   | 45 |

|     |             | B.7.1.1. Multiple Word Load and Store                         |    |

|     |             | B.7.1.2. Use of Conditional Instructions                      |    |

|     |             | B.7.1.3. Use of PLD Instructions                              |    |

|     |             |                                                               |    |

| С   |             | Test Features                                                 | 1  |

| C.1 | Introdu     | uction                                                        | 4  |

| C.2 |             | - IEEE1149.1                                                  |    |

| 0.2 |             |                                                               |    |

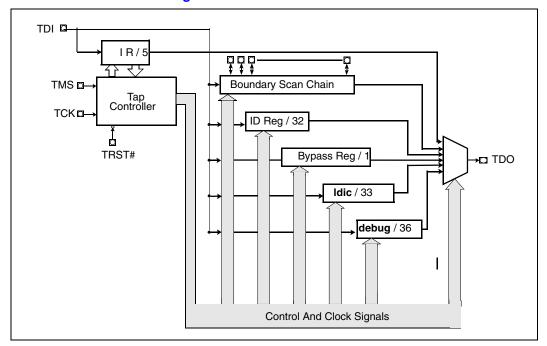

|     | C.2.1       | Boundary Scan Architecture                                    | 2  |

| C.2.2 | TAP Pins                                | 3  |

|-------|-----------------------------------------|----|

| C.2.3 | Instruction Register (IR)               |    |

|       | C.2.3.1. Boundary-Scan Instruction Set  |    |

| C.2.4 | TAP Test Data Registers                 |    |

|       | C.2.4.1. Device Identification Register |    |

|       | C.2.4.2. Bypass Register                |    |

|       | C.2.4.3. Boundary-Scan Register         | 6  |

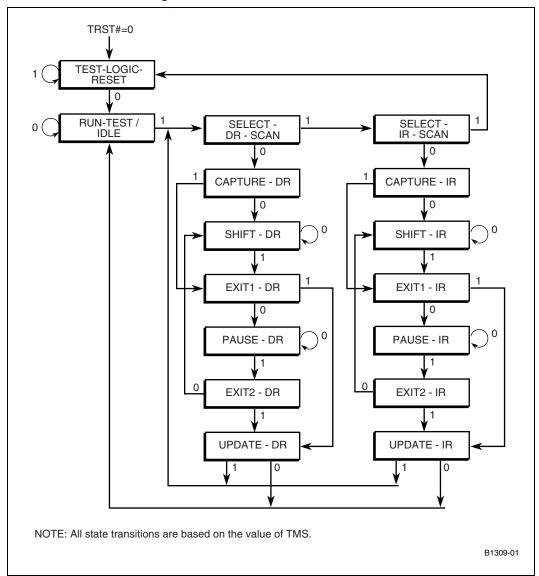

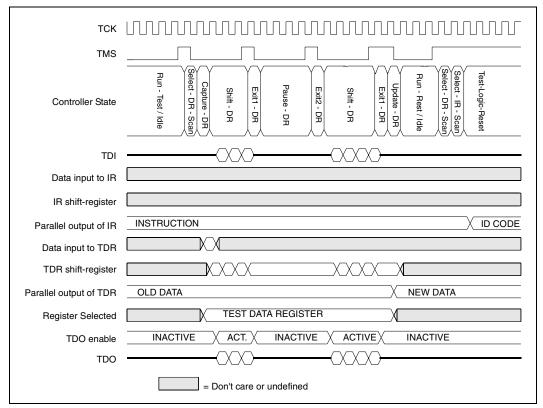

| C.2.5 | TAP Controller                          | 7  |

|       | C.2.5.1. Test Logic Reset State         | 8  |

|       | C.2.5.2. Run-Test/Idle State            | 8  |

|       | C.2.5.3. Select-DR-Scan State           | 8  |

|       | C.2.5.4. Capture-DR State               |    |

|       | C.2.5.5. Shift-DR State                 |    |

|       | C.2.5.6. Exit1-DR State                 | 9  |

|       | C.2.5.7. Pause-DR State                 | 9  |

|       | C.2.5.8. Exit2-DR State                 | 9  |

|       | C.2.5.9. Update-DR State                |    |

|       | C.2.5.10.Select-IR Scan State           | 10 |

|       | C.2.5.11.Capture-IR State               | 10 |

|       | C.2.5.12.Shift-IR State                 |    |

|       | C.2.5.13.Exit1-IR State                 |    |

|       | C.2.5.14.Pause-IR State                 |    |

|       | C.2.5.15.Exit2-IR State                 |    |

|       | C.2.5.16.Update-IR State                |    |

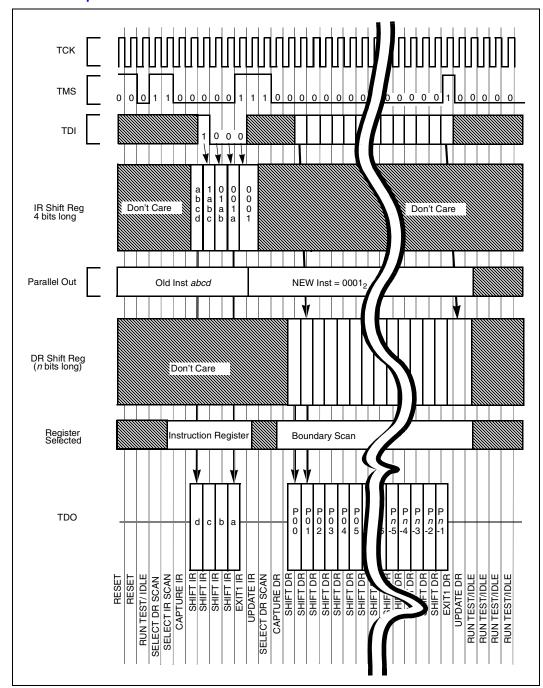

|       | C.2.5.17.Boundary-Scan Example          | 12 |

## **Figures**

| 1-1   | Intel <sup>®</sup> 80200 Processor based on Intel <sup>®</sup> XScale <sup>™</sup> Microarchitecture Features |    |

|-------|---------------------------------------------------------------------------------------------------------------|----|

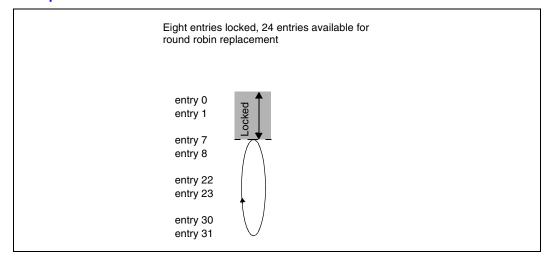

| 3-1   | Example of Locked Entries in TLB                                                                              | 9  |

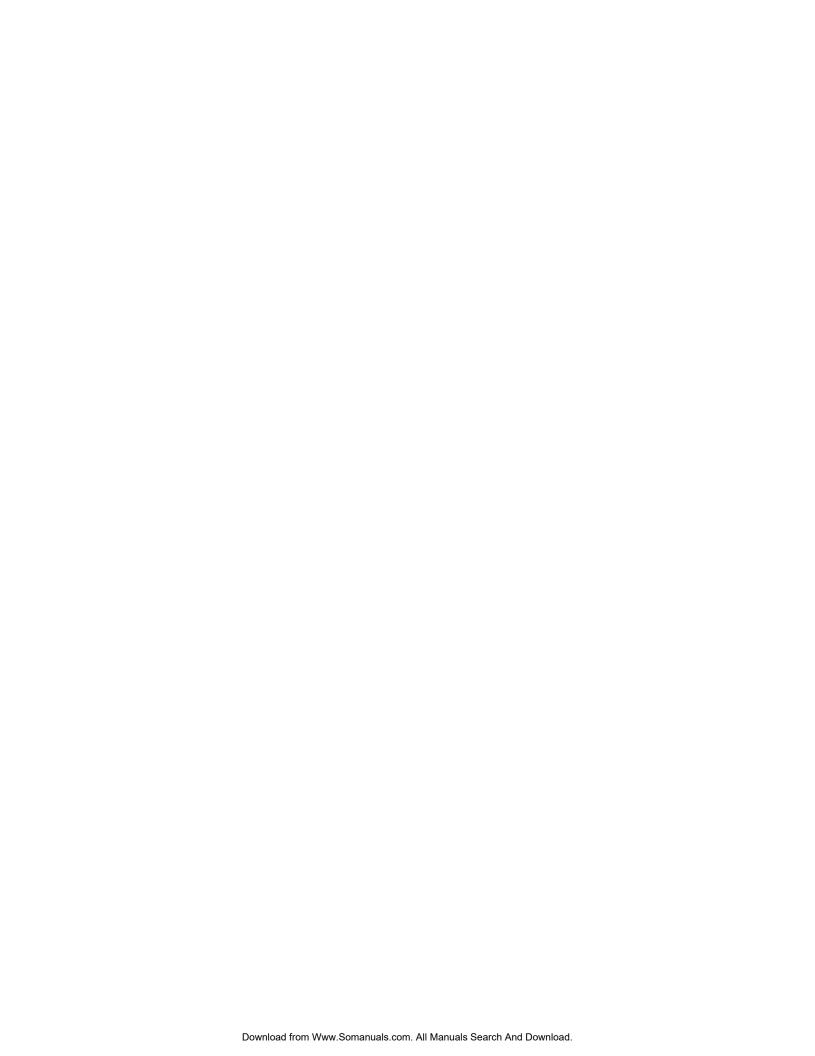

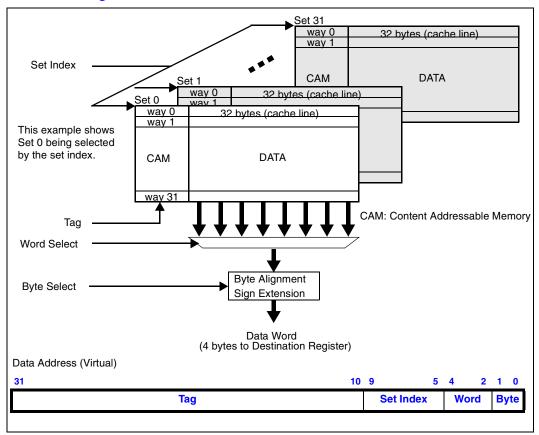

| 4-1   | Instruction Cache Organization                                                                                |    |

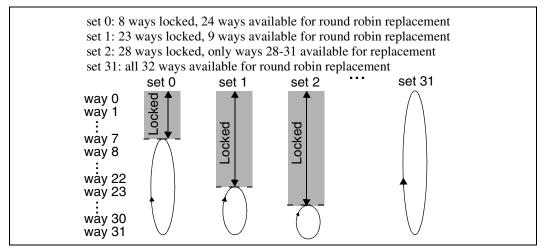

| 4-2   | Locked Line Effect on Round Robin Replacement                                                                 |    |

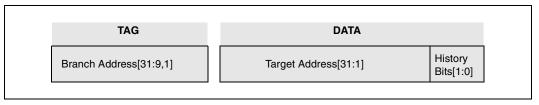

| 5-1   | BTB Entry                                                                                                     |    |

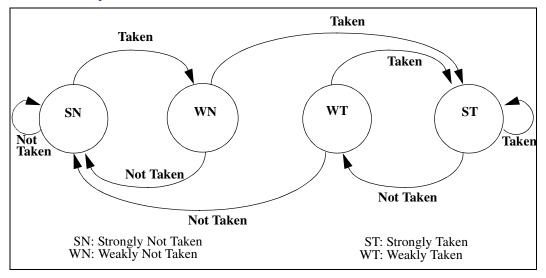

| 5-2   | Branch History                                                                                                | 2  |

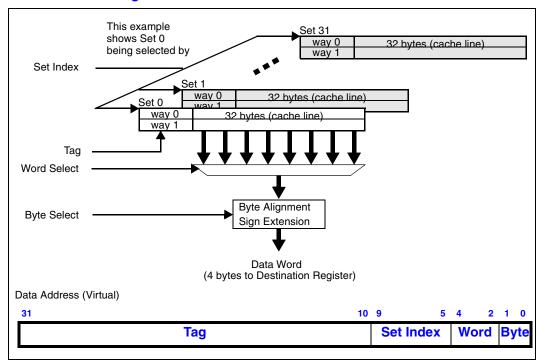

| 6-1   | Data Cache Organization                                                                                       |    |

| 6-2   | Mini-Data Cache Organization                                                                                  |    |

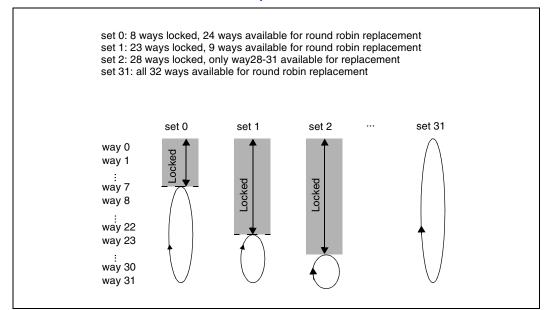

| 6-3   | Locked Line Effect on Round Robin Replacement                                                                 |    |

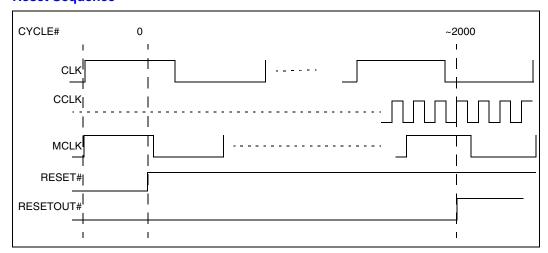

| 8-1   | Reset Sequence                                                                                                | 3  |

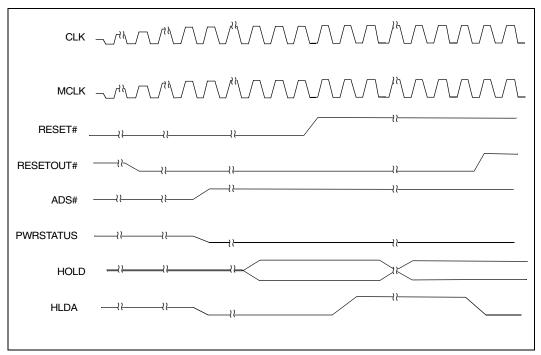

| 8-2   | Pin State at Reset                                                                                            | 4  |

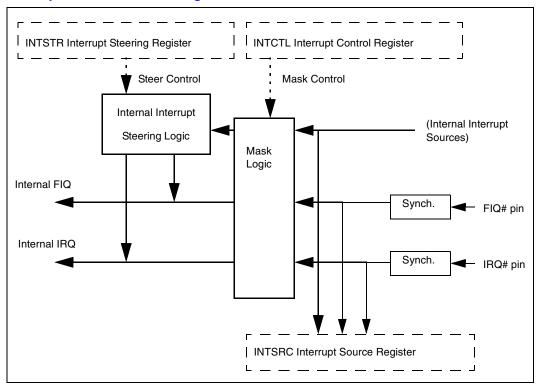

| 9-1   | Interrupt Controller Block Diagram                                                                            | 2  |

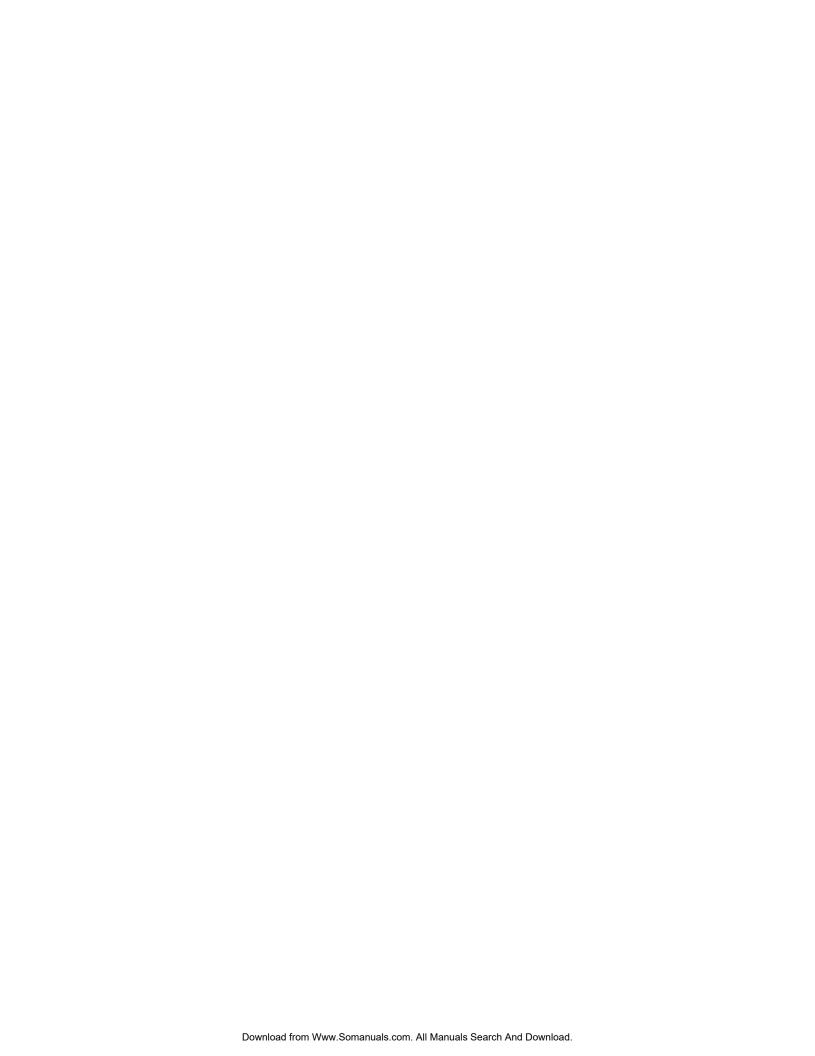

| 10-1  | Typical System                                                                                                | 1  |

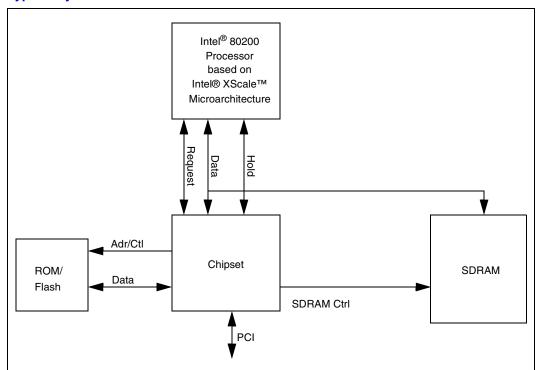

| 10-2  | Alternate Configuration                                                                                       | 2  |

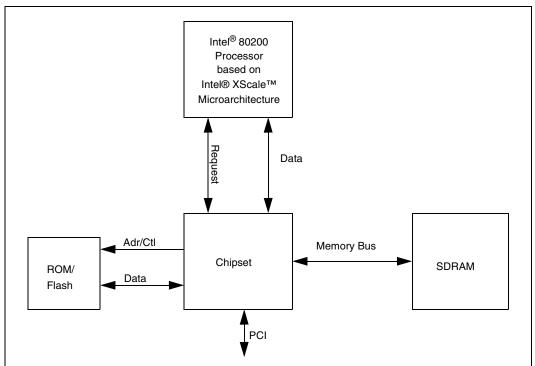

| 10-3  | Big Endian Lane Swapping on a 64-bit Bus                                                                      | 13 |

| 10-4  | Basic Read Timing                                                                                             | 14 |

| 10-5  | Read Burst, No CWF                                                                                            | 15 |

| 10-6  | Read Burst, CWF                                                                                               | 16 |

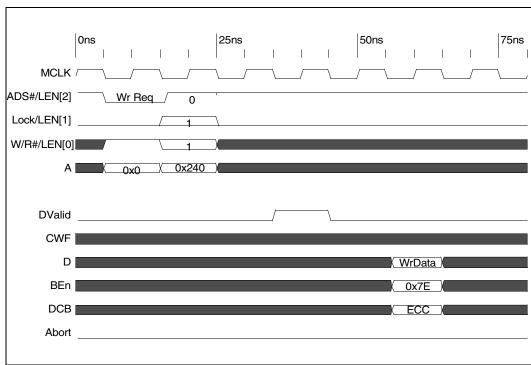

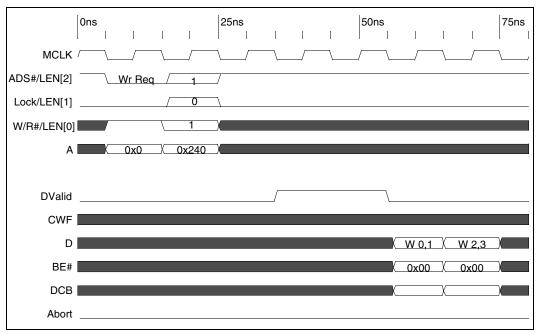

| 10-7  | Basic Word Write                                                                                              | 17 |

| 10-8  | Two Word Coalesced Write                                                                                      | 18 |

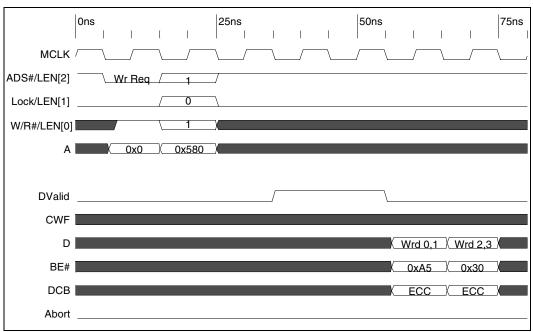

| 10-9  | Four Word Eviction Write                                                                                      | 19 |

| 10-10 | Four Word Coalesced Write Burst                                                                               | 20 |

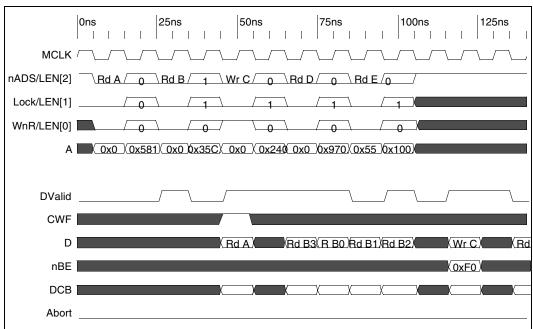

| 10-11 | Pipeline Example                                                                                              | 21 |

| 10-12 | Locked Access                                                                                                 | 22 |

| 10-13 | Aborted Access                                                                                                | 23 |

| 10-14 | Hold Assertion                                                                                                | 24 |

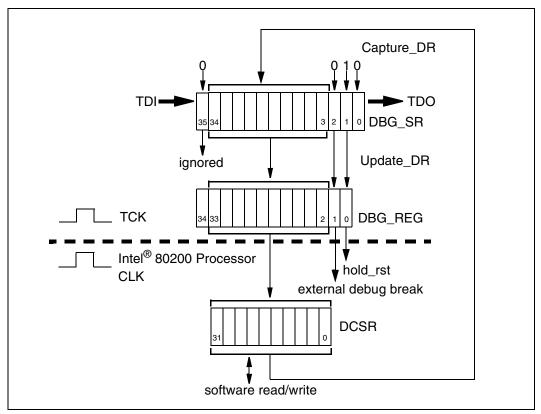

| 13-1  | SELDCSR Hardware                                                                                              | 18 |

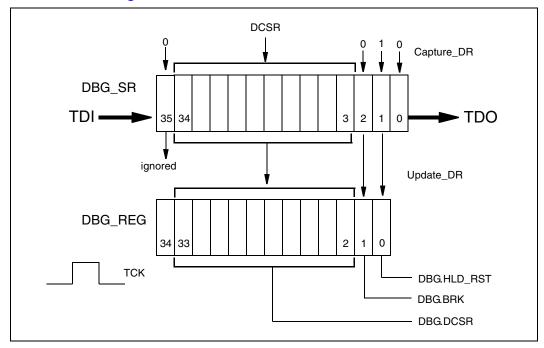

| 13-2  | SELDCSR Data Register                                                                                         | 19 |

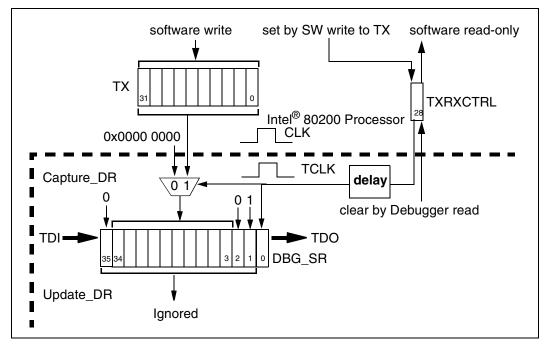

| 13-3  | DBGTX Hardware                                                                                                | 21 |

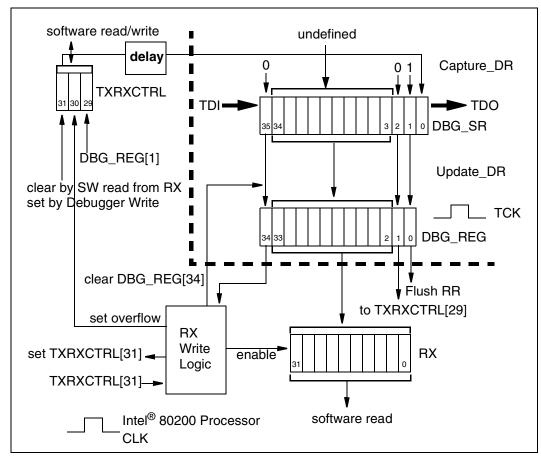

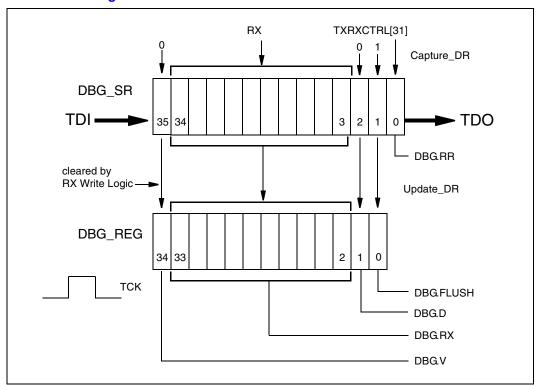

| 13-4  | DBGRX Hardware                                                                                                | 22 |

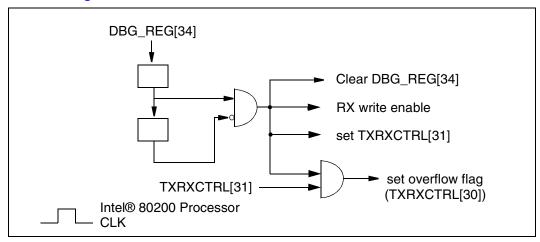

| 13-5  | RX Write Logic                                                                                                | 23 |

| 13-6  | DBGRX Data Register                                                                                           | 24 |

| 13-7  | Message Byte Formats                                                                                          | 28 |

| 13-8  | Indirect Branch Entry Address Byte Organization                                                               |    |

| 13-9  | High Level View of Trace Buffer                                                                               | 32 |

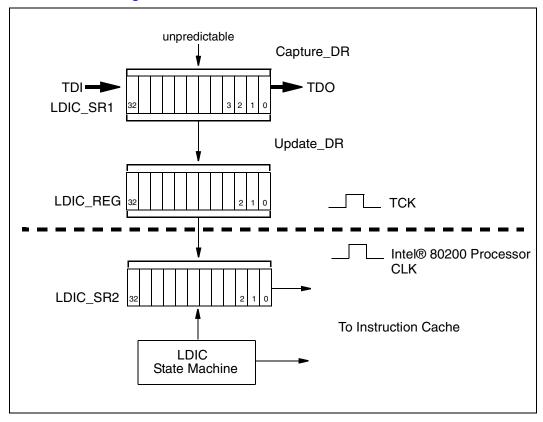

| 13-10 | LDIC JTAG Data Register Hardware                                                                              | 35 |

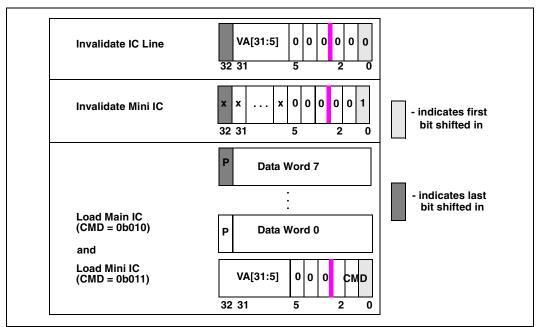

| 13-11 | Format of LDIC Cache Functions                                                                                | 37 |

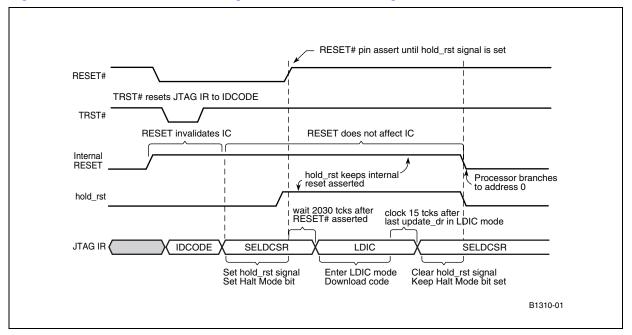

| 13-12 | Code Download During a Cold Reset For Debug                                                                   | 39 |

| 13-13 | Code Download During a Warm Reset For Debug                                                                   | 41 |

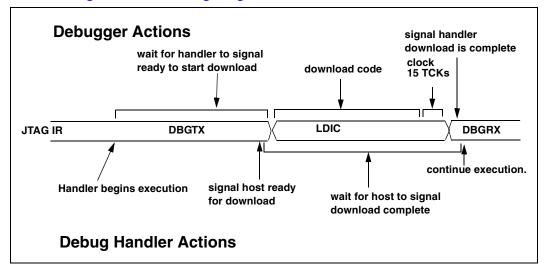

| 13-14 | Downloading Code in IC During Program Execution                                                               |    |

| B-1   | Intel® 80200 Processor RISC Superpipeline                                                                     | 3  |

| C-1   | Test Access Port Block Diagram                                                                                | 2  |

| C-2   | TAP Controller State Diagram                                                                                  | 7  |

| C-3   | JTAG Example                                                                                                  |    |

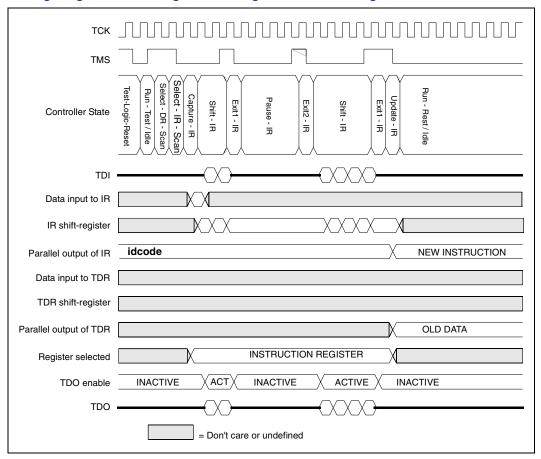

| C-4   | Timing Diagram Illustrating the Loading of Instruction Register                                               | 14 |

| C-5   | Timing Diagram Illustrating the Loading of Data Register                                                      | 15 |

## **Tables**

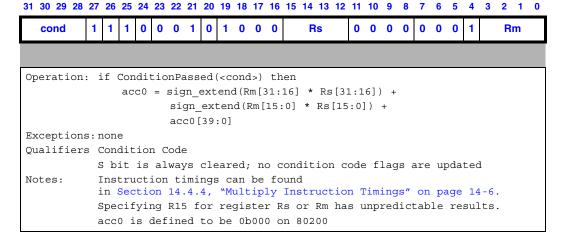

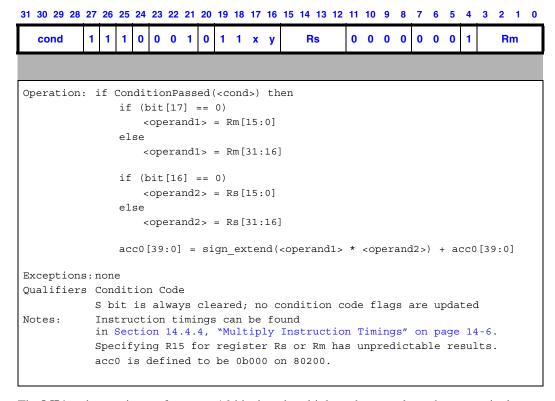

| 2-1  | Multiply with Internal Accumulate Format                            | 4  |

|------|---------------------------------------------------------------------|----|

| 2-2  | MIA{ <cond>} acc0, Rm, Rs</cond>                                    | 4  |

| 2-3  | MIAPH{ <cond>} acc0, Rm, Rs</cond>                                  | 5  |

| 2-4  | MIAxy{ <cond>} acc0, Rm, Rs</cond>                                  | 6  |

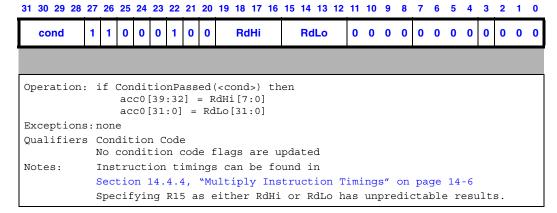

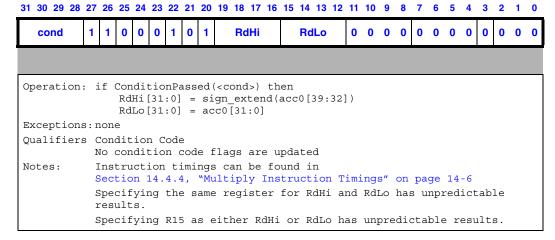

| 2-5  | Internal Accumulator Access Format                                  | 7  |

| 2-6  | MAR{ <cond>} acc0, RdLo, RdHi</cond>                                | 8  |

| 2-7  | MRA{ <cond>} RdLo, RdHi, acc0</cond>                                | 8  |

| 2-9  | Second-level Descriptors for Coarse Page Table                      |    |

| 2-10 | Second-level Descriptors for Fine Page Table                        | 10 |

| 2-8  | First-level Descriptors                                             | 10 |

| 2-11 | Exception Summary                                                   | 12 |

| 2-12 | Event Priority                                                      | 12 |

| 2-13 | Intel® 80200 Processor Encoding of Fault Status for Prefetch Aborts | 13 |

| 2-14 | Intel® 80200 Processor Encoding of Fault Status for Data Aborts     | 14 |

| 3-1  | Data Cache and Buffer Behavior when $X = 0$                         |    |

| 3-2  | Data Cache and Buffer Behavior when X = 1                           | 3  |

| 3-3  | Memory Operations that Impose a Fence                               |    |

| 3-4  | Valid MMU & Data/mini-data Cache Combinations                       |    |

| 7-1  | MRC/MCR Format                                                      | 2  |

| 7-2  | LDC/STC Format                                                      | 3  |

| 7-3  | CP15 Registers                                                      | 4  |

| 7-4  | ID Register                                                         | 5  |

| 7-5  | Cache Type Register                                                 |    |

| 7-6  | ARM* Control Register                                               |    |

| 7-7  | Auxiliary Control Register                                          |    |

| 7-8  | Translation Table Base Register                                     | 9  |

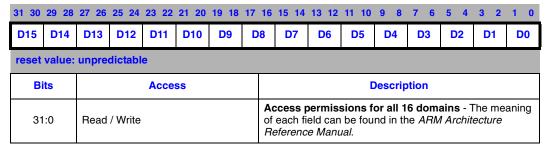

| 7-9  | Domain Access Control Register                                      | 9  |

| 7-10 | Fault Status Register                                               | 10 |

| 7-11 | Fault Address Register                                              | 10 |

| 7-12 | Cache Functions                                                     | 11 |

| 7-13 | TLB Functions                                                       | 13 |

| 7-14 | Cache Lockdown Functions                                            | 14 |

| 7-15 | Data Cache Lock Register                                            | 14 |

| 7-16 | TLB Lockdown Functions                                              | 15 |

| 7-17 | Accessing Process ID                                                | 16 |

| 7-18 | Process ID Register                                                 | 16 |

| 7-19 | Accessing the Debug Registers                                       | 17 |

| 7-20 | Coprocessor Access Register                                         | 19 |

| 7-21 | CP14 Registers                                                      |    |

| 7-22 | Accessing the Performance Monitoring Registers                      | 20 |

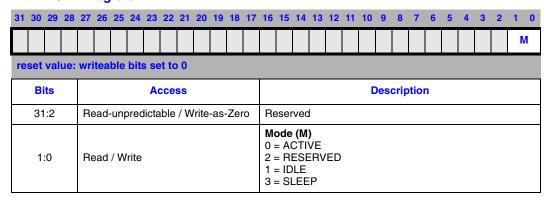

| 7-23 | PWRMODE Register                                                    | 21 |

| 7-24 | Clock and Power Management                                          |    |

| 7-25 | CCLKCFG Register                                                    | 21 |

| 7-26 | Accessing the Debug Registers                                       |    |

| 8-1  | Reset CCLK Configuration                                            | 1  |

| 8-2  | Software CCLK Configuration                                         |    |

| 8-3  | Low Power Modes                                                     | 5  |

| 8-4  | PWRSTATUS[1:0] Encoding                                             |    |

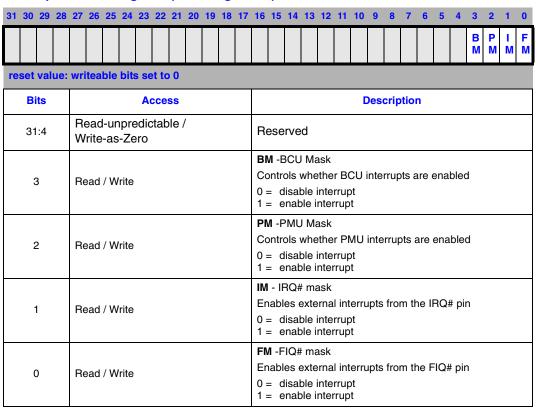

| 9-1   | Interrupt Control Register (CP13 register 0)                                                                     |    |

|-------|------------------------------------------------------------------------------------------------------------------|----|

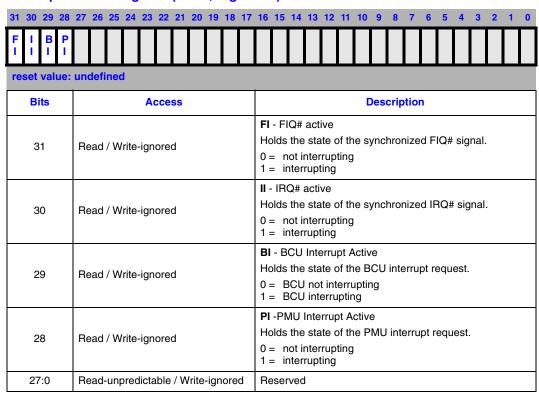

| 9-2   | Interrupt Source Register (CP13, register 4)                                                                     |    |

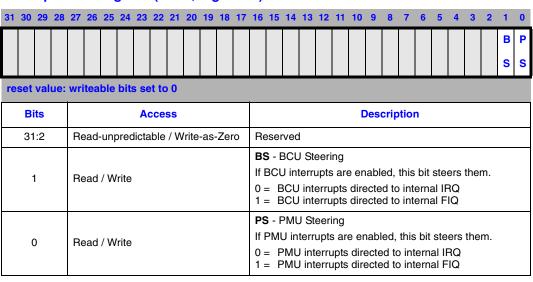

| 9-3   | Interrupt Steer Register (CP13, register 8)                                                                      | 5  |

| 10-1  | Intel <sup>®</sup> 80200 Processor based on Intel <sup>®</sup> XScale <sup>™</sup> Microarchitecture Bus Signals |    |

| 10-2  | Requests on a 64-bit Bus                                                                                         |    |

| 10-3  | Requests on a 32-bit Bus                                                                                         | 5  |

| 10-4  | Return Order for 8-Word Burst, 64-bit Data Bus                                                                   | 7  |

| 10-5  | Return Order for 8-Word Burst, 32-bit Data Bus                                                                   | 7  |

| 11-1  | BCU Response to ECC Errors                                                                                       | 3  |

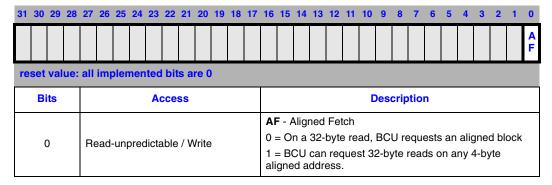

| 11-2  | BCUCTL (Register 0)                                                                                              | 5  |

| 11-3  | BCUMOD (Register 1)                                                                                              | 7  |

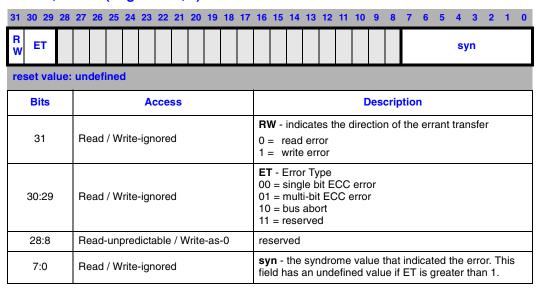

| 11-4  | ELOG0, ELOG1(Registers 4, 5)                                                                                     | 9  |

| 11-5  | ECAR0, ECAR1(Registers 6, 7)                                                                                     | 9  |

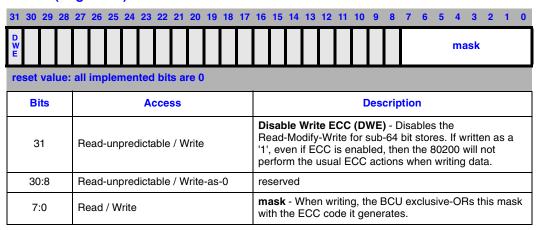

| 11-6  | ECTST (Register 8)                                                                                               |    |

| 12-1  | Clock Count Register (CCNT)                                                                                      | 2  |

| 12-2  | Performance Monitor Count Register (PMN0 and PMN1)                                                               | 3  |

| 12-3  | Performance Monitor Control Register (CP14, register 0)                                                          | 4  |

| 12-4  | Performance Monitoring Events                                                                                    | 6  |

| 12-5  | Some Common Uses of the PMU                                                                                      | 7  |

| 13-1  | Debug Control and Status Register (DCSR)                                                                         | 3  |

| 13-2  | Event Priority                                                                                                   |    |

| 13-3  | Instruction Breakpoint Address and Control Register (IBCRx)                                                      | 9  |

| 13-4  | Data Breakpoint Register (DBRx)                                                                                  | 10 |

| 13-5  | Data Breakpoint Controls Register (DBCON)                                                                        | 10 |

| 13-6  | TX RX Control Register (TXRXCTRL)                                                                                |    |

| 13-7  | Normal RX Handshaking                                                                                            | 13 |

| 13-8  | High-Speed Download Handshaking States                                                                           | 13 |

| 13-9  | TX Handshaking                                                                                                   | 15 |

| 13-10 | TXRXCTRL Mnemonic Extensions                                                                                     | 15 |

| 13-11 | TX Register                                                                                                      | 16 |

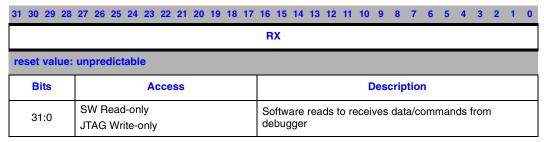

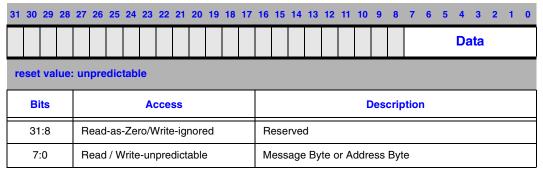

| 13-12 | RX Register                                                                                                      | 16 |

| 13-13 | DEBUG Data Register Reset Values                                                                                 | 25 |

| 13-14 | CP 14 Trace Buffer Register Summary                                                                              | 26 |

| 13-15 | Checkpoint Register (CHKPTx)                                                                                     | 26 |

| 13-16 | TBREG Format                                                                                                     | 27 |

| 13-17 | Message Byte Formats                                                                                             | 28 |

| 13-18 | LDIC Cache Functions                                                                                             | 36 |

| 14-1  | Minimum Interrupt Latency                                                                                        | 1  |

| 14-2  | Branch Latency Penalty                                                                                           | 2  |

| 14-3  | Latency Example                                                                                                  | 4  |

| 14-4  | Branch Instruction Timings (Those predicted by the BTB)                                                          | 4  |

| 14-5  | Branch Instruction Timings (Those not predicted by the BTB)                                                      | 5  |

| 14-6  | Data Processing Instruction Timings                                                                              | 5  |

| 14-7  | Multiply Instruction Timings                                                                                     |    |

| 14-8  | Multiply Implicit Accumulate Instruction Timings                                                                 |    |

| 14-9  | Implicit Accumulator Access Instruction Timings                                                                  |    |

| 14-10 | Saturated Data Processing Instruction Timings                                                                    |    |

| 14-11 | Status Register Access Instruction Timings                                                                       |    |

| 14-12 | Load and Store Instruction Timings                                                                               | 8  |

| 14-13 | Load and Store Multiple Instruction Timings                                                                      | 8  |

## Intel<sup>®</sup> 80200 Processor based on Intel<sup>®</sup> XScale<sup>™</sup> Microarchitecture

| 14-14 | Semaphore Instruction Timings            | 9 |

|-------|------------------------------------------|---|

| 14-15 | CP15 Register Access Instruction Timings | 9 |

| 14-16 | CP14 Register Access Instruction Timings | 9 |

| 14-17 | SWI Instruction Timings                  | 9 |

| 14-18 | Count Leading Zeros Instruction Timings  | 9 |

| A-1   | C and B encoding                         | 3 |

| B-1   | Pipelines and Pipe stages                | 3 |

| C-1   | TAP Controller Pin Definitions           | 3 |

| C-2   | JTAG Instruction Set                     | 4 |

| C-3   | IEEE Instructions.                       | 5 |

| C-4   | JTAG ID Register Value                   | 6 |

Introduction 1

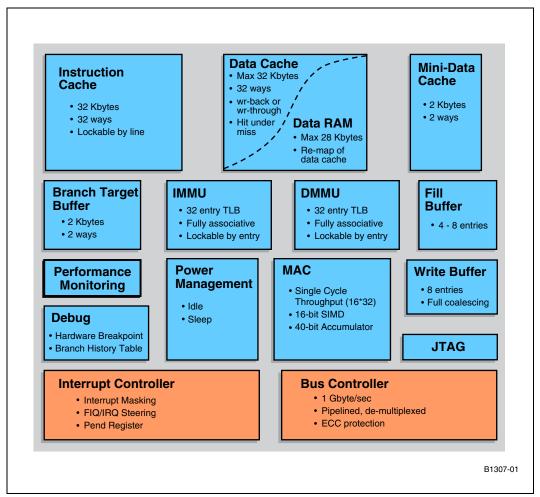

## 1.1 Intel<sup>®</sup> 80200 Processor based on Intel<sup>®</sup> XScale<sup>™</sup> Microarchitecture High-Level Overview

The Intel<sup>®</sup> 80200 processor based on Intel<sup>®</sup> XScale<sup>™</sup> microarchitecture, is the next generation in the Intel<sup>®</sup> StrongARM\* processor family (compliant with ARM\* Architecture V5TE). It is designed for high performance and low-power; leading the industry in mW/MIPs. The Intel<sup>®</sup> 80200 processor integrates a bus controller and an interrupt controller around a core processor, with intended embedded markets such as: handheld devices, networking, remote access servers, etc. This technology is ideal for internet infrastructure products such as network and I/O processors, where ultimate performance is critical for moving and processing large amounts of data quickly.

The Intel<sup>®</sup> 80200 processor incorporates an extensive list of architecture features that allows it to achieve high performance. This rich feature set allows programmers to select the appropriate features that obtains the best performance for their application. Many of the architectural features added to Intel<sup>®</sup> 80200 processor help hide memory latency which often is a serious impediment to high performance processors. This includes:

- the ability to continue instruction execution even while the data cache is retrieving data from external memory.

- a write buffer.

- write-back caching.

- various data cache allocation policies which can be configured different for each application.

- · cache locking.

- and a pipelined external bus.

All these features improve the efficiency of the external bus.

The Intel® 80200 processor has been equipped to efficiently handle audio processing through the support of 16-bit data types and 16-bit operations. These audio coding enhancements center around multiply and accumulate operations which accelerate many of the audio filter operations.

## 1.1.1 ARM\* Architecture Compliance

ARM\* Version 5 (V5) Architecture added floating point instructions to ARM\* Version 4. The Intel® 80200 processor implements the integer instruction set architecture of ARM V5, but does not provide hardware support of the floating point instructions.

The Intel® 80200 processor provides the Thumb\* instruction set (ARM\* V5T) and the ARM\* V5E DSP extensions.

Backward compatibility with the first generation of Intel<sup>®</sup> StrongARM\* products is maintained for user-mode applications. Operating systems may require modifications to match the specific hardware features of the Intel<sup>®</sup> 80200 processor and to take advantage of the performance enhancements added to the Intel<sup>®</sup> 80200 processor.

## 1.1.2 Features

Figure 1-1 shows the major functional blocks of the Intel<sup>®</sup> 80200 processor. The following sections give a brief, high-level overview of these blocks.

Figure 1-1. Intel<sup>®</sup> 80200 Processor based on Intel<sup>®</sup> XScale<sup>™</sup> Microarchitecture Features

## 1.1.2.1 Multiply/Accumulate (MAC)

The MAC unit supports early termination of multiplies/accumulates in two cycles and can sustain a throughput of a MAC operation every cycle. Several architectural enhancements were made to the MAC to support audio coding algorithms, which include a 40-bit accumulator and support for 16-bit packed data.

See Section 2.3, "Extensions to ARM\* Architecture" on page 2-3 for more details.

## 1.1.2.2 Memory Management

The Intel<sup>®</sup> 80200 processor implements the Memory Management Unit (MMU) Architecture specified in the *ARM Architecture Reference Manual*. The MMU provides access protection and virtual to physical address translation.

The MMU Architecture also specifies the caching policies for the instruction cache and data memory. These policies are specified as page attributes and include:

- identifying code as cacheable or non-cacheable

- selecting between the mini-data cache or data cache

- write-back or write-through data caching

- enabling data write allocation policy

- and enabling the write buffer to coalesce stores to external memory

Chapter 3, "Memory Management" discusses this in more detail.

### 1.1.2.3 Instruction Cache

The Intel<sup>®</sup> 80200 processor implements a 32-Kbyte, 32-way set associative instruction cache with a line size of 32 bytes. All requests that "miss" the instruction cache generate a 32-byte read request to external memory. A mechanism to lock critical code within the cache is also provided.

Chapter 4, "Instruction Cache" discusses this in more detail.

## 1.1.2.4 Branch Target Buffer

The Intel<sup>®</sup> 80200 processor provides a Branch Target Buffer (BTB) to predict the outcome of branch type instructions. It provides storage for the target address of branch type instructions and predicts the next address to present to the instruction cache when the current instruction address is that of a branch.

The BTB holds 128 entries. See Chapter 5, "Branch Target Buffer" for more details.

## 1.1.2.5 Data Cache

The Intel® 80200 processor implements a 32-Kbyte, a 32-way set associative data cache and a 2-Kbyte, 2-way set associative mini-data cache. Each cache has a line size of 32 bytes, supports write-through or write-back caching.

The data/mini-data cache is controlled by page attributes defined in the MMU Architecture and by coprocessor 15.

Chapter 6, "Data Cache" discusses all this in more detail.

The Intel® 80200 processor allows applications to re-configure a portion of the data cache as data RAM. Software may place special tables or frequently used variables in this RAM. See Section 6.4, "Re-configuring the Data Cache as Data RAM" on page 6-12 for more information on this.

## 1.1.2.6 Power Management

The Intel<sup>®</sup> 80200 processor supports two low power modes: idle and sleep. These modes are discussed in Section 8.3, "Power Management" on page 8-5.

## 1.1.2.7 Interrupt Controller

An interrupt controller is implemented on the Intel<sup>®</sup> 80200 processor that provides masking of interrupts and the ability to steer interrupts to FIQ or IRQ. It is accessed through Coprocessor 13 registers. See Chapter 9, "Interrupts" for more detail.

#### 1.1.2.8 Bus Controller

The Intel<sup>®</sup> 80200 processor supports a pipelined external bus that runs at 100 MHz. The data bus is 32/64 bits with ECC protection. The bus controller can be configured to provide critical word first on load operations, enhancing overall system performance. The bus controller has four request queues, where all four requests can be active on the pipelined external bus.

Chapter 10, "External Bus" describes the external bus protocol and Chapter 11, "Bus Controller" covers the aspects of ECC protection. The bus controller registers are accessed via coprocessor 13.

## 1.1.2.9 Performance Monitoring

Two performance monitoring counters have been added to the Intel<sup>®</sup> 80200 processor that can be configured to monitor various events in the Intel<sup>®</sup> 80200 processor. These events allow a software developer to measure cache efficiency, detect system bottlenecks and reduce the overall latency of programs.

Chapter 12, "Performance Monitoring" discusses this in more detail.

## 1.1.2.10 **Debug**

The Intel® 80200 processor supports software debugging through two instruction address breakpoint registers, one data-address breakpoint register, one data-address/mask breakpoint register, and a trace buffer.

Chapter 13, "Software Debug" discusses this in more detail.

#### 1.1.2.11 JTAG

Testability is supported on the Intel<sup>®</sup> 80200 processor through the Test Access Port (TAP) Controller implementation, which is based on IEEE 1149.1 (JTAG) Standard Test Access Port and Boundary-Scan Architecture. The purpose of the TAP controller is to support test logic internal and external to the Intel<sup>®</sup> 80200 processor such as built-in self-test, boundary-scan, and scan.

Appendix C.2 discusses this in more detail.

## 1.2 Terminology and Conventions

## 1.2.1 Number Representation

All numbers in this document can be assumed to be base 10 unless designated otherwise. In text and pseudo code descriptions, hexadecimal numbers have a prefix of 0x and binary numbers have a prefix of 0b. For example, 107 would be represented as 0x6B in hexadecimal and 0b1101011 in binary.

## 1.2.2 Terminology and Acronyms

ASSP Application Specific Standard Product

Assert This term refers to the logically active value of a signal or bit.

BTB Branch Target Buffer

Clean A clean operation updates external memory with the contents of the specified line in

the data/mini-data cache if any of the dirty bits are set and the line is valid. There are two dirty bits associated with each line in the cache so only the portion that is dirty

gets written back to external memory.

After this operation, the line is still valid and both dirty bits are deasserted.

Coalescing Coalescing means bringing together a new store operation with an existing store

operation already resident in the write buffer. The new store is placed in the same write buffer entry as an existing store when the address of the new store falls in the 4 word aligned address of the existing entry. This includes, in PCI terminology, write

merging, write collapsing, and write combining.

Deassert This term refers to the logically inactive value of a signal or bit.

Flush A flush operation invalidates the location(s) in the cache by deasserting the valid bit.

Individual entries (lines) may be flushed or the entire cache may be flushed with one command. Once an entry is flushed in the cache it can no longer be used by the

program.

Reserved A reserved field is a field that may be used by an implementation. If the initial value

of a reserved field is supplied by software, this value must be zero. Software should

not modify reserved fields or depend on any values in reserved fields.

## 1.3 Other Relevant Documents

- Intel<sup>®</sup> 80200 Processor based on Intel<sup>®</sup> XScale<sup>™</sup> Microarchitecture Datasheet, Intel Order # 273414

- ARM Architecture Version 5TE Specification Document Number: ARM DDI 0100E

This document describes Version 5TE of the ARM Architecture which includes Thumb ISA and ARM DSP-Enhanced ISA.

- *ARM Architecture Reference Manual* Document Number: ARM DDI 0100B This document describes Version 4 of the ARM Architecture.

- Intel® XScale<sup>™</sup> Microarchitecture Programming Reference Manual, Intel Order # 273436

- Intel® 80312 I/O Companion Chip Developer's Manual, Intel Order # 273410

- StrongARM SA-1100 Microprocessor Developer's Manual, Intel Order # 278088

- StrongARM SA-110 Microprocessor Technical Reference Manual, Intel Order #278058

## Programming Model

2

This chapter describes the programming model of the Intel<sup>®</sup> 80200 processor based on Intel<sup>®</sup> XScale microarchitecture, namely the implementation options and extensions to the ARM\* Version 5 architecture.

The ARM\* Architecture Version 5TE Specification (ARM DDI 0100E) describes Version 5TE of the ARM Architecture, including the Thumb\* ISA and ARM DSP-Enhanced ISA.

## 2.1 ARM\* Architecture Compliance

The Intel<sup>®</sup> 80200 processor implements the integer instruction set architecture specified in ARM\* Version 5TE. T refers to the Thumb instruction set and E refers to the DSP-Enhanced instruction set.

ARM\* Version 5 introduces a few more architecture features over Version 4, specifically the addition of tiny pages (1 Kbyte), a new instruction (**CLZ**) that counts the leading zeroes in a data value, enhanced ARM-Thumb transfer instructions and a modification of the system control coprocessor, CP15.

## 2.2 ARM\* Architecture Implementation Options

## 2.2.1 Big Endian versus Little Endian

The Intel<sup>®</sup> 80200 processor supports both big and little endian data representation. The B-bit of the Control Register (Coprocessor 15, register 1, bit 7) selects big and little endian mode. To run in big endian mode, the B bit must be set before attempting any sub-word accesses to memory, or undefined results occur. Note that this bit takes effect even if the MMU is disabled.

## 2.2.2 26-Bit Code

The Intel® 80200 processor does not support 26-bit code.

## 2.2.3 Thumb\*

The Intel® 80200 processor supports the Thumb instruction set.

## 2.2.4 ARM\* DSP-Enhanced Instruction Set

The Intel® 80200 processor implements ARM DSP-enhanced instruction set, which is a set of instructions that boost the performance of signal processing applications. There are new multiply instructions that operate on 16-bit data values and new saturation instructions. Some of the new instructions are:

32 < = 16x16 + 32• SMLAxy • SMLAWy  $32 <= 32 \times 16 + 32$  SMLALxy 64 <= 16x16 + 64• SMULxy 32<=16x16 SMULWy  $32 <= 32 \times 16$  QADD adds two registers and saturates the result if an overflow occurred QDADD doubles and saturates one of the input registers then add and saturate • QSUB subtracts two registers and saturates the result if an overflow occurred • QDSUB doubles and saturates one of the input registers then subtract and saturate

The Intel<sup>®</sup> 80200 processor also implements LDRD, STRD and PLD instructions with the following implementation notes:

- PLD is interpreted as a read operation by the MMU and is ignored by the data breakpoint unit, i.e., PLD never generates data breakpoint events.

- PLD to a non-cacheable page performs no action. Also, if the targeted cache line is already resident, this instruction has no affect.

- Both LDRD and STRD instructions generation an alignment exception when the address bits [2:0] = 0b100.

MCRR and MRRC are only supported on the Intel<sup>®</sup> 80200 processor when directed to coprocessor 0 and are used to access the internal accumulator. See Section 2.3.1.2 for more information. Access to any other coprocessor besides 0x0 are undefined.

## 2.2.5 Base Register Update

If a data abort is signalled on a memory instruction that specifies writeback, the contents of the base register is not updated. This holds for all load and store instructions. This behavior matches that of the first generation Intel<sup>®</sup> StrongARM\* processor and is referred to in the ARM V5 architecture as the *Base Restored Abort Model*.

## 2.3 Extensions to ARM\* Architecture

The Intel<sup>®</sup> 80200 processor made a few extensions to the ARM Version 5 architecture to meet the needs of various markets and design requirements. The following is a list of the extensions which are discussed in the next sections.

- A DSP coprocessor (CP0) has been added that contains a 40-bit accumulator and new instructions.

- New page attributes were added to the page table descriptors. The C and B page attribute encoding was extended by one more bit to allow for more encodings: write allocate and mini-data cache. An attribute specifying ECC for 1Meg regions was also added.

- Additional functionality has been added to coprocessor 15. Coprocessor 14 was also created.

- Enhancements were made to the Event Architecture, instruction cache and data cache parity error exceptions, breakpoint events, and imprecise external data aborts.

## 2.3.1 DSP Coprocessor 0 (CP0)

The Intel<sup>®</sup> 80200 processor adds a DSP coprocessor to the architecture for the purpose of increasing the performance and the precision of audio processing algorithms. This coprocessor contains a 40-bit accumulator and new instructions.

The 40-bit accumulator is referenced by several new instructions that were added to the architecture; **MIA**, **MIAPH** and **MIAxy** are multiply/accumulate instructions that reference the 40-bit accumulator instead of a register specified accumulator. **MAR** and **MRA** provide the ability to read and write the 40-bit accumulator.