## 80C186XL/80C188XL Microprocessor User's Manual

## 80C186XL/80C188XL Microprocessor User's Manual

1995

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683

© INTEL CORPORATION, 1995

| CHAP INT                 | TER 1<br>RODUCTION                                |      |

|--------------------------|---------------------------------------------------|------|

| 1.1                      | HOW TO USE THIS MANUAL                            | 1-2  |

| 1.2                      | RELATED DOCUMENTS                                 | 1-3  |

| 1.3                      | ELECTRONIC SUPPORT SYSTEMS                        | 1-4  |

| 1.3.1                    |                                                   |      |

| 1.3.2                    |                                                   |      |

| 1.3.                     |                                                   |      |

| 1.3.3                    | CompuServe Forums                                 | 1-6  |

| 1.3.4                    | World Wide Web                                    | 1-6  |

| 1.4                      | TECHNICAL SUPPORT                                 | 1-6  |

| 1.5                      | PRODUCT LITERATURE                                | 1-7  |

| 1.6                      | TRAINING CLASSES                                  |      |

| CHAP <sup>-</sup><br>OVI | TER 2<br>ERVIEW OF THE 80C186 FAMILY ARCHITECTURE |      |

| 2.1                      | ARCHITECTURAL OVERVIEW                            | 2-1  |

| 2.1.1                    | Execution Unit                                    | 2-2  |

| 2.1.2                    | Bus Interface Unit                                | 2-3  |

| 2.1.3                    | General Registers                                 | 2-4  |

| 2.1.4                    | Segment Registers                                 | 2-5  |

| 2.1.5                    | Instruction Pointer                               | 2-6  |

| 2.1.6                    | Flags                                             | 2-7  |

| 2.1.7                    | Memory Segmentation                               | 2-8  |

| 2.1.8                    | Logical Addresses                                 | 2-10 |

| 2.1.9                    | Dynamically Relocatable Code                      | 2-13 |

| 2.1.1                    | 0 Stack Implementation                            | 2-15 |

| 2.1.1                    | 1 Reserved Memory and I/O Space                   | 2-15 |

| 2.2                      | SOFTWARE OVERVIEW                                 | 2-17 |

| 2.2.1                    | Instruction Set                                   | 2-17 |

| 2.2.                     | .1.1 Data Transfer Instructions                   | 2-18 |

| 2.2.                     |                                                   |      |

| 2.2.                     |                                                   |      |

| 2.2.                     | - · · · · · · · · · · · · · · · · · · ·           |      |

| 2.2.                     |                                                   |      |

| 2.2.                     |                                                   |      |

| 2.2.2<br>2.2.            | 3                                                 |      |

| 2.2.<br>2.2.             |                                                   |      |

| 2.2.                     |                                                   |      |

| 2.2.                     |                                                   |      |

| 2.3   | INTERRUPTS AND EXCEPTION HANDLING        | 2-39 |

|-------|------------------------------------------|------|

| 2.3.1 |                                          |      |

| 2.3   | .1.1 Non-Maskable Interrupts             |      |

| 2.3   | .1.2 Maskable Interrupts                 | 2-43 |

| 2.3   | .1.3 Exceptions                          |      |

| 2.3.2 |                                          |      |

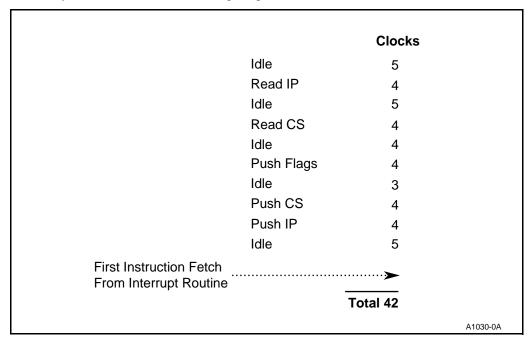

| 2.3.3 | B Interrupt Latency                      | 2-45 |

| 2.3.4 | Interrupt Response Time                  | 2-46 |

| 2.3.5 | Interrupt and Exception Priority         | 2-46 |

| -     | TER 3                                    |      |

| BU    | S INTERFACE UNIT                         |      |

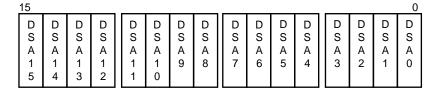

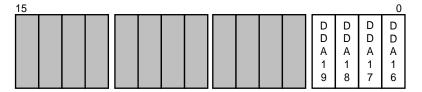

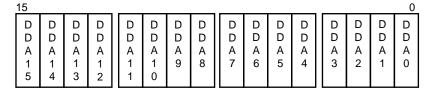

| 3.1   | MULTIPLEXED ADDRESS AND DATA BUS         | 3-1  |

| 3.2   | ADDRESS AND DATA BUS CONCEPTS            | 3-1  |

| 3.2.1 | 16-Bit Data Bus                          | 3-1  |

| 3.2.2 | 2 8-Bit Data Bus                         | 3-5  |

| 3.3   | MEMORY AND I/O INTERFACES                | 3-6  |

| 3.3.1 | 16-Bit Bus Memory and I/O Requirements   | 3-7  |

| 3.3.2 | 8-Bit Bus Memory and I/O Requirements    | 3-7  |

| 3.4   | BUS CYCLE OPERATION                      | 3-7  |

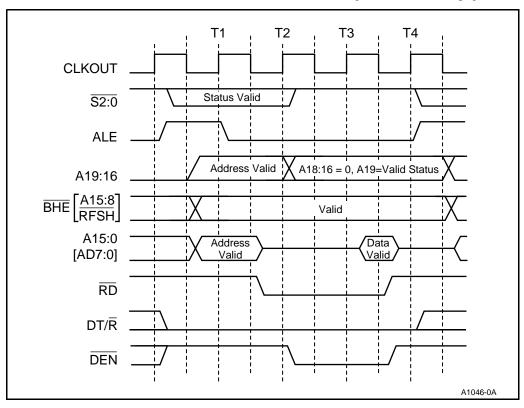

| 3.4.1 | Address/Status Phase                     | 3-10 |

| 3.4.2 | 2 Data Phase                             | 3-13 |

| 3.4.3 |                                          |      |

| 3.4.4 | Idle States                              | 3-18 |

| 3.5   | BUS CYCLES                               | 3-20 |

| 3.5.1 |                                          |      |

|       | .1.1 Refresh Bus Cycles                  |      |

| 3.5.2 | -                                        |      |

| 3.5.3 | •                                        |      |

| 3.5   | .3.1 System Design Considerations        |      |

| 3.5.4 |                                          |      |

| 3.5.5 | Temporarily Exiting the HALT Bus State   | 3-30 |

| 3.5.6 | S Exiting HALT                           | 3-32 |

| 3.6   | SYSTEM DESIGN ALTERNATIVES               | 3-33 |

| 3.6.1 |                                          |      |

| 3.6.2 | •                                        |      |

| 3.6.3 |                                          |      |

| 3.6.4 | _                                        |      |

| 3.7   | MULTI-MASTER BUS SYSTEM DESIGNS          |      |

| 3.7.1 |                                          |      |

| -     | .1.1 HOLD Bus Latency                    |      |

|       | .1.2 Refresh Operation During a Bus HOLD |      |

| 3.7.2 |                                          |      |

| 3.8   | BUS CYCLE PRIORITIES                     |      |

|       |                                          |      |

|       | TER 4                                                    |      |

|-------|----------------------------------------------------------|------|

|       | RIPHERAL CONTROL BLOCK                                   |      |

| 4.1   | PERIPHERAL CONTROL REGISTERS                             |      |

| 4.2   | PCB RELOCATION REGISTER                                  |      |

| 4.3   | RESERVED LOCATIONS                                       |      |

| 4.4   | ACCESSING THE PERIPHERAL CONTROL BLOCK                   |      |

| 4.4.1 | · · · <b>y</b> · · · ·                                   |      |

| 4.4.2 |                                                          |      |

| 4.4.3 |                                                          |      |

|       | .3.1 Writing the PCB Relocation Register                 |      |

|       | .3.2 Accessing the Peripheral Control Registers          |      |

|       | .3.3 Accessing Reserved Locations                        |      |

| 4.5   |                                                          |      |

| 4.5.1 | Considerations for the 80C187 Math Coprocessor Interface | 4-7  |

| СНАР  | TER 5                                                    |      |

|       | OCK GENERATION AND POWER MANAGEMENT                      |      |

| 5.1   | CLOCK GENERATION                                         | 5-1  |

| 5.1.1 |                                                          |      |

| 5.1   | .1.1 Oscillator Operation                                |      |

| 5.1   | .1.2 Selecting Crystals                                  |      |

| 5.1.2 | Using an External Oscillator                             | 5-6  |

| 5.1.3 |                                                          |      |

| 5.1.4 | •                                                        |      |

| 5.2   | POWER MANAGEMENT                                         | 5-10 |

| 5.2.1 |                                                          |      |

|       | .1.1 Entering Power-Save Mode                            | 5-11 |

|       | .1.2 Leaving Power-Save Mode                             |      |

| 5.2   | .1.3 Example Power-Save Initialization Code              | 5-13 |

| СНАР  | TER 6                                                    |      |

|       | IP-SELECT UNIT                                           |      |

| 6.1   | COMMON METHODS FOR GENERATING CHIP-SELECTS               | 6-1  |

| 6.2   | CHIP-SELECT UNIT FEATURES AND BENEFITS                   |      |

| 6.3   | CHIP-SELECT UNIT FUNCTIONAL OVERVIEW                     |      |

| 6.4   | PROGRAMMING                                              |      |

| 6.4.1 |                                                          |      |

| 6.4.2 | •                                                        |      |

|       | .2.1 UCS Active Range                                    |      |

|       | .2.2 LCS Active Range                                    |      |

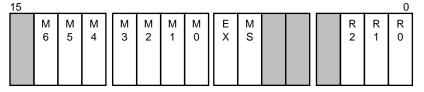

| 6.4   | .2.3 MCS Active Range                                    | 6-13 |

| 6.4   | .2.4 PCS Active Range                                    |      |

| 6.4.3 | · · · · · · · · · · · · · · · · · · ·                    |      |

| 6.4.4 | Overlapping Chip-Selects                                 | 6-16 |

| 6.4.5 | Memory or I/O Bus Cycle Decoding           | 6-17 |

|-------|--------------------------------------------|------|

| 6.4.6 | Programming Considerations                 | 6-17 |

| 6.5   | CHIP-SELECTS AND BUS HOLD                  | 6-18 |

| 6.6   | EXAMPLES                                   | 6-18 |

| 6.6.1 | Example 1: Typical System Configuration    | 6-18 |

| СНАР  | TER 7                                      |      |

| RE    | FRESH CONTROL UNIT                         |      |

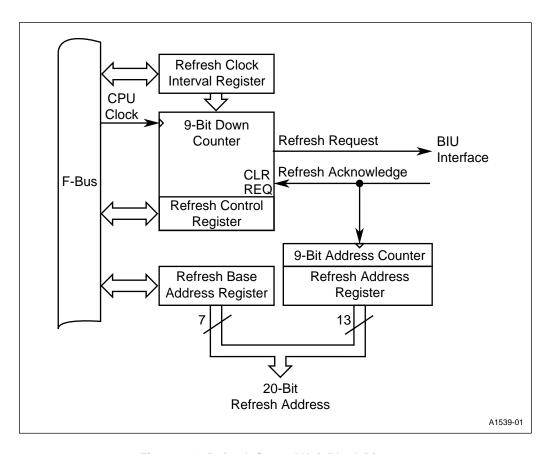

| 7.1   | THE ROLE OF THE REFRESH CONTROL UNIT       | 7-2  |

| 7.2   | REFRESH CONTROL UNIT CAPABILITIES          | 7-2  |

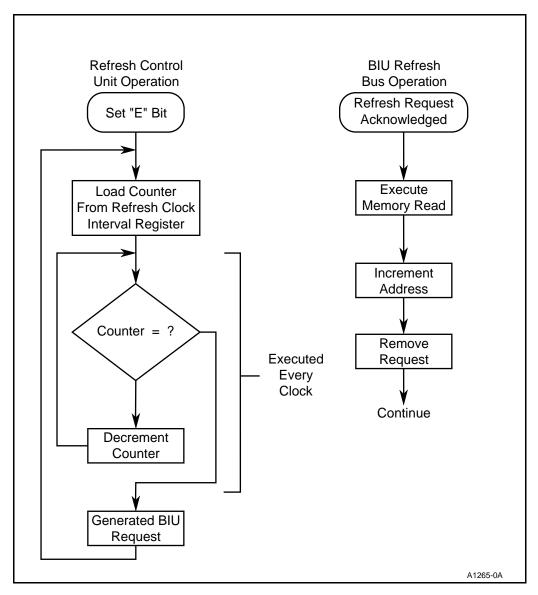

| 7.3   | REFRESH CONTROL UNIT OPERATION             | 7-2  |

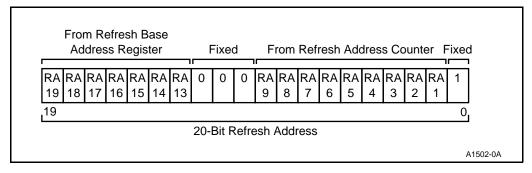

| 7.4   | REFRESH ADDRESSES                          | 7-4  |

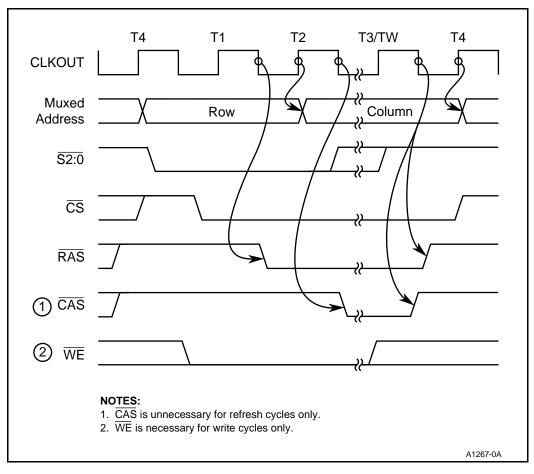

| 7.5   | REFRESH BUS CYCLES                         | 7-5  |

| 7.6   | GUIDELINES FOR DESIGNING DRAM CONTROLLERS  | 7-5  |

| 7.7   | PROGRAMMING THE REFRESH CONTROL UNIT       | 7-7  |

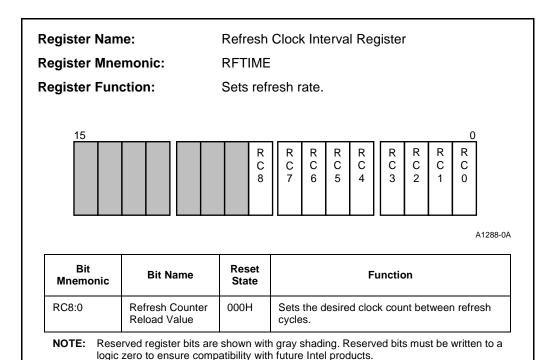

| 7.7.1 | Calculating the Refresh Interval           | 7-7  |

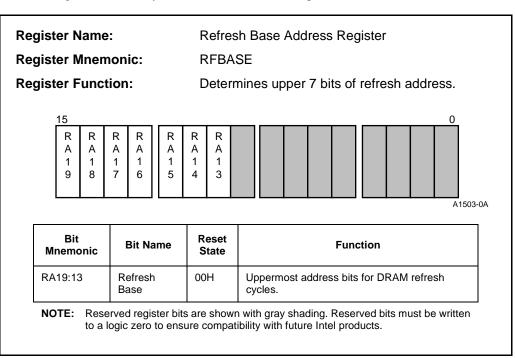

| 7.7.2 | Refresh Control Unit Registers             | 7-7  |

|       | .2.1 Refresh Base Address Register         |      |

|       | .2.2 Refresh Clock Interval Register       |      |

|       | .2.3 Refresh Control Register              |      |

| 7.7.3 |                                            |      |

| 7.8   | REFRESH OPERATION AND BUS HOLD             | 7-12 |

| _     | TER 8                                      |      |

|       | FERRUPT CONTROL UNIT                       |      |

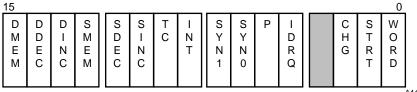

| 8.1   | FUNCTIONAL OVERVIEW                        |      |

| 8.2   | MASTER MODE                                |      |

| 8.2.1 |                                            |      |

|       | .1.1 Interrupt Masking                     |      |

|       | .1.3 Interrupt Nesting                     |      |

| 8.3   | FUNCTIONAL OPERATION IN MASTER MODE        |      |

| 8.3.1 |                                            |      |

| 8.3.2 | ••                                         |      |

|       | .2.1 Priority Resolution Example           |      |

| 8.3   | .2.2 Interrupts That Share a Single Source | 8-7  |

| 8.3.3 | · · · · · · · · · · · · · · · · · · ·      |      |

|       | .3.1 Special Fully Nested Mode             |      |

| 8.3.4 | 31                                         |      |

| 8.3.5 | · · · · · · · · · · · · · · · · · · ·      |      |

| 8.3.6 | 33. 3                                      |      |

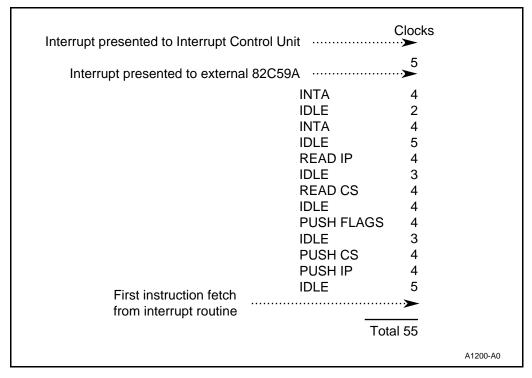

| 8.3.7 | Additional Latency and Response Time       | 8-10 |

| 8.4   | PROGRAMMING THE INTERRUPT CONTROL UNIT                  | 8-11 |

|-------|---------------------------------------------------------|------|

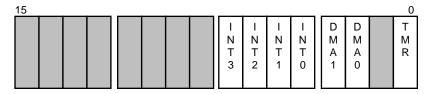

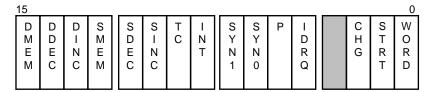

| 8.4.1 | Interrupt Control Registers                             | 8-12 |

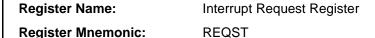

| 8.4.2 | Interrupt Request Register                              | 8-16 |

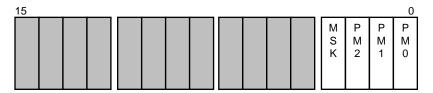

| 8.4.3 | Interrupt Mask Register                                 | 8-16 |

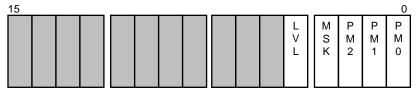

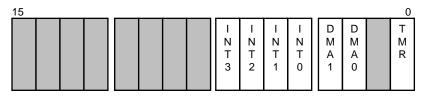

| 8.4.4 | Priority Mask Register                                  | 8-17 |

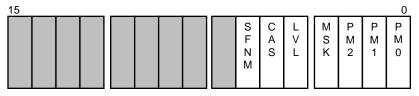

| 8.4.5 | In-Service Register                                     | 8-18 |

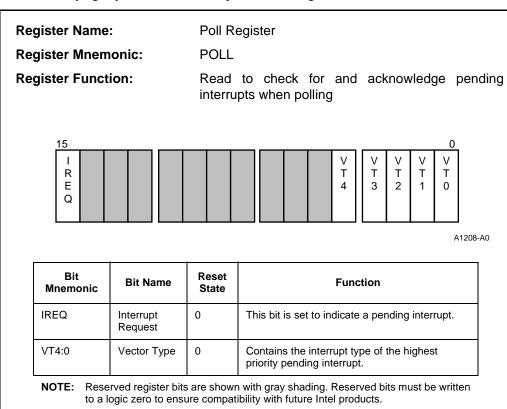

| 8.4.6 | Poll and Poll Status Registers                          | 8-19 |

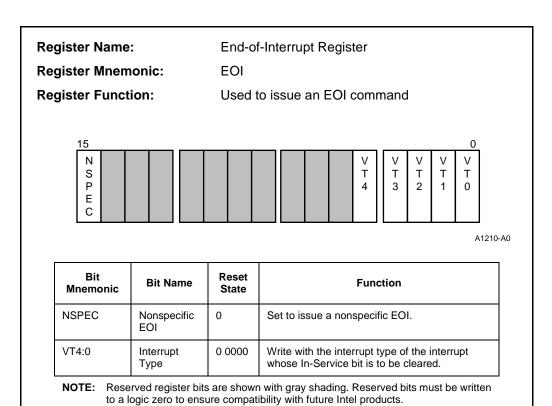

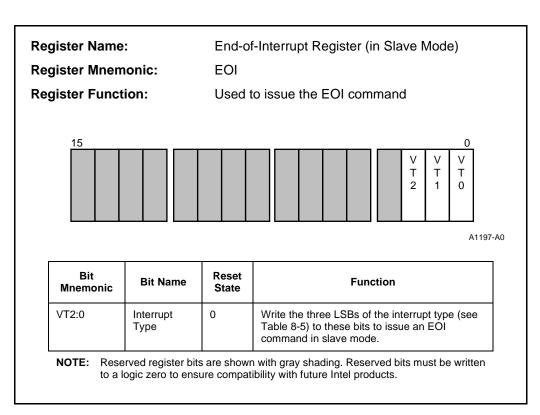

| 8.4.7 | End-of-Interrupt (EOI) Register                         | 8-21 |

| 8.4.8 | Interrupt Status Register                               | 8-22 |

| 8.5   | SLAVE MODE                                              | 8-23 |

| 8.5.1 | Slave Mode Programming                                  |      |

| 8.5.  | 1.1 Interrupt Vector Register                           | 8-26 |

| 8.5.  | 1.2 End-Of-Interrupt Register                           | 8-27 |

| 8.5.  | 3                                                       |      |

| 8.5.2 | 3                                                       |      |

| 8.5.3 | Initializing the Interrupt Control Unit for Master Mode | 8-30 |

| CHAD. | TED 0                                                   |      |

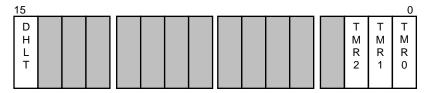

| CHAP' | ER/COUNTER UNIT                                         |      |

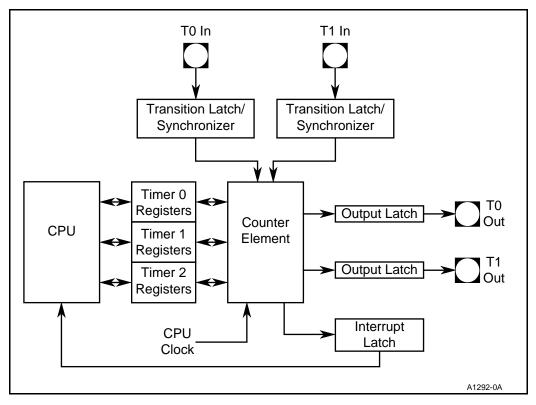

| 9.1   | FUNCTIONAL OVERVIEW                                     | 9-1  |

| 9.2   | PROGRAMMING THE TIMER/COUNTER UNIT                      |      |

| 9.2.1 | Initialization Sequence                                 |      |

| 9.2.2 | •                                                       |      |

| 9.2.3 |                                                         |      |

| 9.2.  | <u> </u>                                                |      |

| 9.2.4 |                                                         |      |

| 9.2.5 |                                                         |      |

| 9.2.6 |                                                         |      |

| 9.2.7 | •                                                       |      |

| 9.3   | TIMING                                                  |      |

| 9.3.1 | Input Setup and Hold Timings                            |      |

| 9.3.2 |                                                         |      |

| 9.3.  |                                                         |      |

| 9.3.3 |                                                         |      |

| 9.3.4 |                                                         |      |

| 9.3.5 | •                                                       |      |

|       | •                                                       |      |

|       | TER 10                                                  |      |

|       | ECT MEMORY ACCESS UNIT                                  |      |

| 10.1  | FUNCTIONAL OVERVIEW                                     |      |

| 10.1. |                                                         |      |

| _     | 1.1.1 DMA Transfer Directions                           |      |

|       | 1.1.2 Byte and Word Transfers                           |      |

| 10.1. | 2 Source and Destination Pointers                       | 10-3 |

| 10.1.3  | DMA Requests                            | 10-3  |

|---------|-----------------------------------------|-------|

| 10.1.4  | External Requests                       | 10-4  |

| 10.1.4  | ·                                       |       |

| 10.1.4  | •                                       |       |

| 10.1.5  | Internal Requests                       |       |

| 10.1.5  |                                         |       |

| 10.1.5  |                                         |       |

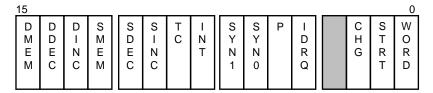

| 10.1.6  | DMA Transfer Counts                     |       |

| 10.1.7  |                                         |       |

| 10.1.7  | ·                                       |       |

| 10.1.7  |                                         |       |

| 10.1.7  |                                         |       |

| 10.1.7  | •                                       |       |

| 10.1.8  | DMA Unit Interrupts                     |       |

| 10.1.9  | DMA Cycles and the BIU                  |       |

|         | The Two-Channel DMA Unit                |       |

| 10.1.10 |                                         |       |

|         | ROGRAMMING THE DMA UNIT                 |       |

| 10.2.1  | DMA Channel Parameters                  |       |

| 10.2.1  |                                         |       |

| 10.2.1  |                                         |       |

| 10.2.1  | <u> </u>                                |       |

| 10.2.1  | ·                                       |       |

| 10.2.1  |                                         |       |

| 10.2.1  |                                         |       |

| 10.2.1  |                                         |       |

| 10.2.1  | •                                       |       |

| 10.2.1  | Suspension of DMA Transfers             |       |

| 10.2.2  | Initializing the DMA Unit               |       |

|         | · · · · · · · · · · · · · · · · · · ·   |       |

|         | ARDWARE CONSIDERATIONS AND THE DMA UNIT |       |

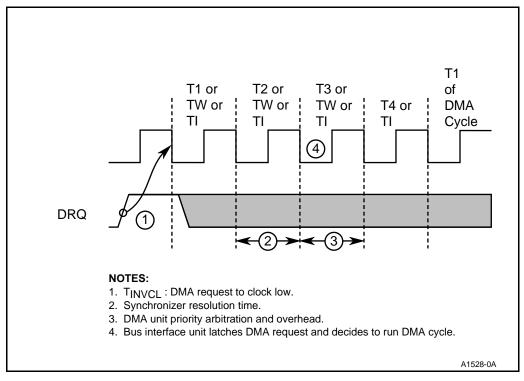

| 10.3.1  | DRQ Pin Timing Requirements             |       |

| 10.3.2  | DMA Latency                             |       |

| 10.3.3  | DMA Transfer Rates                      |       |

| 10.3.4  | Generating a DMA Acknowledge            | 10-22 |

| 10.4 D  | MA UNIT EXAMPLES                        | 10-22 |

| CHAPTE  | ER 11                                   |       |

|         | COPROCESSING                            |       |

| 11.1 O  | VERVIEW OF MATH COPROCESSING            | 11-1  |

| 11.2 A' | VAILABILITY OF MATH COPROCESSING        | 11-1  |

|         | HE 80C187 MATH COPROCESSOR              |       |

| 11.3.1  |                                         |       |

| 11.3.1  |                                         |       |

| 11.3.1  |                                         |       |

| _       | .3 Comparison Instructions              |       |

|         |                                         |       |

| 11.3.1          | .4 Transcendental Instructions                | 11-5  |

|-----------------|-----------------------------------------------|-------|

| 11.3.1          |                                               |       |

| 11.3.1          | .6 Processor Control Instructions             | 11-6  |

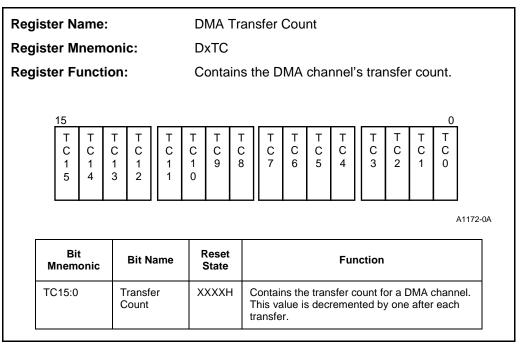

| 11.3.2          | 80C187 Data Types                             | 11-7  |

| 11.4 N          | IICROPROCESSOR AND COPROCESSOR OPERATION      | 11-7  |

| 11.4.1          | Clocking the 80C187                           | 11-10 |

| 11.4.2          | Processor Bus Cycles Accessing the 80C187     | 11-10 |

| 11.4.3          | System Design Tips                            | 11-11 |

| 11.4.4          | Exception Trapping                            |       |

| 11.5 E          | XAMPLE MATH COPROCESSOR ROUTINES              | 11-13 |

| CHAPTE          | ER 12<br>E MODE                               |       |

| 12.1 E          | NTERING/LEAVING ONCE MODE                     | 12-1  |

|                 | 66 INSTRUCTION SET ADDITIONS AND EXTENSIONS   |       |

| _               | 0C186 INSTRUCTION SET ADDITIONS               |       |

| A.1.1           | Data Transfer Instructions                    |       |

| A.1.2           | String Instructions                           |       |

| A.1.3           | High-Level Instructions                       |       |

| A.2 8           | 0C186 INSTRUCTION SET ENHANCEMENTS            | A-8   |

| A.2.1           | Data Transfer Instructions                    |       |

| A.2.2           | Arithmetic Instructions                       |       |

| A.2.3           | Bit Manipulation Instructions                 |       |

| A.2.3           |                                               |       |

| A.2.3           | 2 Rotate Instructions                         | A-10  |

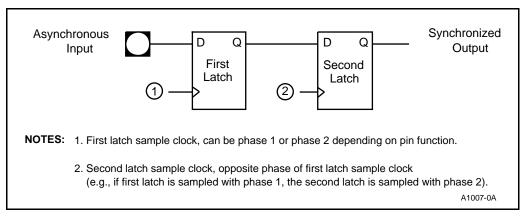

| APPENI          | DIX B<br>F SYNCHRONIZATION                    |       |

|                 | /HY SYNCHRONIZERS ARE REQUIRED                | D 4   |

|                 |                                               |       |

| B.2 A           | SYNCHRONOUS PINS                              | В-2   |

| APPENI<br>INSTI | DIX C<br>RUCTION SET DESCRIPTIONS             |       |

| APPENI<br>INSTI | DIX D<br>RUCTION SET OPCODES AND CLOCK CYCLES |       |

| INDEX           |                                               |       |

| i igui e |                                                              | raye |

|----------|--------------------------------------------------------------|------|

| 2-1      | Simplified Functional Block Diagram of the 80C186 Family CPU |      |

| 2-2      | Physical Address Generation                                  |      |

| 2-3      | General Registers                                            |      |

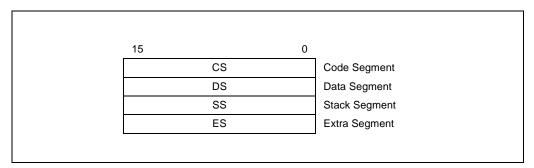

| 2-4      | Segment Registers                                            |      |

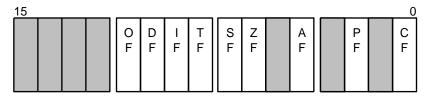

| 2-5      | Processor Status Word                                        |      |

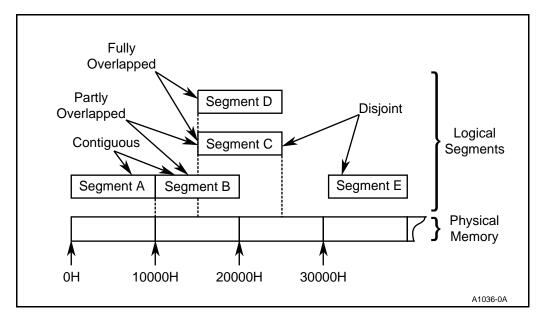

| 2-6      | Segment Locations in Physical Memory                         | 2-10 |

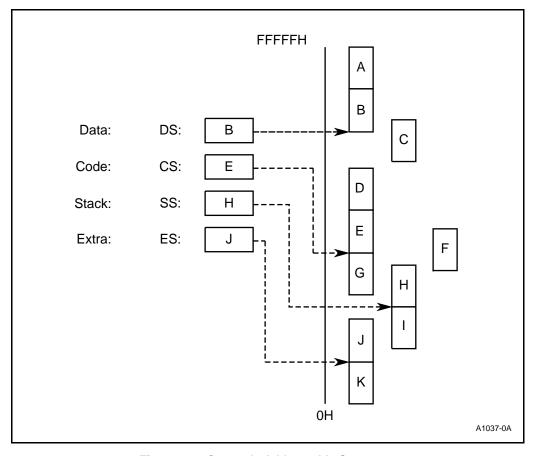

| 2-7      | Currently Addressable Segments                               | 2-11 |

| 2-8      | Logical and Physical Address                                 | 2-12 |

| 2-9      | Dynamic Code Relocation                                      | 2-14 |

| 2-10     | Stack Operation                                              | 2-16 |

| 2-11     | Flag Storage Format                                          |      |

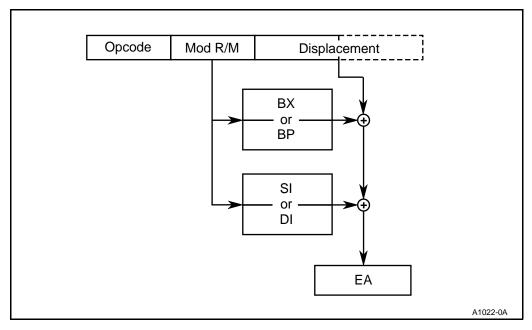

| 2-12     | Memory Address Computation                                   | 2-29 |

| 2-13     | Direct Addressing                                            | 2-30 |

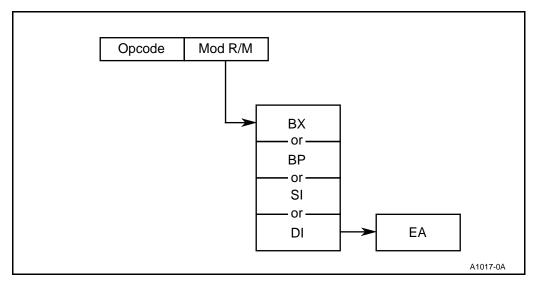

| 2-14     | Register Indirect Addressing                                 | 2-31 |

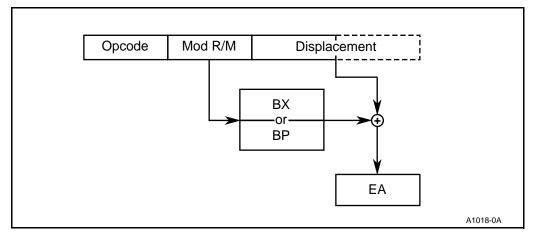

| 2-15     | Based Addressing                                             |      |

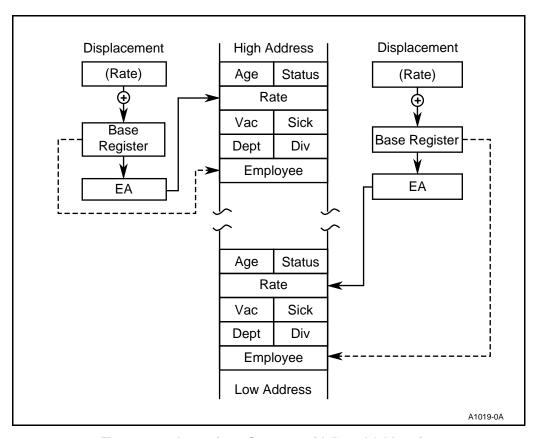

| 2-16     | Accessing a Structure with Based Addressing                  | 2-32 |

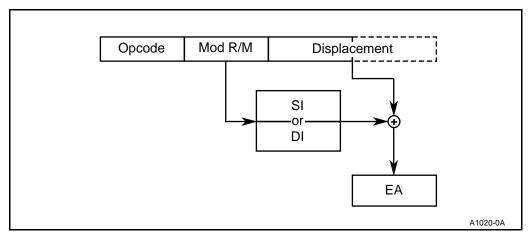

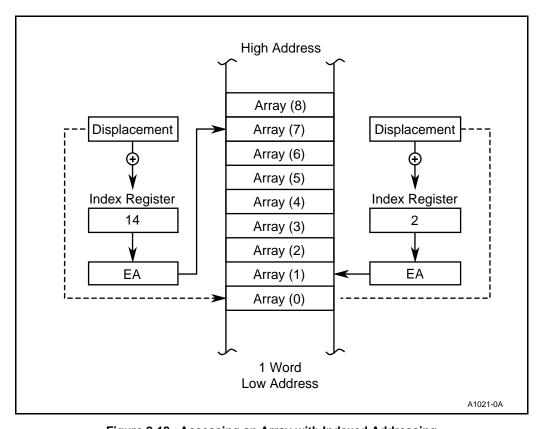

| 2-17     | Indexed Addressing                                           |      |

| 2-18     | Accessing an Array with Indexed Addressing                   | 2-33 |

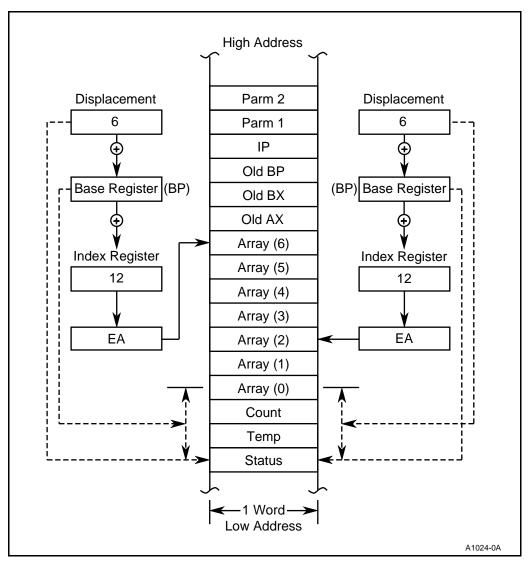

| 2-19     | Based Index Addressing                                       |      |

| 2-20     | Accessing a Stacked Array with Based Index Addressing        | 2-35 |

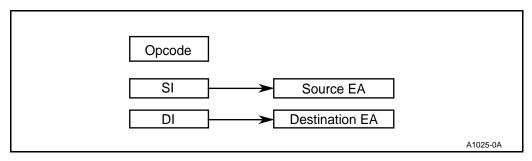

| 2-21     | String Operand                                               | 2-36 |

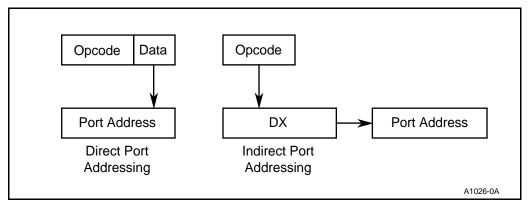

| 2-22     | I/O Port Addressing                                          | 2-36 |

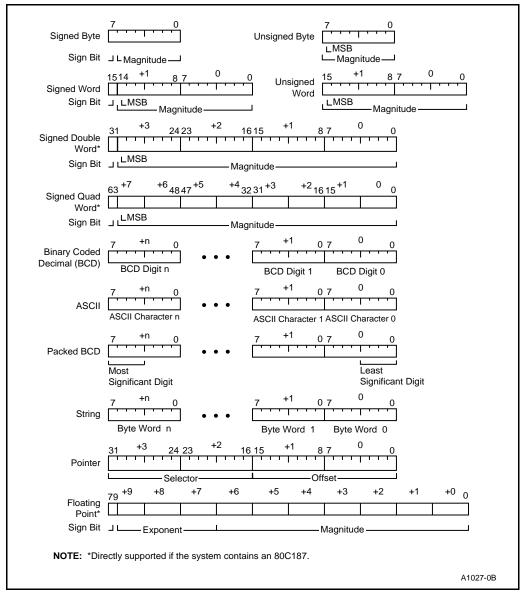

| 2-23     | 80C186 Modular Core Family Supported Data Types              |      |

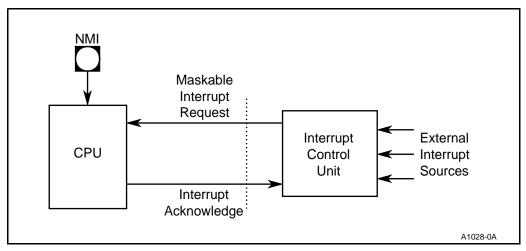

| 2-24     | Interrupt Control Unit                                       | 2-39 |

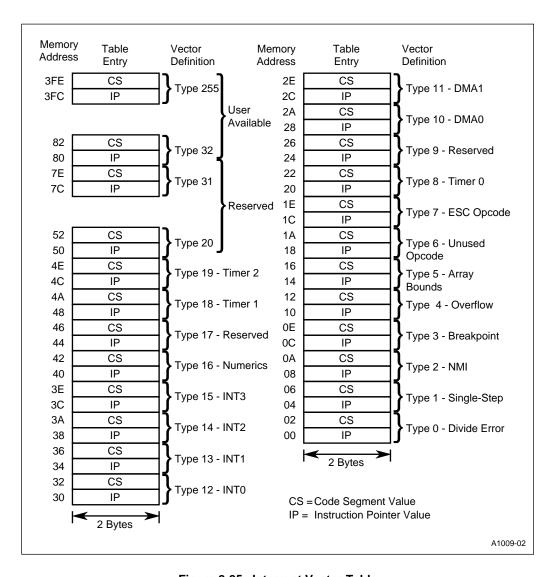

| 2-25     | Interrupt Vector Table                                       | 2-40 |

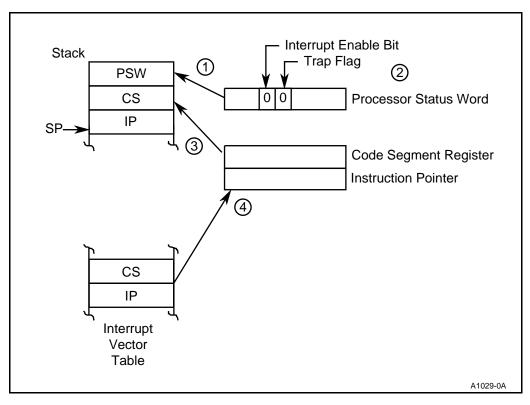

| 2-26     | Interrupt Sequence                                           | 2-42 |

| 2-27     | Interrupt Response Factors                                   |      |

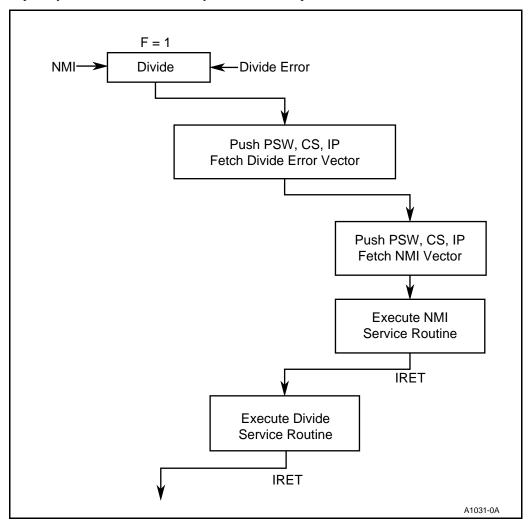

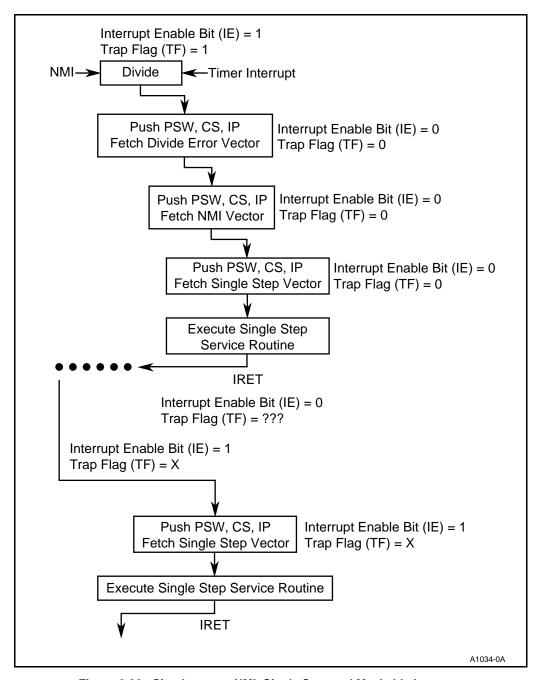

| 2-28     | Simultaneous NMI and Exception                               |      |

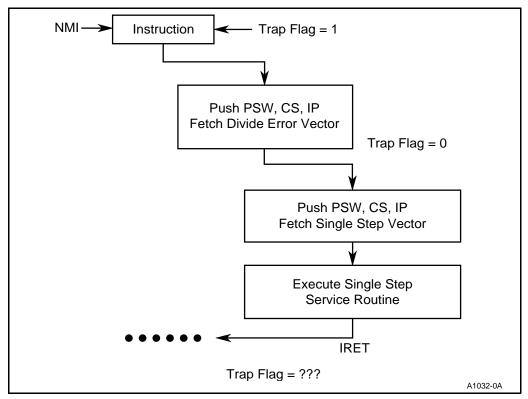

| 2-29     | Simultaneous NMI and Single Step Interrupts                  |      |

| 2-30     | Simultaneous NMI, Single Step and Maskable Interrupt         |      |

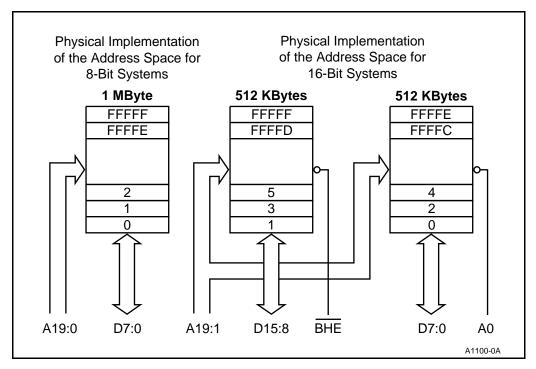

| 3-1      | Physical Data Bus Models                                     | 3-2  |

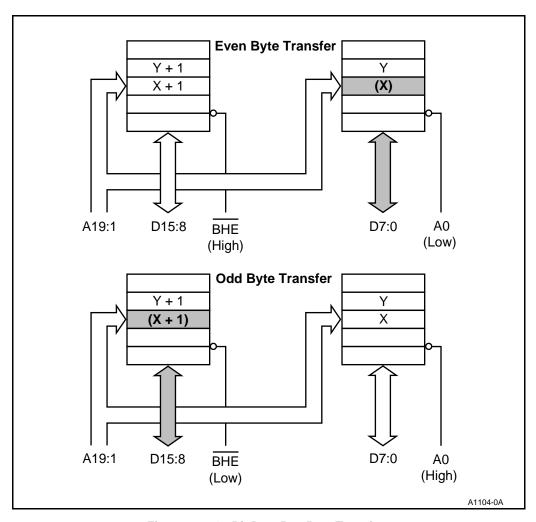

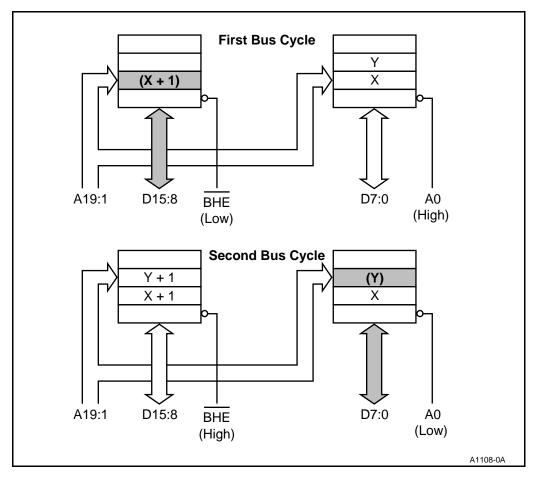

| 3-2      | 16-Bit Data Bus Byte Transfers                               |      |

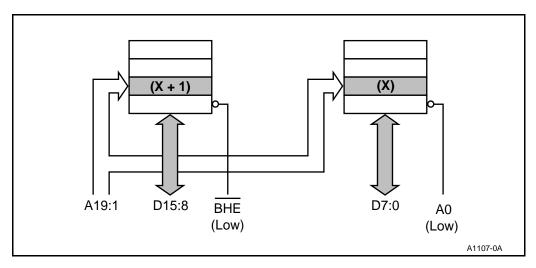

| 3-3      | 16-Bit Data Bus Even Word Transfers                          |      |

| 3-4      | 16-Bit Data Bus Odd Word Transfers                           |      |

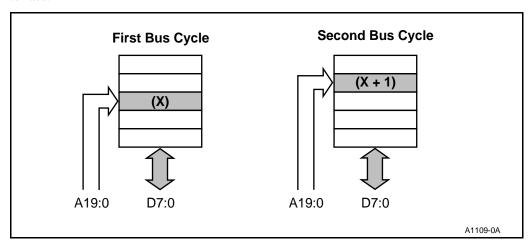

| 3-5      | 8-Bit Data Bus Word Transfers                                | 3-6  |

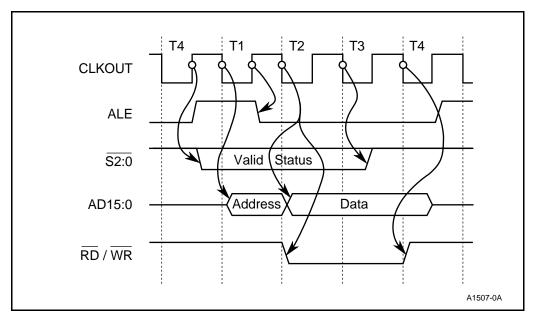

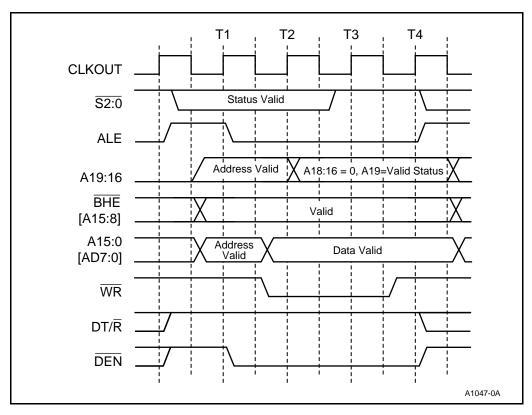

| 3-6      | Typical Bus Cycle                                            |      |

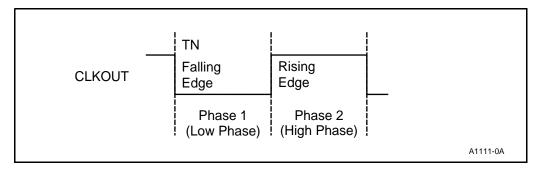

| 3-7      | T-State Relation to CLKOUT                                   | 3-8  |

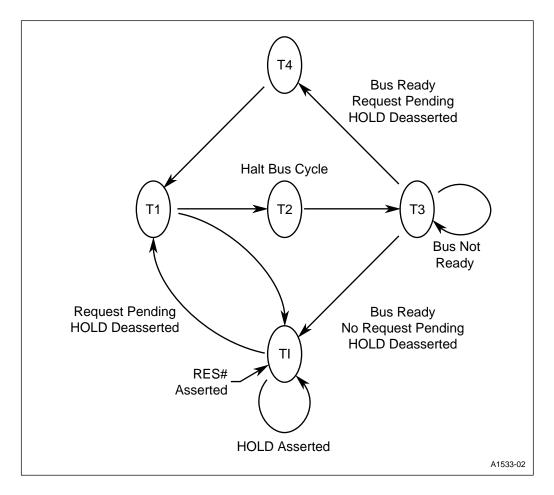

| 3-8      | BIU State Diagram                                            | 3-9  |

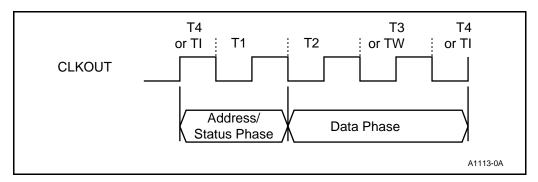

| 3-9      | T-State and Bus Phases                                       |      |

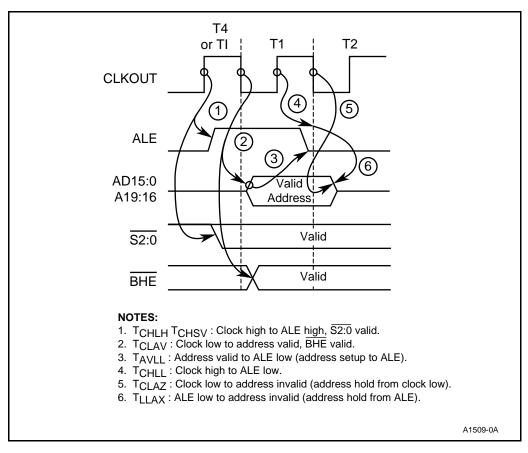

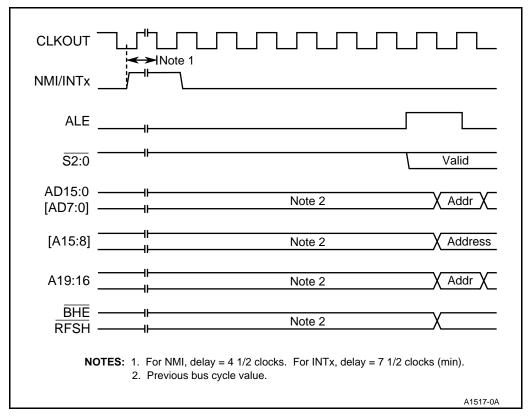

| 3-10     | Address/Status Phase Signal Relationships                    | 3-11 |

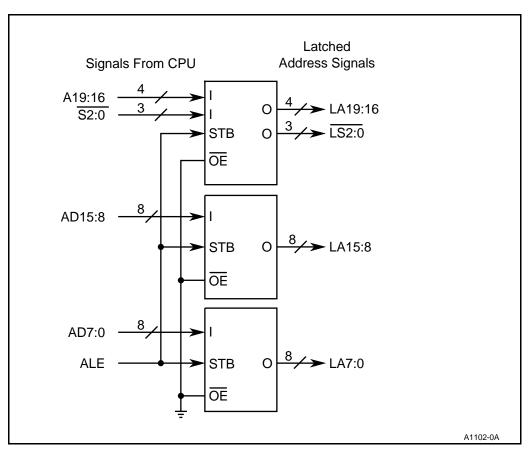

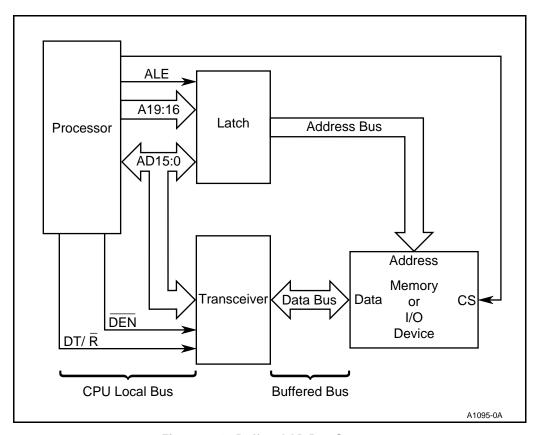

| 3-11     | Demultiplexing Address Information                           |      |

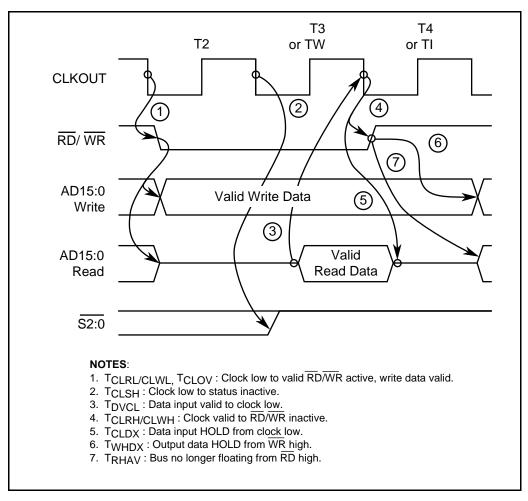

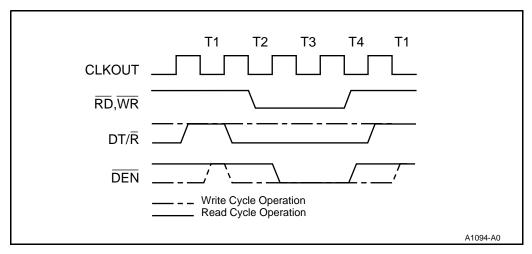

| 3-12     | Data Phase Signal Relationships                              | 3-14 |

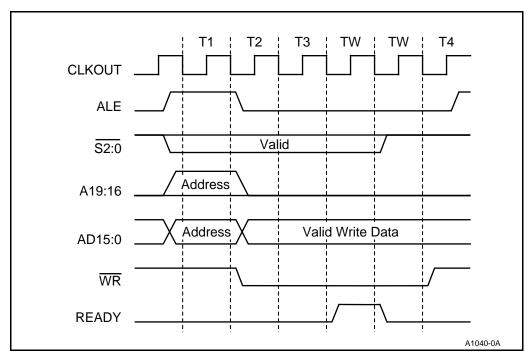

| 3-13     | Typical Bus Cycle with Wait States                           | 3-15 |

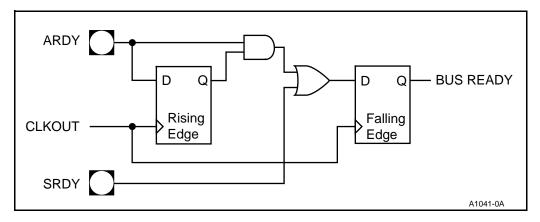

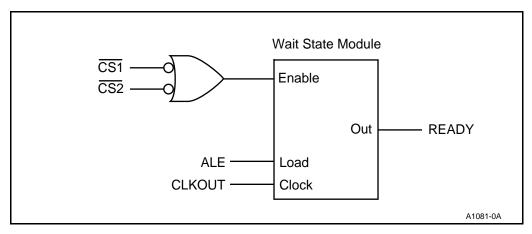

| 3-14     | ARDY and SRDY Pin Block Diagram                              | 3-15 |

|          |                                                              |      |

| Figure |                                                  | Page |

|--------|--------------------------------------------------|------|

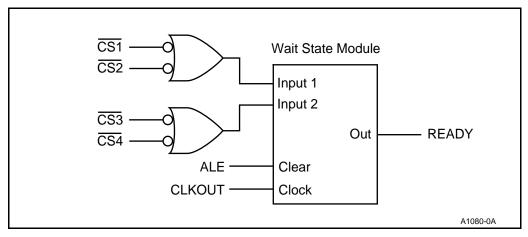

| 3-15   | Generating a Normally Not-Ready Bus Signal       | 3-16 |

| 3-16   | Generating a Normally Ready Bus Signal           |      |

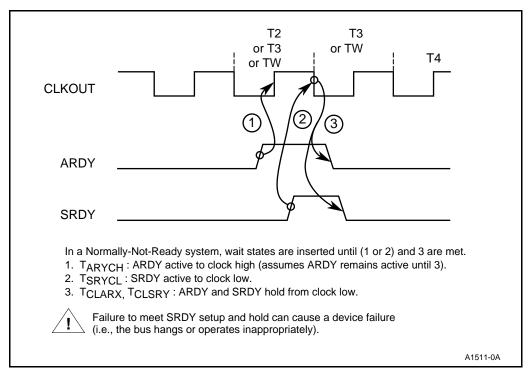

| 3-17   | Normally Not-Ready System Timing                 | 3-18 |

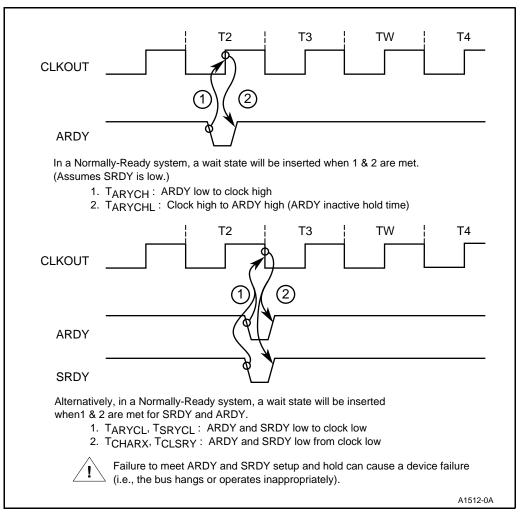

| 3-18   | Normally Ready System Timings                    |      |

| 3-19   | Typical Read Bus Cycle                           |      |

| 3-20   | Read-Only Device Interface                       |      |

| 3-21   | Typical Write Bus Cycle                          |      |

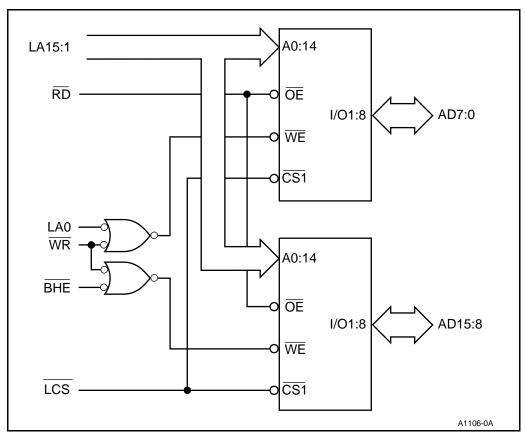

| 3-22   | 16-Bit Bus Read/Write Device Interface           |      |

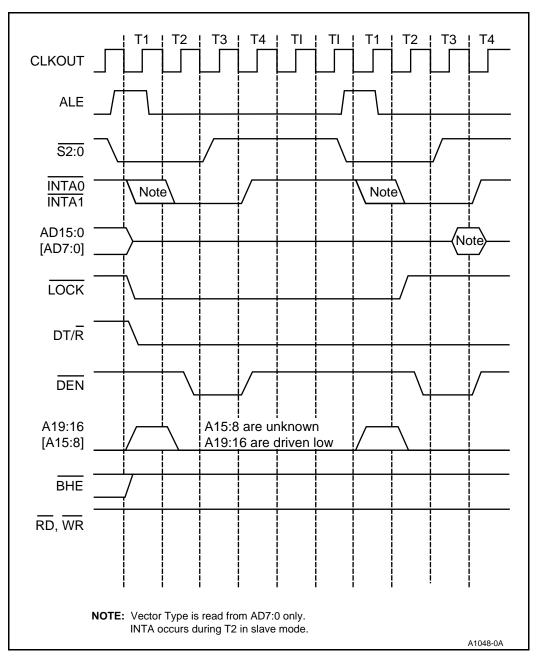

| 3-23   | Interrupt Acknowledge Bus Cycle                  | 3-26 |

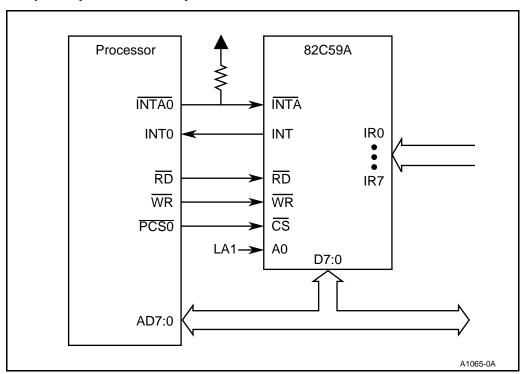

| 3-24   | Typical 82C59A Interface                         | 3-27 |

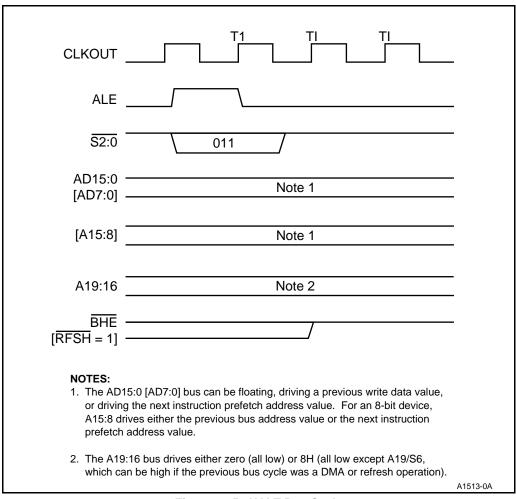

| 3-25   | HALT Bus Cycle                                   | 3-29 |

| 3-26   | Returning to HALT After a HOLD/HLDA Bus Exchange | 3-30 |

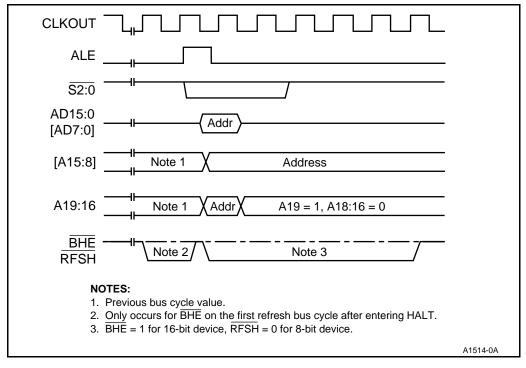

| 3-27   | Returning to HALT After a Refresh Bus Cycle      | 3-31 |

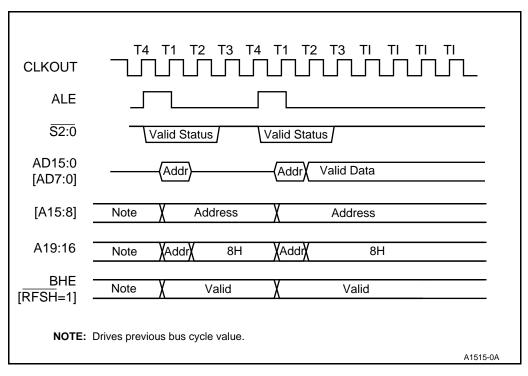

| 3-28   | Returning to HALT After a DMA Bus Cycle          | 3-32 |

| 3-29   | Exiting HALT                                     | 3-33 |

| 3-30   | DEN and DT/R Timing Relationships                | 3-34 |

| 3-31   | Buffered AD Bus System                           |      |

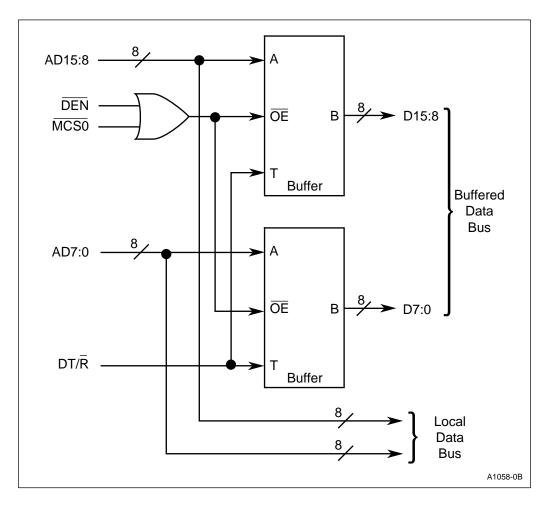

| 3-32   | Qualifying DEN with Chip-Selects                 | 3-36 |

| 3-33   | Queue Status Timing                              | 3-39 |

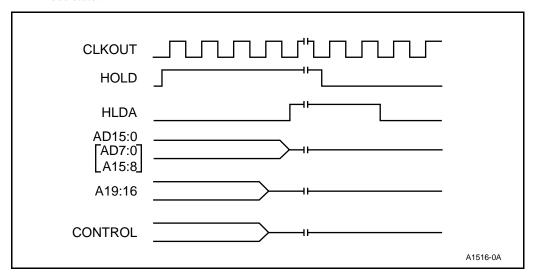

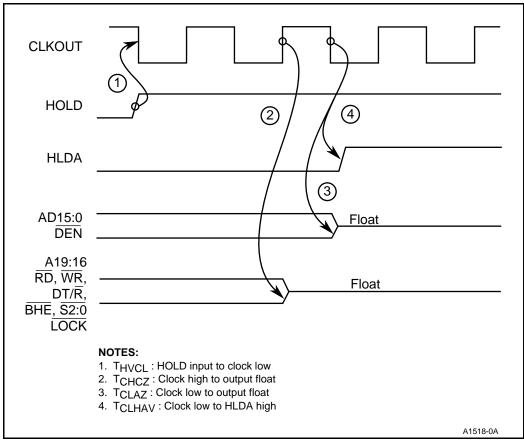

| 3-34   | Timing Sequence Entering HOLD                    | 3-40 |

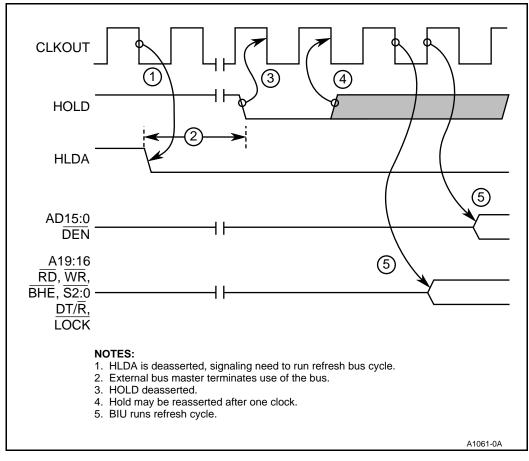

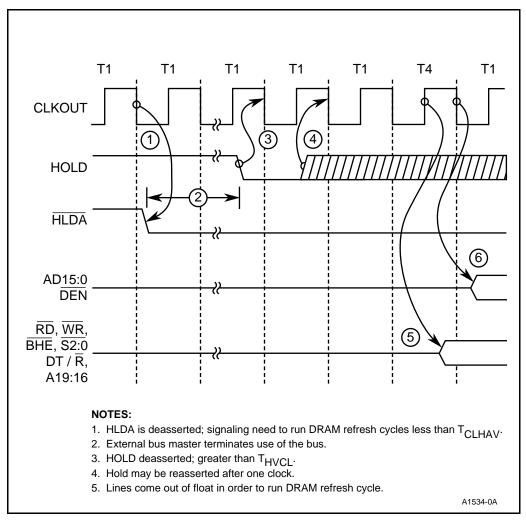

| 3-35   | Refresh Request During HOLD                      | 3-42 |

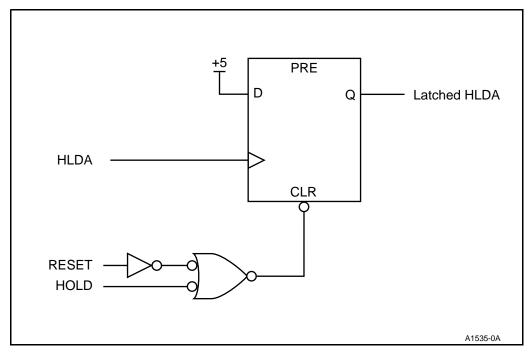

| 3-36   | Latching HLDA                                    | 3-43 |

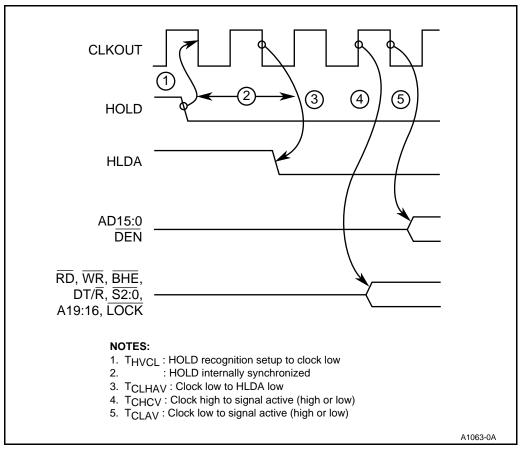

| 3-37   | Exiting HOLD                                     |      |

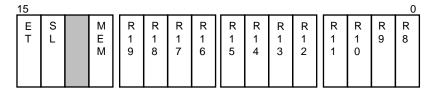

| 4-1    | PCB Relocation Register                          | 4-2  |

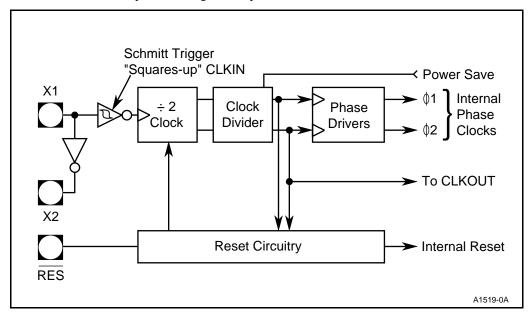

| 5-1    | Clock Generator                                  |      |

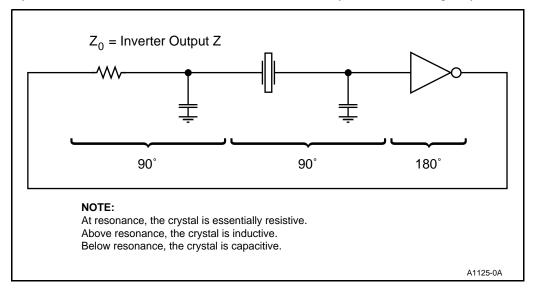

| 5-2    | Ideal Operation of Pierce Oscillator             |      |

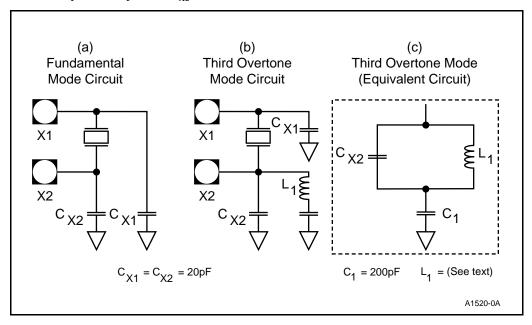

| 5-3    | Crystal Connections to Microprocessor            |      |

| 5-4    | Equations for Crystal Calculations               |      |

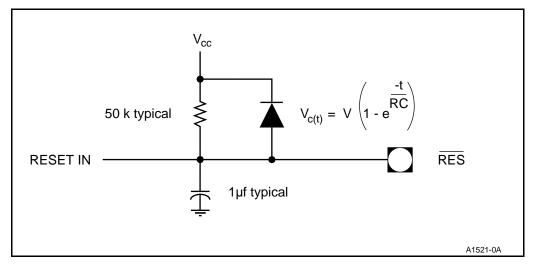

| 5-5    | Simple RC Circuit for Powerup Reset              |      |

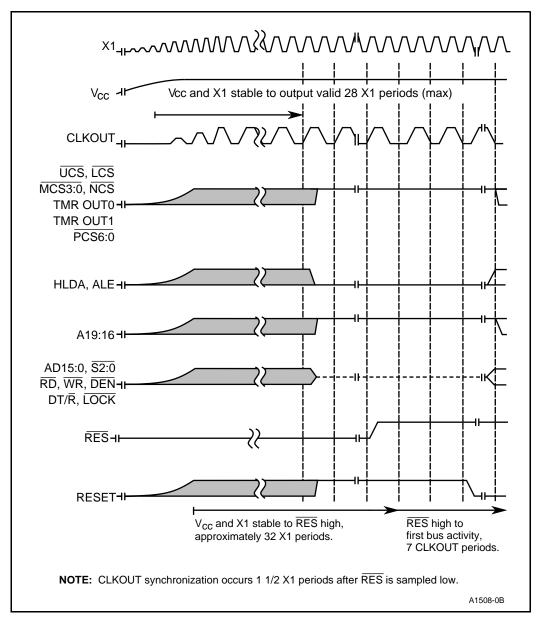

| 5-6    | Cold Reset Waveform                              |      |

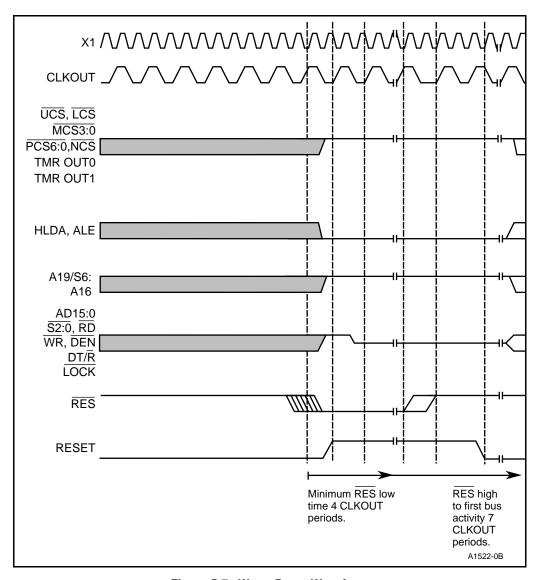

| 5-7    | Warm Reset Waveform                              |      |

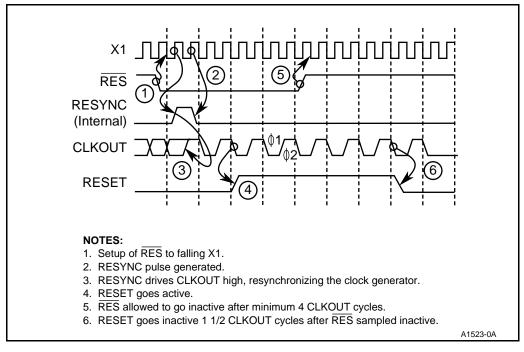

| 5-8    | Clock Synchronization at Reset                   |      |

| 5-9    | Power-Save Register                              |      |

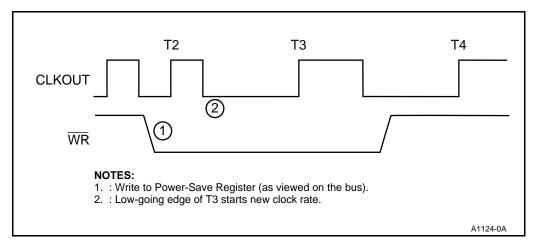

| 5-10   | Power-Save Clock Transition                      |      |

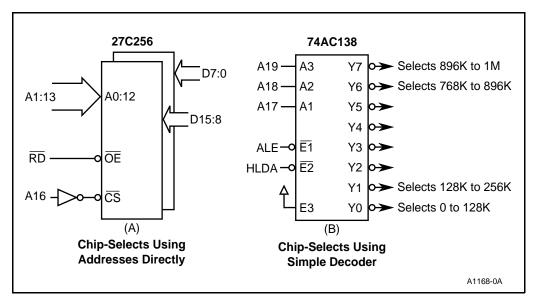

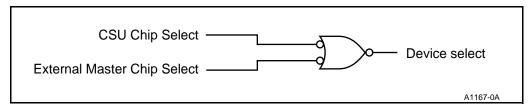

| 6-1    | Common Chip-Select Generation Methods            |      |

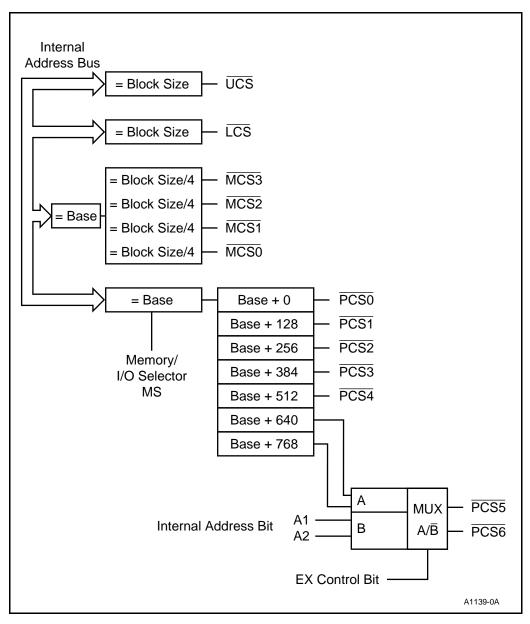

| 6-2    | Chip-Select Block Diagram                        |      |

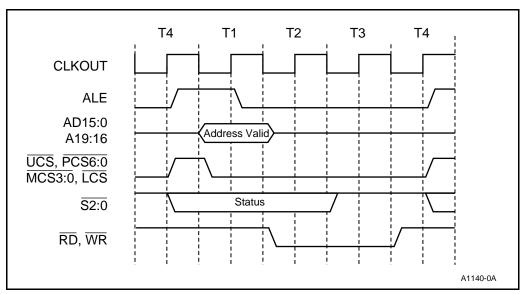

| 6-3    | Chip-Select Relative Timings                     |      |

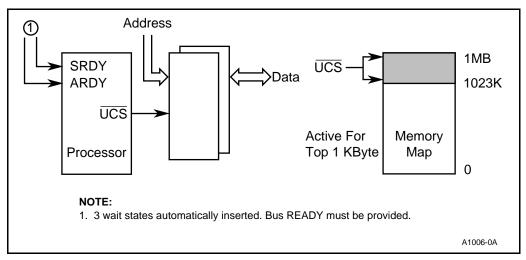

| 6-4    | UCS Reset Configuration                          |      |

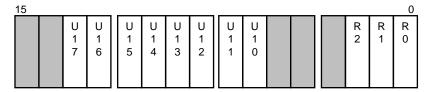

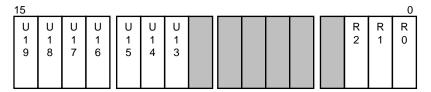

| 6-5    | UMCS Register Definition                         |      |

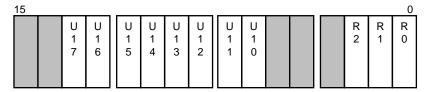

| 6-6    | LMCS Register Definition                         |      |

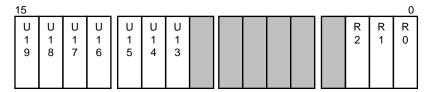

| 6-7    | MMCS Register Definition                         |      |

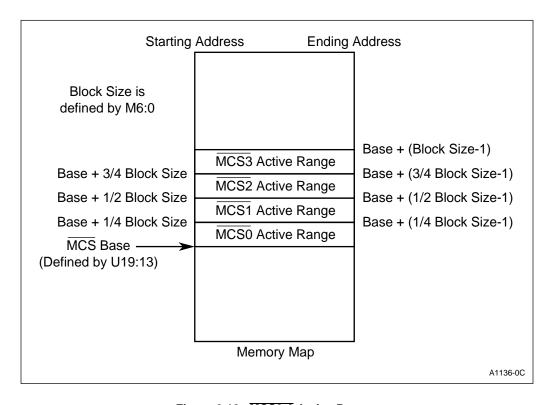

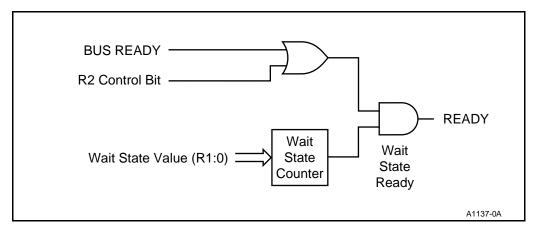

| 6-8    | PACS Register Definition                         |      |

| 6-9    | MPCS Register Definition                         |      |

| 6-10   | MCS3:0 Active Ranges                             | 6-14 |

| Figure |                                                              | Page |

|--------|--------------------------------------------------------------|------|

| 6-11   | Wait State and Ready Control Functions                       | 6-16 |

| 6-12   | Using Chip-Selects During HOLD                               | 6-18 |

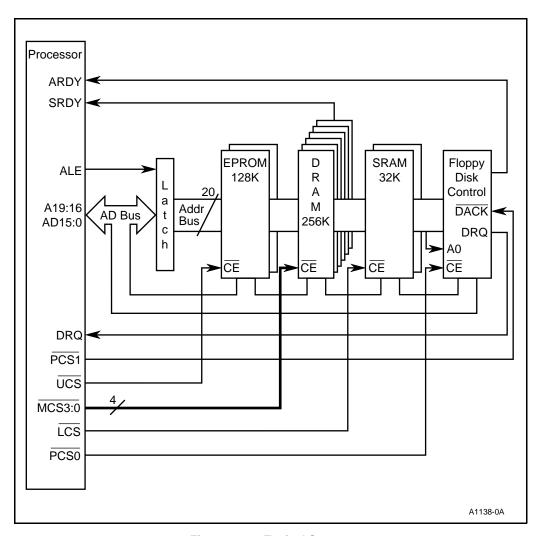

| 6-13   | Typical System                                               |      |

| 7-1    | Refresh Control Unit Block Diagram                           |      |

| 7-2    | Refresh Control Unit Operation Flow Chart                    |      |

| 7-3    | Refresh Address Formation                                    |      |

| 7-4    | Suggested DRAM Control Signal Timing Relationships           |      |

| 7-5    | Formula for Calculating Refresh Interval for RFTIME Register |      |

| 7-6    | Refresh Base Address Register                                |      |

| 7-7    | Refresh Clock Interval Register                              |      |

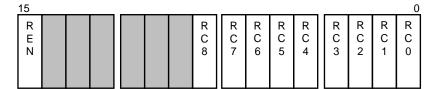

| 7-8    | Refresh Control Register                                     |      |

| 7-9    | Regaining Bus Control to Run a DRAM Refresh Bus Cycle        |      |

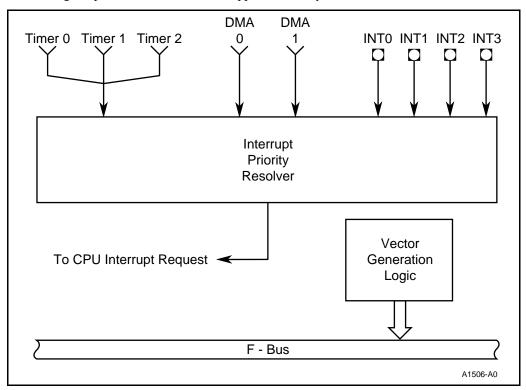

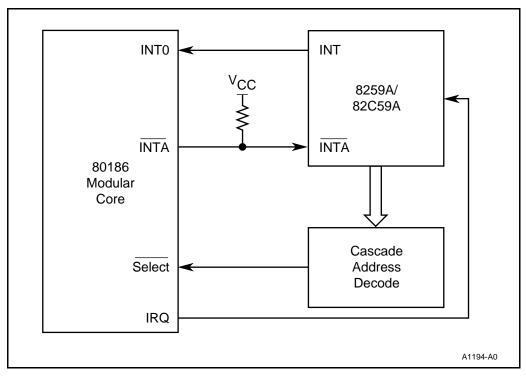

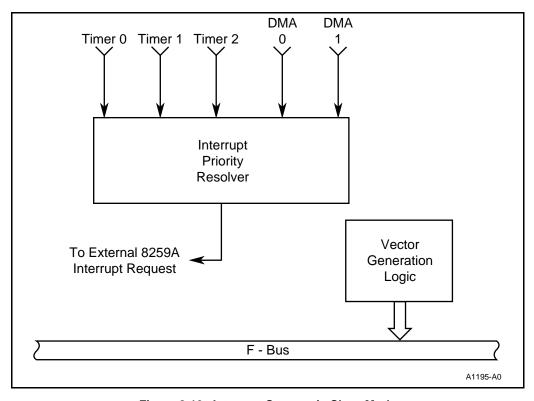

| 8-1    | Interrupt Control Unit in Master Mode                        |      |

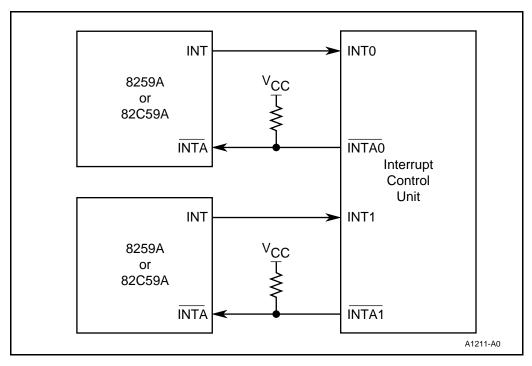

| 8-2    | Using External 8259A Modules in Cascade Mode                 |      |

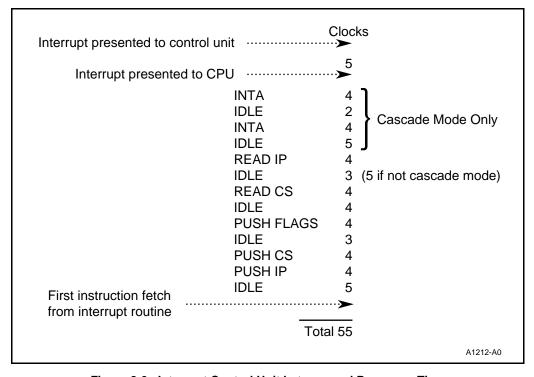

| 8-3    | Interrupt Control Unit Latency and Response Time             |      |

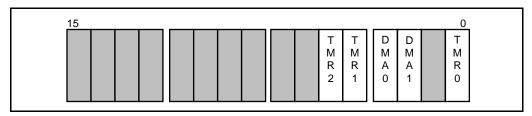

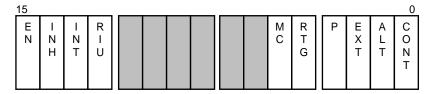

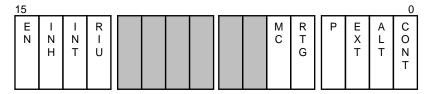

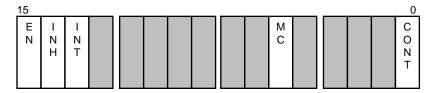

| 8-4    | Interrupt Control Register for Internal Sources              |      |

| 8-5    | Interrupt Control Register for Noncascadable External Pins   |      |

| 8-6    | Interrupt Control Register for Cascadable Interrupt Pins     |      |

| 8-7    | Interrupt Request Register                                   |      |

| 8-8    | Interrupt Mask Register                                      |      |

| 8-9    | Priority Mask Register                                       | 8-18 |

| 8-10   | In-Service Register                                          |      |

| 8-11   | Poll Register                                                |      |

| 8-12   | Poll Status Register                                         |      |

| 8-13   | End-of-Interrupt Register                                    |      |

| 8-14   | Interrupt Status Register                                    |      |

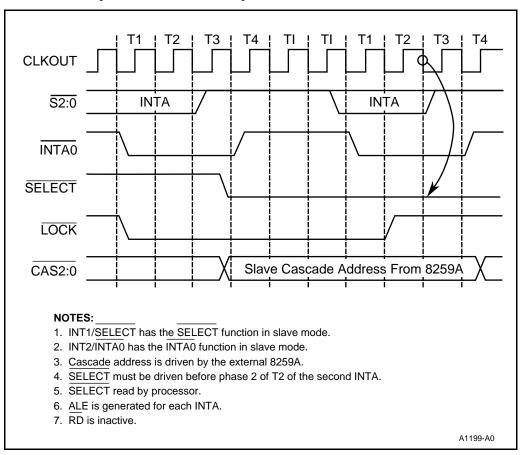

| 8-15   | Interrupt Control Unit in Slave Mode                         |      |

| 8-16   | Interrupt Sources in Slave Mode                              |      |

| 8-17   | Interrupt Vector Register (Slave Mode Only)                  |      |

| 8-18   | End-of-Interrupt Register in Slave Mode                      |      |

| 8-19   | Request, Mask, and In-Service Registers                      |      |

| 8-20   | Interrupt Vectoring in Slave Mode                            |      |

| 8-21   | Interrupt Response Time in Slave Mode                        |      |

| 9-1    | Timer/Counter Unit Block Diagram                             |      |

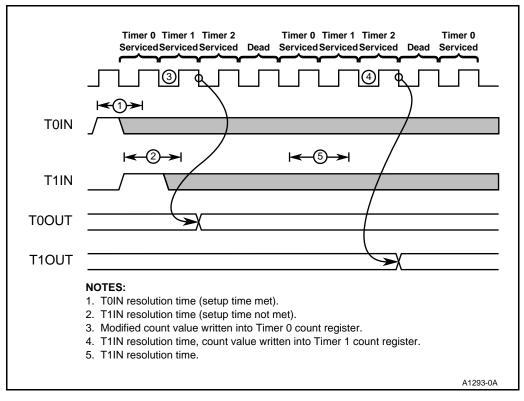

| 9-2    | Counter Element Multiplexing and Timer Input Synchronization |      |

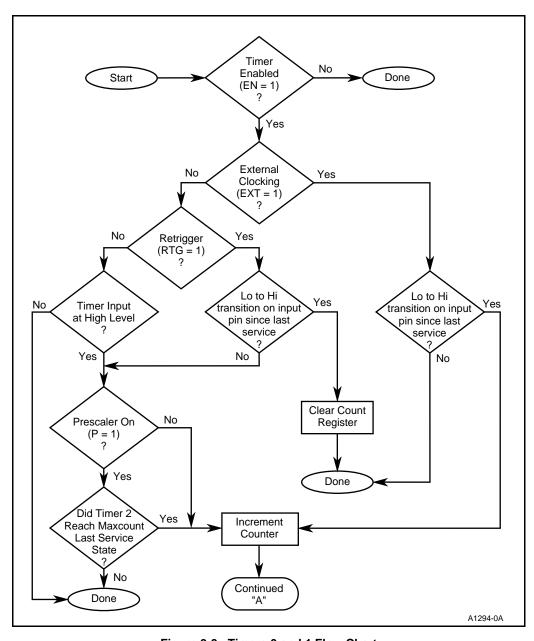

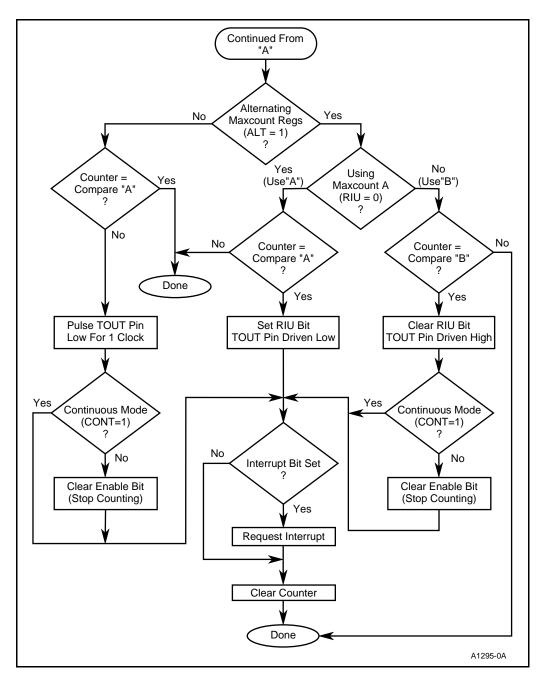

| 9-3    | Timers 0 and 1 Flow Chart                                    |      |

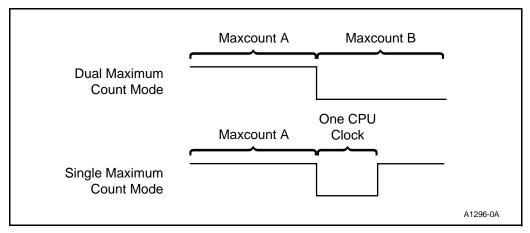

| 9-4    | Timer/Counter Unit Output Modes                              |      |

| 9-5    | Timer 0 and Timer 1 Control Registers                        |      |

| 9-6    | Timer 2 Control Register                                     |      |

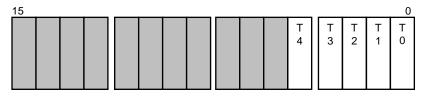

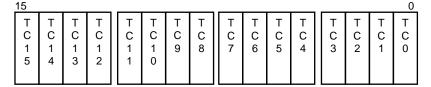

| 9-7    | Timer Count Registers                                        |      |

| 9-8    | Timer Maxcount Compare Registers                             |      |

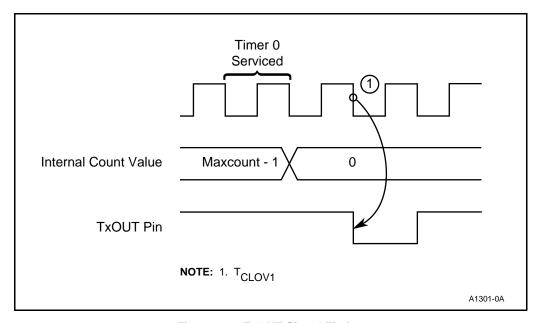

| 9-9    | TxOUT Signal Timing                                          |      |

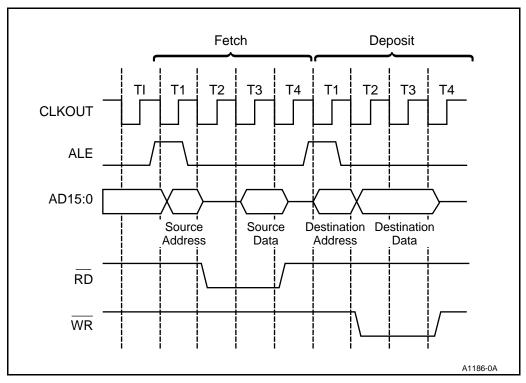

| 10-1   | Typical DMA Transfer                                         |      |

| 10-2   | DMA Request Minimum Response Time                            | 10-4 |

| <b>Figure</b> |                                                        | Page  |

|---------------|--------------------------------------------------------|-------|

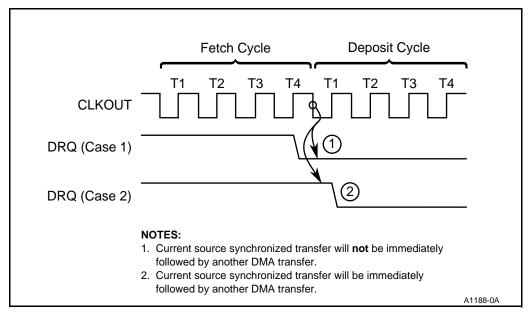

| 10-3          | Source-Synchronized Transfers                          | 10-5  |

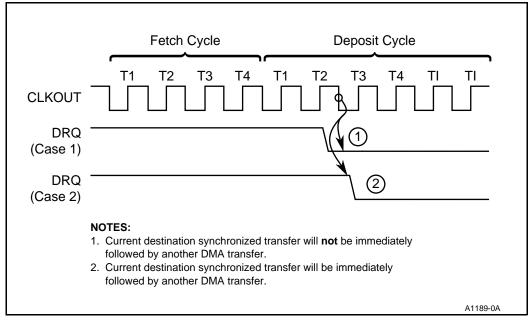

| 10-4          | Destination-Synchronized Transfers                     | 10-6  |

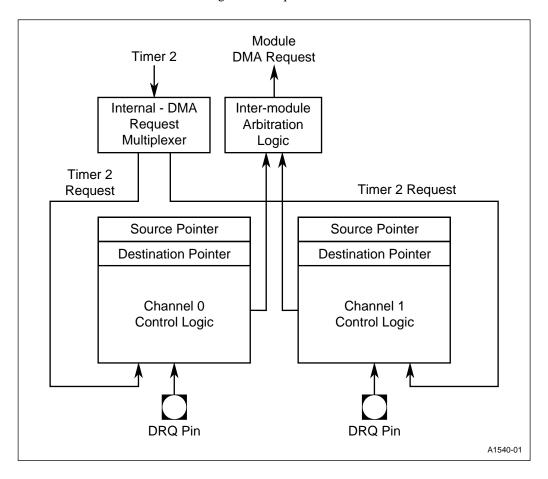

| 10-5          | Two-Channel DMA Module                                 | 10-9  |

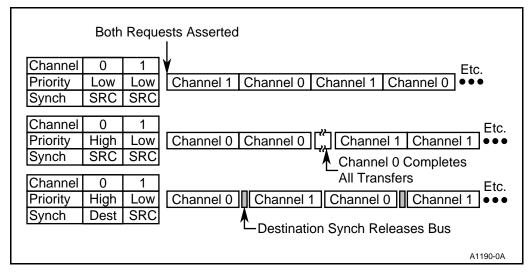

| 10-6          | Examples of DMA Priority                               | 10-10 |

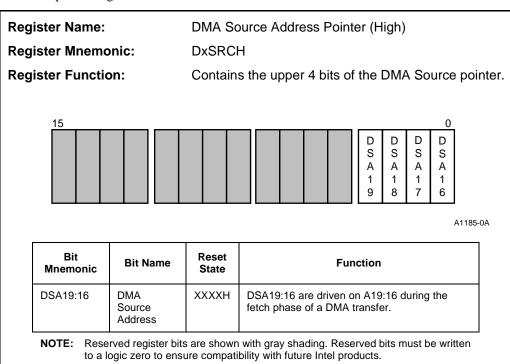

| 10-7          | DMA Source Pointer (High-Order Bits)                   | 10-11 |

| 10-8          | DMA Source Pointer (Low-Order Bits)                    | 10-12 |

| 10-9          | DMA Destination Pointer (High-Order Bits)              | 10-13 |

| 10-10         | DMA Destination Pointer (Low-Order Bits)               | 10-14 |

| 10-11         | DMA Control Register                                   | 10-15 |

| 10-12         | Transfer Count Register                                |       |

| 11-1          | 80C187-Supported Data Types                            | 11-8  |

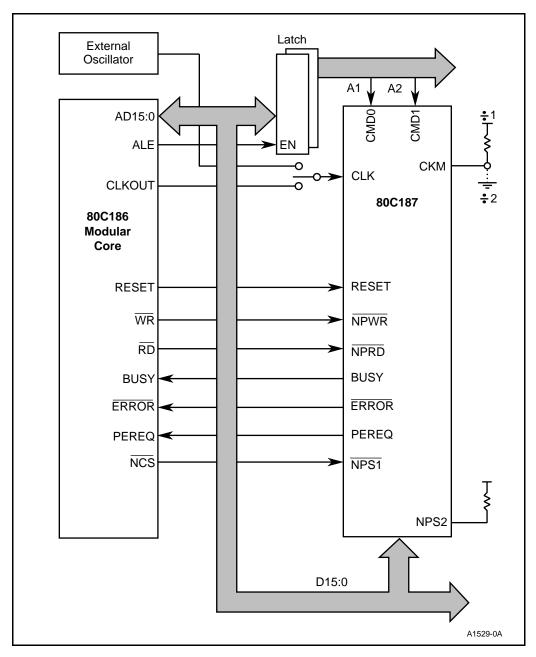

| 11-2          | 80C186 Modular Core Family/80C187 System Configuration | 11-9  |

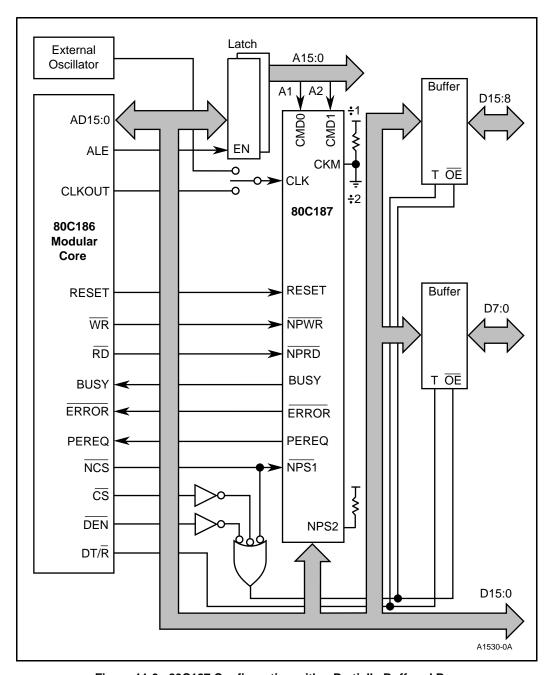

| 11-3          | 80C187 Configuration with a Partially Buffered Bus     | 11-12 |

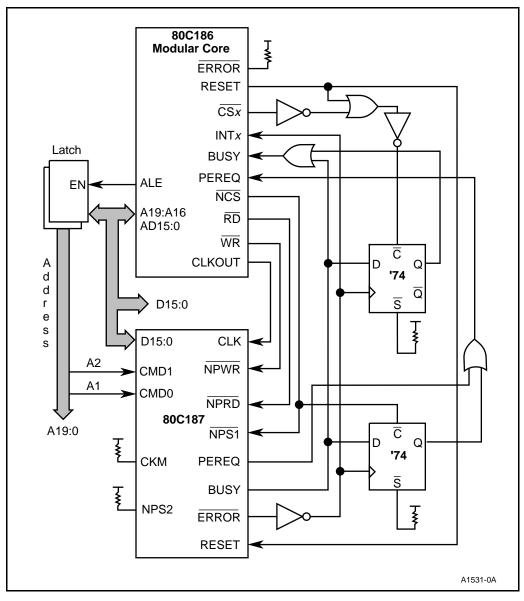

| 11-4          | 80C187 Exception Trapping via Processor Interrupt Pin  | 11-14 |

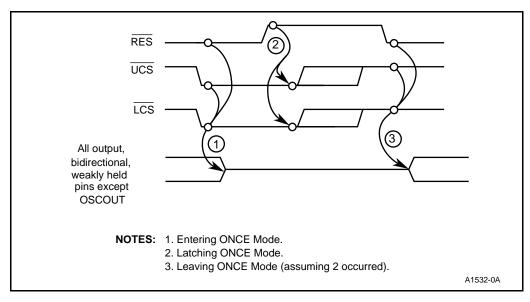

| 12-1          | Entering/Leaving ONCE Mode                             | 12-2  |

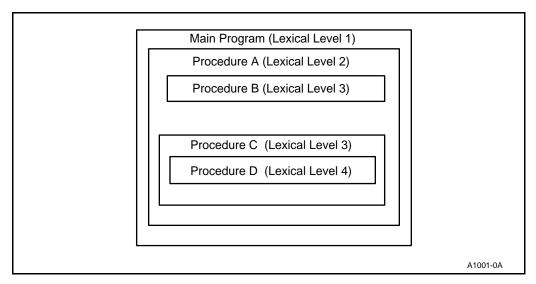

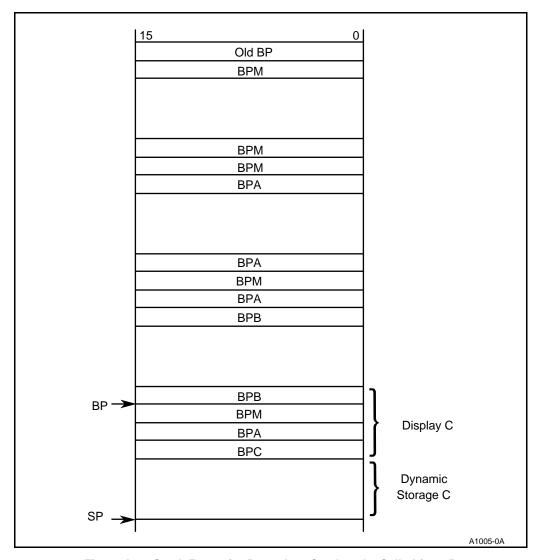

| A-1           | Formal Definition of ENTER                             | A-3   |

| A-2           | Variable Access in Nested Procedures                   | A-4   |

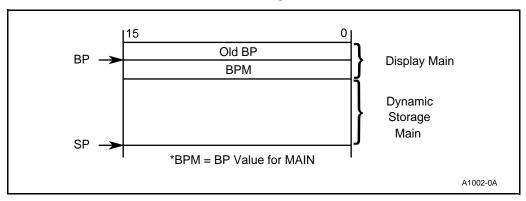

| A-3           | Stack Frame for Main at Level 1                        | A-4   |

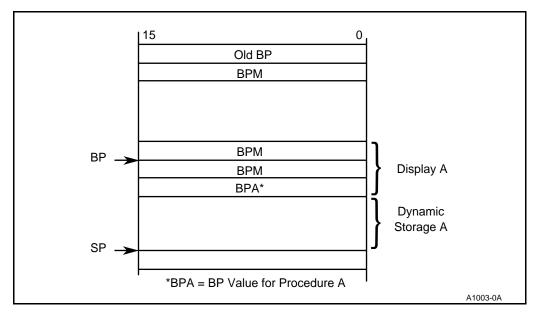

| A-4           | Stack Frame for Procedure A at Level 2                 |       |

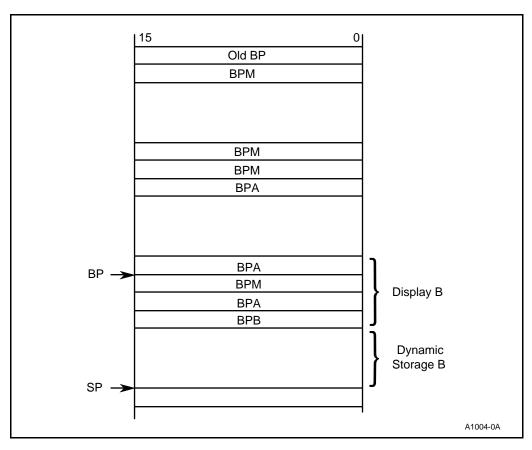

| A-5           | Stack Frame for Procedure B at Level 3 Called from A   | A-6   |

| A-6           | Stack Frame for Procedure C at Level 3 Called from B   | A-7   |

| B-1           | Input Synchronization Circuit                          | B-1   |

|               |                                                        |       |

#### **TABLES**

| Table |                                                                       | Page  |

|-------|-----------------------------------------------------------------------|-------|

| 1-1   | Comparison of 80C186 Modular Core Family Products                     | 1-2   |

| 1-2   | Related Documents and Software                                        |       |

| 2-1   | Implicit Use of General Registers                                     |       |

| 2-2   | Logical Address Sources                                               |       |

| 2-3   | Data Transfer Instructions                                            |       |

| 2-4   | Arithmetic Instructions                                               |       |

| 2-5   | Arithmetic Interpretation of 8-Bit Numbers                            |       |

| 2-6   | Bit Manipulation Instructions                                         |       |

| 2-7   | String Instructions                                                   |       |

| 2-8   | String Instruction Register and Flag Use                              |       |

| 2-9   | Program Transfer Instructions                                         |       |

| 2-10  | Interpretation of Conditional Transfers                               |       |

| 2-11  | Processor Control Instructions                                        |       |

| 2-12  | Supported Data Types                                                  |       |

| 3-1   | Bus Cycle Types                                                       |       |

| 3-2   | Read Bus Cycle Types                                                  |       |

| 3-3   | Read Cycle Critical Timing Parameters                                 |       |

| 3-4   | Write Bus Cycle Types                                                 |       |

| 3-5   | Write Cycle Critical Timing Parameters                                |       |

| 3-6   | HALT Bus Cycle Pin States                                             |       |

| 3-7   | Queue Status Signal Decoding                                          | 3-38  |

| 3-8   | Signal Condition Entering HOLD                                        | 3-40  |

| 4-1   | Peripheral Control Block                                              | 4-3   |

| 5-1   | Suggested Values for Inductor L1 in Third Overtone Oscillator Circuit | 5-4   |

| 6-1   | Chip-Select Unit Registers                                            | 6-6   |

| 6-2   | UCS Block Size and Starting Address                                   | 6-12  |

| 6-3   | LCS Active Range                                                      | 6-13  |

| 6-4   | MCS Active Range                                                      |       |

| 6-5   | MCS Block Size and Start Address Restrictions                         |       |

| 6-6   | PCS Active Range                                                      |       |

| 7-1   | Identification of Refresh Bus Cycles                                  |       |

| 8-1   | Default Interrupt Priorities                                          |       |

| 8-2   | Fixed Interrupt Types                                                 |       |

| 8-3   | Interrupt Control Unit Registers in Master Mode                       |       |

| 8-4   | Interrupt Control Unit Register Comparison                            |       |

| 8-5   | Slave Mode Fixed Interrupt Type Bits                                  |       |

| 9-1   | Timer 0 and 1 Clock Sources                                           |       |

| 9-2   | Timer Retriggering                                                    |       |

| 11-1  | 80C187 Data Transfer Instructions                                     |       |

| 11-2  | 80C187 Arithmetic Instructions                                        |       |

| 11-3  | 80C187 Comparison Instructions                                        |       |

| 11-4  | 80C187 Transcendental Instructions                                    |       |

| 11-5  | 80C187 Constant Instructions                                          |       |

| 11-6  | 80C187 Processor Control Instructions                                 |       |

| 11-7  | 80C187 I/O Port Assignments                                           | 11-10 |

#### **TABLES**

| Table |                                            | Page |

|-------|--------------------------------------------|------|

| C-1   | Instruction Format Variables               |      |

| C-2   | Instruction Operands                       |      |

| C-3   | Flag Bit Functions                         |      |

| C-4   | Instruction Set                            |      |

| D-1   | Operand Variables                          | D-1  |

| D-2   | Instruction Set Summary                    | D-2  |

| D-3   | Machine Instruction Decoding Guide         |      |

| D-4   | Mnemonic Encoding Matrix (Left Half)       |      |

| D-5   | Abbreviations for Mnemonic Encoding Matrix |      |

#### **EXAMPLES**

| Example |                                                            | Page  |

|---------|------------------------------------------------------------|-------|

| 5-1     | Initializing the Power Management Unit for Power-Save Mode | 5-14  |

| 6-1     | Initializing the Chip-Select Unit                          |       |

| 7-1     | Initializing the Refresh Control Unit                      | 7-11  |

| 8-1     | Initializing the Interrupt Control Unit for Master Mode    | 8-31  |

| 9-1     | Configuring a Real-Time Clock                              | 9-18  |

| 9-2     | Configuring a Square-Wave Generator                        |       |

| 9-3     | Configuring a Digital One-Shot                             |       |

| 10-1    | Initializing the DMA Unit                                  |       |

| 10-2    | Timed DMA Transfers                                        | 10-26 |

| 11-1    | Initialization Sequence for 80C187 Math Coprocessor        | 11-15 |

| 11-2    | Floating Point Math Routine Using FSINCOS                  | 11-16 |

1

## Introduction

## CHAPTER 1 INTRODUCTION

The 8086 microprocessor was first introduced in 1978 and gained rapid support as the microcomputer engine of choice. There are literally millions of 8086/8088-based systems in the world today. The amount of software written for the 8086/8088 is rivaled by no other architecture.

By the early 1980's, however, it was clear that a replacement for the 8086/8088 was necessary. An 8086/8088 system required dozens of support chips to implement even a moderately complex design. Intel recognized the need to integrate commonly used system peripherals onto the same silicon die as the CPU. In 1982 Intel addressed this need by introducing the 80186/80188 family of embedded microprocessors. The original 80186/80188 integrated an enhanced 8086/8088 CPU with six commonly used system peripherals. A parallel effort within Intel also gave rise to the 80286 microprocessor in 1982. The 80286 began the trend toward the very high performance Intel architecture that today includes the Intel386<sup>TM</sup>, Intel486<sup>TM</sup> and Pentium<sup>TM</sup> microprocessors.

As technology advanced and turned toward small geometry CMOS processes, it became clear that a new 80186 was needed. In 1987 Intel announced the second generation of the 80186 family: the 80C186/C188. The 80C186 family is pin compatible with the 80186 family, while adding an enhanced feature set. The high-performance CHMOS III process allowed the 80C186 to run at twice the clock rate of the NMOS 80186, while consuming less than one-fourth the power.

The 80186 family took another major step in 1990 with the introduction of the 80C186EB family. The 80C186EB heralded many changes for the 80186 family. First, the enhanced 8086/8088 CPU was redesigned as a static, stand-alone module known as the 80C186 Modular Core. Second, the 80186 family peripherals were also redesigned as static modules with standard interfaces. The goal behind this redesign effort was to give Intel the capability to proliferate the 80186 family rapidly, in order to provide solutions for an even wider range of customer applications.

The 80C186EB/C188EB was the first product to use the new modular capability. The 80C186EB/C188EB includes a different peripheral set than the original 80186 family. Power consumption was dramatically reduced as a direct result of the static design, power management features and advanced CHMOS IV process. The 80C186EB/C188EB has found acceptance in a wide array of portable equipment ranging from cellular phones to personal organizers.

In 1991 the 80C186 Modular Core family was again extended with the introduction of three new products: the 80C186XL, the 80C186EA and the 80C186EC. The 80C186XL/C188XL is a higher performance, lower power replacement for the 80C186/C188. The 80C186EA/C188EA combines the feature set of the 80C186 with new power management features for power-critical applications. The 80C186EC/C188EC offers the highest level of integration of any of the 80C186 Modular Core family products, with 14 on-chip peripherals (see Table 1-1).

#### INTRODUCTION

The 80C186 Modular Core family is the direct result of ten years of Intel development. It offers the designer the peace of mind of a well-established architecture with the benefits of state-of-the-art technology.

Table 1-1. Comparison of 80C186 Modular Core Family Products

| Feature                        | 80C186XL  | 80C186EA  | 80C186EB | 80C186EC           |

|--------------------------------|-----------|-----------|----------|--------------------|

| Enhanced 8086 Instruction Set  |           |           |          |                    |

| Low-Power Static Modular CPU   |           |           |          |                    |

| Power-Save (Clock Divide) Mode |           |           |          |                    |

| Powerdown and Idle Modes       |           |           |          |                    |

| 80C187 Interface               |           |           |          |                    |

| ONCE Mode                      |           |           |          |                    |

| Interrupt Control Unit         |           |           |          | 8259<br>Compatible |

| Timer/Counter Unit             |           |           |          |                    |

| Chip-Select Unit               |           |           | Enhanced | Enhanced           |

| DMA Unit                       | 2 Channel | 2 Channel |          | 4 Channel          |

| Serial Communications Unit     |           |           |          |                    |

| Refresh Control Unit           |           |           | Enhanced | Enhanced           |

| Watchdog Timer Unit            |           |           |          |                    |

| I/O Ports                      |           |           | 16 Total | 22 Total           |

#### 1.1 HOW TO USE THIS MANUAL

This manual uses phrases such as 80C186 Modular Core Family or 80C188 Modular Core, as well as references to specific products such as 80C188EA. Each phrase refers to a specific set of 80C186 family products. The phrases and the products they refer to are as follows:

**80C186 Modular Core Family:** This phrase refers to any device that uses the modular 80C186/C188 CPU core architecture. At this time these include the 80C186EA/C188EA, 80C186EB/C188EB, 80C186EC/C188EC and 80C186XL/C188XL.

**80C186 Modular Core:** Without the word *family*, this phrase refers only to the 16-bit bus members of the 80C186 Modular Core Family.

**80C188 Modular Core:** This phrase refers to the 8-bit bus products.

**80C188EC:** A specific product reference refers only to the named device. For example, *On the 80C188EC...* refers strictly to the 80C188EC and not to any other device.

Each chapter covers a specific section of the device, beginning with the CPU core. Each peripheral chapter includes programming examples intended to aid in your understanding of device operation. Please read the comments carefully, as not all of the examples include all the code necessary for a specific application.

This user's guide is a supplement to the device data sheet. Specific timing values are not discussed in this guide. When designing a system, always consult the most recent version of the device data sheet for up-to-date specifications.

#### 1.2 RELATED DOCUMENTS

The following table lists documents and software that are useful in designing systems that incorporate the 80C186 Modular Core Family. These documents are available through Intel Literature. To order a document, call the number listed for your area in "Product Literature" on page 1-7.

#### NOTE

If you will be transferring a design from the 80186/80188 or 80C186/80C188 to the 80C186XL/80C188XL, refer to FaxBack Document No. 2132.

Table 1-2. Related Documents and Software

| Document/Software Title                                                                                                                | Document<br>Order No. |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Embedded Microprocessors (includes 186 family data sheets)                                                                             | 272396                |

| 186 Embedded Microprocessor Line Card                                                                                                  | 272079                |

| 80186/80188 High-Integration 16-Bit Microprocessor Data Sheet                                                                          | 272430                |

| 80C186XL/C188XL-20, -12 16-Bit High-Integration Embedded Microprocessor Data Sheet                                                     | 272431                |

| 80C186EA/80C188EA-20, -12 and 80L186EA/80L188EA-13, -8 (low power versions) 16-Bit High-Integration Embedded Microprocessor Data Sheet | 272432                |

| 80C186EB/80C188EB-20, -13 and 80L186EB/80L188EB-13, -8 (low power versions) 16-Bit High-Integration Embedded Microprocessor Data Sheet | 272433                |

| 80C186EC/80C188EC-20, -13 and 80L186EC/80L188EC-13, -8 (low power versions) 16-Bit High-Integration Embedded Microprocessor Data Sheet | 272434                |

| 80C187 80-Bit Math Coprocessor Data Sheet                                                                                              | 270640                |

| Low Voltage Embedded Design                                                                                                            | 272324                |

| 80C186/C188, 80C186XL/C188XL Microprocessor User's Manual                                                                              | 272164                |

| 80C186EA/80C188EA Microprocessor User's Manual                                                                                         | 270950                |

| 80C186EB/80C188EB Microprocessor User's Manual                                                                                         | 270830                |

| 80C186EC/80C188EC Microprocessor User's Manual                                                                                         | 272047                |

| 8086/8088/8087/80186/80188 Programmer's Pocket Reference Guide                                                                         | 231017                |

| 8086/8088 User's Manual Programmer's and Hardware Reference Manual                                                                     | 240487                |

Table 1-2. Related Documents and Software (Continued)

| Document/Software Title   | Document<br>Order No. |

|---------------------------|-----------------------|

| ApBUILDER Software        | 272216                |

| 80C186EA Hypertext Manual | 272275                |

| 80C186EB Hypertext Manual | 272296                |

| 80C186EC Hypertext Manual | 272298                |

| 80C186XL Hypertext Manual | 272630                |

| ZCON - Z80 Code Converter | Available on BBS      |

#### 1.3 ELECTRONIC SUPPORT SYSTEMS

Intel's FaxBack\* service and application BBS provide up-to-date technical information. Intel also maintains several forums on CompuServe and offers a variety of information on the World Wide Web. These systems are available 24 hours a day, 7 days a week, providing technical information whenever you need it.

#### 1.3.1 FaxBack Service

FaxBack is an on-demand publishing system that sends documents to your fax machine. You can get product announcements, change notifications, product literature, device characteristics, design recommendations, and quality and reliability information from FaxBack 24 hours a day, 7 days a week.

1-800-628-2283 U.S. and Canada

916-356-3105 U.S., Canada, Japan, APac

44(0)1793-496646 Europe

Think of the FaxBack service as a library of technical documents that you can access with your phone. Just dial the telephone number and respond to the system prompts. After you select a document, the system sends a copy to your fax machine.

Each document has an order number and is listed in a subject catalog. The first time you use Fax-Back, you should order the appropriate subject catalogs to get a complete list of document order numbers. Catalogs are updated twice monthly. In addition, daily update catalogs list the title, status, and order number of each document that has been added, revised, or deleted during the past eight weeks. To recieve the update for a subject catalog, enter the subject catalog number followed by a zero. For example, for the complete microcontroller and flash catalog, request document number 2; for the daily update to the microcontroller and flash catalog, request document number 20.

The following catalogs and information are available at the time of publication:

- 1. Solutions OEM subscription form

- 2. Microcontroller and flash catalog

- 3. Development tools catalog

- 4. Systems catalog

- 5. Multimedia catalog

- 6. Multibus and iRMX® software catalog and BBS file listings

- 7. Microprocessor, PCI, and peripheral catalog

- 8. Quality and reliability and change notification catalog

- 9. iAL (Intel Architecture Labs) technology catalog

#### 1.3.2 Bulletin Board System (BBS)

The bulletin board system (BBS) lets you download files to your computer. The application BBS has the latest *ApBUILDER* software, hypertext manuals and datasheets, software drivers, firmware upgrades, application notes and utilities, and quality and reliability data.

916-356-3600 U.S., Canada, Japan, APac (up to 19.2 Kbaud) 916-356-7209 U.S., Canada, Japan, APac (2400 baud only)

44(0)1793-496340 Europe

The toll-free BBS (available in the U.S. and Canada) offers lists of documents available from FaxBack, a master list of files available from the application BBS, and a BBS user's guide. The BBS file listing is also available from FaxBack (catalog number 6; see page 1-4 for phone numbers and a description of the FaxBack service).

1-800-897-2536 U.S. and Canada only

Any customer with a modem and computer can access the BBS. The system provides automatic configuration support for 1200- through 19200-baud modems. Typical modem settings are 14400 baud, no parity, 8 data bits, and 1 stop bit (14400, N, 8, 1).

To access the BBS, just dial the telephone number and respond to the system prompts. During your first session, the system asks you to register with the system operator by entering your name and location. The system operator will set up your access account within 24 hours. At that time, you can access the files on the BBS.

#### NOTE

If you encounter any difficulty accessing the high-speed modem, try the dedicated 2400-baud modem. Use these modem settings: 2400, N, 8, 1.

#### 1.3.2.1 How to Find ApBUILDER Software and Hypertext Documents on the BBS

The latest ApBUILDER files and hypertext manuals and data sheets are available first from the BBS. To access the files, complete these steps:

- 1. Type **F** from the BBS Main menu. The BBS displays the Intel Apps Files menu.

- 2. Type **L** and press <Enter>. The BBS displays the list of areas and prompts for the area number.

- 3. Type **25** and press <Enter> to select *ApBUILDER*/Hypertext. The BBS displays several options: one for *ApBUILDER* software and the others for hypertext documents for specific product families.

- 4. Type **1** and press <Enter> to list the latest *ApBUILDER* files, or type the number of the appropriate product family sublevel and press <Enter> for a list of available hypertext manuals and datasheets.

- 5. Type the file numbers to select the files you wish to download (for example, **1,6** for files 1 and 6 or **3-7** for files 3, 4, 5, 6, and 7) and press <Enter>. The BBS displays the approximate time required to download the selected files and gives you the option to download them.

#### 1.3.3 CompuServe Forums

The CompuServe forums provide a means for you to gather information, share discoveries, and debate issues. Type "go intel" for access. For information about CompuServe access and service fees, call CompuServe at 1-800-848-8199 (U.S.) or 614-529-1340 (outside the U.S.).

#### 1.3.4 World Wide Web

Intel offers a variety of information through the World Wide Web (http://www.intel.com/). Select "Embedded Design Products" from the Intel home page.

#### 1.4 TECHNICAL SUPPORT

In the U.S. and Canada, technical support representatives are available to answer your questions between 5 a.m. and 5 p.m. PST. You can also fax your questions to us. (Please include your voice telephone number and indicate whether you prefer a response by phone or by fax). Outside the U.S. and Canada, please contact your local distributor.

1-800-628-8686 U.S. and Canada 916-356-7599 U.S. and Canada 916-356-6100 (fax) U.S. and Canada

#### 1.5 PRODUCT LITERATURE

You can order product literature from the following Intel literature centers.

1-800-468-8118, ext. 283 U.S. and Canada

708-296-9333 U.S. (from overseas)

44(0)1793-431155 Europe (U.K.) 44(0)1793-421333 Germany

44(0)1793-421777 France

81(0)120-47-88-32 Japan (fax only)

#### 1.6 TRAINING CLASSES

In the U.S. and Canada, you can register for training classes through the Intel customer training center. Classes are held in the U.S.

1-800-234-8806 U.S. and Canada

# Overview of the 80C186 Family Architecture

## OVERVIEW OF THE 80C186 FAMILY ARCHITECTURE

The 80C186 Modular Microprocessor Core shares a common base architecture with the 8086, 8088, 80186, 80188, 80286, Intel386<sup>TM</sup> and Intel486<sup>TM</sup> processors. The 80C186 Modular Core maintains full object-code compatibility with the 8086/8088 family of 16-bit microprocessors, while adding hardware and software performance enhancements. Most instructions require fewer clocks to execute on the 80C186 Modular Core because of hardware enhancements in the Bus Interface Unit and the Execution Unit. Several additional instructions simplify programming and reduce code size (see Appendix A, "80C186 Instruction Set Additions and Extensions").

#### 2.1 ARCHITECTURAL OVERVIEW

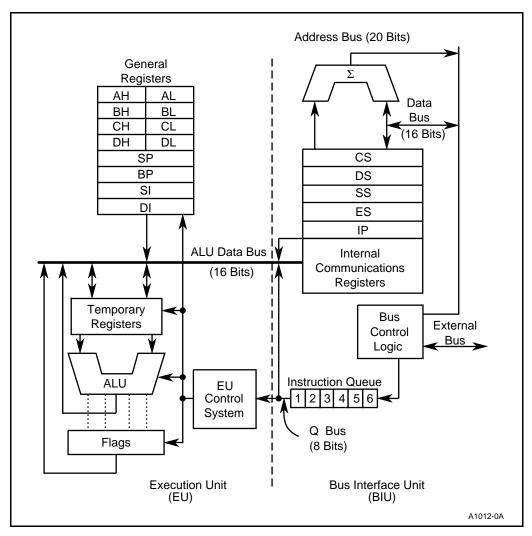

The 80C186 Modular Microprocessor Core incorporates two separate processing units: an Execution Unit (EU) and a Bus Interface Unit (BIU). The Execution Unit is functionally identical among all family members. The Bus Interface Unit is configured for a 16-bit external data bus for the 80C186 core and an 8-bit external data bus for the 80C188 core. The two units interface via an instruction prefetch queue.

The Execution Unit executes instructions; the Bus Interface Unit fetches instructions, reads operands and writes results. Whenever the Execution Unit requires another opcode byte, it takes the byte out of the prefetch queue. The two units can operate independently of one another and are able, under most circumstances, to overlap instruction fetches and execution.

The 80C186 Modular Core family has a 16-bit Arithmetic Logic Unit (ALU). The Arithmetic Logic Unit performs 8-bit or 16-bit arithmetic and logical operations. It provides for data movement between registers, memory and I/O space.

The 80C186 Modular Core family CPU allows for high-speed data transfer from one area of memory to another using string move instructions and between an I/O port and memory using block I/O instructions. The CPU also provides many conditional branch and control instructions.

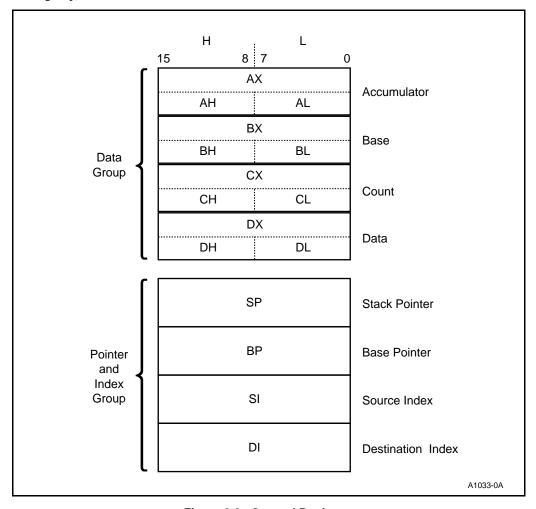

The 80C186 Modular Core architecture features 14 basic registers grouped as general registers, segment registers, pointer registers and status and control registers. The four 16-bit general-purpose registers (AX, BX, CX and DX) can be used as operands for most arithmetic operations as either 8- or 16-bit units. The four 16-bit pointer registers (SI, DI, BP and SP) can be used in arithmetic operations and in accessing memory-based variables. Four 16-bit segment registers (CS, DS, SS and ES) allow simple memory partitioning to aid modular programming. The status and control registers consist of an Instruction Pointer (IP) and the Processor Status Word (PSW) register, which contains flag bits. Figure 2-1 is a simplified CPU block diagram.

Figure 2-1. Simplified Functional Block Diagram of the 80C186 Family CPU

#### 2.1.1 Execution Unit

The Execution Unit executes all instructions, provides data and addresses to the Bus Interface Unit and manipulates the general registers and the Processor Status Word. The 16-bit ALU within the Execution Unit maintains the CPU status and control flags and manipulates the general registers and instruction operands. All registers and data paths in the Execution Unit are 16 bits wide for fast internal transfers.

#### **OVERVIEW OF THE 80C186 FAMILY ARCHITECTURE**

The Execution Unit does not connect directly to the system bus. It obtains instructions from a queue maintained by the Bus Interface Unit. When an instruction requires access to memory or a peripheral device, the Execution Unit requests the Bus Interface Unit to read and write data. Addresses manipulated by the Execution Unit are 16 bits wide. The Bus Interface Unit, however, performs an address calculation that allows the Execution Unit to access the full megabyte of memory space.

To execute an instruction, the Execution Unit must first fetch the object code byte from the instruction queue and then execute the instruction. If the queue is empty when the Execution Unit is ready to fetch an instruction byte, the Execution Unit waits for the Bus Interface Unit to fetch the instruction byte.

#### 2.1.2 Bus Interface Unit

The 80C186 Modular Core and 80C188 Modular Core Bus Interface Units are functionally identical. They are implemented differently to match the structure and performance characteristics of their respective system buses. The Bus Interface Unit executes all external bus cycles. This unit consists of the segment registers, the Instruction Pointer, the instruction code queue and several miscellaneous registers. The Bus Interface Unit transfers data to and from the Execution Unit on the ALU data bus.

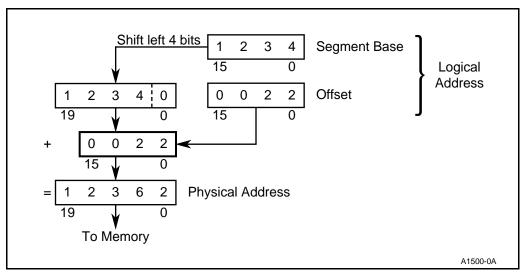

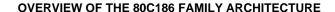

The Bus Interface Unit generates a 20-bit physical address in a dedicated adder. The adder shifts a 16-bit segment value left 4 bits and then adds a 16-bit offset. This offset is derived from combinations of the pointer registers, the Instruction Pointer and immediate values (see Figure 2-2). Any carry from this addition is ignored.

Figure 2-2. Physical Address Generation

During periods when the Execution Unit is busy executing instructions, the Bus Interface Unit sequentially prefetches instructions from memory. As long as the prefetch queue is partially full, the Execution Unit fetches instructions.

#### 2.1.3 General Registers

The 80C186 Modular Core family CPU has eight 16-bit general registers (see Figure 2-3). The general registers are subdivided into two sets of four registers. These sets are the data registers (also called the H & L group for high and low) and the pointer and index registers (also called the P & I group).

Figure 2-3. General Registers

#### **OVERVIEW OF THE 80C186 FAMILY ARCHITECTURE**

The data registers can be addressed by their upper or lower halves. Each data register can be used interchangeably as a 16-bit register or two 8-bit registers. The pointer registers are always accessed as 16-bit values. The CPU can use data registers without constraint in most arithmetic and logic operations. Arithmetic and logic operations can also use the pointer and index registers. Some instructions use certain registers implicitly (see Table 2-1), allowing compact encoding.

Table 2-1. Implicit Use of General Registers

| Register | Operations                                                          |

|----------|---------------------------------------------------------------------|

| AX       | Word Multiply, Word Divide, Word I/O                                |

| AL       | Byte Multiply, Byte Divide, Byte I/O, Translate, Decimal Arithmetic |

| АН       | Byte Multiply, Byte Divide                                          |

| ВХ       | Translate                                                           |

| CX       | String Operations, Loops                                            |

| CL       | Variable Shift and Rotate                                           |

| DX       | Word Multiply, Word Divide, Indirect I/O                            |

| SP       | Stack Operations                                                    |

| SI       | String Operations                                                   |

| DI       | String Operations                                                   |

The contents of the general-purpose registers are undefined following a processor reset.

#### 2.1.4 Segment Registers

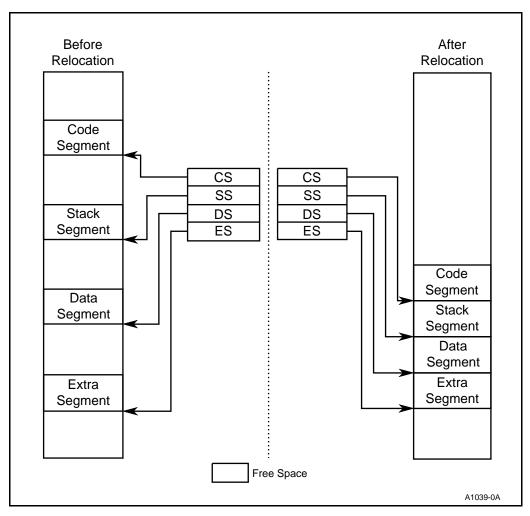

The 80C186 Modular Core family memory space is 1 Mbyte in size and divided into logical segments of up to 64 Kbytes each. The CPU has direct access to four segments at a time. The segment registers contain the base addresses (starting locations) of these memory segments (see Figure 2-4). The CS register points to the current code segment, which contains instructions to be fetched. The SS register points to the current stack segment, which is used for all stack operations. The DS register points to the current data segment, which generally contains program variables. The ES register points to the current extra segment, which is typically used for data storage. The CS register initializes to 0FFFFH, and the SS, DS and ES registers initialize to 0000H. Programs can access and manipulate the segment registers with several instructions.

Figure 2-4. Segment Registers

#### 2.1.5 Instruction Pointer

The Bus Interface Unit updates the 16-bit Instruction Pointer (IP) register so it contains the offset of the next instruction to be fetched. Programs do not have direct access to the Instruction Pointer, but it can change, be saved or be restored as a result of program execution. For example, if the Instruction Pointer is saved on the stack, it is first automatically adjusted to point to the next instruction to be executed.

Reset initializes the Instruction Pointer to 0000H. The CS and IP values comprise a starting execution address of 0FFFF0H (see "Logical Addresses" on page 2-10 for a description of address formation).

#### **OVERVIEW OF THE 80C186 FAMILY ARCHITECTURE**

#### 2.1.6 Flags

The 80C186 Modular Core family has six status flags (see Figure 2-5) that the Execution Unit posts as the result of arithmetic or logical operations. Program branch instructions allow a program to alter its execution depending on conditions flagged by a prior operation. Different instructions affect the status flags differently, generally reflecting the following states:

- If the Auxiliary Flag (AF) is set, there has been a carry out from the low nibble into the high nibble or a borrow from the high nibble into the low nibble of an 8-bit quantity (low-order byte of a 16-bit quantity). This flag is used by decimal arithmetic instructions.

- If the Carry Flag (CF) is set, there has been a carry out of or a borrow into the high-order bit of the instruction result (8- or 16-bit). This flag is used by instructions that add or subtract multibyte numbers. Rotate instructions can also isolate a bit in memory or a register by placing it in the Carry Flag.

- If the Overflow Flag (OF) is set, an arithmetic overflow has occurred. A significant digit

has been lost because the size of the result exceeded the capacity of its destination location.

An Interrupt On Overflow instruction is available that will generate an interrupt in this

situation.

- If the Sign Flag (SF) is set, the high-order bit of the result is a 1. Since negative binary numbers are represented in standard two's complement notation, SF indicates the sign of the result (0 = positive, 1 = negative).

- If the Parity Flag (PF) is set, the result has even parity, an even number of 1 bits. This flag can be used to check for data transmission errors.

- If the Zero Flag (ZF) is set, the result of the operation is zero.

Additional control flags (see Figure 2-5) can be set or cleared by programs to alter processor operations:

- Setting the Direction Flag (DF) causes string operations to auto-decrement. Strings are processed from high address to low address (or "right to left"). Clearing DF causes string operations to auto-increment. Strings are processed from low address to high address (or "left to right").

- Setting the Interrupt Enable Flag (IF) allows the CPU to recognize maskable external or internal interrupt requests. Clearing IF disables these interrupts. The Interrupt Enable Flag has no effect on software interrupts or non-maskable interrupts.

- Setting the Trap Flag (TF) bit puts the processor into single-step mode for debugging. In this mode, the CPU automatically generates an interrupt after each instruction. This allows a program to be inspected instruction by instruction during execution.

The status and control flags are contained in a 16-bit Processor Status Word (see Figure 2-5). Reset initializes the Processor Status Word to 0F000H.

## 2.1.7 Memory Segmentation

Programs for the 80C186 Modular Core family view the 1 Mbyte memory space as a group of user-defined segments. A segment is a logical unit of memory that can be up to 64 Kbytes long. Each segment is composed of contiguous memory locations. Segments are independent and separately addressable. Software assigns every segment a base address (starting location) in memory space. All segments begin on 16-byte memory boundaries. There are no other restrictions on segment locations. Segments can be adjacent, disjoint, partially overlapped or fully overlapped (see Figure 2-6). A physical memory location can be mapped into (covered by) one or more logical segments.

Register Name: Processor Status Word

**Register Mnemonic:** PSW (FLAGS)

**Register Function:** Posts CPU status information.

A1035-0A

| Bit<br>Mnemonic | Bit Name                 | Reset<br>State                                      | Function                                                                                                                                                              |  |

|-----------------|--------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OF              | Overflow Flag            | 0                                                   | If OF is set, an arithmetic overflow has occurred.                                                                                                                    |  |

| DF              | Direction Flag           | 0                                                   | If DF is set, string instructions are processed high address to low address. If DF is clear, strings are processed low address to high address.                       |  |

| IF              | Interrupt<br>Enable Flag | 0                                                   | If IF is set, the CPU recognizes maskable interrupt requests. If IF is clear, maskable interrupts are ignored.                                                        |  |

| TF              | Trap Flag                | 0                                                   | If TF is set, the processor enters single-step mode.                                                                                                                  |  |

| SF              | Sign Flag                | 0                                                   | If SF is set, the high-order bit of the result of an operation is 1, indicating it is negative.                                                                       |  |

| ZF              | Zero Flag                | 0 If ZF is set, the result of an operation is zero. |                                                                                                                                                                       |  |

| AF              | Auxiliary Flag           | 0                                                   | If AF is set, there has been a carry from the low nibble to the high or a borrow from the high nibble to the low nibble of an 8-bit quantity. Used in BCD operations. |  |

| PF              | Parity Flag              | 0                                                   | If PF is set, the result of an operation has even parity.                                                                                                             |  |

| CF              | Carry Flag               | 0                                                   | If CF is set, there has been a carry out of, or a borrow into, the high-order bit of the result of an instruction.                                                    |  |

**NOTE**: Reserved register bits are shown with gray shading. Reserved bits must be written to a logic zero to ensure compatibility with future Intel products.

Figure 2-5. Processor Status Word

Figure 2-6. Segment Locations in Physical Memory

The four segment registers point to four "currently addressable" segments (see Figure 2-7). The currently addressable segments provide a work space consisting of 64 Kbytes for code, a 64 Kbytes for stack and 128 Kbytes for data storage. Programs access code and data in another segment by updating the segment register to point to the new segment.

# 2.1.8 Logical Addresses

It is useful to think of every memory location as having two kinds of addresses, physical and logical. A physical address is a 20-bit value that identifies a unique byte location in the memory space. Physical addresses range from 0H to 0FFFFFH. All exchanges between the CPU and memory use physical addresses.

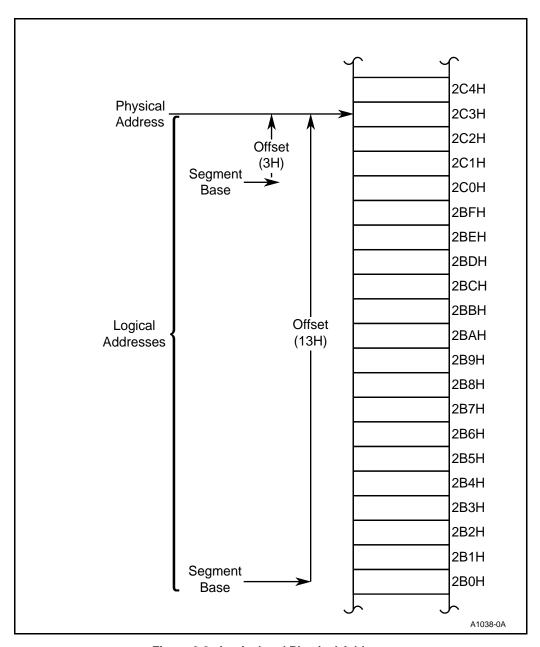

Programs deal with logical rather than physical addresses. Program code can be developed without prior knowledge of where the code will be located in memory. A logical address consists of a segment base value and an offset value. For any given memory location, the segment base value locates the first byte of the segment. The offset value represents the distance, in bytes, of the target location from the beginning of the segment. Segment base and offset values are unsigned 16-bit quantities. Many different logical addresses can map to the same physical location. In Figure 2-8, physical memory location 2C3H is contained in two different overlapping segments, one beginning at 2B0H and the other at 2C0H.

Figure 2-7. Currently Addressable Segments

The segment register is automatically selected according to the rules in Table 2-2. All information in one segment type generally shares the same logical attributes (e.g., code or data). This leads to programs that are shorter, faster and better structured.

The Bus Interface Unit must obtain the logical address before generating the physical address. The logical address of a memory location can come from different sources, depending on the type of reference that is being made (see Table 2-2).

Segment registers always hold the segment base addresses. The Bus Interface Unit determines which segment register contains the base address according to the type of memory reference made. However, the programmer can explicitly direct the Bus Interface Unit to use any currently addressable segment (except for the destination operand of a string instruction). In assembly language, this is done by preceding an instruction with a segment override prefix.

Figure 2-8. Logical and Physical Address

| Type of Memory Reference    | Default<br>Segment Base | Alternate<br>Segment Base | Offset            |

|-----------------------------|-------------------------|---------------------------|-------------------|

| Instruction Fetch           | CS                      | NONE                      | IP                |

| Stack Operation             | SS                      | NONE                      | SP                |