# Intel<sup>®</sup> Compute Module MFS2600KI

**Technical Product Specification**

Intel order number: G51989-002

**Revision 1.0**

June, 2012

**Enterprise Platforms and Services Division**

## **Revision History**

| Date        | Revision<br>Number | Modifications               |

|-------------|--------------------|-----------------------------|

| April, 2012 | 0.5                | Initial release.            |

| June, 2012  | 1.0                | Corrected BMC LAN settings. |

## Disclaimers

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel<sup>®</sup>'s Terms and Conditions of Sale for such products, Intel<sup>®</sup> assumes no liability whatsoever, and Intel<sup>®</sup> disclaims any express or implied warranty, relating to sale and/or use of Intel<sup>®</sup> products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel<sup>®</sup> products are not intended for use in medical, lifesaving, or life sustaining applications. Intel<sup>®</sup> may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel<sup>®</sup> reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> Compute Module MFS2600KI may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel Corporation server baseboards support peripheral components and contain a number of high-density VLSI and power delivery components that need adequate airflow to cool. Intel<sup>®</sup>'s own chassis are designed and tested to meet the intended thermal requirements of these components when the fully integrated system is used together. It is the responsibility of the system integrator that chooses not to use Intel<sup>®</sup> developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of air flow required for their specific application and environmental conditions. Intel Corporation cannot be held responsible if components fail or the compute module does not operate correctly when used outside any of their published operating or non-operating limits.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2012.

# Table of Contents

| 1. | Introduc | tion                                                                                     | .1 |

|----|----------|------------------------------------------------------------------------------------------|----|

| 1  | .1       | Chapter Outline                                                                          | .1 |

| 2. | Product  | Overview                                                                                 | .2 |

| 2  | 2.1      | Intel <sup>®</sup> Compute Module MFS2600KI Feature Set                                  | .2 |

| 2  | 2.2      | Compute Module Layout                                                                    | .3 |

|    | 2.2.1    | Connector and Component Locations                                                        | .3 |

|    | 2.2.2    | External I/O Connector Locations                                                         | .4 |

| 3. | Functio  | nal Architecture                                                                         | .5 |

| З  | 5.1      | Intel <sup>®</sup> Xeon <sup>®</sup> processor                                           | .5 |

|    | 3.1.1    | Processor Support                                                                        | .5 |

|    | 3.1.2    | Processor Initialization Error Summary                                                   | .7 |

| З  | 3.2      | Processor Functions Overview                                                             | .9 |

|    | 3.2.1    | Intel® QuickPath Interconnect                                                            | 10 |

|    | 3.2.2    | Intel® Hyper-Threading Technology                                                        | 10 |

| З  | 5.3      | Processor Integrated I/O Module (IIO)                                                    | 10 |

|    | 3.3.1    | PCI Express Interfaces                                                                   | 10 |

|    | 3.3.2    | DMI2 Interface to the PCH                                                                | 11 |

|    | 3.3.3    | Integrated IOAPIC                                                                        | 11 |

|    | 3.3.4    | Intel <sup>®</sup> QuickData Technology                                                  | 11 |

| З  | 3.4      | Memory Subsystem                                                                         | 11 |

|    | 3.4.1    | Integrated Memory Controller (IMC) and Memory Subsystem                                  | 11 |

|    | 3.4.2    | Publishing Compute Module Memory                                                         | 15 |

|    | 3.4.3    | Memory Map and Population Rules                                                          | 15 |

|    | 3.4.4    | Memory RAS                                                                               | 19 |

| З  | 5.5      | Intel <sup>®</sup> C602-J Chipset Overvew                                                |    |

|    | 3.5.1    | Digital Media Interface (DMI)                                                            | 21 |

|    | 3.5.2    | PCI Express* Interface                                                                   | 21 |

|    | 3.5.3    | Serial ATA (SATA) Controller                                                             | 21 |

|    | 3.5.4    | Low Pin Count (LPC) Interface                                                            | 21 |

|    | 3.5.5    | Serial Peripheral Interface (SPI)                                                        |    |

|    | 3.5.6    | Advanced Programmable Interrupt Controller (APIC)                                        |    |

|    | 3.5.7    | Universal Serial Bus (USB) Controllers                                                   | 22 |

| 3  | 6.6      | Integrated Baseboard Management Controller Overview2                                     | 22 |

|    | 3.6.1    | Super I/O Controller                                                                     | 22 |

|    | 3.6.2    | Graphics Controller and Video Support                                                    |    |

|    | 3.6.3    | Baseboard Management Controller                                                          |    |

|    | 5.7      | Network Interface Controller (NIC)                                                       |    |

| З  | 8.8      | Intel <sup>®</sup> Virtualization Technology for Directed I/O (Intel <sup>®</sup> VT-d)2 | 26 |

| 4.  | System                                                         | Security                                          | 27 |  |  |  |

|-----|----------------------------------------------------------------|---------------------------------------------------|----|--|--|--|

| 4   | .1                                                             | BIOS Password Protection                          | 27 |  |  |  |

| 4   | .2                                                             | Trusted Platform Module (TPM) Support             | 28 |  |  |  |

|     | 4.2.1                                                          | TPM security BIOS                                 | 28 |  |  |  |

|     | 4.2.2                                                          | Physical Presence                                 | 29 |  |  |  |

|     | 4.2.3                                                          | TPM Security Setup Options                        | 29 |  |  |  |

| 4   | .3                                                             | Intel <sup>®</sup> Trusted Execution Technology   | 30 |  |  |  |

| 5.  | Connect                                                        | tor/Header Locations and Pin-outs                 | 31 |  |  |  |

| 5   | .1                                                             | Board Connector Information                       | 31 |  |  |  |

| 5   | .2                                                             | Power Connectors                                  | 31 |  |  |  |

| 5   | .3                                                             | I/O Connector Pin-out Definition                  | 32 |  |  |  |

|     | 5.3.1                                                          | VGA Connector                                     | 32 |  |  |  |

|     | 5.3.2                                                          | I/O Mezzanine Card Connector                      | 32 |  |  |  |

|     | 5.3.3                                                          | Midplane Signal Connector                         | 36 |  |  |  |

|     | 5.3.4                                                          | Serial Port Connector                             | 37 |  |  |  |

|     | 5.3.5                                                          | USB 2.0 Connectors                                | 37 |  |  |  |

|     | 5.3.6                                                          | Low Profile eUSB SSD Support                      | 38 |  |  |  |

| 6.  | Jumper                                                         | Block Settings                                    | 39 |  |  |  |

| 6   | .1                                                             | CMOS Clear and Password Clear Usage Procedure     | 40 |  |  |  |

| 6   | .2                                                             | Integrated BMC Force Update Procedure             |    |  |  |  |

| 6   | .3                                                             | Integrated BMC Initialization                     | 41 |  |  |  |

| 6   | .4                                                             | ME Force Update Jumper                            | 41 |  |  |  |

| 6   | .5                                                             | BIOS Recovery Jumper                              | 42 |  |  |  |

| 7.  | Product                                                        | Regulatory Requirements                           | 43 |  |  |  |

| 7   | .1                                                             | Product Regulatory Requirements                   | 43 |  |  |  |

| 7   | .2                                                             | Product Regulatory Compliance and Safety Markings | 43 |  |  |  |

| 7   | .3                                                             | Product Environmental/Ecology Requirements        | 43 |  |  |  |

|     |                                                                | : Integration and Usage Tips                      |    |  |  |  |

|     |                                                                | : POST Code Diagnostic LED Decoder                |    |  |  |  |

|     |                                                                | : POST Error Code                                 |    |  |  |  |

|     | Appendix D: Supported Intel <sup>®</sup> Modular Server System |                                                   |    |  |  |  |

| Glo | lossary                                                        |                                                   |    |  |  |  |

| Ref | eference Documents60                                           |                                                   |    |  |  |  |

# List of Figures

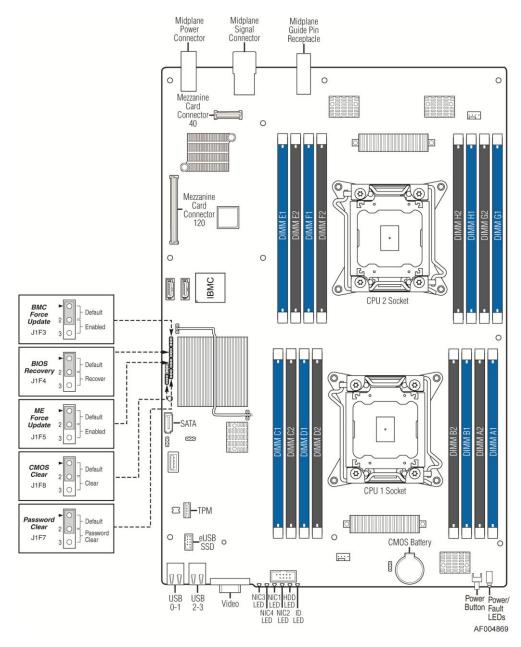

| Figure 1. Component and Connector Location Diagram                             | 3  |

|--------------------------------------------------------------------------------|----|

| Figure 2. Intel <sup>®</sup> Compute Module MFS2600KI Front Panel Layout       | 4  |

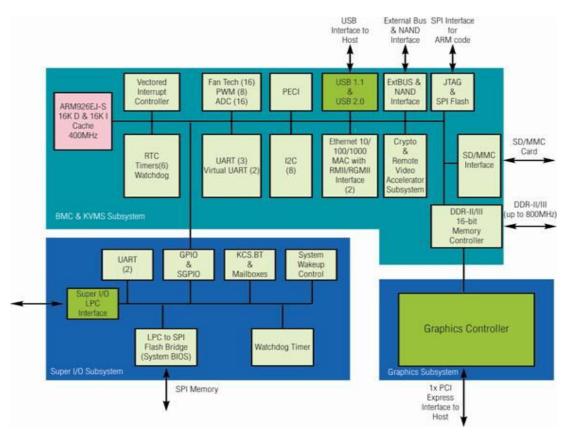

| Figure 3. Intel <sup>®</sup> Compute Module MFS2600KI Functional Block Diagram | 5  |

| Figure 4. Processor Socket Assembly                                            | 6  |

| Figure 5. Intergrated Memory Controller (IMC) and Memory Subsystem             | 11 |

| Figure 6. DIMM Slot Order                                                      | 18 |

| Figure 7. Integrated BMC Functional Block Diagram                              | 22 |

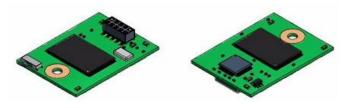

| Figure 8. eUSB SSD Support                                                     | 38 |

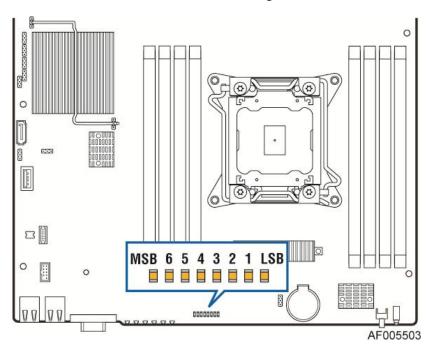

| Figure 9. Recovery Jumper Blocks                                               | 39 |

| Figure 10. POST Code Diagnostic LED Decoder                                    | 45 |

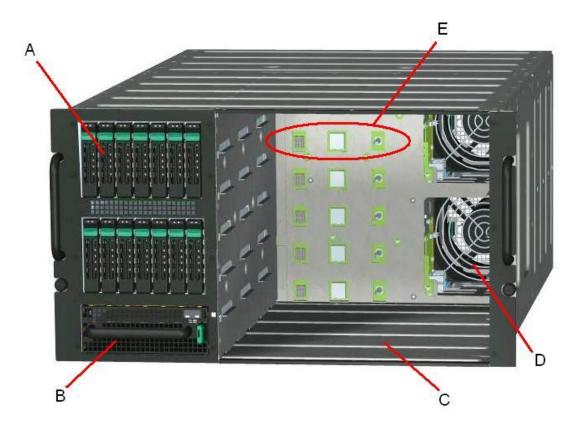

| Figure 11. Intel <sup>®</sup> Modular Server System MFSYS25V2                  | 56 |

# List of Tables

| Table 1. Intel <sup>®</sup> compute module MFS2600KI Feature Set                      | 2  |

|---------------------------------------------------------------------------------------|----|

| Table 2. Mixed Processor Configurations                                               | 8  |

| Table 3. Intel <sup>®</sup> Compute Module MFS2600KI PCIe Bus Segment Characteristics | 11 |

| Table 4. UDIMM Support Guidelines (Preliminary. Subject to Change)                    | 13 |

| Table 5. RDIMM Support Guidelines (Preliminary. Subject to Change)                    | 14 |

| Table 6. LRDIMM Support Guidelines (Preliminary. Subject to Change)                   | 14 |

| Table 7. DDR3 RDIMM Population within a Channel                                       | 16 |

| Table 8. DDR3L Low Voltage RDIMM Population within a Channel                          | 16 |

| Table 9. DDR3 UDIMM Population within a Channel                                       | 17 |

| Table 10. DDR3L Low Voltage UDIMM Poplulation within a Channel                        | 17 |

| Table 11. Intel <sup>®</sup> Compute Module MFS2600KI DIMM Nomenclature               | 18 |

| Table 12. Video Modes                                                                 | 23 |

| Table 13. Video mode                                                                  | 24 |

| Table 14. NIC LED BEHAVIOR                                                            | 25 |

| Table 15. Board Connector Matrix                                                      | 31 |

| Table 16. Power Connector Pin-out (J1A1)                                              | 31 |

| Table 17. VGA Connector Pin-out (J2K1)                                                | 32 |

| Table 18. 120-pin I/O Mezzanine Card Connector Pin-out                                | 33 |

| Table 19. 120-pin I/O Mezzanine Card Connector Signal Definitions                     | 34 |

| Table 20. 40-pin I/O Mezzanine Card Connector Pin-out                                 | 36 |

| Table 21. 96-pin Midplane Signal Connector Pin-out                                    | 36 |

| Table 22. Internal 9-pin Serial Header Pin-out (J4K1)                                 |    |

| Table 23. External USB Connector Pin-out                                              | 38 |

| Table 24. Pin-out of Internal USB Connector for low-profile Solid State Drive (J1K1)  | 38 |

| Table 25. Recovery Jumpers                                                            | 40 |

| Table 26. POST Progress Code LED Example                                              | 45 |

| Table 27. POST Progress Codes                                                         | 46 |

| Table 28. MRC Progress Codes                                                          | 48 |

| Table 29. MRC Fatal Error Codes                                                       | 48 |

| Table 30. POST Error Codes and Messages                                               | 50 |

| Table 31. POST Error Beep Codes                                                       | 55 |

| Table 32. Integrated BMC Beep Codes                                                   | 55 |

< This page intentionally left blank.>

## 1. Introduction

This Technical Product Specification (TPS) provides board-specific information detailing the features, functionality, and high-level architecture of the Intel<sup>®</sup> Compute Module MFS2600KI.

## 1.1 Chapter Outline

This document is divided into the following chapters:

- Chapter 1 Introduction

- Chapter 2 Product Overview

- Chapter 3 Functional Architecture

- Chapter 4 System Security

- Chapter 5 Connector/Header Locations and Pin-outs

- Chapter 6 Jumper Block Settings

- Chapter 7 Product Regulatory Requirements

- Appendix A Integration and Usage Tips

- Appendix B POST Code Diagnostic LED Decoder

- Appendix C Post Error Code

- Appendix D Supported Intel<sup>®</sup> Modular Server System

- Glossary

- Reference Documents

# 2. Product Overview

The Intel<sup>®</sup> Compute Module MFS2600KI is a monolithic printed circuit board with features that were designed to support the high-density compute module market.

## 2.1 Intel<sup>•</sup> Compute Module MFS2600KI Feature Set

| Feature                           | Description                                                                                                                                      |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Processors                        | Support for one or two Intel <sup>®</sup> Xeon <sup>®</sup> Processor E5-2600 series with up to 95W Thermal Design Power (TDP).                  |  |

|                                   | <ul> <li>8.0 GT/s, and 6.4 GT/s Intel<sup>®</sup> QuickPath Interconnect (Intel<sup>®</sup> QPI)</li> </ul>                                      |  |

|                                   | <ul> <li>Enterprise Voltage Regulator-Down (EVRD) 12.0</li> </ul>                                                                                |  |

| Memory                            | Support for 1067/1333/1600 MT/s ECC registered (RDIMM), unbuffered (UDIMM) and LRDIMM DDR3 memory.                                               |  |

|                                   | 16 DIMMs total across 8 memory channels (4 channels per processor).                                                                              |  |

|                                   | Note: Mixed memory is not tested or supported. Non-ECC memory is not tested and is not supported in a server environment.                        |  |

| Chipset                           | <ul> <li>Intel<sup>®</sup> C602-J Chipset</li> </ul>                                                                                             |  |

| On-board                          | External connections:                                                                                                                            |  |

| Connectors/Headers                | Four USB 2.0 ports                                                                                                                               |  |

|                                   | <ul> <li>DB-15 Video connector</li> </ul>                                                                                                        |  |

|                                   | Internal connectors/headers:                                                                                                                     |  |

|                                   | <ul> <li>One low-profile USB Type-A connector to support low-profile USB solid state drives</li> </ul>                                           |  |

|                                   | <ul> <li>One internal 7pin SATA connector for embedded SATA Flash Drive</li> </ul>                                                               |  |

|                                   | <ul> <li>One eUSB for embedded USB device</li> </ul>                                                                                             |  |

|                                   | <ul> <li>Intel<sup>®</sup> I/O Mezzanine connectors supporting Dual Gigabit NIC Intel<sup>®</sup> I/O Expansion<br/>Module (Optional)</li> </ul> |  |

| On-board Video                    | Integrated Matrox* G200 Core, one DB15 Video port (Front)                                                                                        |  |

| On-board Hard Drive<br>Controller | LSI* 1064e SAS controller                                                                                                                        |  |

| LAN                               | Intel <sup>®</sup> I350 Dual 1GbE Network Controller                                                                                             |  |

| Table 1. Intel <sup>®</sup> | compute modul | le MFS2600KI Feature | Set |

|-----------------------------|---------------|----------------------|-----|

|-----------------------------|---------------|----------------------|-----|

## 2.2 Compute Module Layout

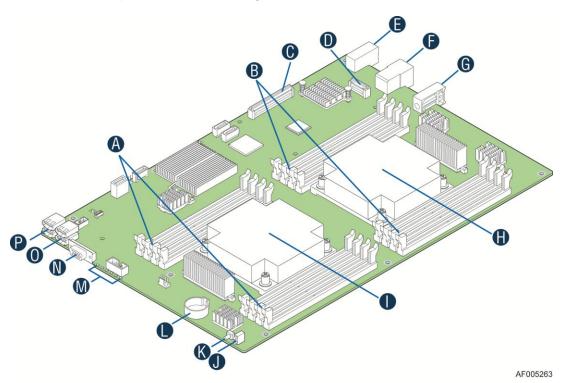

## 2.2.1 Connector and Component Locations

The following figure shows the board layout of the Intel<sup>®</sup> Compute Module MFS2600KI. Each connector and major component is identified by a number or letter. A description of each identified item is provided below the figure.

| А | CPU 1 DIMM Slots              | Ι | CPU 1 Socket         |

|---|-------------------------------|---|----------------------|

| В | CPU 2 DIMM Slots              | J | Power/Fault LEDs     |

| С | Mezzanine Card Connector 1    | К | Power Button         |

| D | Mezzanine Card Connector 2    | L | Battery              |

| Е | Midplane Power Connector      | М | Activity and ID LEDs |

| F | Midplane Signal Connector     | Ν | Video Connector      |

| G | Midplane Guide Pin Receptacle | 0 | USB Ports 2 and 3    |

| Н | CPU 2 Socket                  | Р | USB1 Ports 0 and 1   |

| Figure 1. | <b>Component and</b> | Connector | Location Diagram |

|-----------|----------------------|-----------|------------------|

|-----------|----------------------|-----------|------------------|

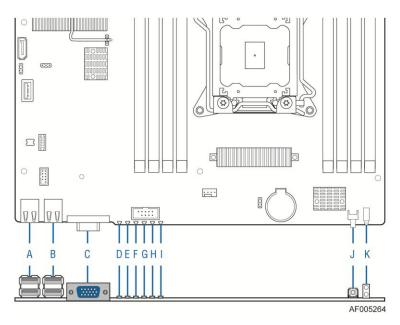

## 2.2.3 External I/O Connector Locations

The following drawing shows the layout of the external I/O components for the  $Intel^{\mbox{\tiny B}}$  Compute Module MFS2600KI.

| А | USB ports 0 and 1       | G | NIC 1 LED               |

|---|-------------------------|---|-------------------------|

| В | USB ports 2 and 3       | Н | Hard Drive Activity LED |

| С | Video                   | Ι | ID LED                  |

| D | I/O Mezzanine NIC 4 LED | J | Power button            |

| Е | I/O Mezzanine NIC 3 LED | Κ | Power and Fault LEDs    |

| F | NIC 2 LED               |   |                         |

Figure 2. Intel<sup>®</sup> Compute Module MFS2600KI Front Panel Layout

# 3. Functional Architecture

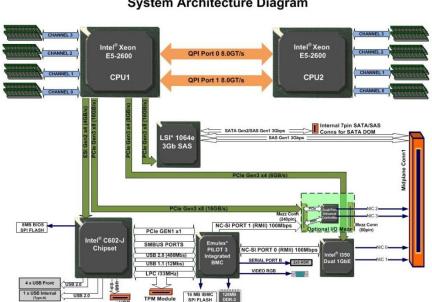

The architecture of the Intel<sup>®</sup> Compute Module MFS2600KI is developed around the integrated features and functions of the Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2600 product family the Intel<sup>®</sup> C602-J chipset, the Intel<sup>®</sup> Ethernet Controller I350 GbE controller chip and the Baseboard Management Controller.

The following diagram provides an overview of the compute module architecture, showing the features and interconnects of each of the major sub-system components.

MFS2600KI Compute Module System Architecture Diagram

#### Figure 3. Intel<sup>®</sup> Compute Module MFS2600KI Functional Block Diagram

## 3.1 Intel<sup>•</sup> Xeon<sup>•</sup> processor

### 3.1.1 Processor Support

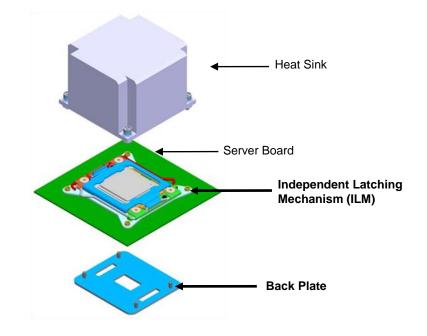

The compute module includes two Socket-R (LGA2011) processor sockets and can support one or two of the Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2600 product family, with a Thermal Design Power (TDP) of up to 95W processors.

#### 3.1.1.1 Processor Socket Assembly

Each processor socket of the server board is pre-assembled with an Independent Latching Mechanism (ILM) and Back Plate which allow for secure placement of the processor and processor heat to the server board.

The illustration below identifies each sub-assembly component.

Figure 4. Processor Socket Assembly

#### 3.1.1.2 Processor Population Rules

**Note:** Although the Compute Module does support dual-processor configurations consisting of different processors that meet the defined criteria below, Intel<sup>®</sup> does not perform validation testing of this configuration. For optimal performance in dual-processor configurations, Intel<sup>®</sup> recommends that identical processors be installed.

When using a single processor configuration, the processor must be installed into the processor socket labeled CPU1.

When two processors are installed, the following population rules apply:

- Both processors must be of the same processor family.

- Both processors must have the same number of cores.

- Both processors must have the same cache sizes for all levels of processor cache memory.

- Processors with different core frequencies can be mixed in a system, given the prior rules are met. If this condition is detected, all processor core frequencies are set to the lowest common denominator (highest common speed) and an error is reported.

- Processors which have different Intel<sup>®</sup> Quickpath (QPI) Link Frequencies may operate together if they are otherwise compatible and if a common link frequency can be selected. The common link frequency would be the highest link frequency that all installed processors can achieve.

- Processor stepping within a common processor family can be mixed as long as it is listed in the processor specification updates published by Intel Corporation.

#### 3.1.2 Processor Initialization Error Summary

The following table describes mixed processor conditions and recommended actions for the MFS2600KIdesigned around the Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2600 product family and Intel<sup>®</sup> C602-J chipset product family architecture. The errors fall into one of the following categories:

Fatal: If the system can boot, it pauses at a blank screen with the text "Unrecoverable fatal error found. System will not boot until the error is resolved" and "Press <F2> to enter setup", regardless of whether the "Post Error Pause" setup option is enabled or disabled.

When the operator presses the <F2> key on the keyboard, the error message is displayed on the Error Manager screen, and an error is logged to the System Event Log (SEL) with the POST Error Code.

The system cannot boot unless the error is resolved. The user needs to replace the faulty part and restart the system.

For Fatal Errors during processor initialization, the System Status LED will be set to a steady Amber color, indicating an unrecoverable system failure condition.

Major: If the "Post Error Pause" setup option is enabled, the system goes directly to the Error Manager to display the error, and logs the POST Error Code to SEL. Operator intervention is required to continue booting the system.

Otherwise, if "POST Error Pause" is disabled, the system continues to boot and no prompt is given for the error, although the Post Error Code is logged to the Error Manager and in a SEL message.

Minor: The message is displayed on the screen or on the Error Manager screen, and the POST Error Code is logged to the SEL. The system continues booting in a degraded state. The user may want to replace the erroneous unit. The POST Error Pause option setting in the BIOS setup does not have any effect on this error.

| Error                                        | Severity | System Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor family not<br>Identical            | Fatal    | <ul> <li>The BIOS detects the error condition and responds as follows:</li> <li>Logs the POST Error Code into the System Event Log (SEL).</li> <li>Alerts the BMC to set the System Status LED to steady Amber.</li> <li>Displays "0194: Processor family mismatch detected" message in the Error Manager.</li> <li>Takes Fatal Error action (see above) and will not boot until the fault condition is remedied.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       |

| Processor model not<br>Identical             | Fatal    | <ul> <li>The BIOS detects the error condition and responds as follows:</li> <li>Logs the POST Error Code into the System Event Log (SEL).</li> <li>Alerts the BMC to set the System Status LED to steady Amber.</li> <li>Displays "0196: Processor model mismatch detected" message in the Error Manager.</li> <li>Takes Fatal Error action (see above) and will not boot until the fault condition is remedied.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                        |

| Processor cores/threads not<br>identical     | Fatal    | <ul> <li>The BIOS detects the error condition and responds as follows:</li> <li>Logs the POST Error Code into the SEL.</li> <li>Alerts the BMC to set the System Status LED to steady Amber.</li> <li>Displays "0191: Processor core/thread count mismatch detected" message in the Error Manager.</li> <li>Takes Fatal Error action (see above) and will not boot until the fault condition is remedied.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               |

| Processor cache not<br>identical             | Fatal    | <ul> <li>The BIOS detects the error condition and responds as follows:</li> <li>Logs the POST Error Code into the SEL.</li> <li>Alerts the BMC to set the System Status LED to steady Amber.</li> <li>Displays "0192: Processor cache size mismatch detected message in the Error Manager.</li> <li>Takes Fatal Error action (see above) and will not boot until the fault condition is remedied.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                       |

| Processor frequency (speed)<br>not identical | Fatal    | <ul> <li>The BIOS detects the processor frequency difference, and responds as follows:</li> <li>Adjusts all processor frequencies to the highest common frequency.</li> <li>No error is generated – this is not an error condition.</li> <li>Continues to boot the system successfully.</li> <li>If the frequencies for all processors cannot be adjusted to be the same, then this is an error, and the BIOS responds as follows:</li> <li>Logs the POST Error Code into the SEL.</li> <li>Alerts the BMC to set the System Status LED to steady Amber.</li> <li>Does not disable the processor.</li> <li>Displays "0197: Processor speeds unable to synchronize" message in the Error Manager.</li> <li>Takes Fatal Error action (see above) and will not boot until the fault condition is remedied.</li> </ul> |

#### Table 2. Mixed Processor Configurations

| System Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Action<br>System |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## 3.2 Processor Functions Overview

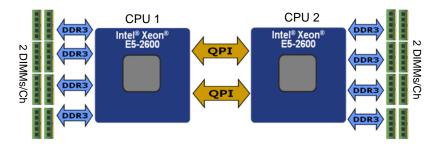

With the release of the Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2600 product family, several key system components, including the CPU, Integrated Memory Controller (IMC), and Integrated IO Module (IIO), have been combined into a single processor package and feature per socket; two Intel<sup>®</sup> QuickPath Interconnect point-to-point links capable of up to 8.0 GT/s, up to 40 lanes of Gen 3 PCI Express\* links capable of 8.0 GT/s, and 4 lanes of DMI2/PCI Express\* Gen 2 interface with a peak transfer rate of 5.0 GT/s. The processor supports up to 46 bits of physical address space and 48-bit of virtual address space.

The following sections will provide an overview of the key processor features and functions that help to define the architecture, performance and supported functionality of the server board. For more comprehensive processor specific information, refer to the Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2600 product family documents listed in the Reference Document list in Chapter 1.

Processor Core Features:

- Up to 8 execution cores

- Each core supports two threads (Intel<sup>®</sup> Hyper-Threading Technology), up to 16 threads per socket

- 46-bit physical addressing and 48-bit virtual addressing

- 1 GB large page support for server applications

- A 32-KB instruction and 32-KB data first-level cache (L1) for each core

- A 256-KB shared instruction/data mid-level (L2) cache for each core

- Up to 20 MB last level cache (LLC): up to 2.5 MB per core instruction/data last level cache (LLC), shared among all cores

Supported Technologies:

- Intel<sup>®</sup> Virtualization Technology (Intel<sup>®</sup> VT)

- Intel<sup>®</sup> Virtualization Technology for Directed I/O (Intel<sup>®</sup> VT-d)

- Intel<sup>®</sup> Trusted Execution Technology (Intel<sup>®</sup> TXT)

- Intel<sup>®</sup> 64 Architecture

- Intel<sup>®</sup> Streaming SIMD Extensions 4.1 (Intel<sup>®</sup> SSE4.1)

- Intel<sup>®</sup> Streaming SIMD Extensions 4.2 (Intel<sup>®</sup> SSE4.2)

- Intel<sup>®</sup> Advanced Vector Extensions (Intel<sup>®</sup> AVX)

- Intel<sup>®</sup> Hyper-Threading Technology

- Execute Disable Bit

- Intel<sup>®</sup> Turbo Boost Technology

- Intel<sup>®</sup> Intelligent Power Technology

- Enhanced Intel<sup>®</sup> SpeedStep Technology

#### 3.2.1 Intel<sup>•</sup> QuickPath Interconnect

The Intel<sup>®</sup> QuickPath Interconnect (QPI) is a high speed, packetized, point-to-point interconnect used in the processor. The narrow high-speed links stitch together processors in distributed shared memory and integrated I/O platform architecture. It offers much higher bandwidth with low latency. The Intel<sup>®</sup> QuickPath Interconnect has an efficient architecture allowing more interconnect performance to be achieved in real systems. It has a snoop protocol optimized for low latency and high scalability, as well as packet and lane structures enabling quick completions of transactions. Reliability, availability, and serviceability features (RAS) are built into the architecture.

The physical connectivity of each interconnect link is made up of twenty differential signal pairs plus a differential forwarded clock. Each port supports a link pair consisting of two uni-directional links to complete the connection between two components. This supports traffic in both directions simultaneously. To facilitate flexibility and longevity, the interconnect is defined as having five layers: Physical, Link, Routing, Transport, and Protocol.

The Intel<sup>®</sup> QuickPath Interconnect includes a cache coherency protocol to keep the distributed memory and caching structures coherent during system operation. It supports both low-latency source snooping and a scalable home snoop behavior. The coherency protocol provides for direct cache-to-cache transfers for optimal latency.

#### 3.2.2 Intel<sup>•</sup> Hyper-Threading Technology

Most Intel<sup>®</sup> Xeon<sup>®</sup> processors support Intel<sup>®</sup> Hyper-Threading Technology. The BIOS detects processors that support this feature and enables the feature during POST.

If the processor supports this feature, the BIOS Setup provides an option to enable or disable this feature. The default is enabled.

## 3.3 Processor Integrated I/O Module (IIO)

The processor's integrated I/O module provides features traditionally supported through chipset components. The integrated I/O module provides the following features:

#### 3.3.1 PCI Express Interfaces

The integrated I/O module incorporates the PCI Express interface and supports up to 40 lanes of PCI Express. The following tables list the CPU PCIe port connectivity of the Intel<sup>®</sup> Compute Module MFS2600KI.

| CPU# | Device                      | Physical Connector                     | Electrical<br>Width |

|------|-----------------------------|----------------------------------------|---------------------|

| CPU1 | Intel <sup>®</sup> C602-J   | N/A                                    | x4 Gen2             |

| CPU1 | IO Mezzanine Card           | 120 pin<br>Mezzanine Card<br>Connector | x8 Gen2             |

| CPU1 | Intel <sup>®</sup> I350 NIC | N/A                                    | x4 Gen2             |

| CPU1 | LSI* 1064e SAS              | N/A                                    | x8 Gen1             |

#### Table 3. Intel<sup>®</sup> Compute Module MFS2600KI PCIe Bus Segment Characteristics

#### 3.3.2 DMI2 Interface to the PCH

The platform requires an interface to the legacy Southbridge (PCH) which provides basic, legacy functions required for the server platform and operating systems. Since only one PCH is required and allowed for the system, CPU2 which does not connect to PCH would use this port as a standard x4 PCI Express 2.0 interface.

#### 3.3.3 Integrated IOAPIC

Provides support for PCI Express devices implementing legacy interrupt messages without interrupt sharing.

#### 3.3.4 Intel<sup>•</sup> QuickData Technology

Used for efficient, high bandwidth data movement between two locations in memory or from memory to I/O.

#### 3.4 Memory Subsystem

#### 3.4.1 Integrated Memory Controller (IMC) and Memory Subsystem

Figure 5. Intergrated Memory Controller (IMC) and Memory Subsystem

Integrated into the processor is a memory controller. Each processor provides four DDR3 channels that support the following:

- Unbuffered DDR3 and registered DDR3 DIMMs

- LR DIMM (Load Reduced DIMM) for buffered memory solutions demanding higher capacity memory subsystems

- Independent channel mode or lockstep mode

- Data burst length of eight cycles for all memory organization modes

- Memory DDR3 data transfer rates of 800, 1066, 1333, and 1600 MT/s

- 64-bit wide channels plus 8-bits of ECC support for each channel

- DDR3 standard I/O Voltage of 1.5 V and DDR3 Low Voltage of 1.35 V

- 1-Gb, 2-Gb, and 4-Gb DDR3 DRAM technologies supported for these devices:

- UDIMM DDR3 SR x8 and x16 data widths, DR x8 data width

- $\circ$  RDIMM DDR3 SR,DR, and QR x4 and x8 data widths

- LRDIMM DDR3 QR x4 and x8 data widths with direct map or with rank multiplication

- Up to eight ranks supported per memory channel, 1, 2 or 4 ranks per DIMM

- Open with adaptive idle page close timer or closed page policy

- Per channel memory test and initialization engine can initialize DRAM to all logical zeros with valid ECC (with or without data scrambler) or a predefined test pattern

- Isochronous access support for Quality of Service (QoS)

- Minimum memory configuration: independent channel support with 1 DIMM populated

- Integrated dual SMBus\* master controllers

- Command launch modes of 1n/2n

- RAS Support:

- Rank Level Sparing and Device Tagging

- Demand and Patrol Scrubbing

- DRAM Single Device Data Correction (SDDC) for any single x4 or x8 DRAM device. Independent channel mode supports x4 SDDC. x8 SDDC requires lockstep mode

- Lockstep mode where channels 0 and 1 and channels 2 and 3 are operated in lockstep mode

- Data scrambling with address to ease detection of write errors to an incorrect address.

- Error reporting through Machine Check Architecture

- Read Retry during CRC error handling checks by iMC

- Channel mirroring within a socket

- CPU1 Channel Mirror Pairs (A,B) and (C,D)

- CPU2 Channel Mirror Pairs (E,F) and (G,H)

- Error Containment Recovery

- Improved Thermal Throttling with dynamic Closed Loop Thermal Throttling (CLTT)

- Memory thermal monitoring support for DIMM temperature

#### 3.4.1.1 Intel<sup>•</sup> Compute Module MFS2600KI Supported Memory

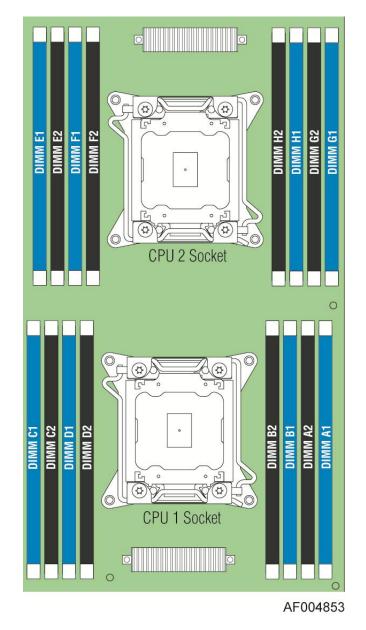

Each processor provides four banks of memory, each capable of supporting up to two DIMMs.

- DIMMs are organized into physical slots on DDR3 memory channels that belong to processor sockets.

- The memory channels from processor socket 1 are identified as Channel A, B, C, and D. The memory channels from processor socket 2 are identified as Channel E, F, G, and H.

- The silk screened DIMM slot identifiers on the board provide information about the channel, and therefore the processor to which they belong. For example, DIMM\_A1 is the first slot on Channel A on processor 1; DIMM\_E1 is the first DIMM socket on Channel E on processor 2.

- The memory slots associated with a given processor are unavailable if the corresponding processor socket is not populated.

- A processor may be installed without populating the associated memory slots provided and a second processor is installed with associated memory. In this case, the memory is shared by the processors. However, the platform suffers performance degradation and latency due to the remote memory.

- Processor sockets are self-contained and autonomous. However, all memory subsystem support (such as Memory RAS, Error Management,) in the BIOS setup are applied commonly across processor sockets.

For a complete list of supported memory for the Intel<sup>®</sup> Compute Module MFS2600KI, refer to the Tested Memory List published in the Intel<sup>®</sup> Server Configurator Tool.

| Ranks<br>Per<br>DIMM | -     | y Capacit | :y Per |            | Speed (MT/s) and Voltage Validated by<br>Slot per Channel (SPC) and DIMM Per Channel (DPC)2,3 |       |            |            |            |

|----------------------|-------|-----------|--------|------------|-----------------------------------------------------------------------------------------------|-------|------------|------------|------------|

| and<br>Data          |       | DIMM1     |        | 1 Slot per | r Channel                                                                                     |       | 2 Slots pe | er Channel |            |

| Width                |       |           |        | 1D         | PC                                                                                            | 1 DPC |            | 2DPC       |            |

| widuri               |       | -         | _      | 1.35V      | 1.5V                                                                                          | 1.35V | 1.5V       | 1.35V      | 1.5V       |

| SRx8<br>Non-<br>ECC  | 1GB   | 2GB       | 4GB    | n/a        | 1066,<br>1333, 1600                                                                           | n/a   | 1066, 1333 | n/a        | 1066, 1333 |

| DRx8<br>Non-<br>ECC  | 2GB   | 4GB       | 8GB    | n/a        | 1066,<br>1333, 1600                                                                           | n/a   | 1066, 1333 | n/a        | 1066, 1333 |

| SRx16<br>Non-<br>ECC | 512MB | 1GB       | 2GB    | n/a        | 1066,<br>1333, 1600                                                                           | n/a   | 1066, 1333 | n/a        | 1066, 1333 |

| SRx8<br>ECC          | 1GB   | 2GB       | 4GB    | 1066, 1333 | 1066,<br>1333, 1600                                                                           | 1066  | 1066, 1333 | 1066       | 1066, 1333 |

| DRx8<br>ECC          | 2GB   | 4GB       | 8GB    | 1066, 1333 | 1066,<br>1333, 1600                                                                           | 1066  | 1066, 1333 | 1066       | 1066, 1333 |

#### Table 4. UDIMM Support Guidelines (Preliminary. Subject to Change)

Notes:

- 1. Supported DRAM Densities are 1Gb, 2Gb, and 4Gb. Only 2Gb and 4Gb are validated by Intel®

- 2. Command Address Timing is 1N for 1DPC and 2N for 2DPC

- 3. No Support for 3DPC when using UDIMMs

| Ranks<br>Per<br>DIMM<br>and | Mem | ory Capac<br>DIMM1 | ity Per | 1 Slot        | Speed (MT/s) and Voltage Validated by<br>Slot per Channel (SPC) and DIMM Per Channel (DPC)2<br>1 Slot per Channel 2 Slots per Channel |            |            |       |            |  |

|-----------------------------|-----|--------------------|---------|---------------|---------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-------|------------|--|

| Data<br>Width               |     |                    |         | 1 5101        | 1DPC                                                                                                                                  | 10         | PC         |       | PC         |  |

| widun                       |     |                    |         | 1.35V         | 1.5V                                                                                                                                  | 1.35V      | 1.5V       | 1.35V | 1.5V       |  |

| SRx8                        | 1GB | 2GB                | 4GB     | 1066,<br>1333 | 1066,<br>1333, 1600                                                                                                                   | 1066, 1333 | 1066, 1333 | 1066  | 1066, 1333 |  |

| DRx8                        | 2GB | 4GB                | 8GB     | 1066,<br>1333 | 1066,<br>1333, 1600                                                                                                                   | 1066, 1333 | 1066, 1333 | 1066  | 1066, 1333 |  |

| SRx4                        | 2GB | 4GB                | 8GB     | 1066,<br>1333 | 1066,<br>1333, 1600                                                                                                                   | 1066, 1333 | 1066, 1333 | 1066  | 1066, 1333 |  |

| DRx4                        | 4GB | 8GB                | 16GB    | 1066,<br>1333 |                                                                                                                                       | 1066, 1333 | 1066, 1333 | 1066  | 1066, 1333 |  |

| QRx4                        | 8GB | 16GB               | 32GB    | 800           | 1066                                                                                                                                  | 800        | 1066       | 800   | 800        |  |

| QRx8                        | 4GB | 8GB                | 16GB    | 800           | 1066                                                                                                                                  | 800        | 1066       | 800   | 800        |  |

#### Table 5. RDIMM Support Guidelines (Preliminary. Subject to Change)

#### Notes:

- 1. Supported DRAM Densities are 1Gb, 2Gb, and 4Gb. Only 2Gb and 4Gb are validated by Intel<sup>®</sup>.

- 2. Command Address Timing is 1N

#### Table 6. LRDIMM Support Guidelines (Preliminary. Subject to Change)

| Ranks<br>Per   | Momory | apacity Dor        |            | Speed (MT/s) and Voltage Validated by<br>Slot per Channel (SPC) and DIMM Per Channel (DPC)3,4,5 |                     |            |  |  |

|----------------|--------|--------------------|------------|-------------------------------------------------------------------------------------------------|---------------------|------------|--|--|

| DIMM           | -      | apacity Per<br>1M2 | 1 Slot     | per Channel                                                                                     | 2 Slots per Channel |            |  |  |

| and Data       | 0      |                    |            | 1DPC 1DPC                                                                                       |                     | and 2DPC   |  |  |

| Width1         |        |                    | 1.35V      | 1.5V                                                                                            | 1.35V               | 1.5V       |  |  |

| QRx4<br>(DDP)6 | 16GB   | 32GB               | 1066, 1333 | 1066, 1333                                                                                      | 1066                | 1066, 1333 |  |  |

| QRx8<br>(P)6   | 8GB    | 16GB               | 1066, 1333 | 1066, 1333                                                                                      | 1066                | 1066, 1333 |  |  |

#### Notes:

- 1. Physical Rank is used to calculate DIMM Capacity

- 2. Supported and validated DRAM Densities are 2Gb and 4Gb

- 3. Command address timing is 1N

- 4. The speeds are estimated targets and will be verified through simulation

- 5. For 3SPC/3DPC Rank Multiplication (RM) >=2

- 6. DDP Dual Die Package DRAM stacking. P Planar monolithic DRAM Dies.

Supported and Validated

#### 3.4.2 Publishing Compute Module Memory

- The BIOS displays the "Total Memory" of the compute module during POST if Display Logo is disabled in the BIOS setup. This is the total size of memory discovered by the BIOS during POST, and is the sum of the individual sizes of installed DDR3 DIMMs in the system.

- The BIOS displays the "Effective Memory" of the compute module in the BIOS setup. The term Effective Memory refers to the total size of all DDR3 DIMMs that are active (not disabled) and not used as redundant units.

- The BIOS provides the total memory of the compute module in the main page of the BIOS setup. This total is the same as the amount described by the first bullet above.

- If Display Logo is disabled, the BIOS displays the total system memory on the diagnostic screen at the end of POST. This total is the same as the amount described by the first bullet above.

#### 3.4.3 Memory Map and Population Rules

The following are generic DIMM population requirements that generally apply to the Intel<sup>®</sup> Compute Module MFS2600KI.

- DIMM slots on any memory channel must be filled following the "farthest fill first" rule.

- A maximum of eight ranks can be installed on any one channel, counting all ranks in each DIMM on the channel.

- DIMM types (UDIMM, RDIMM, LRDIMM) must not be mixed within or across processor sockets.

- Mixing ECC with non-ECC DIMMs (UDIMMs) is not supported within or across processor sockets.

- Mixing Low Voltage (1.35V) DIMMs with Standard Voltage (1.5V) DIMMs is not supported within or across processor sockets.

- Mixing DIMMs of different frequencies and latencies is not supported within or across processor sockets.

- LRDIMM Rank Multiplication Mode and Direct Map Mode must not be mixed within or across processor sockets.

- Only ECC UDIMMs support Low Voltage 1.35V operation.

- QR RDIMMs may only be installed in DIMM Slot 1 or 2 on a channel.

- Two DPC QR Low Voltage RDIMMs are not supported.

- In order to install 3 QR LRDIMMs on the same channel, they must be operated with Rank Multiplication as RM = 2.

- RAS Modes Lockstep, Rank Sparing, and Mirroring are mutually exclusive in this BIOS.

Only one operating mode may be selected, and it will be applied to the entire system.

- If a RAS Mode has been configured, and the memory population will not support it during boot, the system will fall back to Independent Channel Mode and log and display errors

- Rank Sparing Mode is only possible when all channels that are populated with memory meet the requirement of having at least two SR or DR DIMM installed, or at least one QR DIMM installed, on each populated channel.

- Lockstep or Mirroring Modes require that for any channel pair that is populated with memory, the memory population on both channels of the pair must be identically sized.

DIMM population rules require that DIMMs within a channel be populated starting with the BLUE DIMM slot or DIMM farthest from the processor in a "fill-farthest" approach. In addition, when populating a Quad-rank DIMM with a Single- or Dual-rank DIMM in the same channel, the Quad-rank DIMM must be populated farthest from the processor.

| Configuration<br>Number | Speed               | 1N or 2N | DIMM 2      | DIMM 1<br>(Blue Slot) |

|-------------------------|---------------------|----------|-------------|-----------------------|

| 1                       | DDR3-1333, and 1066 | 1N       | Empty       | Single-rank           |

| 2                       | DDR3-1333, and 1066 | 1N       | Empty       | Dual-rank             |

| 3                       | DDR3-1066           | 1N       | Empty       | Quad-rank             |

| 4                       | DDR3-1333, and 1066 | 1N       | Single-rank | Single-rank           |

| 5                       | DDR3-1333, and 1066 | 1N       | Single-rank | Dual-rank             |

| 6                       | DDR3-1333, and 1066 | 1N       | Dual-rank   | Dual-rank             |

| 7                       | DDR3-800            | 1N       | Single-rank | Quad-rank             |

| 8                       | DDR3-800            | 1N       | Dual-rank   | Quad-rank             |

| 9                       | DDR3-800            | 1N       | Quad-rank   | Quad-rank             |

| 10                      | DDR3-800            | 1N       | Single-rank | Single-rank           |

| 11                      | DDR3-800            | 1N       | Single-rank | Dual-rank             |

| 12                      | DDR3-800            | 1N       | Dual-rank   | Dual-rank             |

| 13                      | DDR3-800            | 1N       | Dual-rank   | Dual-rank             |

| 14                      | DDR3-800            | 1N       | Single-rank | Quad-rank             |

| 15                      | DDR3-800            | 1N       | Dual-rank   | Quad-rank             |

| 16                      | DDR3-800            | 1N       | Dual-rank   | Quad-rank             |

#### Table 7. DDR3 RDIMM Population within a Channel

Table 8. DDR3L Low Voltage RDIMM Population within a Channel

| Configuration<br>Number | Speed            | 1N or 2N | DIMM 2      | DIMM 1<br>(Blue Slot) |

|-------------------------|------------------|----------|-------------|-----------------------|

| 1                       | DDR3L-1333, 1066 | 1N       | Empty       | Single-rank           |

| 2                       | DDR3L-1333, 1066 | 1N       | Empty       | Dual-rank             |

| 3                       | DDR3L-800        | 1N       | Empty       | Quad-rank             |

| 4                       | DDR3L-1066       | 1N       | Single-rank | Single-rank           |

| 5                       | DDR3L-1066       | 1N       | Single-rank | Dual-rank             |

| 6                       | DDR3L-1066       | 1N       | Dual-rank   | Dual-rank             |

| 7                       | DDR3L- 800       | 1N       | Single-rank | Quad-rank             |

| Configuration<br>Number | Speed               | 1N or 2N | DIMM 2      | DIMM 1<br>(Blue Slot) |

|-------------------------|---------------------|----------|-------------|-----------------------|

| 1                       | DDR3-1333, and 1066 | 1N       | Empty       | Single-rank           |

| 2                       | DDR3-1333, and 1066 | 1N       | Empty       | Dual-rank             |

| 3                       | DDR3-1333, and 1066 | 2N       | Single-rank | Single-rank           |

| 4                       | DDR3-1333, and 1066 | 2N       | Single-rank | Dual-rank             |

| 5                       | DDR3-1333, and 1066 | 2N       | Dual-rank   | Dual-rank             |

#### Table 9. DDR3 UDIMM Population within a Channel

#### Table 10. DDR3L Low Voltage UDIMM Poplulation within a Channel

| Configuration<br>Number | Speed           | 1N or 2N | DIMM 2      | DIMM 1<br>(Blue Slot) |

|-------------------------|-----------------|----------|-------------|-----------------------|

| 1                       | DDR3-1333,1066  | 1N       | Empty       | Single-rank           |

| 2                       | DDR3-1333, 1066 | 1N       | Empty       | Dual-rank             |

| 3                       | DDR3-1066       | 2N       | Single-rank | Single-rank           |

| 4                       | DDR3-1066       | 2N       | Single-rank | Dual-rank             |

| 5                       | DDR3-1066       | 2N       | Dual-rank   | Dual-rank             |

#### 3.4.3.1 Memory Subsystem Nomenclature

The nomenclature for DIMM sockets implemented on the Intel<sup>®</sup> Compute Module MFS2600KI is detailed in the following table.

| Table 11. Intel <sup>®</sup> Compute Module MFS2600KI DIMM Nomenclature |

|-------------------------------------------------------------------------|

|-------------------------------------------------------------------------|

|     |        | F    | rocesso | r Socket   | t 1   |      |        | Processor Socket 2 |        |           |       |      |        |      |       |

|-----|--------|------|---------|------------|-------|------|--------|--------------------|--------|-----------|-------|------|--------|------|-------|

| (   | 0)     | (*   | 1)      | (2         | 2)    | (:   | 3)     | ((                 | D)     | (*        | 1)    | (2   | 2)     | (3   | 3)    |

| Cha | nnel A | Chan | nel B   | Chan       | nel C | Char | nnel D | Chan               | inel E | Char      | nel F | Chan | inel G | Chan | nel H |

| A1  | A2     | B1   | B2      | <b>C</b> 1 | C2    | D1   | D2     | E1                 | E2     | <b>F1</b> | F2    | G1   | G2     | H1   | H2    |

#### 3.4.3.2 Publishing System Memory

The BIOS displays the "Total Memory" of the system during POST if Quite Boot is disabled in the BIOS setup. This is the total size of memory discovered by the BIOS during POST, and is the sum of the individual sizes of installed DDR3 DIMMs in the system.

The BIOS displays the "Effective Memory" of the system in the BIOS setup. The term Effective Memory refers to the total size of all DDR3 DIMMs that are active (not disabled) and not used as redundant units.

The BIOS provides the total memory of the system in the main page of the BIOS setup. This total is the same as the amount described by the first bullet above.

If Quite Boot is disabled, the BIOS displays the total system memory on the diagnostic screen at the end of POST. This total is the same as the amount described by the first bullet above.

#### 3.4.4 Memory RAS

#### 3.4.4.1 RAS Features

The Compute Module supports the following memory RAS features:

- Independent Channel Mode

- Rank Sparing Mode

- Mirrored Channel Mode

- Lockstep Channel Mode

Regardless of RAS mode, the requirements for populating within a channel given in the section 3.3.3 must be met at all times. Note that support of RAS modes that require matching DIMM population between channels (Mirrored and Lockstep) require that ECC DIMMs be populated. Independent Channel Mode is the only mode that supports non-ECC DIMMs in addition to ECC DIMMs.

For RAS modes that require matching populations, the same slot positions across channels must hold the same DIMM type with regards to size and organization. DIMM timings do not have to match but timings will be set to support all DIMMs populated (that is, DIMMs with slower timings will force faster DIMMs to the slower common timing modes).

#### 3.4.4.2 Independent Channel Mode

Channels can be populated in any order in Independent Channel Mode. All four channels may be populated in any order and have no matching requirements. All channels must run at the same interface frequency but individual channels may run at different DIMM timings (RAS latency, CAS Latency, and so forth).

#### 3.4.4.3 Rank Sparing Mode

In Rank Sparing Mode, one rank is a spare of the other ranks on the same channel. The spare rank is held in reserve and is not available as system memory. The spare rank must have identical or larger memory capacity than all the other ranks (sparing source ranks) on the same channel. After sparing, the sparing source rank will be lost.

#### 3.4.4.4 Mirrored Channel Mode

In Mirrored Channel Mode, the memory contents are mirrored between Channel 0 and Channel 2 and also between Channel 1 and Channel 3. As a result of the mirroring, the total physical memory available to the system is half of what is populated. Mirrored Channel Mode requires that Channel 0 and Channel 2, and Channel 1 and Channel 3 must be populated identically with regards to size and organization. DIMM slot populations within a channel do not have to be identical but the same DIMM slot location across Channel 0 and Channel 2 and across Channel 1 and Channel 3 must be populated identical 1 and Channel 3 must be populated the same.

#### 3.4.4.5 Lockstep Channel Mode

In Lockstep Channel Mode, each memory access is a 128-bit data access that spans Channel 0 and Channel 1, and Channel 2 and Channel 3. Lockstep Channel mode is the only RAS mode that allows SDDC for x8 devices. Lockstep Channel Mode requires that Channel 0 and Channel 1, and Channel 2 and Channel 3 must be populated identically with regards to size and organization. DIMM slot populations within a channel do not have to be identical but the same DIMM slot location across Channel 0 and Channel 1 and across Channel 2 and Channel 3 must be populated the same.

## 3.5 Intel<sup>•</sup> C602-J Chipset Overvew

The Intel<sup>®</sup> C602-J chipset in the Intel<sup>®</sup> Compute Module MFS2600KI provide a connection point between various I/O components and Intel<sup>®</sup> Xeon E5-2600 processors, which includes the following core platform functions:

- Digital Media Interface (DMI)

- PCI Express\* Interface

- Serial ATA (SATA) Controller

- Serial Attached SCSI (SAS)/SATA Controller

- AHCI

- Rapid Storage Technology

- PCI Interface

- Low Pin Count (LPC) Interface

- Serial Peripheral Interface (SPI)

- Compatibility Modules (DMA Controller, Timer/Counters, Interrupt Controller)

- Advanced Programmable Interrupt Controller (APIC)

- Universal Serial Bus (USB) Controllers

- Gigabit Ethernet Controller

- RTC

- GPIO

- Enhanced Power Management

- Intel<sup>®</sup> Active Management Technology (Intel<sup>®</sup> AMT)

- Manageability

- System Management Bus (SMBus\* 2.0)

- Integrated NVSRAM controller

- Virtualization Technology for Directed I/O (Intel<sup>®</sup> VT-d)

- JTAG Boundary-Scan

- KVM/Serial Over LAN (SOL) Function

#### 3.5.1 Digital Media Interface (DMI)

Digital Media Interface (DMI) is the chip-to-chip connection between the processor and Intel<sup>®</sup> C602-J chipset. This high-speed interface integrates advanced priority-based servicing allowing for concurrent traffic and true isochronous transfer capabilities. Base functionality is completely software-transparent, permitting current and legacy software to operate normally.

#### 3.5.2 PCI Express\* Interface

The Intel<sup>®</sup> C602-J chipset provides up to eight PCI Express Root Ports, supporting the PCI Express Base Specification, Revision 2.0. Each Root Port x1 lane supports up to 5 Gb/s bandwidth in each direction (10 Gb/s concurrent). PCI Express Root Ports 1-4 or Ports 5-8 can independently be configured to support four x1s, two x2s, one x2 and two x1s, or one x4 port widths.

#### 3.5.3 Serial ATA (SATA) Controller

The Intel<sup>®</sup> C602-J chipset has two integrated SATA host controllers that support independent DMA operation on up to six ports and supports data transfer rates of up to 6.0 Gb/s (600 MB/s) on up to two ports (Port 0 and 1 Only) while all ports support rates up to 3.0 Gb/s (300 MB/s) and up to 1.5 Gb/s (150 MB/s). The SATA controller contains two modes of operation – a legacy mode using I/O space, and an AHCI mode using memory space. Software that uses legacy mode will not have AHCI capabilities.

The Intel<sup>®</sup> C602-J chipset supports the Serial ATA Specification, Revision 3.0. The Intel<sup>®</sup> C602-J also supports several optional sections of the Serial ATA II: Extensions to Serial ATA 1.0 Specification, Revision 1.0 (AHCI support is required for some elements).

#### 3.5.4 Low Pin Count (LPC) Interface

The Intel<sup>®</sup> C602-J chipset implements an LPC Interface as described in the LPC 1.1 Specification. The Low Pin Count (LPC) bridge function of the Intel<sup>®</sup> C602-J resides in PCI Device 31: Function 0. In addition to the LPC bridge interface function, D31:F0 contains other functional units including DMA, interrupt controllers, timers, power management, system management, GPIO, and RTC.

#### 3.5.5 Serial Peripheral Interface (SPI)

The Intel<sup>®</sup> C602-J chipset implements an SPI Interface as an alternative interface for the BIOS flash device. The SPI flash is required to support Gigabit Ethernet and Intel<sup>®</sup> Active Management Technology. The Intel<sup>®</sup> C602-J chipset supports up to two SPI flash devices with speeds up to 50 MHz.

#### 3.5.6 Advanced Programmable Interrupt Controller (APIC)

In addition to the standard ISA compatible Programmable Interrupt controller (PIC) described in the previous section, the Intel<sup>®</sup> C602-J incorporates the Advanced Programmable Interrupt Controller (APIC).

## 3.5.7 Universal Serial Bus (USB) Controllers

The Intel<sup>®</sup> C602-J chipset has up to two Enhanced Host Controller Interface (EHCI) host controllers that support USB high-speed signaling. High-speed USB 2.0 allows data transfers up to 480 Mb/s which is 40 times faster than full-speed USB. The Intel<sup>®</sup> C602-J chipset supports up to fourteen USB 2.0 ports. All fourteen ports are high-speed, full-speed, and low-speed capable.

- Four external connectors are located on the front of the compute module.

- One internal 2x5 header is provided, capable of supporting a low-profile USB solid state drive.

- Two ports are routed to the Integrated BMC to support rKVM.

## 3.6 Integrated Baseboard Management Controller Overview

The Intel<sup>®</sup> Computer Module MFS2600KI utilizes the I/O controller, Graphics Controller, and Baseboard Management features of the Emulex\* Pilot-III Management Controller. The following is an overview of the features as implemented on the server board from each embedded controller.

#### Figure 7. Integrated BMC Functional Block Diagram

### 3.6.1 Super I/O Controller

The integrated super I/O controller provides support for the following features as implemented on the server board:

- Two Fully Functional Serial Ports, compatible with the 16C550

- Serial IRQ Support

- Up to 16 Shared direct GPIO's

- Serial GPIO support for 80 general purpose inputs and 80 general purpose outputs available for host processor

- Programmable Wake-up Event Support

- Plug and Play Register Set

- Power Supply Control

- Host SPI bridge for system BIOS support

#### 3.6.1.1 Keyboard and Mouse Support

The Intel<sup>®</sup> Computer Module MFS2600KI does not support PS/2 interface keyboards and mice. However, the system BIOS recognizes USB specification-compliant keyboard and mice.

#### 3.6.1.2 Wake-up Control

The super I/O contains functionality that allows various events to power on and power off the system.

#### 3.6.2 Graphics Controller and Video Support

The integrated graphics controller provides support for the following features as implemented on the server board:

- Integrated Graphics Core with 2D Hardware accelerator

- DDR-3 memory interface with 16 MB of memory allocated and reported for graphics memory

- High speed Integrated 24-bit RAMDAC

- Single lane PCI-Express host interface running at Gen 1 speed

The integrated video controller supports all standard IBM VGA modes. The following table shows the 2D modes supported for both CRT and LCD:

| 2D Mode     |       | 2D Video M | lode Supp | ort    |

|-------------|-------|------------|-----------|--------|

|             | 8 bpp | 16 bpp     | 24 bpp    | 32 Брр |