# Intel<sup>®</sup> Solid-State Drive 530 Series (mSATA)

#### **Product Specification**

- Capacities: 80 GB, 120 GB, 180 GB, 240 GB

- Components:

- Intel<sup>®</sup> 20 nm NAND Flash Memory

- Multi-Level Cell (MLC)

- Form Factors: mSATA full size

- Thickness: up to 3.8 mm

- Weight: < 10 grams

- SATA 6Gb/s Bandwidth Performance<sup>1</sup>

(Iometer\* Queue Depth 32)

- Sustained Sequential Read: up to 540 MB/s

- Sustained Sequential Write: up to 490 MB/s

- Read and Write IOPS<sup>1</sup>

(Iometer Queue Depth 32)

- Random 4 KB Reads: up to 41,000 IOPS

- Random 4 KB Writes: up to 80,000 IOPS<sup>2</sup>

- Data Compression

- AES 256-bit Encryption

- End-to-End Data Protection

- Compatibility

- Intel<sup>®</sup> SSD Toolbox with Intel<sup>®</sup> SSD Optimizer

- Intel<sup>®</sup> Data Migration Software

- Intel<sup>®</sup> Rapid Storage Technology

- SATA Revision 3.0

- ACS-2 (ATA/ATAPI Command Set 2)

- SSD Enhanced SMART ATA feature set

- Power Management

- 3.3 V SATA Supply Rail

- SATA Link Power Management (LPM)

- Device Sleep (DevSleep)

- Power

- Active (BAPCo MobileMark\* 2007 Workload): 140 mW

- Idle<sup>3</sup>: 55 mW

- DevSleep: 200 μW

- Temperature

- Operating<sup>4</sup>: 0° C to 70° C

- Non-Operating: -55° C to 95° C

- Reliability

- Uncorrectable Bit Error Rate (UBER):

<1 sector per 10<sup>16</sup> bits read

- Mean Time Between Failure (MTBF):

1,200,000 hours

- Shock (operating and non-operating): 1,000 G/0.5 msec

- Vibration

- Operating: 2.17 G<sub>RMS</sub> (5-700 Hz)

- Non-operating: 3.13 G<sub>RMS</sub> (5-800 Hz)

- Certifications and Declarations:

- UL\*

- CE\*

- C-Tick\*

- BSMI\*

- KCC\*

- Microsoft\* WHCK (Windows\* 7 and 8)

- VCCI\*

- SATA-IO\*

- Product Ecological Compliance

- RoHS\*

#### NOTES:

- 1. Performance values vary by capacity.

- 2. Random 4 KB writes measured using out-of-box SSD

- 3. Non-DevSleep idle power with SATA Link Power Management (LPM) enabled

- 4. As measured by temperature sensor, SMART Attribute BEh. Active airflow is recommended within the system for maintaining proper device operating temperatures on heavier workloads.

#### **Ordering Information**

Contact your local Intel sales representative for ordering information.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.html

Low Halogen applies only to brominated and chlorinated flame retardants (BFRs/CFRs) and PVC in the final product. Intel components as well as purchased components on the finished assembly meet JS-709 requirements, and the PCB/substrate meet IEC 61249-2-21 requirements. The replacement of halogenated flame retardants and/or PVC may not be better for the environment

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2013 Intel Corporation. All rights reserved.

Product Specification

September 2013

## **Contents**

| Revisio | on History                          | 4   |

|---------|-------------------------------------|-----|

| 1       | Introduction                        | 5   |

| 1.1     | Terminology                         | 6   |

| 1.2     | Reference Documents                 |     |

| 2       | Product Specifications              | 8   |

| 2.1     | Capacity                            | 8   |

| 2.2     | Performance                         | 8   |

| 2.3     | Electrical Characteristics          | . 9 |

| 2.4     | Environmental Conditions            | 10  |

|         | 2.4.1 Temperature, Shock, Vibration | 10  |

|         | 2.4.2 Altitude                      | 10  |

| 2.5     | Product Regulatory Compliance       | 11  |

| 2.6     | Reliability                         | 12  |

| 3       | Mechanical Information              | 13  |

| 4       | Pin and Signal Descriptions         | 14  |

| 4.1     | Pin Locations                       | 14  |

| 4.2     | Signal Descriptions                 |     |

| 4.3     | Device Sleep Feature                |     |

| 5       | Supported Command Sets              | 17  |

| 5.1     | ATA General Feature Command Set     | 17  |

| 5.2     | Power Management                    | 18  |

| 5.3     | Security Mode Feature Set           | 18  |

| 5.4     | SMART Command Set                   | 19  |

|         | 5.4.1 SMART Attributes              | 19  |

|         | 5.4.2 SMART Logs                    | 22  |

| 5.5     | Device Statistics                   | 22  |

| 5.6     | SMART Command Transport             |     |

| 5.7     | Data Set Management Command Set     | 23  |

| 5.8     | Host Protected Area Command Set     | 23  |

| 5.9     | 48-Bit Address Command Set          |     |

| 5.10    | General Purpose Log Command Set     | 23  |

| 5.11    | Native Command Queuing              | 23  |

| 5.12    | Software Settings Preservation      | 24  |

| 5.13    | SATA Link Power Management (LPM)    | 24  |

| 6       | Certifications and Declarations     | 25  |

| 7       | Annendix                            | 26  |

## **Revision History**

| Document<br>Number | Revision<br>Number | Description           | Revision Date  |

|--------------------|--------------------|-----------------------|----------------|

| 329280             | 001US              | Initial Release       | July 2013      |

| 329280             | 002US              | Added 120 GB Capacity | September 2013 |

## 1 Introduction

This document describes the specifications and capabilities of the Intel® Solid-State Drive 530 Series (Intel® SSD 530 Series).

The Intel® SSD 530 Series is a case-less mSATA (mini-SATA) design that is designed for Ultrabook™ and small form factor compute platforms. This form factor allows ultra-compact solutions which deliver leading performance for Serial Advanced Technology Attachment (SATA)-based computers in capacities ranging up to 240GB.

The latest feature addition is the DevSleep functionality, a low power drive state controlled by the host via the DevSleep pin. The drive will consume a mere 200  $\mu$ W while in this state.

As compared to standard SATA HDDs, Intel SSD 530 Series offers these key features:

- High I/O and throughput performance

- Lower power consumption

- Increased system responsiveness

- Higher reliability

- Enhanced ruggedness

- Small form-factor

- Minimum weight

The Intel SSD 530 Series also offers additional key features such as:

• Advanced Encryption Standard (AES) 256-bit Encryption

AES 256-bit encryption is an industry standard in data security, providing a hardware-based mechanism for encryption and decryption of user data. Utilizing a 256-bit encryption key, AES encryption—when combined with an ATA drive password—helps protect user data.

End-to-End Data Protection

End-to-end data protection helps protect data from being corrupted across the data path by using cyclic redundancy check (CRC), parity, and error correction code (ECC) checks in the data path from the host interface to the NAND, and back.

Data Compression

Data compression helps improve performance and endurance by automatically compressing information sent to the SSD so that less data has to be processed and stored on the NAND. The amount of data that can be compressed depends on the type of data.

## 1.1 Terminology

| Term     | Description                                                                                                                                                                                                                 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATA      | Advanced Technology Attachment                                                                                                                                                                                              |

| DAS      | Device Activity Signal                                                                                                                                                                                                      |

| DevSleep | Device Sleep, a power feature that allows the host to initiate ultra-low power consumption by the drive.                                                                                                                    |

| DIPM     | Device Initiated Power Management                                                                                                                                                                                           |

| DMA      | Direct Memory Access                                                                                                                                                                                                        |

| EXT      | Extended                                                                                                                                                                                                                    |

| FPDMA    | First Party Direct Memory Access                                                                                                                                                                                            |

| GB       | Gigabyte (1,000,000,000 bytes)  Note: The total usable capacity of the SSD may be less than the total physical capacity because a small portion of the capacity is used for NAND flash management and maintenance purposes. |

| HDD      | Hard Disk Drive                                                                                                                                                                                                             |

| HIPM     | Host Initiated Power Management                                                                                                                                                                                             |

| 1/0      | Input/Output                                                                                                                                                                                                                |

| IOPS     | Input/Output Operations Per Second                                                                                                                                                                                          |

| КВ       | Kilobyte (1,024 bytes)                                                                                                                                                                                                      |

| LBA      | Logical Block Address                                                                                                                                                                                                       |

| LPM      | Link Power Management                                                                                                                                                                                                       |

| MB       | Megabyte (1,000,000 bytes)                                                                                                                                                                                                  |

| MLC      | Multi-level Cell                                                                                                                                                                                                            |

| MTBF     | Mean Time Between Failures                                                                                                                                                                                                  |

| NCQ      | Native Command Queuing                                                                                                                                                                                                      |

| NOP      | No Operation                                                                                                                                                                                                                |

| PIO      | Programmed Input/Output                                                                                                                                                                                                     |

| RDT      | Reliability Demonstration Test                                                                                                                                                                                              |

| RMS      | Root Mean Squared                                                                                                                                                                                                           |

| SATA     | Serial Advanced Technology Attachment                                                                                                                                                                                       |

| SMART    | Self-Monitoring, Analysis and Reporting Technology                                                                                                                                                                          |

| SSD      | Solid-State Drive                                                                                                                                                                                                           |

| TYP      | Typical                                                                                                                                                                                                                     |

| UBER     | Uncorrectable Bit Error Rate                                                                                                                                                                                                |

### 1.2 Reference Documents

#### **Table 2: Standard References**

| Date or Rev. # | Title                                                                                                                                     | Location                                                                                        |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Sept 2008      | IEC 55022 Information Technology Equipment — Radio disturbance Characteristics— Limits and methods of measurement CISPR22:2008 (Modified) | http://www.iec.ch/                                                                              |

| Dec 2008       | VCCI                                                                                                                                      | http://www.vcci.jp/vcci_e/                                                                      |

| June 2009      | RoHS                                                                                                                                      | http://qdms.intel.com/ Click Search MDDS Database and search for material description datasheet |

| June 2009      | Serial ATA Revision 3.0                                                                                                                   | http://www.sata-io.org/                                                                         |

| August 2009    | ACS-2 Specification                                                                                                                       | http://www.t13.org/                                                                             |

| August 2010    | IEC 55024 Information Technology Equipment — Immunity characteristics— Limits and methods of measurement CISPR24:2010                     | http://www.iec.ch/                                                                              |

| Sept 2010      | Solid-State Drive (SSD) Requirements and Endurance Test Method (JESD218)                                                                  | http://www.jedec.org/standards-<br>documents/docs/jesd218/                                      |

| Oct 2010       | JEDEC Solid-State Product Outline – mSATA SSD Assembly                                                                                    | http://www.jedec.org/                                                                           |

| July 2011      | Serial ATA Revision 3.1 (mSATA definition)                                                                                                | http://www.sata-io.org/                                                                         |

## 2 Product Specifications

### 2.1 Capacity

**Table 3: User Addressable Sectors**

| Intel® SSD 530 Series | Unformatted Capacity (Total User Addressable Sectors in LBA mode) |

|-----------------------|-------------------------------------------------------------------|

| 80 GB                 | 156,301,488                                                       |

| 120 GB                | 234,441,648                                                       |

| 180 GB                | 351,651,888                                                       |

| 240 GB                | 468,862,128                                                       |

#### 2.2 Performance

**Table 4: Compressible Performance**

| Specification                           | Unit | Intel® SSD 530 Series |        |        |        |

|-----------------------------------------|------|-----------------------|--------|--------|--------|

|                                         |      | 80 GB                 | 120 GB | 180 GB | 240 GB |

| Random 4 KB Read (up to) <sup>1</sup>   | IOPS | 24,000                | 24,000 | 41,000 | 41,000 |

| Random 4 KB Write (up to) <sup>2</sup>  | IOPS | 80,000                | 80,000 | 80,000 | 80,000 |

| Random 4 KB Write (TYP) 1               | IOPS | 33,000                | 37,500 | 49,000 | 49,000 |

| Sequential 128 KB Read (SATA 6 Gb/s) 1  | MB/s | 540                   | 540    | 540    | 540    |

| Sequential 128 KB Write (SATA 6 Gb/s) 1 | MB/s | 480                   | 480    | 490    | 490    |

#### Note:

- Performance measured using Iometer\* with Queue Depth 32. Measurements are performed on 8 GB of Logical Block Address (LBA) range on a full SSD

- 2. Random 4 KB writes measured using out-of-box SSD

**Table 5: Incompressible Performance**

| Specification                                     | Unit | Intel® SSD 530 Series |        |        |        |

|---------------------------------------------------|------|-----------------------|--------|--------|--------|

|                                                   |      | 80 GB                 | 120 GB | 180 GB | 240 GB |

| Random 4 KB Read (up to) <sup>1</sup>             | IOPS | 20,500                | 18,000 | 37,500 | 37,500 |

| Random 4 KB Write (up to) 1                       | IOPS | 9,200                 | 15,000 | 17,000 | 23,000 |

| Sequential 128 KB Read (SATA 6Gb/s) 1             | MB/s | 430                   | 450    | 470    | 510    |

| Sequential 128 KB Write (SATA 6Gb/s) <sup>1</sup> | MB/s | 100                   | 130    | 170    | 230    |

#### Note:

1. Performance measured using Iometer\* with Queue Depth 32

**Product Specification**

September 2013 Order Number: 329280-002US

8

#### Intel® Solid-State Drive 530 Series (mSATA)

**Table 6: Latency**

| Specification                  | Intel® SSD 530 Series |        |        |        |

|--------------------------------|-----------------------|--------|--------|--------|

|                                | 80 GB                 | 120 GB | 180 GB | 240 GB |

| Read <sup>1</sup>              | 80 μs (TYP)           |        |        |        |

| Write <sup>1</sup>             | 85 μs (TYP)           |        |        |        |

| Power On To Ready <sup>2</sup> | 1 s (TYP)             |        |        |        |

#### Note:

- 1. Based on sequential 4 KB using Iometer with Queue Depth 1 workload with compressible (non-random) data pattern. Write Cache enabled.

- 2. Power On To Ready time assumes proper shutdown

#### 2.3 Electrical Characteristics

**Table 7: Operating Voltage and Power Consumption**

| Electrical Characteristics Value                                                                                                  |                                                                                       | lue    |                         |        |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------|-------------------------|--------|

|                                                                                                                                   | 80 GB                                                                                 | 120 GB | 180 GB                  | 240 GB |

| Operating Voltage for 3.3 V (±5%)  Min  Max  Rise Time (Max/Min)  Fall Time (Max/Min)  Noise Tolerance  Min Off Time <sup>1</sup> | 3.14 V<br>3.47 V<br>100 ms / 0.1 ms<br>5 s / 1 ms<br>70 mV pp (10 Hz – 30 MHz)<br>1 s |        |                         |        |

| Power Consumption (TYP) Active <sup>2</sup> Idle <sup>3</sup> DevSleep <sup>4</sup> Thermal Power <sup>5</sup>                    | 2.7 W                                                                                 | 55     | mW<br>mW<br>μW<br>3.8 W | 4.5 W  |

| Regulator Power <sup>6</sup>                                                                                                      | 3 W                                                                                   | 3.4 W  | 4.1 W                   | 4.9 W  |

#### Note:

- 1. Minimum time from when power removed from drive (Vcc < 100 mV) to when power can be reapplied to drive

- Active power measured during execution of MobileMark\* 2007 with SATA Link Power Management (LPM) enabled.

- 3. Non-DevSleep idle power with SATA Link Power Management (LPM) enabled.

- 4. Power consumption during DevSleep state.

- 5. Power measured during 128 KB sequential writes with Queue Depth 32 workload using 100 ms sample period. This represents power that would be thermal load on system during heavy workloads.

- Power measured during 128 KB sequential writes with Queue Depth 32 workload using 500 µs sample period. This represents power that system power supply would have to regulate for proper device operation.

#### 2.4 Environmental Conditions

### 2.4.1 Temperature, Shock, Vibration

Table 8: Temperature, Shock, Vibration

| Table 6: Temperature, Snock, Vibration |                           |  |  |  |

|----------------------------------------|---------------------------|--|--|--|

| <b>Electrical Characteristics</b>      | Range                     |  |  |  |

| Module Temperature                     |                           |  |  |  |

| Operating <sup>1</sup>                 | 0° C - 70° C              |  |  |  |

| Non-operating <sup>2</sup>             | -55° C - 95° C            |  |  |  |

| Temperature Gradient <sup>3</sup>      |                           |  |  |  |

| Operating                              | 30 (TYP) °C /hr           |  |  |  |

| Non-operating                          | 30 (TYP) °C /hr           |  |  |  |

| Humidity                               |                           |  |  |  |

| Operating                              | 5 – 95 %                  |  |  |  |

| Non-operating                          | 5 – 95 %                  |  |  |  |

| Shock and Vibration                    | Range                     |  |  |  |

| Shock <sup>4</sup>                     |                           |  |  |  |

| Operating                              | 1,000 G (Max) at 0.5 msec |  |  |  |

| Non-operating                          | 1,000 G (Max) at 0.5 msec |  |  |  |

| Vibration <sup>5</sup>                 |                           |  |  |  |

| Operating                              | 2.17 GRMS (5-700 Hz) Max  |  |  |  |

| Non-operating                          | 3.13 GRMS (5-800 Hz) Max  |  |  |  |

#### Note:

- 1. As measured by temperature sensor, SMART Attribute BEh. Active airflow is recommended within the system for maintaining proper device operating temperature on heavier workloads.

- 2. Please contact your Intel representative for details on the non-operating temperature range.

- 3. Temperature gradient measured without condensation.

- 4. Shock specifications assume the SSD is mounted securely with the input vibration applied to the drive-mounting screws. Stimulus may be applied in the X, Y or Z axis. Shock specification is measured using peak acceleration and pulse width value.

- 5. Vibration specifications assume the SSD is mounted securely with the input vibration applied to the drive-mounting screws. Stimulus may be applied in the X, Y or Z axis. Vibration specification is measured using Root Mean Squared (RMS) value.

#### 2.4.2 Altitude

The drive is not sensitive to changes in atmospheric pressure because it has no moving parts. Drive tested under non-operational conditions to pressures representative of -1 K and +40 K feet.

## 2.5 **Product Regulatory Compliance**

The Intel® SSD 530 Series meets or exceeds the regulatory or certification requirements in the table below.

**Table 9: Product Regulatory Compliance Specifications**

| Title                                                                                                                                     | Description                                                                 | Region For Which<br>Conformity<br>Declared |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------|

| TITLE 47-Telecommunications CHAPTER 1— FEDERAL COMMUNMICATIONS COMMISSION PART 15 — RADIO FREQUENCY DEVICES                               | FCC Part 15B Class B                                                        | USA                                        |

| ICES-003, Issue 4 Interference-Causing<br>Equipment<br>Standard Digital Apparatus                                                         | CA/CSA - CEI/IEC CISPR 22-10 (Ref. CISPR 22: 2008)                          | Canada                                     |

| IEC 55024 Information Technology Equipment — Immunity characteristics— Limits and methods of measurement CISPR24:2010                     | EN-55024: 2010 and its amendments                                           | European Union                             |

| IEC 55022 Information Technology Equipment — Radio disturbance Characteristics— Limits and methods of measurement CISPR24:2008 (Modified) | EN-55022: 2010 and its amendments                                           | European Union                             |

| EN-60950-1 2 <sup>nd</sup> Edition                                                                                                        | Information Technology Equipment —<br>Safety — Part 1: General Requirements | USA/Canada                                 |

| UL/CSA EN-60950-1 2 <sup>nd</sup> Edition                                                                                                 | Information Technology Equipment —<br>Safety — Part 1: General Requirements | USA/Canada                                 |

## 2.6 Reliability

The Intel® SSD 530 Series meets or exceeds SSD endurance and data retention requirements as specified in the JESD218 specification.

**Table 10: Reliability Specifications**

| Parameter                                                                                                                                                                                                                                                                             | Value                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Uncorrectable Bit Error Rate (UBER)                                                                                                                                                                                                                                                   |                                           |

| Uncorrectable bit error rate will not exceed one sector in the specified number of bits read. In the unlikely event of a non-recoverable read error, the SSD will report it as a read failure to the host; the sector in error is considered corrupt and is not returned to the host. | < 1 sector per 10 <sup>16</sup> bits read |

| Mean Time Between Failures (MTBF)                                                                                                                                                                                                                                                     |                                           |

| Mean Time Between Failures is estimated based on Telcordia* methodology and demonstrated through Reliability Demonstration Test (RDT).                                                                                                                                                | ≥ 1.2 million hours                       |

| Minimum Useful Life/Endurance Rating                                                                                                                                                                                                                                                  |                                           |

| The SSD will have a minimum useful life based on a typical client workload assuming up to 20 GB of host writes per day.                                                                                                                                                               | 5 years                                   |

| Insertion Cycles                                                                                                                                                                                                                                                                      |                                           |

| Maximum insertion/removal cycles on mSATA port                                                                                                                                                                                                                                        | 250 insertion/removal cycles              |

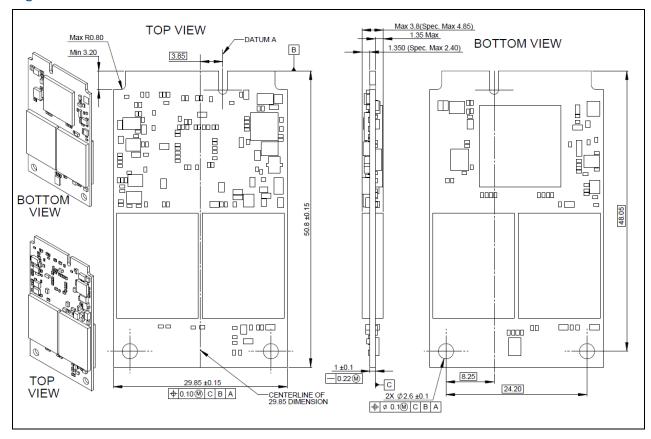

## 3 Mechanical Information

The figure below shows the mechanical information for the mSATA full size Intel\$ SSD 530 Series SSD. All dimensions are in millimeters.

Figure 1: Dimensions for Full Size mSATA Drives

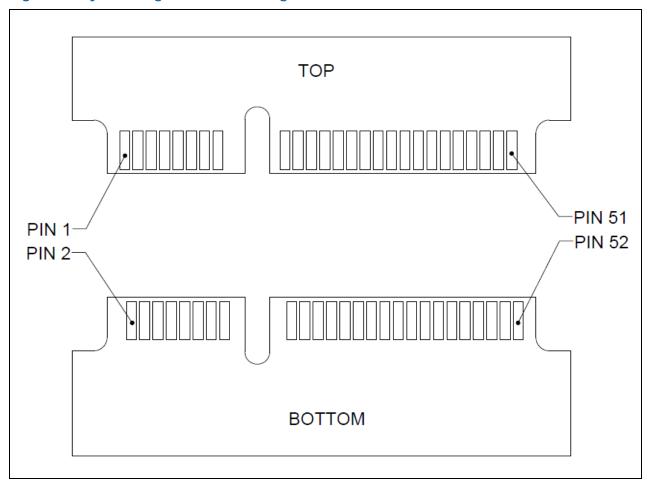

## 4 Pin and Signal Descriptions

### 4.1 Pin Locations

Figure 2: Layout of Signal and Power Segment Pins

## 4.2 Signal Descriptions

Table 11. Serial ATA Power Pin Definitions

| Pin   Reserved         No Connect           P2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 11         | I. Serial ATA Power I | PIN DETINITIONS                                                         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------------------------------------------------------------------|--|

| P2 +3.3 V 3.3 V Source  P3 Reserved No Connect  P4 GND Ground  P5 Reserved No Connect  P6¹ +1.5 V 1.5 V Source  P7 Reserved No Connect  P8 Reserved No Connect  P9 GND Ground  P10 Reserved No Connect  P11 Reserved No Connect  P12 Reserved No Connect  P13 Reserved No Connect  P14 Reserved No Connect  P15 GND Ground  P16 Reserved No Connect  P17 Reserved No Connect  P18 GND Ground  P19 Reserved No Connect  P19 GND Ground  P10 Reserved No Connect  P11 Reserved No Connect  P12 Reserved No Connect  P13 Reserved No Connect  P14 Reserved No Connect  P15 GND Ground  P16 Reserved No Connect  P17 Reserved No Connect  P18 GND Ground  P19 Reserved No Connect  P20 Reserved No Connect  P21 GND Ground  P22 Reserved No Connect  P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD)  P24 +3.3 V 3.3 V Source  P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD)  P26 GND Ground  P27 GND Ground  P28¹ +1.5 V 1.5 V Source  P29 GND Ground  P30² Two Wire Interface Two Wire Interface Clock  P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD) | Pin <sup>1</sup> | Function              | Definition                                                              |  |

| P3 Reserved No Connect P4 GND Ground P5 Reserved No Connect P6¹ +1.5 V 1.5 V Source P7 Reserved No Connect P8 Reserved No Connect P9 GND Ground P10 Reserved No Connect P11 Reserved No Connect P12 Reserved No Connect P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P19 GND Ground P10 Reserved No Connect P11 Reserved No Connect P12 Reserved No Connect P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28¹ +1.5 V 1.5 V Source P29 GND Ground P30² Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                        | P1               | Reserved              | No Connect                                                              |  |

| P4 GND Ground P5 Reserved No Connect P6¹ +1.5 V 1.5 V Source P7 Reserved No Connect P8 Reserved No Connect P9 GND Ground P10 Reserved No Connect P11 Reserved No Connect P12 Reserved No Connect P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P19 Reserved No Connect P10 Reserved No Connect P11 Reserved No Connect P12 Reserved No Connect P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P20 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28¹ +1.5 V 1.5 V Source P29 GND Ground P30² Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                      | P2               | +3.3 V                | 3.3 V Source                                                            |  |

| P5 Reserved No Connect P6¹ +1.5 V 1.5 V Source P7 Reserved No Connect P8 Reserved No Connect P9 GND Ground P10 Reserved No Connect P11 Reserved No Connect P12 Reserved No Connect P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P19 Reserved No Connect P19 Reserved No Connect P10 Reserved No Connect P11 Reserved No Connect P12 Reserved No Connect P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P20 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28¹ +1.5 V 1.5 V Source P29 GND Ground P30² Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                            | P3               | Reserved              | No Connect                                                              |  |

| P6¹         +1.5 V         1.5 V Source           P7         Reserved         No Connect           P8         Reserved         No Connect           P9         GND         Ground           P10         Reserved         No Connect           P11         Reserved         No Connect           P12         Reserved         No Connect           P13         Reserved         No Connect           P14         Reserved         No Connect           P15         GND         Ground           P16         Reserved         No Connect           P17         Reserved         No Connect           P18         GND         Ground           P19         Reserved         No Connect           P20         Reserved         No Connect           P21         GND         Ground           P22         Reserved         No Connect           P21         GND         Ground           P22         Reserved         No Connect           P23         +B         Host Receiver Differential Signal Pair (This is an output of the SSD)           P24         +3.3 V         3.3 V Source           P25         -B         Hos                        | P4               | GND                   | Ground                                                                  |  |

| P7 Reserved No Connect P8 Reserved No Connect P9 GND Ground P10 Reserved No Connect P11 Reserved No Connect P12 Reserved No Connect P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28 +1.5 V 1.5 V Source P29 GND Ground P302 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                          | P5               | Reserved              | No Connect                                                              |  |

| P8 Reserved No Connect P9 GND Ground P10 Reserved No Connect P11 Reserved No Connect P12 Reserved No Connect P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P20 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28 +1.5 V 1.5 V Source P29 GND Ground P302 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                  | P6 <sup>1</sup>  | +1.5 V                | 1.5 V Source                                                            |  |

| P9 GND Ground P10 Reserved No Connect P11 Reserved No Connect P12 Reserved No Connect P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28 +1.5 V 1.5 V Source P29 GND Ground P30 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                  | P7               | Reserved              | No Connect                                                              |  |

| P10 Reserved No Connect P11 Reserved No Connect P12 Reserved No Connect P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P19 Reserved No Connect P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28 +1.5 V 1.5 V Source P29 GND Ground P29 GND Ground P30 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                | P8               | Reserved              | No Connect                                                              |  |

| P11 Reserved No Connect P12 Reserved No Connect P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P19 Reserved No Connect P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28 Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28 H.5 V 1.5 V Source P29 GND Ground P302 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                               | P9               | GND                   | Ground                                                                  |  |

| P12 Reserved No Connect P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P19 Reserved No Connect P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28 +1.5 V 1.5 V Source P29 GND Ground P302 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P10              | Reserved              | No Connect                                                              |  |

| P13 Reserved No Connect P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28 +1.5 V 1.5 V Source P29 GND Ground P302 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P11              | Reserved              | No Connect                                                              |  |

| P14 Reserved No Connect P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28 +1.5 V 1.5 V Source P29 GND Ground P30² Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P12              | Reserved              | No Connect                                                              |  |

| P15 GND Ground P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28 +1.5 V 1.5 V Source P29 GND Ground P302 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P13              | Reserved              | No Connect                                                              |  |

| P16 Reserved No Connect P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28 +1.5 V 1.5 V Source P29 GND Ground P302 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P14              | Reserved              | No Connect                                                              |  |

| P17 Reserved No Connect P18 GND Ground P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P28 +1.5 V 1.5 V Source P29 GND Ground P302 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P15              | GND                   | Ground                                                                  |  |

| P18 GND Ground P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P281 +1.5 V 1.5 V Source P29 GND Ground P302 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P16              | Reserved              | No Connect                                                              |  |

| P19 Reserved No Connect P20 Reserved No Connect P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P281 +1.5 V 1.5 V Source P29 GND Ground P302 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P17              | Reserved              | No Connect                                                              |  |

| P20 Reserved No Connect  P21 GND Ground  P22 Reserved No Connect  P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD)  P24 +3.3 V 3.3 V Source  P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD)  P26 GND Ground  P27 GND Ground  P281 +1.5 V 1.5 V Source  P29 GND Ground  P302 Two Wire Interface Two Wire Interface Clock  P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P18              | GND                   | Ground                                                                  |  |

| P21 GND Ground P22 Reserved No Connect P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD) P24 +3.3 V 3.3 V Source P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD) P26 GND Ground P27 GND Ground P281 +1.5 V 1.5 V Source P29 GND Ground P302 Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P19              | Reserved              | No Connect                                                              |  |

| P22 Reserved No Connect  P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD)  P24 +3.3 V 3.3 V Source  P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD)  P26 GND Ground  P27 GND Ground  P28¹ +1.5 V 1.5 V Source  P29 GND Ground  P30² Two Wire Interface Two Wire Interface Clock  P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P20              | Reserved              | No Connect                                                              |  |

| P23 +B Host Receiver Differential Signal Pair (This is an output of the SSD)  P24 +3.3 V 3.3 V Source  P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD)  P26 GND Ground  P27 GND Ground  P28 <sup>1</sup> +1.5 V 1.5 V Source  P29 GND Ground  P30 <sup>2</sup> Two Wire Interface Two Wire Interface Clock  P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P21              | GND                   | Ground                                                                  |  |

| P24 +3.3 V 3.3 V Source  P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD)  P26 GND Ground  P27 GND Ground  P28¹ +1.5 V 1.5 V Source  P29 GND Ground  P30² Two Wire Interface Two Wire Interface Clock  P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P22              | Reserved              | No Connect                                                              |  |

| P25 -B Host Receiver Differential Signal Pair (This is an output of the SSD)  P26 GND Ground  P27 GND Ground  P281 +1.5 V 1.5 V Source  P29 GND Ground  P302 Two Wire Interface Two Wire Interface Clock  P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P23              | +B                    | Host Receiver Differential Signal Pair (This is an output of the SSD)   |  |

| P26 GND Ground  P27 GND Ground  P281 +1.5 V 1.5 V Source  P29 GND Ground  P302 Two Wire Interface Two Wire Interface Clock  P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P24              | +3.3 V                | 3.3 V Source                                                            |  |

| P27 GND Ground  P28 <sup>1</sup> +1.5 V 1.5 V Source  P29 GND Ground  P30 <sup>2</sup> Two Wire Interface Two Wire Interface Clock  P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P25              | -В                    | Host Receiver Differential Signal Pair (This is an output of the SSD)   |  |

| P28 <sup>1</sup> +1.5 V 1.5 V Source  P29 GND Ground  P30 <sup>2</sup> Two Wire Interface Two Wire Interface Clock  P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P26              | GND                   | Ground                                                                  |  |

| P29 GND Ground  P30 <sup>2</sup> Two Wire Interface Two Wire Interface Clock  P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P27              | GND                   | Ground                                                                  |  |

| P30 <sup>2</sup> Two Wire Interface Two Wire Interface Clock P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P28 <sup>1</sup> | +1.5 V                | 1.5 V Source                                                            |  |

| P31 -A Host Transmitter Differential Signal Pair (This is an input of the SSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P29              | GND                   | Ground                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P30 <sup>2</sup> | Two Wire Interface    | Two Wire Interface Clock                                                |  |

| P32 <sup>2</sup> Two Wire Interface Two Wire Interface Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P31              | -A                    | Host Transmitter Differential Signal Pair (This is an input of the SSD) |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P32 <sup>2</sup> | Two Wire Interface    | Two Wire Interface Data                                                 |  |

September 2013

Order Number: 329280-002US

**Product Specification**

15

Table 11. Serial ATA Power Pin Definitions

| Pin <sup>1</sup> | Function           | Definition                                                              |

|------------------|--------------------|-------------------------------------------------------------------------|

| P33              | +A                 | Host Transmitter Differential Signal Pair (This is an input of the SSD) |

| P34              | GND                | Ground                                                                  |

| P35              | GND                | Ground                                                                  |

| P36              | Reserved           | No Connect                                                              |

| P37              | GND                | Ground                                                                  |