**Programmer's Guide**

**April 2005**

Document Number: 252539, Revision: 007

Download from Www.Somanuals.com. All Manuals Search And Download.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled platforms may require licenses from various entities, including Intel Corporation.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Chips, Dialogic, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantlP, Intel, Intel Centrino, Intel Centrino logo, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Xcon, Intel XScale, IPLink, Itanium, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PDCharm, Pentium, II Xeon, Pentium III Xeon, Performance at Your Command, Sound Mark, The Computer Inside, The Journe, Inside, VTune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation 2005. All Rights Reserved.

IXP400 Software Version 2.0 Document Number: 252539, Revision: 007

# int<sub>el</sub>。 Contents

| 1 | Introduction                                                                                                                                                                                                                                      |                                                                                                                                                                          | .19                                                                       |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|   | <ul><li>1.2 Hardwar</li><li>1.3 Intended</li><li>1.4 How to L</li><li>1.5 About the</li><li>1.6 Related</li></ul>                                                                                                                                 | Supported by this Document<br>e Supported by this Release<br>l Audience<br>Jse this Document<br>e Processors<br>Documents                                                | . 19<br>. 19<br>. 20<br>. 20<br>. 21                                      |

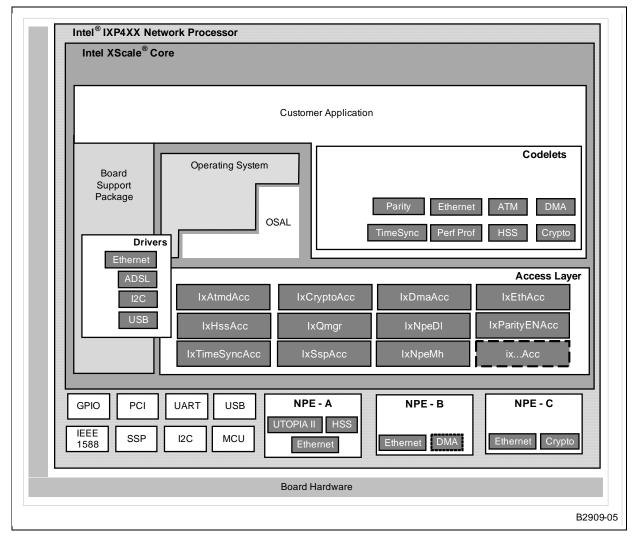

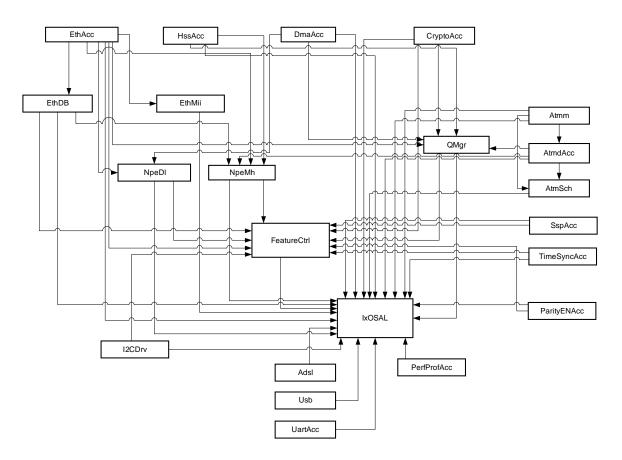

| 2 | Software Arch                                                                                                                                                                                                                                     | itecture Overview                                                                                                                                                        | .27                                                                       |

|   | <ul> <li>2.2 Deliveral</li> <li>2.3 Operatin</li> <li>2.4 Develope</li> <li>2.5 Access L</li> <li>2.6 Release</li> <li>2.7 Threadin</li> <li>2.8 Polled an</li> <li>2.9 Statistics</li> </ul>                                                     | vel Overview<br>ble Model                                                                                                                                                | .28<br>.29<br>.29<br>.30<br>.32<br>.32<br>.32                             |

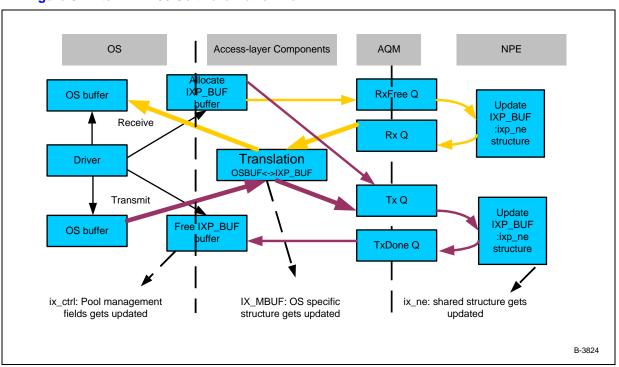

| 3 | Buffer Manage                                                                                                                                                                                                                                     | ment                                                                                                                                                                     | .35                                                                       |

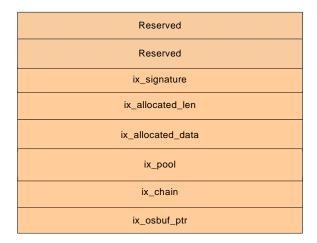

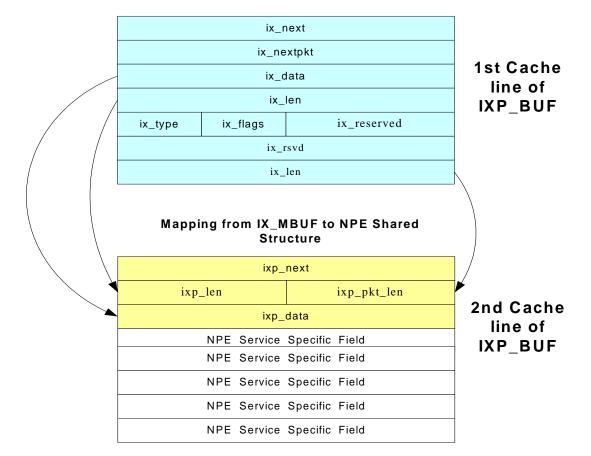

|   | <ul> <li>3.2 Overview</li> <li>3.3 IXP_BUF</li> <li>3.3.1 I</li> <li>3.4 Mapping</li> <li>3.5 IX_MBUF</li> <li>3.6 Mapping</li> <li>3.6.1 M</li> <li>3.6.2 I</li> <li>3.7 Caching</li> <li>3.7.1 F</li> <li>3.7.2 F</li> <li>3.7.3 (0)</li> </ul> | Jew<br>V                                                                                                                                                                 | .35<br>.38<br>.43<br>.44<br>.46<br>.46<br>.46<br>.47<br>.49<br>.49<br>.50 |

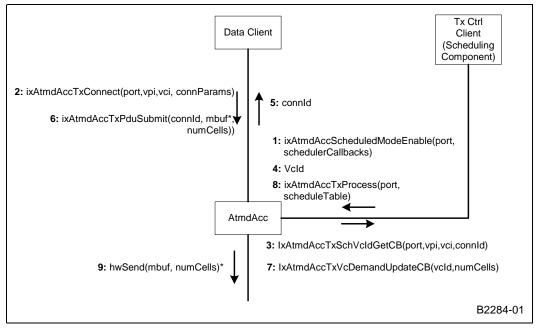

| 4 | Access-Layer                                                                                                                                                                                                                                      | Components:<br>ccess (IxAtmdAcc) API                                                                                                                                     | .53                                                                       |

|   | <ul> <li>4.1 What's N</li> <li>4.2 Overview</li> <li>4.3 IxAtmdA</li> <li>4.4 Configure</li> <li>4.4.1 U</li> <li>4.4.2 A</li> <li>4.4.3 N</li> </ul>                                                                                             | Iewv<br>v<br>cc Component Features<br>ation Services<br>UTOPIA Port-Configuration Service<br>ATM Traffic-Shaping Services<br>VC-Configuration Services<br>ssion Services | .53<br>.53<br>.55<br>.55<br>.55<br>.55                                    |

IXP400 Software Version 2.0 Document Number: 252539, Revision: 007

April 2005

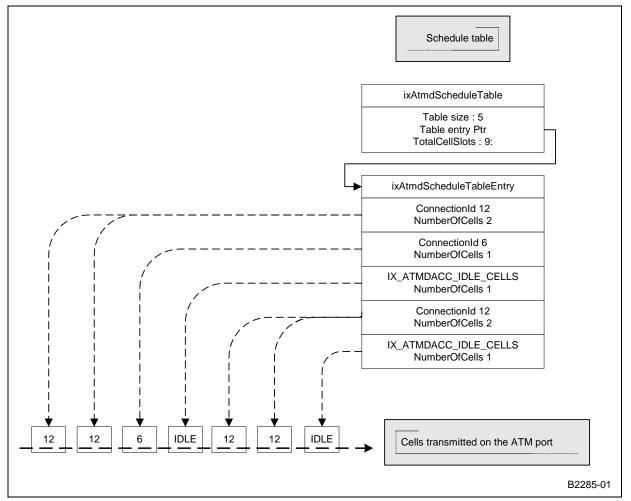

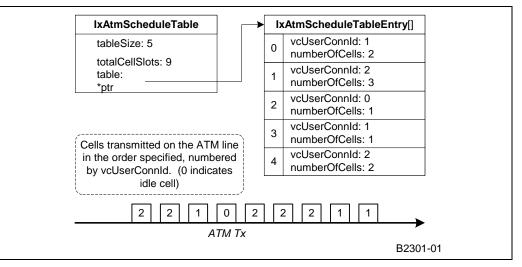

|   |       | 4.5.1    | Schedule           | ed Transmission                             |    |

|---|-------|----------|--------------------|---------------------------------------------|----|

|   |       |          | 4.5.1.1            | Schedule Table Description                  |    |

|   |       | 4.5.2    | Transmis           | ssion Triggers (Tx-Low Notification)        | 60 |

|   |       |          | 4.5.2.1            | Transmit-Done Processing                    |    |

|   |       |          | 4.5.2.2            | Transmit Disconnect                         |    |

|   |       | 4.5.3    |                    | Services                                    |    |

|   |       |          | 4.5.3.1            | Receive Triggers (Rx-Free-Low Notification) |    |

|   |       |          | 4.5.3.2            | Receive Processing                          |    |

|   |       |          | 4.5.3.3            | Receive Disconnect                          |    |

|   |       | 4.5.4    |                    | anagement                                   |    |

|   |       |          | 4.5.4.1            | Buffer Allocation                           |    |

|   |       |          | 4.5.4.2<br>4.5.4.3 | Buffer Contents<br>Buffer-Size Constraints  |    |

|   |       |          | 4.5.4.3            | Buffer-Chaining Constraints                 |    |

|   |       | 4.5.5    |                    | ndling                                      |    |

|   |       | 4.5.5    | 4.5.5.1            | API-Usage Errors                            |    |

|   |       |          | 4.5.5.1            | Real-Time Errors                            |    |

|   |       |          |                    |                                             |    |

| 5 | Acces | ss-Layei | r Compo            | nents:                                      |    |

|   | ΑΤΜ Ι | Manage   | r (IxAtmn          | n) API                                      | 71 |

|   | 5.1   | What's   | New                |                                             | 71 |

|   | 5.2   |          |                    | N                                           |    |

|   | 5.3   |          |                    | ent Features                                |    |

|   | 5.4   |          |                    | Port Initialization                         |    |

|   | 5.5   |          |                    | gement Service Model                        |    |

|   | 5.6   |          |                    | onfiguration                                |    |

|   | 5.7   |          |                    | , ingeneated in                             |    |

|   | 5.8   | •        |                    |                                             |    |

|   | 5.9   |          | 0                  | erfaces                                     |    |

|   | 5.10  |          |                    | ments                                       |    |

|   | 5.11  |          |                    |                                             |    |

|   | -     |          |                    |                                             |    |

| 6 |       |          | r Compo            |                                             |    |

|   | ATM 1 | Fransmi  | it Schedu          | ıler (IxAtmSch) API                         | 79 |

|   | 6.1   | What's   | New                |                                             |    |

|   | 6.2   |          |                    |                                             |    |

|   | 6.3   | IxAtmS   | ch Compo           | onent Features                              |    |

|   | 6.4   |          |                    | ission Control (CAC) Function               |    |

|   | 6.5   |          |                    | Traffic Shaping                             |    |

|   |       | 6.5.1    | -                  | e Table                                     |    |

|   |       |          | 6.5.1.1            | Minimum Cells Value (minCellsToSchedule)    |    |

|   |       |          | 6.5.1.2            | Maximum Cells Value (maxCells)              |    |

|   |       | 6.5.2    | Schedule           | e Service Model                             |    |

|   |       | 6.5.3    |                    | nd Idle Cells                               |    |

|   | 6.6   |          |                    |                                             |    |

|   | 6.7   | •        |                    |                                             |    |

|   | 6.8   |          | •                  | ments                                       |    |

|   |       | 6.8.1    |                    | Ze                                          |    |

|   |       | 6.8.2    |                    |                                             |    |

|   | 6.9   |          |                    |                                             |    |

|   |       | 6.9.1    |                    |                                             |    |

|   |       |          | ,                  |                                             |    |

IXP400 Software Version 2.0 Document Number: 252539, Revision: 007

#### Intel<sup>®</sup> IXP400 Software Contents

# intel®

|      | ess-Layer<br>arity (IxCr | -         | ) API                                                                         |  |

|------|--------------------------|-----------|-------------------------------------------------------------------------------|--|

| 7.1  |                          |           | ·                                                                             |  |

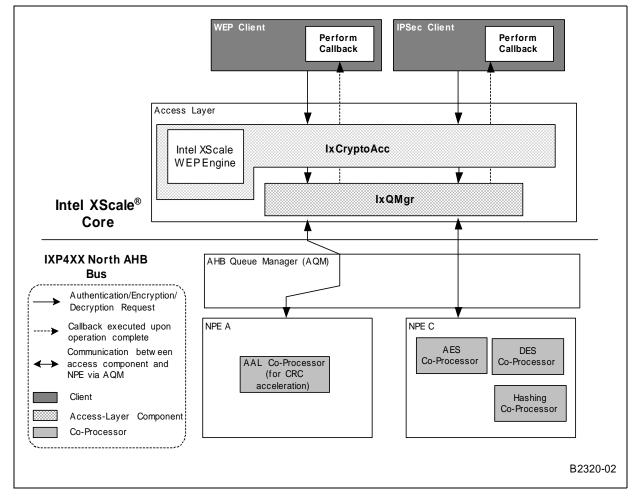

| 7.2  | Overviev                 | w         |                                                                               |  |

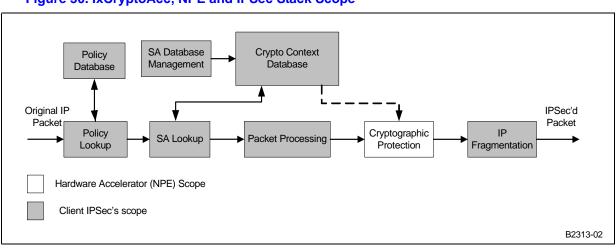

| 7.3  |                          |           | Architecture                                                                  |  |

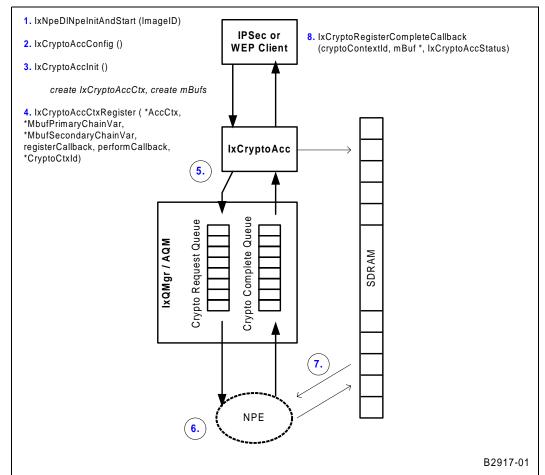

|      |                          |           | Acc Interfaces                                                                |  |

|      |                          |           | I Flow                                                                        |  |

|      |                          |           | Registration and the Cryptographic Context Database                           |  |

|      |                          |           | d Queue Management                                                            |  |

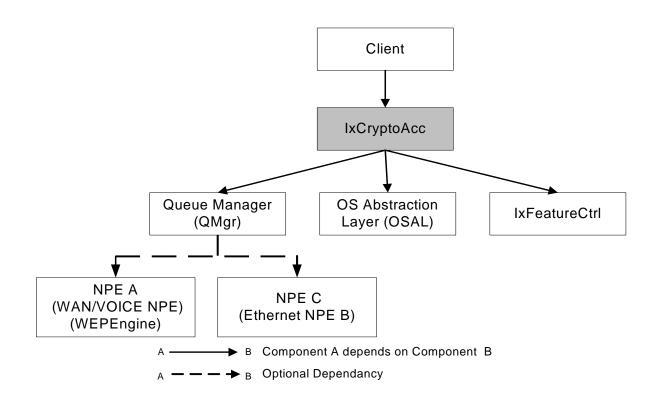

|      |                          |           | Requirements                                                                  |  |

|      |                          |           | ncies                                                                         |  |

|      |                          |           | I Functionality                                                               |  |

|      |                          |           | ndling                                                                        |  |

|      |                          |           | PSS                                                                           |  |

|      |                          |           | nd Export of Cryptographic Technology                                         |  |

| 7.4  |                          | •         |                                                                               |  |

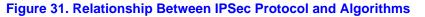

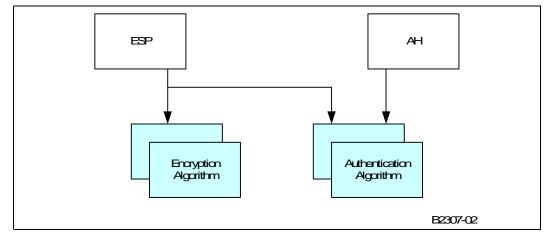

| 1.7  |                          |           | ackground and Implementation                                                  |  |

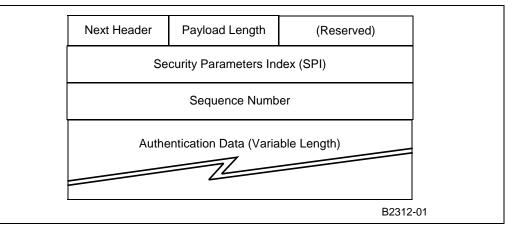

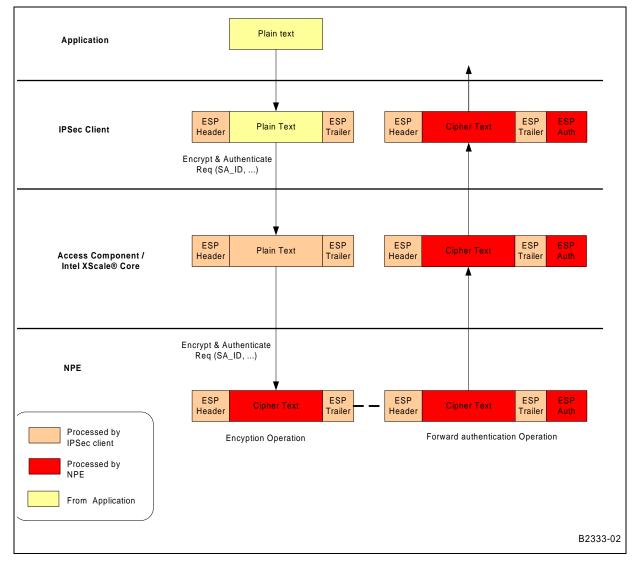

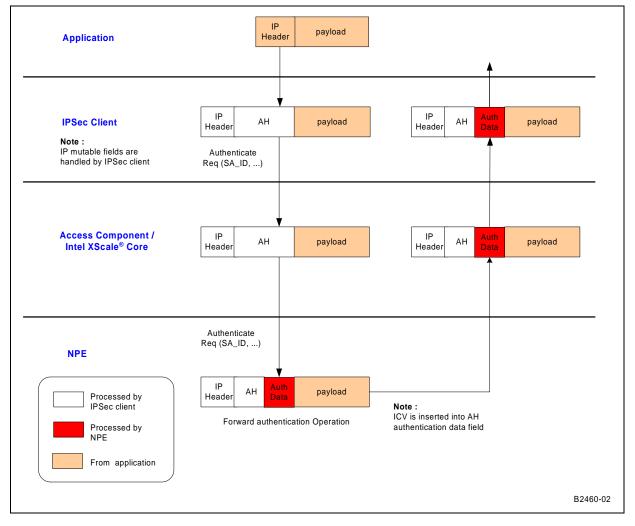

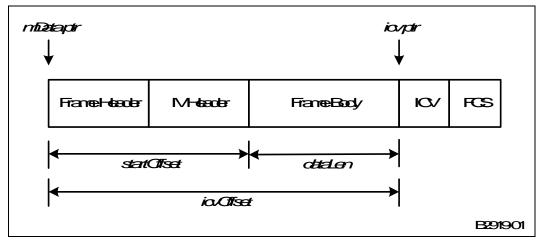

|      |                          |           | acket Formats                                                                 |  |

|      |                          | 7.4.2.1   | Reference ESP Dataflow                                                        |  |

|      |                          | 7.4.2.2   | Reference AH Dataflow                                                         |  |

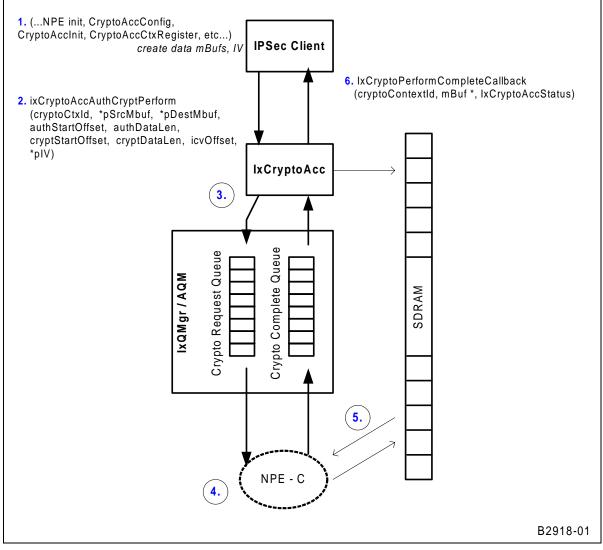

|      |                          |           | e Acceleration for IPSec Services                                             |  |

|      |                          |           | PI Call Flow                                                                  |  |

|      |                          |           | API Use Cases                                                                 |  |

|      |                          | 7.4.5.1   | HMAC with Key Size Greater Than 64 Bytes                                      |  |

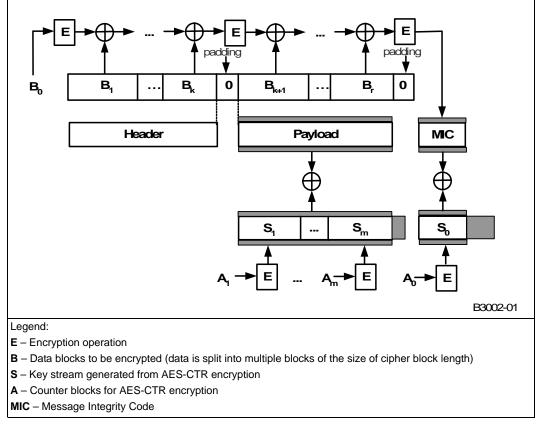

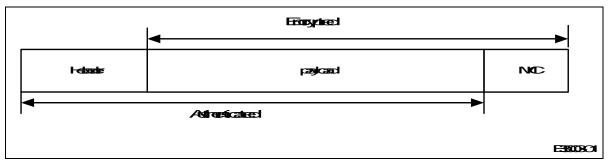

|      |                          | 7.4.5.2   | Performing CCM (AES CTR-Mode Encryption and AES                               |  |

|      |                          |           | CBC-MAC Authentication) for IPSec                                             |  |

|      |                          |           | sumptions, Dependencies, and Limitations                                      |  |

| 7.5  |                          |           |                                                                               |  |

|      |                          |           | ckground and Implementation                                                   |  |

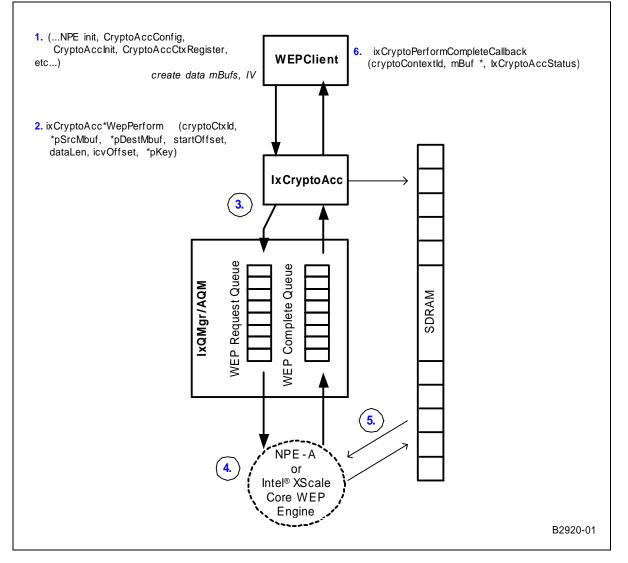

|      |                          |           | e Acceleration for WEP Services                                               |  |

|      | 7.5.3                    | WEP AP    | I Call Flow                                                                   |  |

| 7.6  | SSL and                  | d TLS Pro | otocol Usage Models                                                           |  |

| 7.7  | Support                  | ed Encry  | ption and Authentication Algorithms                                           |  |

|      | 7.7.1                    | Encryptic | on Algorithms                                                                 |  |

|      | 7.7.2                    | Cipher N  | odes                                                                          |  |

|      |                          | 7.7.2.1   | Electronic Code Book (ECB)                                                    |  |

|      |                          | 7.7.2.2   | Cipher Block Chaining (CBC)                                                   |  |

|      |                          | 7.7.2.3   | Counter Mode (CTR)                                                            |  |

|      |                          | 7.7.2.4   | Counter-Mode Encryption with CBC-MAC Authentication (CCM) for CCMP in 802.11i |  |

|      | 7.7.3                    | Authentio | cation Algorithms                                                             |  |

| Acce | ess-Layer                | Compor    | nents:                                                                        |  |

|      | •                        | -         | DmaAcc) API                                                                   |  |

| 8.1  |                          |           |                                                                               |  |

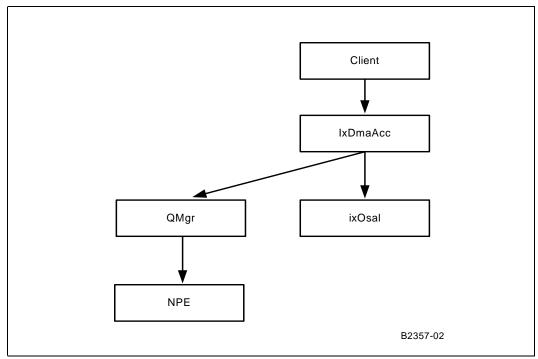

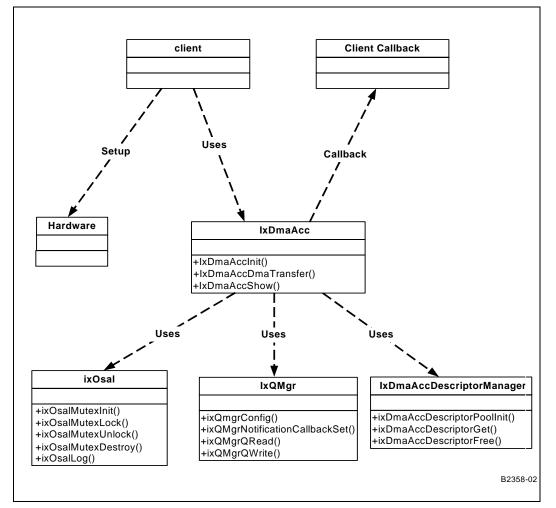

| 8.2  | Overview                 | w         |                                                                               |  |

| 8.3  |                          |           |                                                                               |  |

| 8.4  |                          |           |                                                                               |  |

| 8.5  |                          |           |                                                                               |  |

| 8.6  |                          |           | er API                                                                        |  |

IXP400 Software Version 2.0 Document Number: 252539, Revision: 007 April 2005

|   |       | 8.6.1     | IxDmaAc    | cDescriptorManager                                           | . 1 | 18 |

|---|-------|-----------|------------|--------------------------------------------------------------|-----|----|

|   | 8.7   | Parame    |            | ription                                                      |     |    |

|   |       | 8.7.1     |            |                                                              |     |    |

|   |       | 8.7.2     | Destinatio | on Address                                                   | . 1 | 19 |

|   |       | 8.7.3     | Transfer   | Mode                                                         | . 1 | 19 |

|   |       | 8.7.4     |            | Width                                                        |     |    |

|   |       | 8.7.5     |            | ng Modes                                                     |     |    |

|   |       | 8.7.6     |            | Length                                                       |     |    |

|   |       | 8.7.7     |            | d Modes                                                      |     |    |

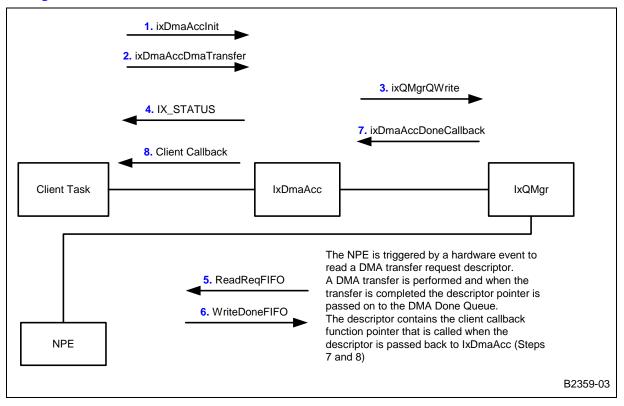

|   | 8.8   | Data Fl   |            |                                                              |     |    |

|   | 8.9   | Control   | Flow       |                                                              | . 1 | 23 |

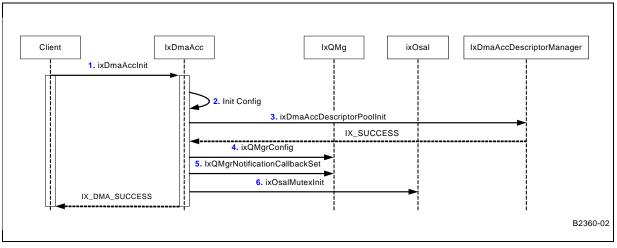

|   |       | 8.9.1     | DMA Initi  | alization                                                    | . 1 | 24 |

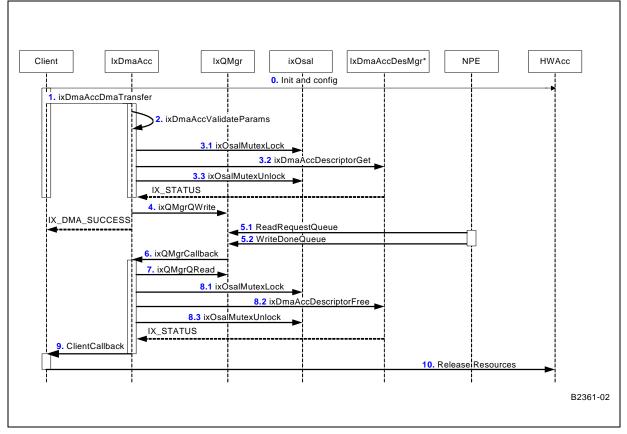

|   |       | 8.9.2     |            | nfiguration and Data Transfer                                |     |    |

|   | 8.10  | Restrict  |            | e DMA Transfer                                               |     |    |

|   | 8.11  | Error H   | andling    |                                                              | . 1 | 28 |

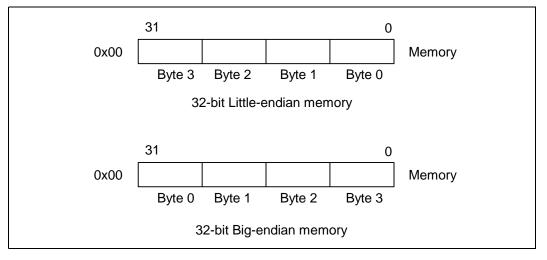

|   | 8.12  | Little Er | ndian      |                                                              | . 1 | 28 |

| 9 | A     |           | Compos     | anta.                                                        |     |    |

| 9 |       | -         | r Compor   |                                                              |     | ~~ |

|   | Ether |           | -          | nAcc) API                                                    |     |    |

|   | 9.1   |           |            |                                                              |     |    |

|   | 9.2   |           |            | W                                                            |     |    |

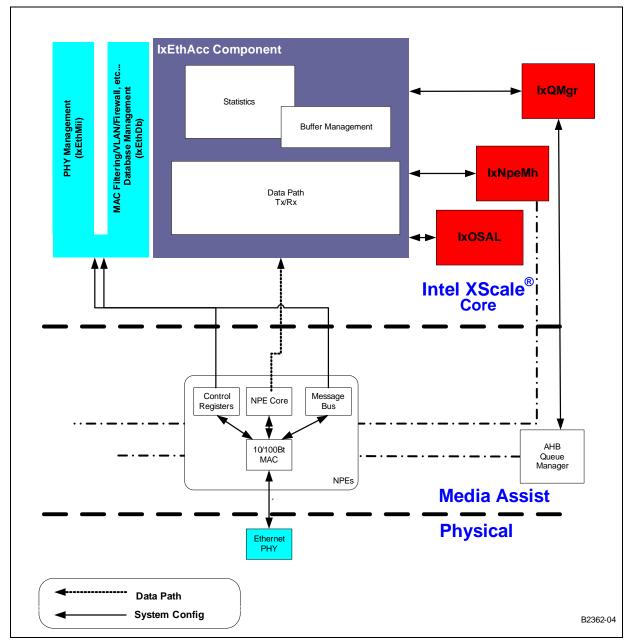

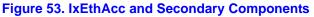

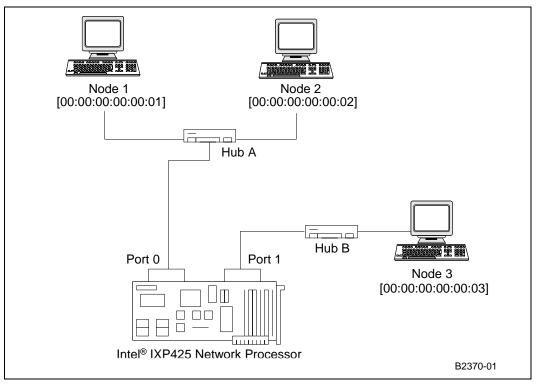

|   | 9.3   | Etherne   |            | Layers: Architectural Overview                               |     |    |

|   |       | 9.3.1     |            | ne Ethernet NPE Microcode                                    |     |    |

|   |       | 9.3.2     |            | anager                                                       |     |    |

|   |       | 9.3.3     |            | /Filtering Database                                          |     |    |

|   |       | 9.3.4     |            | Y Configuration                                              |     |    |

|   | 9.4   |           |            | Layers: Component Features                                   |     |    |

|   | 9.5   |           |            |                                                              |     |    |

|   |       | 9.5.1     |            | ilization                                                    |     |    |

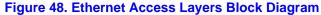

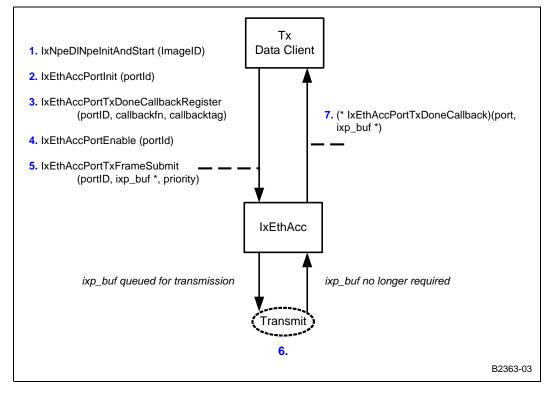

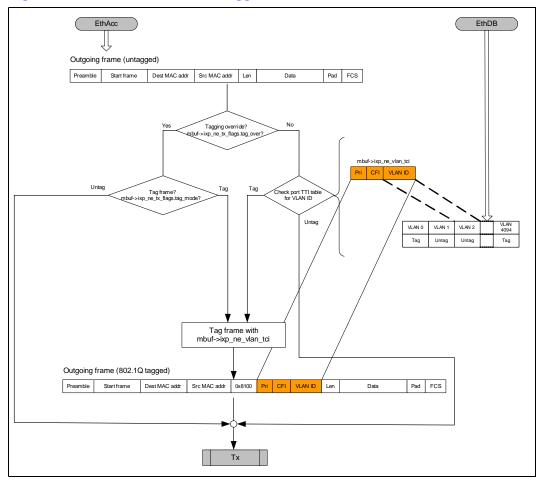

|   |       | 9.5.2     |            | Frame Transmission                                           |     |    |

|   |       |           | 9.5.2.1    | Transmission Flow                                            |     |    |

|   |       |           | 9.5.2.2    | Transmit Buffer Management and Priority                      |     |    |

|   |       | 0 5 2     | 9.5.2.3    | Using Chained IX_OSAL_MBUFs for Transmission / Buffer Sizing |     |    |

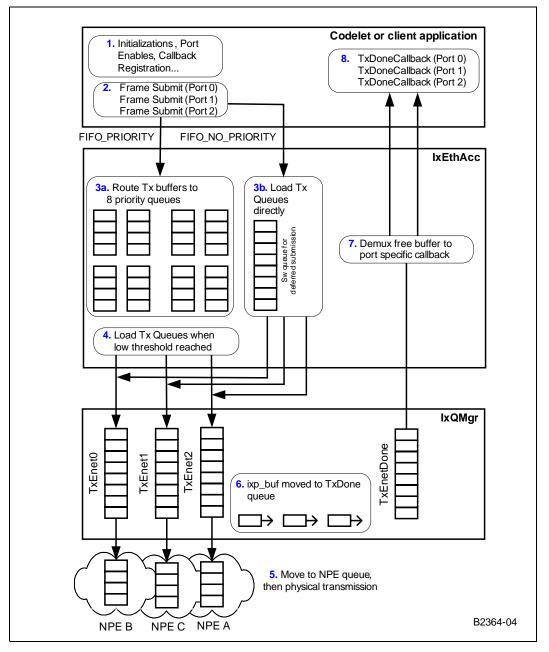

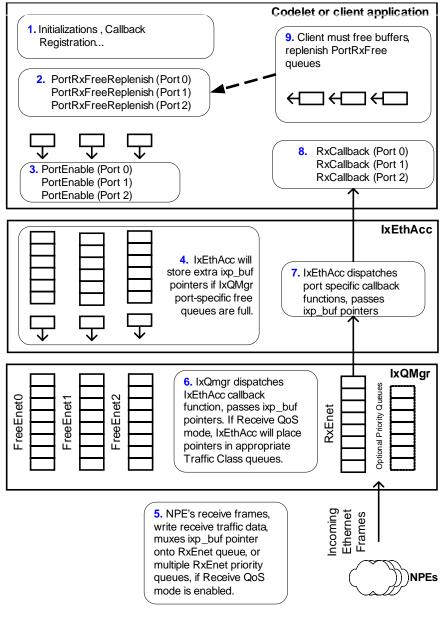

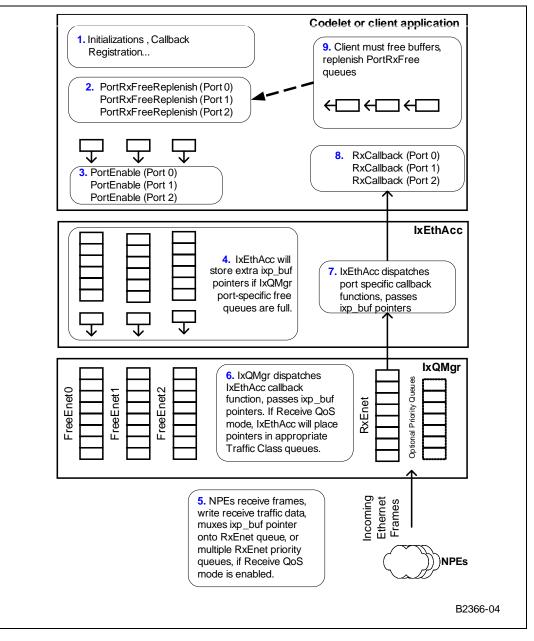

|   |       | 9.5.3     | 9.5.3.1    | Frame Reception                                              |     |    |

|   |       |           | 9.5.3.1    | Receive Flow<br>Receive Buffer Management and Priority       |     |    |

|   |       |           | 9.5.3.3    | Additional Receive Path Information                          |     |    |

|   |       | 954       |            | ne Endianness                                                |     |    |

|   |       | 9.5.5     | Maximum    | n Ethernet Frame Size                                        | 1   | 43 |

|   | 9.6   |           |            |                                                              |     | -  |

|   |       | 9.6.1     |            | MAC Control                                                  |     |    |

|   |       |           | 9.6.1.1    | MAC Duplex Settings                                          |     |    |

|   |       |           | 9.6.1.2    | MII I/O                                                      |     |    |

|   |       |           | 9.6.1.3    | Frame Check Sequence                                         | . 1 | 45 |

|   |       |           | 9.6.1.4    | Frame Padding                                                |     |    |

|   |       |           | 9.6.1.5    | MAC Filtering                                                |     |    |

|   |       |           | 9.6.1.6    | 802.3x Flow Control                                          |     |    |

|   |       |           | 9.6.1.7    | NPE Loopback                                                 |     |    |

|   | 0.7   | Initialia | 9.6.1.8    | Emergency Security Port Shutdown                             |     |    |

|   | 9.7   |           |            | ctures                                                       |     |    |

|   | 9.8   | Snared    | Data Stru  |                                                              | . F | 41 |

#### Intel<sup>®</sup> IXP400 Software Contents

# intel®

|    | 9.9   | Management Information                                                                     | 152 |

|----|-------|--------------------------------------------------------------------------------------------|-----|

| 10 | Acce  | ess-Layer Components:                                                                      |     |

|    | Ether | rnet Database (IxEthDB) API                                                                | 155 |

|    | 10.1  | Overview                                                                                   |     |

|    | 10.1  | What's New.                                                                                |     |

|    | 10.3  | IxEthDB Functional Behavior                                                                |     |

|    |       | 10.3.1 MAC Address Learning and Filtering                                                  |     |

|    |       | 10.3.1.1 Learning and Filtering                                                            |     |

|    |       | 10.3.1.2 Other MAC Learning/Filtering Usage Models                                         |     |

|    |       | 10.3.1.3 Learning/Filtering General Characteristics                                        |     |

|    |       | 10.3.2 Frame Size Filtering                                                                |     |

|    |       | 10.3.2.1 Filtering Example Based Upon Maximum Frame Size                                   |     |

|    |       | 10.3.3 Source MAC Address Firewall                                                         |     |

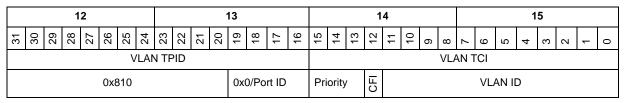

|    |       | 10.3.4 802.1Q VLAN                                                                         | 162 |

|    |       | 10.3.4.1 Background – VLAN Data in Ethernet Frames                                         |     |

|    |       | 10.3.4.2 Database Records Associated With VLAN IDs                                         |     |

|    |       | 10.3.4.3 Acceptable Frame Type Filtering                                                   | 164 |

|    |       | 10.3.4.4 Ingress Tagging and Tag Removal                                                   |     |

|    |       | 10.3.4.5 Port-Based VLAN Membership Filtering                                              |     |

|    |       | 10.3.4.6 Port and VLAN-Based Egress Tagging and Tag Removal<br>10.3.4.7 Port ID Extraction |     |

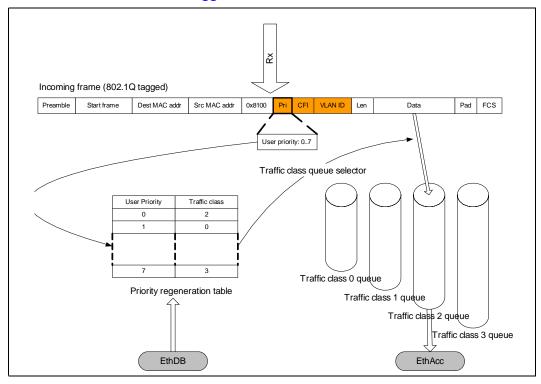

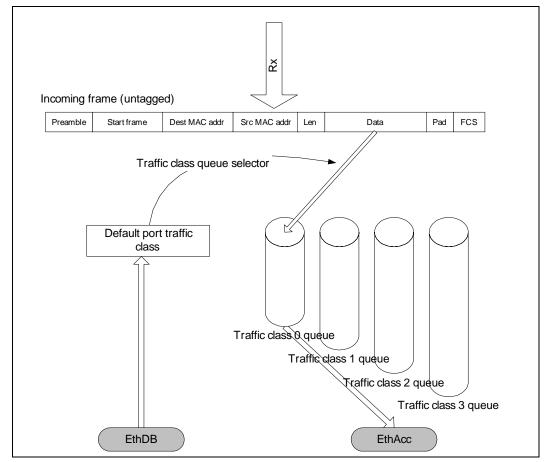

|    |       | 10.3.5 802.1Q User Priority / QoS Support                                                  |     |

|    |       | 10.3.5.1 Priority Aware Transmission                                                       |     |

|    |       | 10.3.5.2 Receive Priority Queuing                                                          |     |

|    |       | 10.3.5.3 Priority to Traffic Class Mapping                                                 |     |

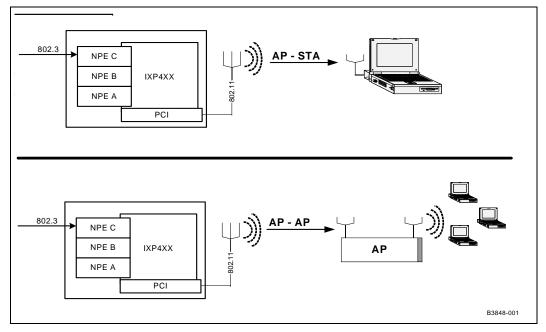

|    |       | 10.3.6 802.3 / 802.11 Frame Conversion                                                     |     |

|    |       | 10.3.6.1 Background — 802.3 and 802.11 Frame Formats                                       |     |

|    |       | 10.3.6.2 How the 802.3 / 802.11 Frame Conversion Feature Works                             |     |

|    |       | 10.3.6.3 802.3 / 802.11 API Details                                                        |     |

|    |       | 10.3.7 Spanning Tree Protocol Port Settings                                                | 177 |

|    | 10.4  | IxEthDB API                                                                                | 177 |

|    |       | 10.4.1 Initialization                                                                      | 177 |

|    |       | 10.4.2 Dependencies                                                                        | 177 |

|    |       | 10.4.3 Feature Set                                                                         | 178 |

|    |       | 10.4.4 Additional Database Features                                                        | -   |

|    |       | 10.4.4.1 User-Defined Field                                                                |     |

|    |       | 10.4.4.2 Database Clear                                                                    |     |

|    |       | 10.4.5 Dependencies on IxEthAcc Configuration                                              |     |

|    |       | 10.4.5.1 Promiscuous-Mode Requirement                                                      |     |

|    |       | 10.4.5.2 FCS Appending                                                                     | 179 |

| 11 | Acce  | ess-Layer Components:                                                                      |     |

|    |       | rnet PHY (IxEthMii) API                                                                    |     |

|    | 11.1  | What's New                                                                                 |     |

|    | 11.1  |                                                                                            |     |

|    | 11.2  | Overview<br>Features                                                                       |     |

|    | 11.3  |                                                                                            |     |

|    | 11.4  | Supported PHYs Dependencies                                                                |     |

|    | 11.5  | Dopondonoico                                                                               |     |

|    |       |                                                                                            |     |

Programmer's Guide

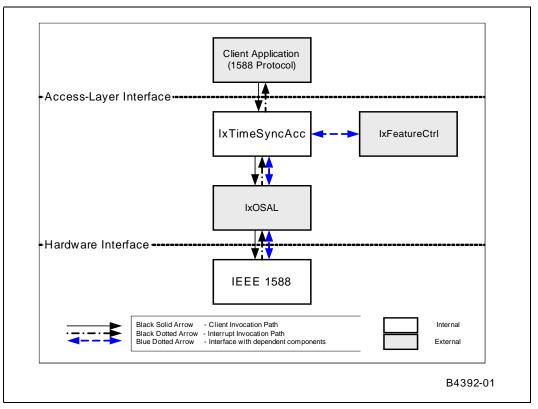

| 12 | Access-Layer Components: |                                                      |       |  |  |  |

|----|--------------------------|------------------------------------------------------|-------|--|--|--|

|    | Featu                    | re Control (IxFeatureCtrl) API                       | 183   |  |  |  |

|    | 12.1                     | What's New                                           |       |  |  |  |

|    | 12.2                     | Overview                                             |       |  |  |  |

|    | 12.3                     | Hardware Feature Control                             |       |  |  |  |

|    |                          | 12.3.1 Using the Product ID-Related Functions        |       |  |  |  |

|    |                          | 12.3.2 Using the Feature Control Register Functions  |       |  |  |  |

|    | 12.4                     | Component Check by Other APIs                        |       |  |  |  |

|    | 12.5                     | Software Configuration                               |       |  |  |  |

|    | 12.6                     | Dependencies                                         | 187   |  |  |  |

| 13 |                          | ss-Layer Components:                                 |       |  |  |  |

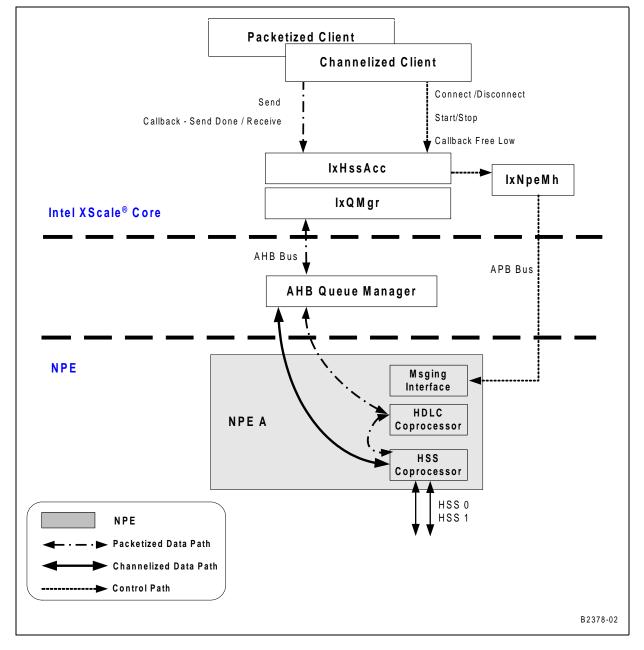

|    | HSS-                     | Access (IxHssAcc) API                                | 189   |  |  |  |

|    | 13.1                     | What's New                                           | . 189 |  |  |  |

|    | 13.2                     | Overview                                             | 189   |  |  |  |

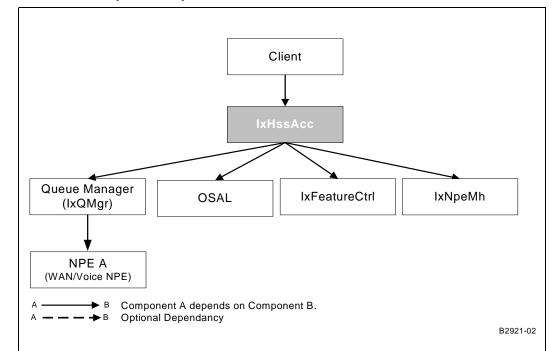

|    | 13.3                     | IxHssAcc API Overview                                | 190   |  |  |  |

|    |                          | 13.3.1 IxHssAcc Interfaces                           | 190   |  |  |  |

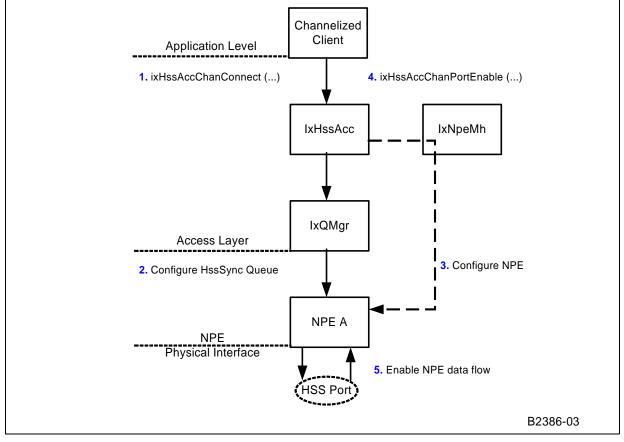

|    |                          | 13.3.2 Basic API Flow                                | 191   |  |  |  |

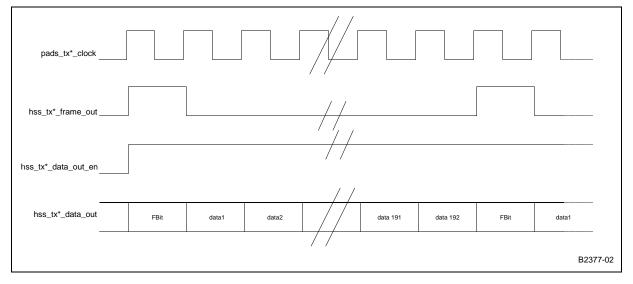

|    |                          | 13.3.3 HSS and HDLC Theory and Coprocessor Operation | 192   |  |  |  |

|    |                          | 13.3.4 High-Level API Call Flow                      | 195   |  |  |  |

|    |                          | 13.3.5 Dependencies                                  | 196   |  |  |  |

|    |                          | 13.3.6 Key Assumptions                               | 196   |  |  |  |

|    |                          | 13.3.7 Error Handling                                | 197   |  |  |  |

|    | 13.4                     | HSS Port Initialization Details                      | 197   |  |  |  |

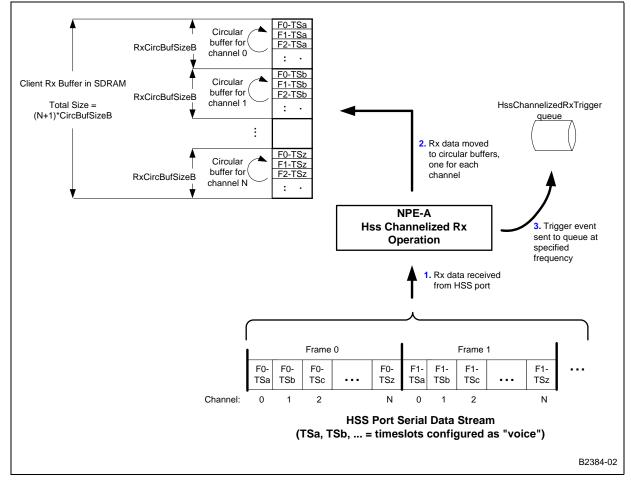

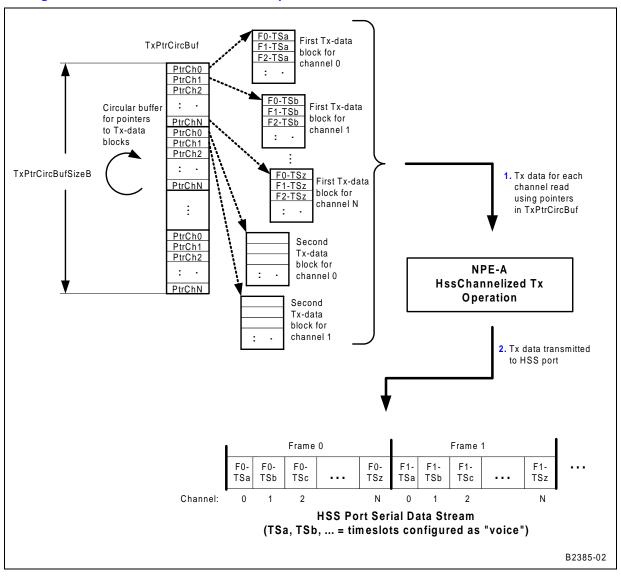

|    | 13.5                     | HSS Channelized Operation                            |       |  |  |  |

|    |                          | 13.5.1 Channelized Connect and Enable                |       |  |  |  |

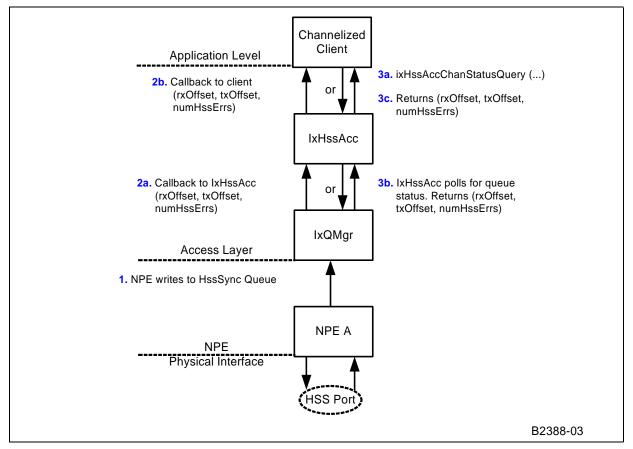

|    |                          | 13.5.2 Channelized Tx/Rx Methods                     |       |  |  |  |

|    |                          | 13.5.2.1 CallBack                                    |       |  |  |  |

|    |                          | 13.5.2.2 Polled                                      |       |  |  |  |

|    |                          | 13.5.3 Channelized Disconnect                        |       |  |  |  |

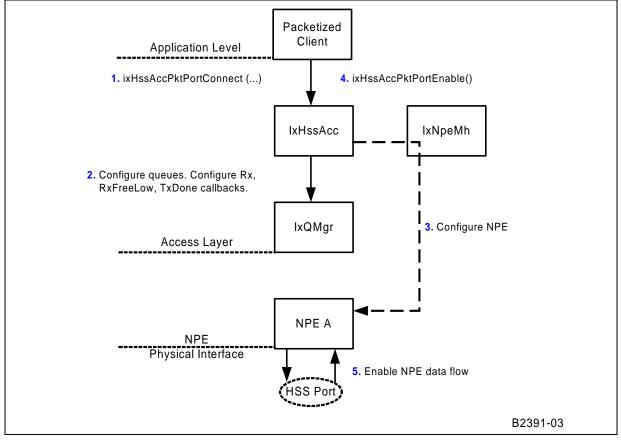

|    | 13.6                     | HSS Packetized Operation                             |       |  |  |  |

|    |                          | 13.6.1 Packetized Connect and Enable                 |       |  |  |  |

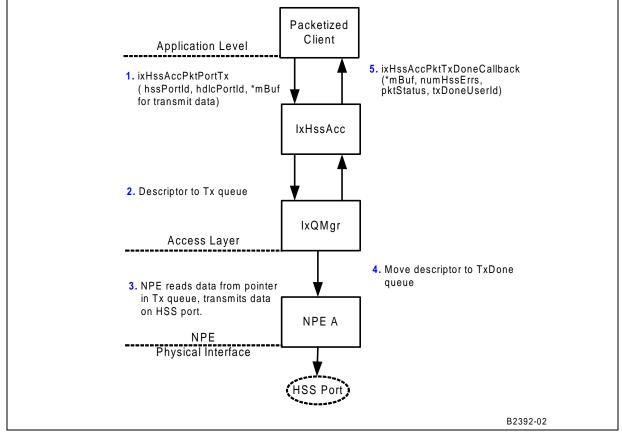

|    |                          | 13.6.2 Packetized Tx                                 |       |  |  |  |

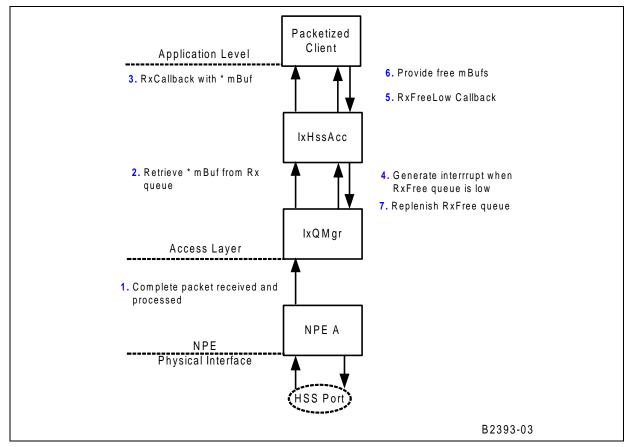

|    |                          | 13.6.3 Packetized Rx                                 |       |  |  |  |

|    |                          | 13.6.4 Packetized Disconnect                         |       |  |  |  |

|    |                          | 13.6.5 56-Kbps, Packetized Raw Mode                  |       |  |  |  |

|    | 13.7                     | Buffer Allocation Data-Flow Overview                 |       |  |  |  |

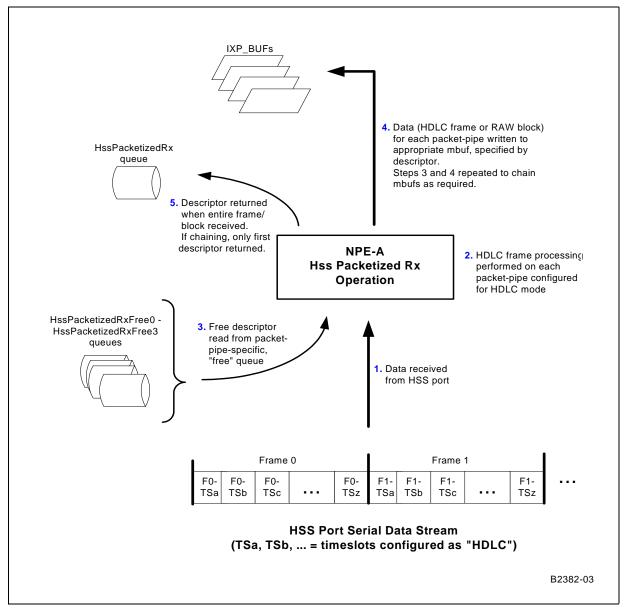

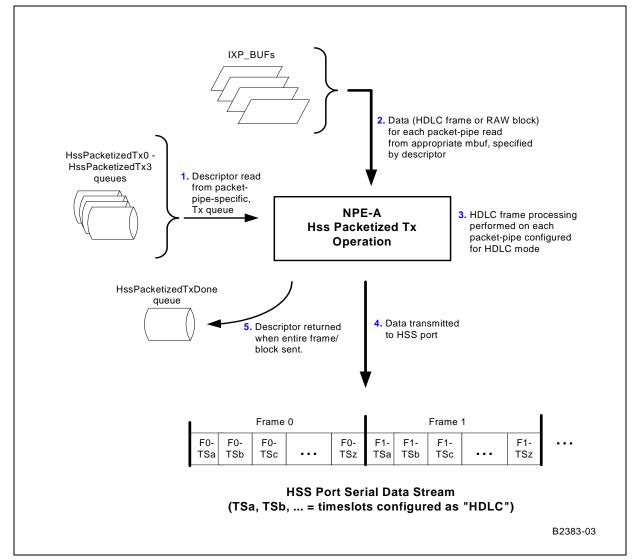

|    |                          | 13.7.1 Data Flow in Packetized Service               |       |  |  |  |

|    |                          | 13.7.2 Data Flow in Channelized Service              | 214   |  |  |  |

| 14 |                          | ss-Layer Components:                                 |       |  |  |  |

|    | NPE-I                    | Downloader (IxNpeDI) API                             | 219   |  |  |  |

|    | 14.1                     | What's New                                           | 219   |  |  |  |

|    | 14.2                     | Overview                                             |       |  |  |  |

|    | 14.3                     | Microcode Images                                     |       |  |  |  |

|    | 14.4                     | Standard Usage Example                               |       |  |  |  |

|    | 14.5                     | Custom Usage Example                                 |       |  |  |  |

|    | 14.6                     | IxNpeDI Uninitialization                             |       |  |  |  |

|    | 14.7                     | Deprecated APIs                                      | 224   |  |  |  |

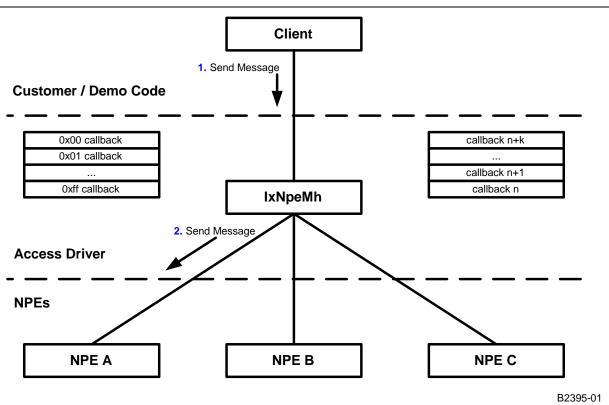

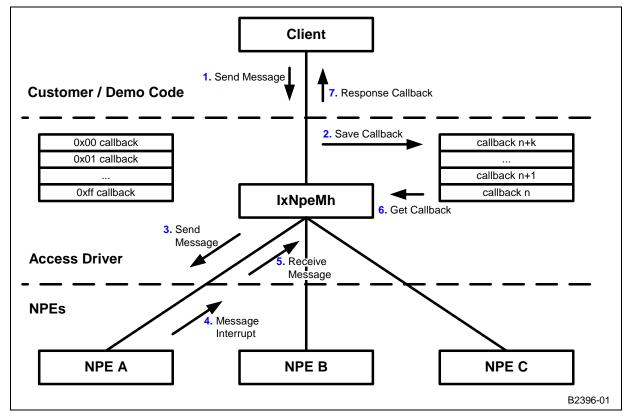

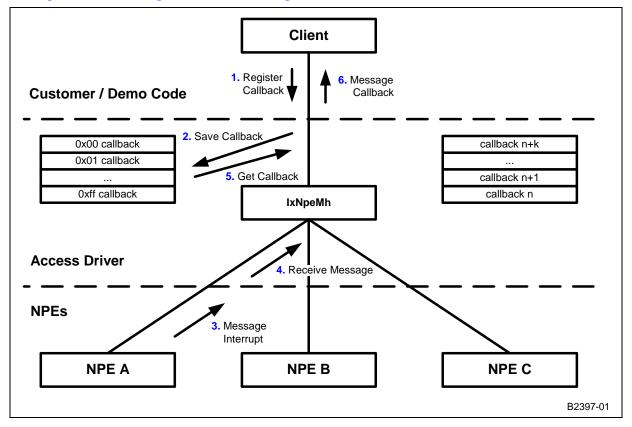

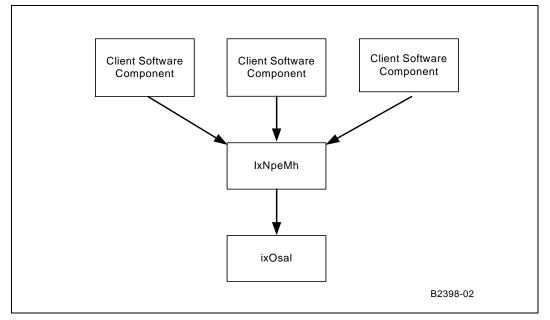

| 15 | Access-Layer Components:<br>NPE Message Handler (IxNpeMh) API |                                                                                                                         |      |  |  |  |  |

|----|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

|    |                                                               | ,                                                                                                                       |      |  |  |  |  |

|    | 15.1                                                          | What's New                                                                                                              |      |  |  |  |  |

|    | 15.2                                                          | Overview                                                                                                                |      |  |  |  |  |

|    | 15.3                                                          | Initializing the IxNpeMh                                                                                                |      |  |  |  |  |

|    |                                                               | 15.3.1 Interrupt-Driven Operation                                                                                       |      |  |  |  |  |

|    | 15.4                                                          | 15.3.2 Polled Operation<br>Uninitializing IxNpeMh                                                                       |      |  |  |  |  |

|    | -                                                             |                                                                                                                         |      |  |  |  |  |

|    | 15.5                                                          | 15.5 Sending Messages from an Intel XScale <sup>®</sup> Core Software Client to an NPE<br>15.5.1 Sending an NPE Message |      |  |  |  |  |

|    |                                                               | 15.5.2 Sending an NPE Message with Response                                                                             |      |  |  |  |  |

|    | 15.6                                                          | Receiving Unsolicited Messages from an NPE to Client Software                                                           |      |  |  |  |  |

|    | 15.7                                                          | Dependencies                                                                                                            |      |  |  |  |  |

|    | 15.8                                                          | Error Handling                                                                                                          |      |  |  |  |  |

|    |                                                               |                                                                                                                         |      |  |  |  |  |

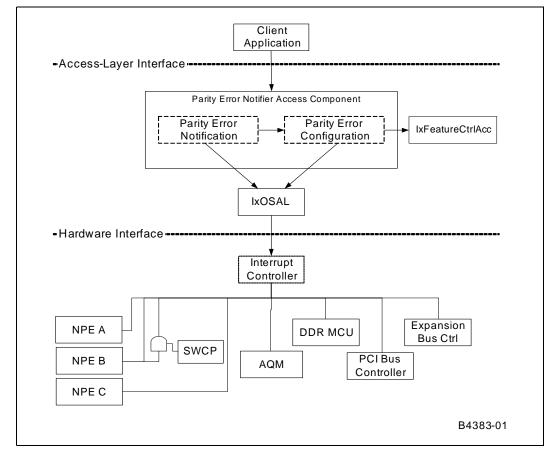

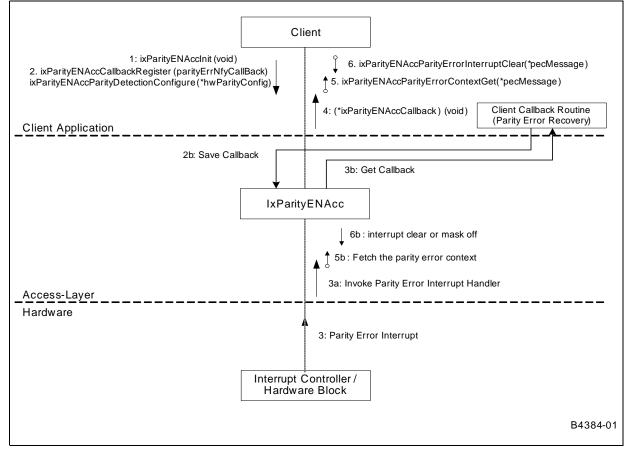

| 16 |                                                               | ss-Layer Components:                                                                                                    |      |  |  |  |  |

|    | Parity                                                        | / Error Notifier (IxParityENAcc) API                                                                                    | 233  |  |  |  |  |

|    | 16.1                                                          | What's New                                                                                                              | 233  |  |  |  |  |

|    | 16.2                                                          | Introduction                                                                                                            | 233  |  |  |  |  |

|    |                                                               | 16.2.1 Background                                                                                                       | 233  |  |  |  |  |

|    |                                                               | 16.2.2 Parity and ECC Capabilities in the                                                                               |      |  |  |  |  |

|    |                                                               | Intel <sup>®</sup> IXP45X and Intel <sup>®</sup> IXP46X Product Line                                                    |      |  |  |  |  |

|    |                                                               | 16.2.2.1 Network Processing Engines                                                                                     |      |  |  |  |  |

|    |                                                               | 16.2.2.2 Switching Coprocessor in NPE B (SWCP)                                                                          |      |  |  |  |  |

|    |                                                               | 16.2.2.3 AHB Queue Manager (AQM)<br>16.2.2.4 DDR SDRAM Memory Controller Unit (MCU)                                     |      |  |  |  |  |

|    |                                                               | 16.2.2.4 DDR SDRAM Memory Controller Onit (MCO)                                                                         |      |  |  |  |  |

|    |                                                               | 16.2.2.6 PCI Controller                                                                                                 |      |  |  |  |  |

|    |                                                               | 16.2.2.7 Secondary Effects of Parity Interrupts                                                                         |      |  |  |  |  |

|    |                                                               | 16.2.3 Interrupt Prioritization                                                                                         |      |  |  |  |  |

|    | 16.3                                                          | IxParityENAcc API Details                                                                                               |      |  |  |  |  |

|    |                                                               | 16.3.1 Features                                                                                                         |      |  |  |  |  |

|    |                                                               | 16.3.2 Dependencies                                                                                                     |      |  |  |  |  |

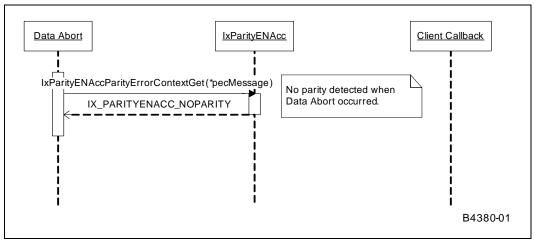

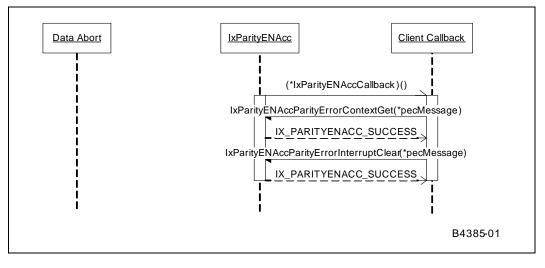

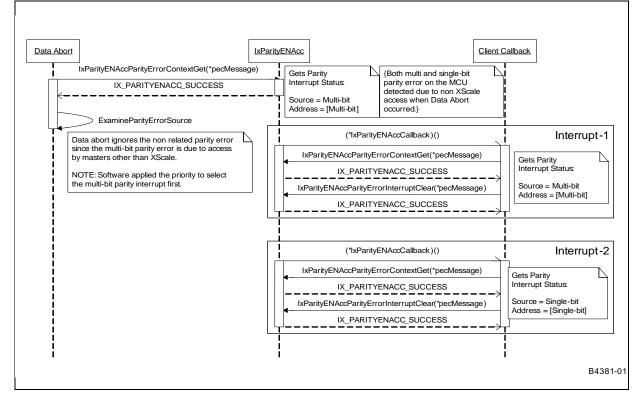

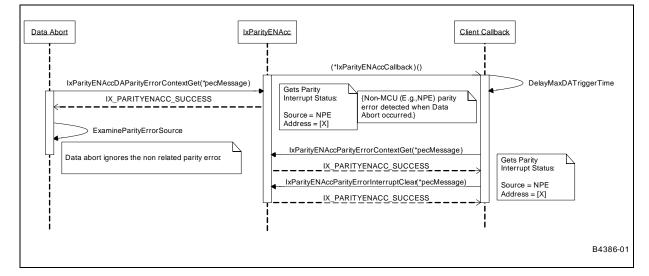

|    | 16.4                                                          | IxParityENAcc API Usage Scenarios                                                                                       |      |  |  |  |  |

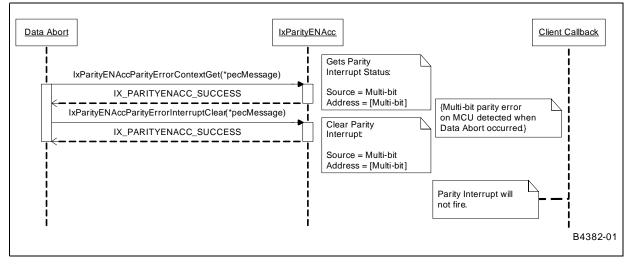

|    |                                                               | 16.4.1 Summary Parity Error Notification Scenario                                                                       | 239  |  |  |  |  |

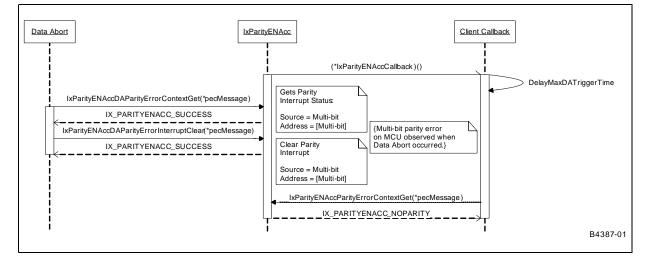

|    |                                                               | 16.4.2 Summary Parity Error Recovery Scenario                                                                           | 241  |  |  |  |  |

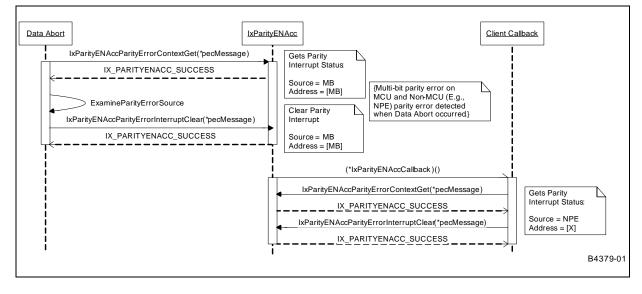

|    |                                                               | 16.4.3 Summary Parity Error Prevention Scenario                                                                         | 242  |  |  |  |  |

|    |                                                               | 16.4.4 Parity Error Notification Detailed Scenarios                                                                     | 242  |  |  |  |  |

| 17 | Acce                                                          | ss-Layer Components:                                                                                                    |      |  |  |  |  |

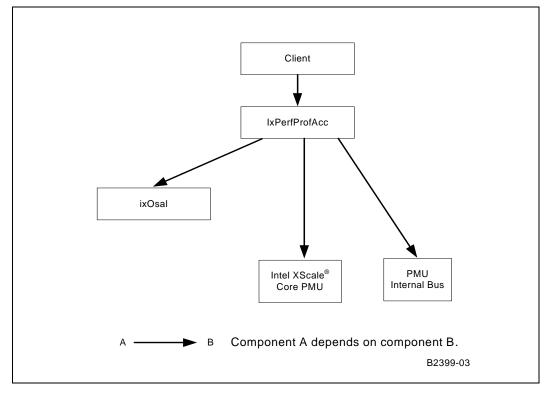

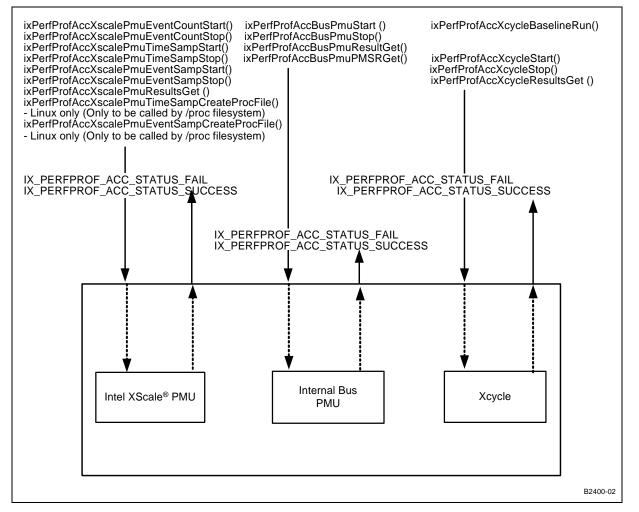

| 17 |                                                               | rmance Profiling (IxPerfProfAcc) API                                                                                    | 2/17 |  |  |  |  |

|    |                                                               |                                                                                                                         |      |  |  |  |  |

|    | 17.1                                                          | What's New                                                                                                              |      |  |  |  |  |

|    | 17.2                                                          | Overview                                                                                                                |      |  |  |  |  |

|    | 17.3                                                          | Intel XScale <sup>®</sup> Core PMU                                                                                      | -    |  |  |  |  |

|    | 47 4                                                          | 17.3.1 Counter Buffer Overflow                                                                                          |      |  |  |  |  |

|    | 17.4                                                          | Internal Bus PMU                                                                                                        |      |  |  |  |  |

|    | 17.5                                                          | Idle-Cycle Counter Utilities ('Xcycle')                                                                                 |      |  |  |  |  |

|    | 17.6                                                          |                                                                                                                         |      |  |  |  |  |

|    | 17.7                                                          | Error Handling                                                                                                          |      |  |  |  |  |

|    | 17.8                                                          | Interrupt Handling                                                                                                      | 251  |  |  |  |  |

IXP400 Software Version 2.0 Document Number: 252539, Revision: 007 April 2005

|          |                                                                                 | Threading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                      |

|----------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 17.10                                                                           | Using the API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 252                                                                                                                                                                  |

|          |                                                                                 | 17.10.1 API Usage for Intel XScale <sup>®</sup> Core PMU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

|          |                                                                                 | 17.10.1.1 Event and Clock Counting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                      |

|          |                                                                                 | 17.10.1.2 Time-Based Sampling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                      |

|          |                                                                                 | 17.10.1.3 Event-Based Sampling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 257                                                                                                                                                                  |

|          |                                                                                 | 17.10.1.4 Using Intel XScale <sup>®</sup> Core PMU to Determine Cache Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

|          |                                                                                 | 17.10.2 Internal Bus PMU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

|          |                                                                                 | 17.10.2.1 Using the Internal Bus PMU Utility to Monitor<br>Read/Write Activity on the North Bus                                                                                                                                                                                                                                                                                                                                                                                                                                             | 262                                                                                                                                                                  |

|          |                                                                                 | 17.10.3 Xcycle (Idlecycle Counter)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                      |

| 18       | A                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

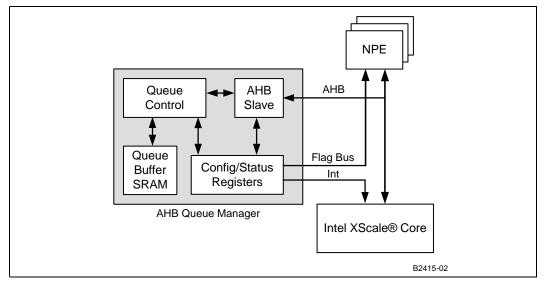

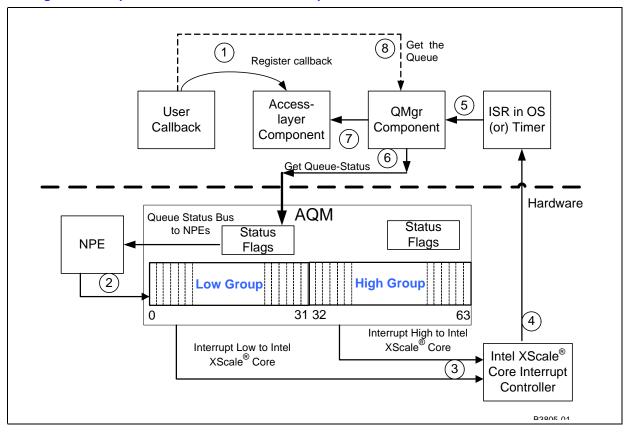

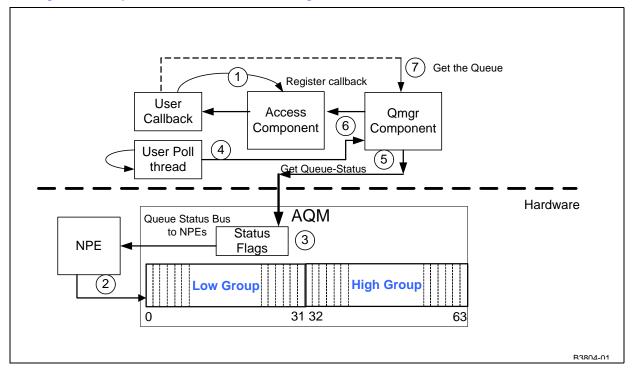

| 10       |                                                                                 | ss-Layer Components:<br>e Manager (IxQMgr) API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 265                                                                                                                                                                  |

|          |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

|          | 18.1                                                                            | What's New                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

|          | 18.2                                                                            | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

|          | 18.3                                                                            | Features and Hardware Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

|          | 18.4                                                                            | IxQMgr Initialization and Uninitialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

|          | 18.5                                                                            | Queue Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                      |

|          | 18.6                                                                            | Queue Identifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

|          | 18.7                                                                            | Configuration Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

|          | 18.8                                                                            | Dispatcher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

|          | 18.9                                                                            | Dispatcher Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

|          |                                                                                 | Livelock Prevention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                      |

|          |                                                                                 | Threading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                      |

|          | 18 12                                                                           | Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .274                                                                                                                                                                 |

|          | 10.12                                                                           | Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

| 19       | Acces                                                                           | ss-Layer Components:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

| 19       | Acces                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

| 19       | Acces                                                                           | ss-Layer Components:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 275                                                                                                                                                                  |

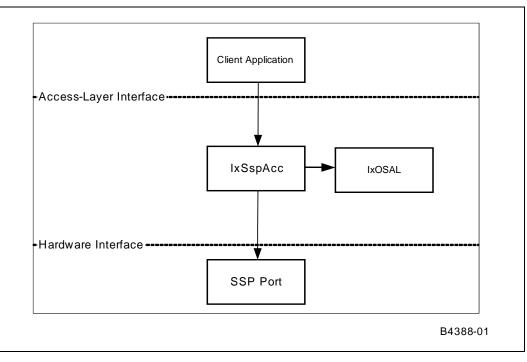

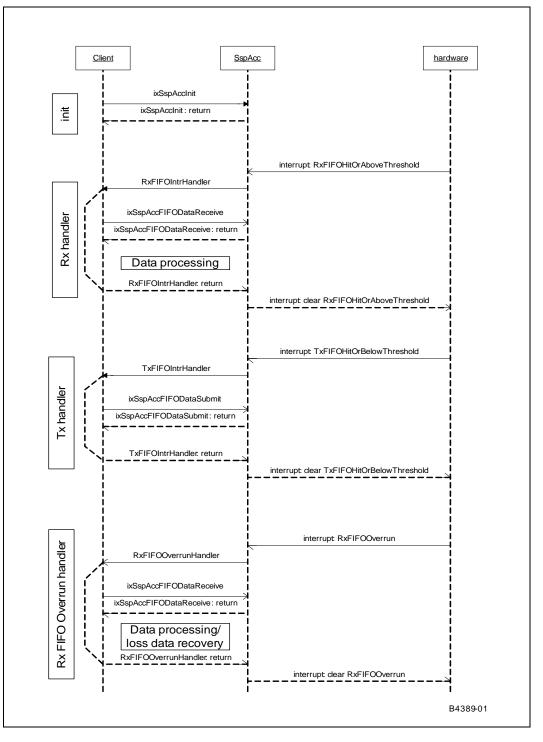

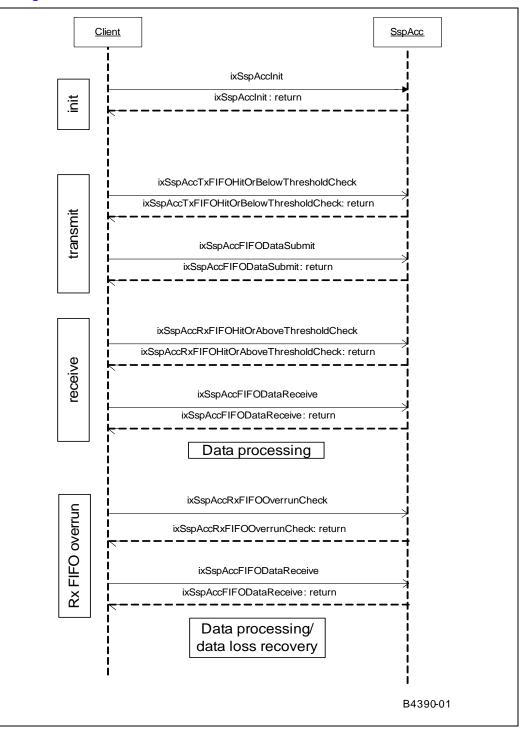

| 19       | Acces<br>Syncl                                                                  | ss-Layer Components:<br>hronous Serial Port (IxSspAcc) API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 275<br>275                                                                                                                                                           |

| 19       | Acces<br>Syncl<br>19.1                                                          | ss-Layer Components:<br>hronous Serial Port (IxSspAcc) API<br>What's New<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 275<br>275<br>275                                                                                                                                                    |

| 19       | Acces<br>Syncl<br>19.1<br>19.2                                                  | ss-Layer Components:<br>hronous Serial Port (IxSspAcc) API<br>What's New                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 275<br>275<br>275<br>275                                                                                                                                             |

| 19       | Acces<br>Syncl<br>19.1<br>19.2                                                  | ss-Layer Components:<br>hronous Serial Port (IxSspAcc) API<br>What's New<br>Introduction<br>IxSspAcc API Details                                                                                                                                                                                                                                                                                                                                                                                                                            | 275<br>275<br>275<br>275<br>275<br>275                                                                                                                               |

| 19       | Acces<br>Syncl<br>19.1<br>19.2                                                  | ss-Layer Components:<br>hronous Serial Port (IxSspAcc) API<br>What's New<br>Introduction<br>IxSspAcc API Details<br>19.3.1 Features                                                                                                                                                                                                                                                                                                                                                                                                         | 275<br>275<br>275<br>275<br>275<br>276                                                                                                                               |

| 19       | Acces<br>Syncl<br>19.1<br>19.2<br>19.3                                          | ss-Layer Components:<br>hronous Serial Port (IxSspAcc) API<br>What's New<br>Introduction<br>IxSspAcc API Details<br>19.3.1 Features<br>19.3.2 Dependencies                                                                                                                                                                                                                                                                                                                                                                                  | 275<br>275<br>275<br>275<br>275<br>276<br>277                                                                                                                        |

| 19       | Acces<br>Syncl<br>19.1<br>19.2<br>19.3                                          | ss-Layer Components:<br>hronous Serial Port (IxSspAcc) API<br>What's New<br>Introduction<br>IxSspAcc API Details<br>19.3.1 Features<br>19.3.2 Dependencies<br>IxSspAcc API Usage Models                                                                                                                                                                                                                                                                                                                                                     | 275<br>275<br>275<br>275<br>275<br>276<br>277<br>277                                                                                                                 |

| 19       | Acces<br>Syncl<br>19.1<br>19.2<br>19.3                                          | ss-Layer Components:<br>hronous Serial Port (IxSspAcc) API<br>What's New<br>Introduction<br>IxSspAcc API Details<br>19.3.1 Features<br>19.3.2 Dependencies<br>IxSspAcc API Usage Models<br>19.4.1 Initialization and General Data Model                                                                                                                                                                                                                                                                                                     | 275<br>275<br>275<br>275<br>275<br>276<br>277<br>277<br>277                                                                                                          |

| 19<br>20 | Acces<br>Syncl<br>19.1<br>19.2<br>19.3<br>19.4                                  | ss-Layer Components:<br>hronous Serial Port (IxSspAcc) API<br>What's New.<br>Introduction<br>IxSspAcc API Details<br>19.3.1 Features.<br>19.3.2 Dependencies<br>IxSspAcc API Usage Models<br>IxSspAcc API Usage Models<br>19.4.1 Initialization and General Data Model<br>19.4.2 Interrupt Mode                                                                                                                                                                                                                                             | 275<br>275<br>275<br>275<br>275<br>276<br>277<br>277<br>277                                                                                                          |