# NuDAQ<sup>®</sup> / NuIPC<sup>®</sup> PCI-7200 / cPCI-7200 / LPCI-7200S

12MB/S High Speed Digital Input/ Output Card User's Guide

©Copyright 2003 ADLINK Technology Inc.

All Rights Reserved.

Manual Rev. 2.30: October 13, 2003

Part No: 50-11102-101

The information in this document is subject to change without prior notice in order to improve reliability, design, and function and does not represent a commitment on the part of the manufacturer.

In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or inability to use the product or documentation, even if advised of the possibility of such damages.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

#### **Trademarks**

NuDAQ, NuIPC, DAQBench are registered trademarks of ADLINK Technology Inc.

Other product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

# **Getting Service from ADLINK**

Customer Satisfaction is top priority for ADLINK TECHNOLOGY INC. If you need any help or service, please contact us.

| ADLINK TECHNOLOGY INC. |                               |                                     |                   |  |  |  |  |

|------------------------|-------------------------------|-------------------------------------|-------------------|--|--|--|--|

| Web Site               | http://www.adlinktech.com     |                                     |                   |  |  |  |  |

| Sales & Service        | Service@adlinktech.com        | Service@adlinktech.com              |                   |  |  |  |  |

| TEL                    | +886-2-82265877               | +886-2-82265877 FAX +886-2-82265717 |                   |  |  |  |  |

| Address                | 9F, No. 166, Jian Yi Road, Ch | ungho City, T                       | aipei, 235 Taiwan |  |  |  |  |

Please email or FAX your detailed information for prompt, satisfactory, and consistent service.

| ı                      | Detailed Company Information                              |    |      |     |    |  |  |  |

|------------------------|-----------------------------------------------------------|----|------|-----|----|--|--|--|

| Company/Organization   |                                                           |    |      |     |    |  |  |  |

| Contact Person         |                                                           |    |      |     |    |  |  |  |

| E-mail Address         |                                                           |    |      |     |    |  |  |  |

| Address                |                                                           |    |      |     |    |  |  |  |

| Country                |                                                           |    |      |     |    |  |  |  |

| TEL                    |                                                           |    | FAX  |     |    |  |  |  |

| Web Site               |                                                           |    |      |     |    |  |  |  |

|                        | Questio                                                   | ns |      |     |    |  |  |  |

| Product Model          |                                                           |    |      |     |    |  |  |  |

| Environment            | OS: Computer Brand: M/B: Chipset: Video Card: NIC: Other: | В  | IOS: | CPI | U: |  |  |  |

| Detail Description     |                                                           |    |      |     |    |  |  |  |

| Suggestions for ADLINK |                                                           |    |      |     |    |  |  |  |

# **Table of Contents**

| Chapter | 1 Introduction                                                 | 1        |

|---------|----------------------------------------------------------------|----------|

| 1.1     | Applications                                                   | 1        |

| 1.2     | Features                                                       |          |

| 1.3     | Specifications                                                 |          |

| 1.4     | Software Supporting                                            | 4        |

|         | 1.1 Programming Library<br>1.2 PCIS-LVIEW: LabVIEW® Driver     | 4        |

|         |                                                                |          |

| == :    | 1.3 PCIS-VEE: HP-VEE Driver<br>1.4 DAQBench™: ActiveX Controls | 5        |

|         | 4.5 DASYLab™ PRO                                               | 5        |

|         | 4.5 DASYLab <sup>TM</sup> PRO                                  | 5        |

|         | 4.7        PCIS-ISG:                                           | 6        |

| 1.4     | 4.8 PCIS-ICL: InControl <sup>™</sup> Driver                    | 6        |

| 1.4     | 4.9 PCIS-OPC: OPC Server                                       | 6        |

| Chapter | 2 Installation                                                 | <b>7</b> |

| 2.1     | What Included                                                  |          |

| 2.2     | Unpacking                                                      | 8        |

| 2.3     | Device Installation for Windows Systems                        | 8        |

| 2.4     | PCI-7200/cPCI-7200/LPCI-7200S's Layout                         | 9        |

| 2.5     | Hardware Installation Outline                                  |          |

| 2.6     | Connector Pin Assignments                                      |          |

|         | 5.1 PCI-7200 Pin Assignments                                   | 14       |

|         | 5.2 cPCI-7200 Pin Assignments                                  |          |

| 2.7     | 8254 for Timer Pacer Generation                                |          |

| 2.8     | LPCI-7200S PCI Bus Signaling                                   |          |

| 2.9     | Onboard Pull-ups and Terminations in digital input             | 20       |

| Chanter | 3 Register Format                                              |          |

| 3.1     | I/O Registers Format                                           |          |

| 3.1     | Digital Input Register (BASE + 10)                             | 21       |

| 3.3     | Digital Output Register (BASE + 14)                            | 22       |

| 3.4     | DIO Status & Control Register (BASE + 18)                      | 22       |

| 3.5     | Interrupt Status & Control Register (BASE + 1C)                | 24       |

| 3.6     | 8254 Timer Registers (BASE + 0)                                |          |

| Chapter | 4 Operation Theory                                             | 29       |

| 4.1     | Direct Program Control                                         | 29       |

| 4.2     | Timer Pacer Mode                                               |          |

|      | 4.3          | External Clock Mode            | 31  |

|------|--------------|--------------------------------|-----|

|      | 4.4          | Handshaking                    | 31  |

|      | 4.5          | Timing Characteristic          | 33  |

| Cha  | apter        | 5 C/C++ Libraries              | 37  |

|      | <b>5</b> .1  | Libraries Installation         |     |

|      | 5.2          | Programming Guide              |     |

|      |              | 2.1 Naming Convention          | 38  |

|      |              | 2.2 Data Types                 |     |

|      | 5.3          | _7200_Initial                  | 39  |

|      | 5.4          | _7200_Switch_Card_No           | 40  |

|      | 5.5          | _7200_AUX_DI                   |     |

|      | 5.6          | _7200_AUX_DI_Channel           |     |

|      | 5.7          | _7200_AUX_DO                   |     |

|      | 5.8          | _7200_AUX_DO_Channel           |     |

|      | 5.9          | _7200_DI                       |     |

|      | 5.10         | _7200_DI_Channel               |     |

|      | 5.11         | _7200_DO                       |     |

|      | 5.12         | _7200_DO_Channel               |     |

|      | 5.13         | _7200_Alloc_DMA_Mem            | 40  |

|      | 5.14<br>5.15 | _7200_Free_DMA_Mem             | 40  |

|      | 5.16         | 7200_Alloc_DBDMA_Mem           | 40  |

|      | 5.17         | 7200 DI DMA Start              |     |

|      | 5.17         | _7200_DI_DMA_Status            |     |

|      | 5.10         | _7200_DI_DMA_Status            |     |

|      | 5.20         | 7200 DblBufferMode             |     |

|      | 5.21         | 7200 CheckHalfReady            |     |

|      | 5.22         | 7200 DblBufferTransfer         |     |

|      | 5.23         | _7200_GetOverrunStatus         |     |

|      | 5.24         |                                | 53  |

|      | 5.25         |                                | 54  |

|      | 5.26         | _7200_DO_DMA_Stop              | 55  |

|      | 5.27         |                                | 56  |

|      | 5.28         |                                |     |

| Cha  | pter         | 6 Double Buffer Mode Principle | 59  |

|      | _            | 7 Limitations                  |     |

|      | rrant        |                                | 63  |

| ww a | HANI         | I V                            | D-5 |

# **How to Use This Guide**

This manual is designed to help users use the PCI-7200, cPCI-7200, and LPCI-7200S. The functionality of PCI-7200, cPCI-7200, and LPCI-7200S are the same except that the cPCI-7200 has 4 auxiliary digital inputs and outputs. In this guide, "PCI-7200" represents PCI-7200, cPCI-7200, and LPCI-7200S if not specified.

The manual describes how to modify various settings on the PCI-7200 card to meet application requirements. It is divided into seven chapters:

### Chapter 1 Introduction

Gives an overview of product features, applications, and specifications.

### Chapter 2 Installation

Describes how to install the PCI-7200. The layout of PCI-7200 is shown, and the installation procedures, pin assignment of connectors, and timer pacer generation are specified.

#### Chapter 3 Register Structure & Format

Describes the low-level register structure and format of the PCI-7200.

#### Chapter 4 Operation Theory

Describes how the PCI-7200 works.

#### Chapter 5 C/C++ & DLL Libraries

Describes the high level C and DLL libraries to assist with programming in DOS and Windows environments.

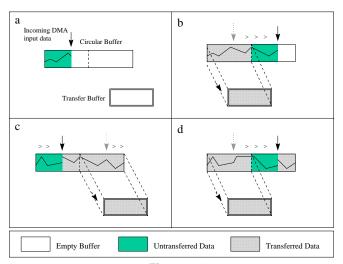

#### Chapter 6 **Double Buffer Mode Principle**

Describes the data buffer for double-buffered DMA DI operations.

#### Chapter 7 Limitations

Describes three limitations on using PCI-7200.

# Introduction

The PCI-7200, cPCI-7200, and LPCI-7200S are PCI/CompactPCI/Low profile PCI form factor high-speed digital I/O cards, consisting of 32 digital input channels, and 32 digital output channels. High performance design and state-of-the-art technology make this card suitable for high-speed digital input and output applications.

The PCI-7200 performs high-speed data transfers using bus-mastering DMA via the 32-bit PCI bus architecture. The maximum data transfer rates can be up to 12MB per second—very suitable for interfacing high-speed peripherals and your computer system.

Several different digital I/O operation modes are supported:

- **1. Direct Program Control:** the digital inputs and outputs can be accessed and controlled by its corresponding I/O ports directly.

- Timer Pacer Mode: the digital input and output operations are handled by internal timer pacer clock and transferred by bus mastering DMA.

- 3. External Clock Mode: the digital input operations are handled by an external input strobe signal (I REQ) and transferred by bus mastering DMA.

- **4. Handshaking:** through the REQ and ACK signals, digital I/O data can utilize simple handshaking data transfer.

# 1.1 Applications

- Interface to high-speed peripherals

- High-speed data transfers from other computers

- ◆ Digital I/O control

- ◆ Interface to external high-speed A/D and D/A converter

- Digital pattern generator

- Waveform and pulse generation

- BCD interface driver.

### 1.2 Features

The PCI-7200 high-speed DIO Card provides the following advanced features:

- ♦ 32 TTL digital input channels

- ♦ 32 TTL digital output channels

- ◆ Transfer up to 12M Bytes per second

- High output driving and low input loading

- ◆ 32-bit PCI bus, Plug and Play

- On-board internal timer pacer clock

- Internal timer controls input sampling rate

- Internal timer controls digital output rate

- ACK and REQ for handshaking

- On-board 32-byte FIFO for both digital input and output

- ◆ Extra 2k double word digital input FIFO for cPCI-7200

- ◆ 4 auxiliary digital input and output channels (cPCI-7200 only)

- Diode terminators for 32 input channels and control signals(cPCI-7200/LPCI-7200S)

- Multiple interrupt sources are selectable by software

# 1.3 Specifications

- ♦ Digital I/O (DIO)

- Number of DI Channels: 32 TTL compatible

- Number of DO Channels: 32 TTL compatible

- Data Transfer Mode

- ♦ Program I/O

- ♦ Internal timer pacer transfer

- ♦ External I REG strobe input

- ♦ Handshake data transfer

- Maximum Transfer Speed:

- ♦ 3MHz (12MHz) by external clock, handshake or external strobe

- ♦ 2MHz (8MHz) by internal timer pacer transfer

- FIFO:

- 8 words (32-bit) (for PCI-7200/LPCI-7200S)

- 2k + 8 words (32-bit) (for cPCI-7200 Digital input channels)

#### 2 • Introduction

### Input Voltage:

Low: Min. 0V; Max. 0.8V High: Min. +2.0V

#### Input Load:

Low: +0.5V @ -0.6mA max. High: +2.7V @ +20uA max.

#### Output Voltage:

Low: Min. 0V; Max. 0.5V High: Min. +2.7V

### • Driving Capacity:

Low: Max. +0.5V at 24mA (Sink) High: Min. 2.4V at -3.0mA (Source)

### **♦** Programmable Counter

• **Device:** 82C54-10, with a 4MHz time base

Timer 0: DI clock source

Timer 1: DO clock source

• Timer2: Base clock of Timer #0 and Timer #1

Pacer Output: 0.00046Hz to 2MHz

#### General Specifications

Operating Temperature: 0°C to 60°C

Storage Temperature: -20°C to 80°C

Humidity: 5 to 95%, non-condensing

#### Connector:

PCI-7200: one 37-pin D-type and one 40-pin ribbon connector

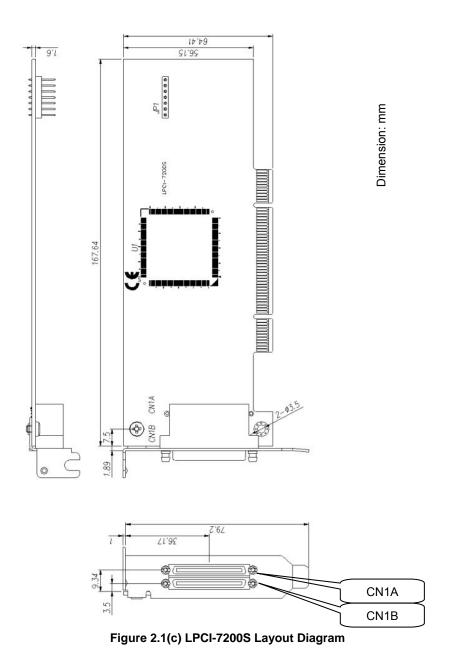

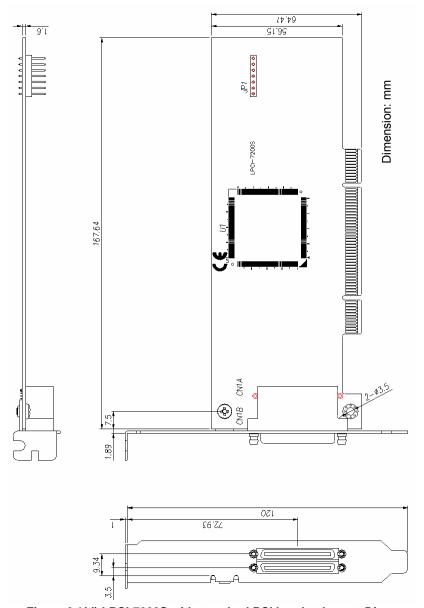

cPCI-7200: one 100-pin SCSI-type connector LPCI-7200S: two 68-pin SCSI-type connectors

#### Dimension:

PCI-7200: Compact size, only 148mm (L) X 102mm (H) cPCI-7200: Standard 3U CompactPCI form factor

LPCI-7200S: Low Profile PCI, 167.64mm (L) X 64.41mm (H)

### Power Consumption:

PCI-7200: +5V @ 720 mA typical cPCI-7200: +5V @ 820 mA typical LPCI-7200S: +5V @ 500 mA typical

### PCI signaling environment:

PCI-7200: 5V board supports a 5V PCI BUS

cPCI-7200: 3U Eurocard form factor, CompactPCI compliant

(PICMG 2.0 R2.1)

LPCI-7200S: Universal board, supports a 3.3V or 5V PCI BUS

# 1.4 Software Supporting

ADLINK provides versatile software drivers and packages for users' different approach to building a system. We not only provide programming library for many Windows systems, but also provide drivers for many software packages including LabVIEW<sup>®</sup>, HP VEE<sup>TM</sup>, DASYLab<sup>TM</sup>, InTouch<sup>TM</sup>, InControl<sup>TM</sup>, ISaGRAF<sup>TM</sup>, etc.

All software options are included in the ADLINK CD. Commercial software drivers require licenses. Without the software license, users can still install them and run the demo version for two hours for demonstration purpose. Please contact an ADLINK dealer to purchase licenses.

## 1.4.1 Programming Library

For customers writing customized programs, we provide function libraries for many different operating systems, including:

- DOS Library: Borland C/C++ and Microsoft C++ (function descriptions are included in this user's guide).

- Windows 95 DLL: For VB, VC++, Delphi, BC5 (functions descriptions are included in this user's guide).

- ◆ PCIS-DASK: Includes device drivers and DLLs for **Windows 98**, **Windows NT**, and **Windows 2000**. The DLL is compatible across Windows 98, Windows NT, and Windows 2000. All applications developed with PCIS-DASK are compatible across Windows 98, Windows NT, and Windows 2000. The developing environment can be VB, VC++, Delphi, BC5, or any Windows programming language that allows calls to a DLL. The PCIS-DASK user's guide and function reference manual are on the CD. Please refer the PDF manual files under the following directory: \Manual\_PDF\Software\PCIS-DASK

- ◆ PCIS-DASK/X: Includes device drivers and a shared library for Linux. The developing environment can be Gnu C/C++ or any programming language that allows linking to a shared library. The PCIS-DASK/X user's guide and function reference manual are on the CD (\Manual\_PDF\Software\PCIS-DASK-X).

The above software drivers are shipped with the board. Please refer to the "Software Installation Guide" to install these drivers.

## 1.4.2 PCIS-LVIEW: LabVIEW® Driver

PCIS-LVIEW contains VIs to interface with NI's LabVIEW<sup>®</sup> software package. PCIS-LVIEW supports Windows 95/98/NT/2000. The LabVIEW<sup>®</sup> drivers are shipped free with the board. Users can install and use them without a license. For detailed information about PCIS-LVIEW, please refer to the user's guide on the CD.

(\Manual\_PDF\Software\PCIS-LVIEW)

#### 1.4.3 PCIS-VEE: HP-VEE Driver

PCIS-VEE includes the user objects, which are used to interface with the HP VEE software package. PCIS-VEE supports Windows 95/98/NT. The HP-VEE drivers are shipped free with the board. Users can install and use them without a license. For detailed information about PCIS-VEE, please refer to the user's guide on the CD.

(\Manual\_PDF\Software\PCIS-VEE)

## 1.4.4 DAQBench™: ActiveX Controls

Customers who are familiar with ActiveX controls and VB/VC++ programming can use the DAQBench ActiveX Control components library for developing applications. DAQBench is designed under Windows NT/98. For more detailed information about DAQBench, please refer to the user's guide on the CD

(\Manual\_PDF\Software\DAQBench\DAQBench Manual.PDF)

# 1.4.5 DASYLab<sup>™</sup> PRO

DASYLab is an easy-to-use software package that provides easy-setup instrument functions such as FFT analysis. Please contact ADLINK to get DASYLab PRO, which include DASYLab and ADLINK hardware drivers.

# 1.4.6 PCIS-DDE: DDE Server and InTouch™

DDE stands for Dynamic Data Exchange specifications. The PCIS-DDE includes the PCI cards' DDE server. The PCIS-DDE server is included on the ADLINK CD. It requires a license. The DDE server can be used conjunction with any DDE client under Windows NT.

## 1.4.7 PCIS-ISG: ISaGRAF<sup>™</sup> driver

The ISaGRAF WorkBench is an IEC1131-3 SoftPLC control program development environment. The PCIS-ISG includes ADLINK products' target drivers for ISaGRAF under the Windows NT environment. The PCIS-ISG is included on the ADLINK CD. It requires a license.

# 1.4.8 PCIS-ICL: InControl<sup>™</sup> Driver

PCIS-ICL is the InControl driver, which support the Windows NT. The PCIS-ICL is included on the ADLINK CD. It requires a license.

#### 1.4.9 PCIS-OPC: OPC Server

PCIS-OPC is an OPC Server that can link with OPC clients. Many software packages on the market provide OPC clients. PCIS-OPC supports Windows NT. It requires a license.

# Installation

This chapter describes how to install the PCI-7200. Package contents and unpacking information are described. Because the PCI-7200 is a Plug and Play device, there are no more jumper or DIP switch settings for configuration. The interrupt number and I/O port address are assigned by the system BIOS during system boot up.

### 2.1 What Included

In addition to this *User's Manual*, the package includes the following items:

- ◆ PCI-7200 Digital I/O & Counter Card

- ◆ ACL-10437: 40-pin to 37-pin D-Sub cable

or

- ◆ cPCI-7200 Digital I/O & Counter Module for 3U CompactPCI

- ◆ 100-pin SCSI connector assembly

or

- ◆ LPCI-7200S Low profile Digital I/O & Counter Card

- ◆ Two 68-pin SCSI connectors assembly

- ADLINK CD

- Software Installation Guide

If any of these items is missing or damaged, contact the ADLINK dealer. Save the shipping materials and carton to ship or store the product in the future.

# 2.2 Unpacking

The PCI-7200 card contains sensitive electronic components that can be easily damaged by static electricity.

The work area should have a grounded anti-static mat. The operator should be wearing an anti-static wristband, grounded at the same point as the anti-static mat.

Inspect the card module carton for obvious damage. Shipping and handling may cause damage to the module. Be sure there is no shipping and handling damage on the module before proceeding.

After opening the card module carton, extract the system module and place it only on a grounded anti-static surface component side up.

Again inspect the module for damage. Press down on all the socketed IC's to make sure that they are properly seated. Do this only with the module place on a firm flat surface.

Note: DO NOT APPLY POWER TO THE CARD IF IT HAS BEEN DAMAGED.

You are now ready to install your PCI-7200.

# 2.3 Device Installation for Windows Systems

Once Windows 95/98/2000 has started, the Plug and Play function of Windows system will find the new NuDAQ/NuIPC cards. If this is the first time to installing NuDAQ/NuIPC cards in this system, Windows will require device information source. Please refer to the "Software Installation Guide" for the steps of installing the device.

# 2.4 PCI-7200/cPCI-7200/LPCI-7200S's Layout

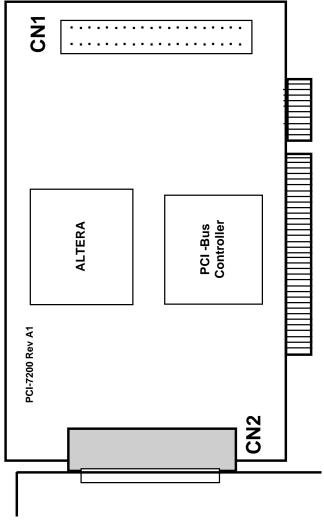

Figure 2.1(a) PCI-7200 Layout Diagram

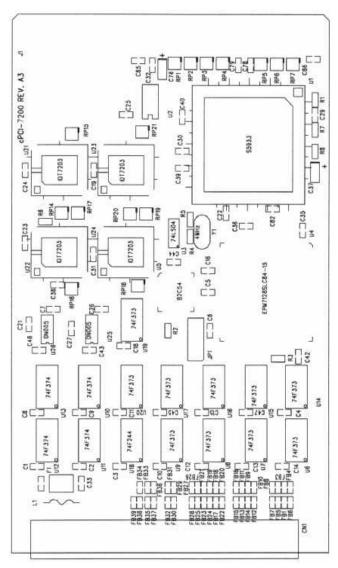

Figure 2.1(b) cPCI-7200 Layout Diagram

Figure 2.1(d) LPCI-7200S with standard PCI bracket Layout Diagram

### 2.5 Hardware Installation Outline

#### Hardware configuration

These PCI cards (or CompactPCI, Low Profile PCI cards) are equipped with a Plug and Play PCI controller that requests base addresses and interrupts according to PCI standard. The system BIOS will install the system resource based on the PCI cards' configuration registers and system parameters (which are set by system BIOS). Interrupt assignment and memory usage (I/O port locations) of the PCI cards can be assigned by system BIOS only. These system resource assignments are done on a board-by-board basis. It is not suggested to assign the system resource by any other methods.

#### PCI slot selection

The PCI and Low-Profile PCI cards can be inserted to any PCI slot without any configuration for system resource. CompactPCI peripheral slots are marked with a circle on the backplane. Please note that the PCI, CompactPCI, and Low-Profile PCI system board must provide bus-mastering capability to operate this board well.

#### Installation Procedures

- 1. Turn off the computer

- Turn off all accessories (printer, modem, monitor, etc.) connected to the computer

- 3. Remove the cover from your computer

- Select a 32-bit PCI slot. PCI slot are short than ISA or EISA slots, and are usually white or ivory

- 5. Before handling the PCI cards, discharge any static buildup on your body by touching the metal case of the computer. Hold the edge of the card and do not touch the components

- 6. Position the board into the PCI selected slot.

- 7. Secure the card in place at the rear panel of the system

### Running 7200UTIL.EXE

The IRQ number and I/O port address can be configured by the system. Use the  $7200\mathtt{UTIL}.\mathtt{EXE}$  utility to displayed the above values. A testing program is included in this utility to check if the PCI-7200 can work properly. Refer to Section 5.2 for further information.

# 2.6 Connector Pin Assignments

### 2.6.1 PCI-7200 Pin Assignments

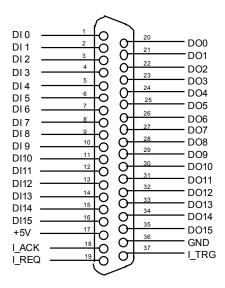

The PCI-7200 comes equipped with one 37-pin D-Sub connector (CN2) located on the rear mounting plate and one 40-pin female flat cable header connector (CN1). The CN2 is located on the rear mounting plate; the CN1 is on front of the board. Refer section 2.4 PCI-7200's layout.

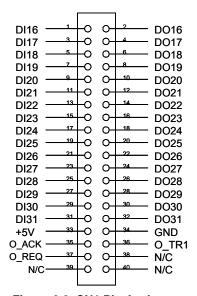

CN2 is used for digital inputs (DI 0 to DI 15) and digital outputs (DO 0 to DO 15) The reminding digital I/O channels DI 16 to DI 31 and DO 16 to DO 31 are on CN1. The pin assignment of CN1 and CN2 is illustrated in the Figures 2.2 and 2.3.

#### Legend:

DO n : Digital Output CH n DI n : Digital Input CH n

GND: Ground

ACK: ACK handshaking signal REQ: REQ handshaking signal

I\_TRG: Input signal to start DI data samplingO TRG: Output signal can be controlled by software

Figure 2.2 CN1 Pin Assignments

Figure 2.3 CN2 Pin Assignments

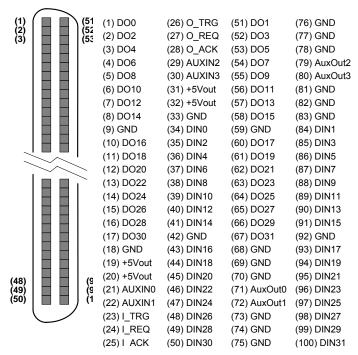

### 2.6.2 cPCI-7200 Pin Assignments

Figure 2.4 CN Pin Assignments

# 2.6.3 LPCI-7200S Pin Assignments

| DIN0  | A1  | A35   | GND      |

|-------|-----|-------|----------|

| DIN1  | A2  | A36   | GND      |

| DIN2  | А3  | A37   | GND      |

| DIN3  | A4  | A38   | GND      |

| DIN4  | A5  | A39   | GND      |

| DIN5  | A6  | A40   | GND      |

| DIN6  | A7  | A41   | GND      |

| DIN7  | A8  | A42   | GND      |

| DIN8  | A9  | A43   | GND      |

| DIN9  | A10 | A44   | GND      |

| DIN10 | A11 | A45   | GND      |

| DIN11 | A12 | A46   | GND      |

| DIN12 | A13 | A47   | GND      |

| DIN13 | A14 | A48   | GND      |

| DIN14 | A15 | A49   | GND      |

| DIN15 | A16 | A50   | GND      |

| DIN16 | A17 | A51   | GND      |

| DIN17 | A18 | A52   | GND      |

| DIN18 | A19 | A53   | GND      |

| DIN19 | A20 | A54   | GND      |

| DIN20 | A21 | A55   | GND      |

| DIN21 | A22 | A56   | GND      |

| DIN22 | A23 | A57   | GND      |

| DIN23 | A24 | A58   | GND      |

| DIN24 | A25 | A59   | GND      |

| DIN25 | A26 | A60   | GND      |

| DIN26 | A27 | A61   | GND      |

| DIN27 | A28 | A62   | GND      |

| DIN28 | A29 | A63   | GND      |

| DIN29 | A30 | A64   | GND      |

| DIN30 | A31 | A65   | GND      |

| DIN31 | A32 | A66   | GND      |

| _REQ  | A33 | A67   | I_ACK    |

| _TRG  |     | A68   | 5Vout    |

| ro 25 | CN1 | Δ Pin | Accianma |

Figure 2.5 CN1A Pin Assignments

| DOUT0  | B1  | B35 | GND   |

|--------|-----|-----|-------|

| DOUT1  | B2  | B36 | GND   |

| DOUT2  | В3  | B37 | GND   |

| DOUT3  | B4  | B38 | GND   |

| DOUT4  | B5  | B39 | GND   |

| DOUT5  | B6  | B40 | GND   |

| DOUT6  | B7  | B41 | GND   |

| DOUT7  | B8  | B42 | GND   |

| DOUT8  | B9  | B43 | GND   |

| DOUT9  | B10 | B44 | GND   |

| DOUT10 | B11 | B45 | GND   |

| DOUT11 | B12 | B46 | GND   |

| DOUT12 | B13 | B47 | GND   |

| DOUT13 | B14 | B48 | GND   |

| DOUT14 | B15 | B49 | GND   |

| DOUT15 | B16 | B50 | GND   |

| DOUT16 | B17 | B51 | GND   |

| DOUT17 | B18 | B52 | GND   |

| DOUT18 | B19 | B53 | GND   |

| DOUT19 | B20 | B54 | GND   |

| DOUT20 | B21 | B55 | GND   |

| DOUT21 | B22 | B56 | GND   |

| DOUT22 | B23 | B57 | GND   |

| DOUT23 | B24 | B58 | GND   |

| DOUT24 | B25 | B59 | GND   |

| DOUT25 | B26 | B60 | GND   |

| DOUT26 | B27 | B61 | GND   |

| DOUT27 | B28 | B62 | GND   |

| DOUT28 | B29 | B63 | GND   |

| DOUT29 | B30 | B64 | GND   |

| DOUT30 | B31 | B65 | GND   |

| DOUT31 | B32 | B66 | GND   |

| O_REQ  | B33 | B67 | O_ACK |

| O_TRG  | B34 | B68 | 5Vout |

Figure 2.6 CN1B Pin Assignments

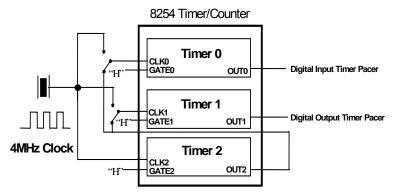

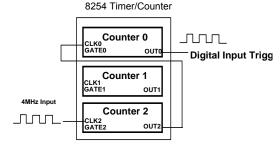

#### 2.7 8254 for Timer Pacer Generation

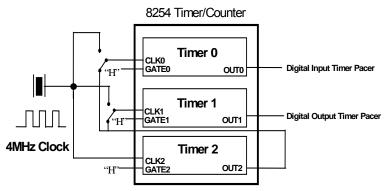

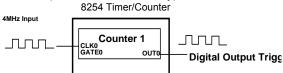

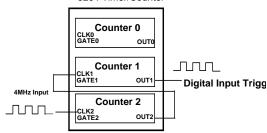

Figure 2.7 8254 configuration

The internal timer/counter 8254 on the PCI-7200 is configured as the above diagram (Figure 2.7). Users can use it to generate the timer pacer for both digital input and digital output triggers.

The digital input timer pacer is from OUT0 (Timer 0), and the digital output timer pacer is from OUT1 (Timer 1). Besides, Timer 0 and Timer 2 can be cascaded together to generate more timer pacer frequencies for digital input. Also, Timer 2 can be cascaded with Timer 1 for digital output.

pacer rate = 4MHz / (C0 \* C2)

if Timer 0 & Timer 2 are cascaded

pacer rate = 4MHz / C0

if timer 0 & Timer 2 are not cascaded

The maximum pacer signal rate of input and output are 4MHz/2 = 2Mhz. The minimum signal rate is 4MHz/65535/65535.

For example, to get a pacer rate of 2.5kHz, set C0 = 40 and C2 = 40. That is 2.5KHz = 4Mhz /  $(40 \times 40)$

# 2.8 LPCI-7200S PCI Bus Signaling

Low-Profile PCI is a new PCI card standard for space-constrained system designs. The new form factor maintain the same electrical protocols, PCI signals, and software drivers as standard PCI v2.2 expansion cards. However, Low-Profile PCI bus interface only supports 3.3V signaling. To support both 5V and 3.3V signaling, LPCI-7200S implements 5V I/O tolerant bus switches to achieve the I/O voltage transition. This allows LPCI-7200S to be used in both 5V and 3.3V systems.

# 2.9 Onboard Pull-ups and Terminations in digital input

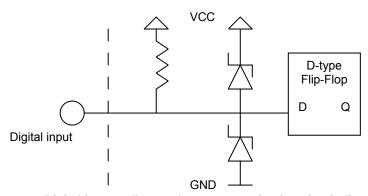

The PCI-7200, cPCI-7200 and LPCI-7200S have 32 digital input channels. On-board pull-ups and terminations for digital input circuits may be needed for some applications. The pull-ups guarantee a fixed input state when external connections are floating. Schottky terminations can minimize undershoot/overshoot disturbances caused by reflection noise on high-speed bus lines. Table 2.1 lists the pull-ups and termination status of PCI-7200, cPCI-7200 and LPCI-7200S. Figure 2.8 is the illustration of the pull-up resistor and terminations on-board.

|            | Pull-up resistor | Terminations                             |

|------------|------------------|------------------------------------------|

| PCI-7200   | None             | None                                     |

| cPCI-7200  | None             | Schottky diode clamped to ground & power |

| LPCI-7200S | 10kΩ             | Schottky diode clamped to ground & power |

Table 2.1 pull-ups and termination of PCI/cPCI-7200 and LPCI-7200S.

Figure 2.8 Digital input pull-up resistor and termination circuit diagram.

# **Register Format**

# 3.1 I/O Registers Format

The PCI-7200 occupies 8 consecutive 32-bit I/O addresses in the PC I/O address space. The cPCI-7200 occupies 9 consecutive 32-bit I/O addresses. Table 4.1 shows the I/O Map

| Address                          | Read                          | Write                |

|----------------------------------|-------------------------------|----------------------|

| Base + 0                         | Counter 0                     | Counter 0            |

| Base + 4                         | Counter 1                     | Counter 1            |

| Base + 8                         | Counter 2                     | Counter 2            |

| Base + C                         |                               | CLK Control CW0      |

| Base + 10                        | Digital Input Reg.            |                      |

| Base + 14                        | Digital Output<br>(Read-back) | Digital Output Reg.  |

| Base + 18                        | DIO Status & Control          | DIO Status &Control  |

| Base + 1C                        | INT Status & Control          | INT Status & Control |

| Base + 20<br>(cPCI-7200<br>only) | AUXDIO Reg.                   | AUXDO Reg.           |

Note: (1) I/O port is 32-bits wide

(2) 8-bit or 16-bit I/O access is not allowed

# 3.2 Digital Input Register (BASE + 10)

32 digital input channels can be read from this register

Address: BASE + 10 Attribute: READ Only

**Data Format:**

| Byte     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|------|------|------|------|------|------|------|------|

| Base +10 | DI7  | DI6  | DI5  | DI4  | DI3  | DI2  | DI1  | DI0  |

| Base +11 | DI15 | DI14 | DI13 | DI12 | DI11 | DI10 | DI9  | DI8  |

| Base +12 | DI23 | DI22 | DI21 | DI20 | DI19 | DI18 | DI17 | DI16 |

| Base +13 | DI31 | DI30 | DI29 | DI28 | DI27 | DI26 | DI25 | DI24 |

# 3.3 Digital Output Register (BASE + 14)

32 digital output channels can be written and read to/from this register

Address: BASE + 14 Attribute: READ/WRITE

Data Format:

| Byte     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------|------|------|------|------|------|------|------|------|

| Base +14 | DO7  | DO6  | DO5  | DO4  | DO3  | DO2  | DO1  | DO0  |

| Base +15 | DO15 | DO14 | DO13 | DO12 | DO11 | DO10 | DO9  | DO8  |

| Base +16 | DO23 | DO22 | DO21 | DO20 | DO19 | DO18 | DO17 | DO16 |

| Base +17 | DO31 | DO30 | DO29 | DO28 | DO27 | DO26 | DO25 | DO24 |

The digital output status can be read back through the same location (BASE + 14)

# 3.4 DIO Status & Control Register (BASE + 18)

The data transfer mode of digital input is controlled and status is checked through this register.

Address: BASE + 18 Attribute: READ/WRITE

Data Format:

| Byte     | 7     | 6      | 5     | 4     | 3      | 2       | 1       | 0     |

|----------|-------|--------|-------|-------|--------|---------|---------|-------|

| Base +18 | O_ACK | DIN_EN | I_TRG | TRGPL | I_FIFO | I_TIME0 | I_REQ   | I_ACK |

| Base +19 |       | I_OVER |       |       | O_TRG  | O_FIFO  | O_TIME1 | O_REQ |

| Base +20 |       |        |       |       |        |         |         | O_UND |

| Base +21 |       |        |       |       |        |         |         |       |

### 22 • Register Format

### **♦** Digital Input Mode Setting:

- I\_ACK: Input ACK Enable

- 1: Input ACK is enabled (input ACK will be asserted after input data is read by CPU or written to input FIFO)

- 0: Input ACK is disabled

- **I\_REQ**: Input REQ Strobe Enabled

- 1: Use I\_REQ edge to latch input data

- 0: I\_REQ is disabled

- I\_TIME0: Input Timer 0 Enable

- 1: Input is sampled by falling edge of Counter 0 output (COUT0)

- 0: Input Timer 0 is disabled

- I\_FIFO: Input FIFO Enable Mode

- 1: Input FIFO is enabled (input data is saved to input FIFO)

- 0: Input FIFO is disabled

- **TRGPOL**: Input Trigger Polarity

- 1: I TRG is Rising Edge Active

- 0: I TRG is Falling Edge Active

- I\_TRG: External Trigger Enable

- 1: Wait until I\_TRG signal is active, digital input sampling will begin after a rising or falling edge of I\_TRG

- 0: Start input sampling immediately (if input control register is set)

- **DIN\_EN**: Digital Input Enable

- 1: Digital Input Enable

- 0: Digital Input Disabled, when this bit is set as 0, all digital input operation will be stopped

#### **♦** Digital Output Mode Setting:

- O ACK: Output ACK Enable

- 1: Output ACK is enabled; the output circuit will wait for O ACK after

- O REQ strobe is asserted

- 0: Output ACK is disabled

- O\_REQ: Output REQ Enable

- 1: Output REQ is enabled; an O\_REQ strobe will be generated after output data is ready

- 0: Output REQ is disabled

- O TIME1: Output Timer 1 Enable

- 1: Output Timer 1 is enabled; output data is moved from output FIFO to DO registers when output of Counter1 goes low

- 0: Output Counter 1 is disabled

- O\_FIFO: Output FIFO Enable

- 1: Output FIFO is enabled (output data is moved from output FIFO)

- 0: Output FIFO is disabled

### O\_TRG: Digital Output Trigger Signal

This bit is used to control the O\_TRG output of PCI-7200; the signal is on CN1 pin 36 of PCI-7200, CN1 pin 26 of cPCI-7200, CN2 pin 34 of

LPCI 7200S when

1: O\_TRG 1 goes High (1) 0: O TRG 1 goes Low (0)

### ◆ Digital I/O FIFO Status:

**I\_OVR**: Input data overrun

1: Digital Input FIFO is full (overrun) during input data transfer

0: No input data overrun occurred

Input data overrun occurred, the I\_OVR bit is set when input FIFO is full and there is new input data coming in. This bit can be cleared by writing "1" to it.

O\_UND: Output data FIFO is underrun

1: Output FIFO is empty during output data transfer

0: No output data underrun occurred

Output data underrun, the O\_UND bit is set when output FIFO is empty and the output request for new data, this bit can be cleared by writing "1" to it.

# 3.5 Interrupt Status & Control Register (BASE + 1C)

The interrupt mode/status is set/checked through this register.

Address: BASE + 1C Attribute: READ/WRITE

**Data Format:**

| Byte     | 7      | 6      | 5       | 4       | 3     | 2     | 1      | 0      |

|----------|--------|--------|---------|---------|-------|-------|--------|--------|

| Base +1C | SI_TO  | SI_REQ | SO_ACK  | T2_EN   | T1_EN | T0_EN | II_REQ | IO_ACK |

| Base +1D | FIFOFF | FIFOEF | FIFORST | REQ_NEG | T1_T2 | T0_T2 | SI_T2  | SI_T1  |

| Base +1E |        |        |         |         |       |       |        |        |

| Base +1F |        |        |         |         |       |       |        |        |

### **♦** Interrupt Control:

With the PCI-7200, interrupts can be triggered by many signal sources such as O\_ACK, I\_REQ, timer 0, timer 1, and timer 2. The following bits control the interrupt source:

**IO\_ACK:** Interrupt is triggered by O\_ACK signal.

1: O\_ACK interrupt is enabled

0: O\_ACK interrupt is disabled

**II\_REQ:** Interrupt is triggered by I\_REQ signal.

1: I\_REQ interrupt is enabled

0: I REQ interrupt is disabled

### 24 • Register Format

- **T0\_EN:** Interrupt is triggered by timer 0 output.

- 1: Timer 0 interrupt is enabled

- 0: Timer 0 interrupt is disabled

- **T1\_EN:** Interrupt is triggered by timer 1 output.

- 1: Timer 1 interrupt is enabled

- 0: Timer 1 interrupt is disabled

- **T2\_EN:** Interrupt is triggered by timer 2 output.

- 1: Timer 2 interrupt is enabled

- 0: Timer 2 interrupt is disabled

### Interrupt Status:

The following bits are used to check interrupt status:

- **SO\_ACK:** Status of O\_ACK interrupt

- 1: O ACK Interrupt occurred

- 0: No O ACK interrupt

- SI REQ: Status of I REQ interrupt

- 1: I REQ Interrupt occurred

- 0: No I REQ Interrupt

- **SI\_T0:** Status of timer 0 interrupt

- 1: OUT0 (output of timer 0) Interrupt occurred

- 0: No timer 0 Interrupt

- **SI\_T1:** Status of timer 1 interrupt

- 1: OUT1 (output of timer 1) Interrupt occurred

- 0: No timer 1 Interrupt

- **SI\_T2:** Status of timer 2 interrupt

- 1: OUT2 (output of timer 2) interrupt occurred

- 0: No timer 2 Interrupt

**Note:** Writing "1" to the corresponding bit of the register can clear all interrupt statuses. In order to make the interrupt work properly, the interrupt service routine has to clear all the interrupt status before end of the ISR.

### ◆ Timer Configuration Control:

The 8254 timer on the PCI-7200 can be configured as either timer 0 cascaded with timer 2 or timer 1 cascaded with timer 2. These configurations are controlled by the following bits:

- **T0 T2:** Timer 0 is cascaded with timer 2

- 1: Timer 0 and timer 2 are cascaded together; output of timer 2 connects to the clock input of timer 0.

- 0: Not cascaded, the 4MHz clock is connected to the timer 0 clock input.

#### T1\_T2: Timer 1 is cascaded with timer 2

- 1: Timer 1 and timer 2 are cascaded together; output of timer 2 connects to the clock input of timer 1.

- 0: Not cascaded, the 4MHz clock is connected to the timer 1 clock input.

### ♦ I\_REQ Polarity Selection:

When the input sampling is controlled by the I\_REQ signal only, the I\_REQ can be programmed to be rising edge active or falling edge active.

**REQ\_NEG:** I\_REQ trigger polarity

- 1: latch input data on falling edge of I\_REQ 0: latch input data on rising edge of I\_REQ

- ♦ FIFO Control and Status (cPCI-7200 only):

The cPCI-7200 has an extra 2k samples digital input FIFO. The FIFO can be cleared and monitored by the following bits:

FIFORST (Write only): Clear the on-board DI FIFO

1: Write 1 to clear the data of the FIFO.

0: No operation.

FIFOEF (Read only): Empty flag of the DI FIFO

1: DI FIFO is empty.

0: DI FIFO is not empty.

FIFOFF (Read only): Full flag of the DI FIFO

1: DI FIFO is full.

0: DI FIFO is not full.

**Note:** The cPCI-7200 has 2 cascaded DI FIFOs. One is located in the PCI controller chip, the other one is on the PCI-7200 board. The above bits only control the on-board FIFO. In order to control the on-chip FIFO, please refer to the AMCC-5933 data book.

# 3.6 8254 Timer Registers (BASE + 0)

The 8254 timer/counter IC occupies 4 I/O address. Users can refer to Tundra's or Intel's data sheet for a full description of the 8254 features. Download the 8254 data sheet from the following web site:

http://support.intel.com/support/controllers/peripheral/231164.htm or

http://www.tundra.com (for Tundra's 82C54 datasheet).

| Address  | Read      | Write           |

|----------|-----------|-----------------|

| Base + 0 | Counter 0 | Counter 0       |

| Base + 4 | Counter 1 | Counter 1       |

| Base + 8 | Counter 2 | Counter 2       |

| Base + C |           | CLK Control CW0 |

# **Operation Theory**

In PCI-7200, there are four data transfer modes can be used for digital I/O access and control, these modes are:

- Direct Program Control: the digital inputs and outputs can be read/written and controlled by its corresponding I/O port address directly.

- Internal Timer Pacer Mode: the digital input and output operations are paced by an internal timer pacer and are transferred by bus mastering DMA.

- 3. **External Clock Mode**: the digital input operation is clocked by external I REQ strobe and transferred by bus mastering DMA.

- 4. *Handshaking*: through REQ and ACK signals, the digital I/O can have simple handshaking data transfers.

# 4.1 Direct Program Control

Digital I/O operations can be controlled by I/O port **BASE+10** for digital input and **BASE+14** for digital output.

The I/O port address BASE is assigned by system BIOS, please refer to Section 5 for a more detailed description.

The digital OUT operation is:

```

outport (BASE+14, 0xAAAAAAAA) // (A: 0 to F)

```

The digital IN operation is:

```

value = inport (BASE+10) // The input status is save in the // value variable

```

# 4.2 Timer Pacer Mode

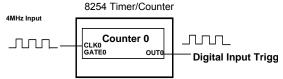

The digital I/O access control is clocked by timer pacer, which is generated by an interval programming timer/counter chip (8254). There are three timers on the 8254. Timer 0 is used to generate timer pacer for digital input and timer 1 is used for digital output. The configuration is illustrated as below.

The operation sequences are:

- 1. Define the frequency (timer pacer rate)

- The digital input data are saved in FIFO after a timer pacer pulse is generated. The sampling is controlled by timer pacer.

- 3. The data saved in FIFO will be transferred to main memory of the computer system directly and automatically. This is controlled by bus mastering DMA control, this function is supported by PCI controller chip.

The operation flow is show as following:

### 30 • Operation Theory

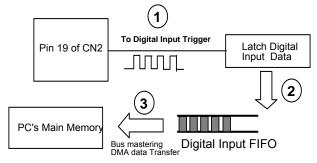

# 4.3 External Clock Mode

The digital input is clocked by external strobe, which is from Pin 19 (I\_REQ) of CN2 (PCI-7200), Pin 24 of CN1 (cPCI-7200), or PIN 33 of CN1A (LPCI-7200S). The operation sequence is very similar to the Timer Pacer Trigger. The only difference is the clock source.

- 1. The external input strobe is generated from outside device, and goes through the Pin 19 (I\_REQ) of CN2 to latch the digital input.

- 2. The digital input data is saved in FIFO after an I/O strobe signal is coming in.

- 3. The data saved in input FIFO will be transferred to main memory on your computer system directly. This is controlled by bus mastering DMA control, this function is supported by PCI.

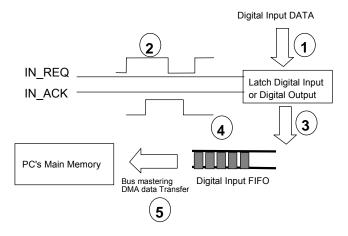

# 4.4 Handshaking

The PCI-7200 also supports a handshaking digital I/O transfer mode. That is, after input data is ready, an I\_REQ is sent from an external device, and I\_ACK will go high to acknowledge the data already accessed.

# I\_REQ & I\_ACK for Digital Input

- 1. Digital Input Data is ready.

- 2. An I\_REQ signal is generated for digital input operation.

- 3. Digital input data is saved to FIFO.

- 4. An I\_ACK signal is generated and sent to an outside device.

- 5. If the FIFO is not empty and PCI bus is not occupied, the data will be transferred to main memory.

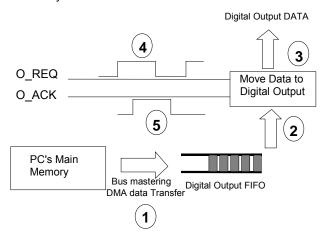

### O\_REQ & O\_ACK for Digital Output

- Digital Output Data is moved from PC memory to FIFO of PCI-7200 by using DMA data mastering data transfer.

- 2. Move output data from FIFO to digital output circuit.

- 3. Output data is ready.

- 4. An O REQ signal is generated and sent to outside device.

- 5. After an O ACK is captured, steps 2-5 will be repeated.

- \*\* If the FIFO is not full, the output data is moved form PC's main memory to FIFO automatically.

### 32 • Operation Theory

#### **Timing Characteristic** 4.5

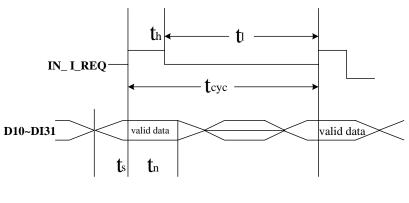

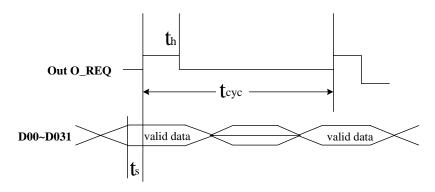

**1.** I REQ as input data strobe (Rising Edge Active)

t<sub>h</sub> ≥ 60ns t<sub>l</sub> ≥ 60ns  $t_{\text{CYC}} \ge 5$  PCI CLK Cycle

t<sub>s</sub> ≥ 2ns  $t_n \ge 30 ns$

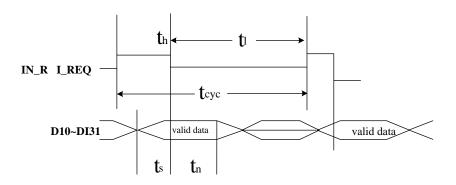

# 2. I\_REQ as input data strobe (Falling Edge Active)

$t_h \ge 60$ ns  $t_l \ge 60$ ns

t<sub>CYC</sub> ≥ 5 PCI CLK Cycle

t<sub>s</sub> ≥ 2ns

$t_n \ge 30 ns$

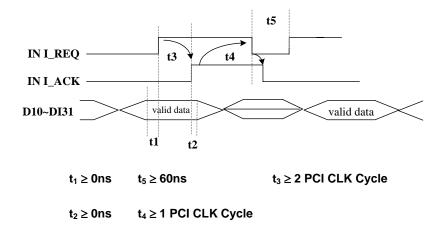

# 3. I\_REQ & I\_ACK Handshaking

Note: I\_REQ must be asserted until I\_ACK asserts, I\_ACK will be asserted until I\_REQ de-asserts.

# 4. O\_REQ as output data strobe

$t_s \geq 19 ns \qquad t_h \geq 2 \; PCI \; CLK \; Cycles \qquad T_{cyc} \geq 500 ns$

# 34 • Operation Theory

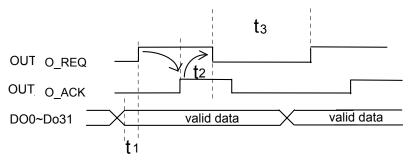

# 5. O\_REQ & O\_ACK Handshaking

$t_1 \gg 19$ ns  $t_2 \gg 1$  PCI CLK Cycle  $t_3 \gg 5$  PCI CLK Cycle

Note: O\_ACK must be de-asserted before O\_REQ asserts, O\_ACK can be asserted any time after O\_REQ asserts, O\_REQ will be reasserted after O\_ACK is asserted.

# C/C++ Libraries

This chapter describes the software library for operating the card. Only functions in DOS library and Windows 95 DLL are described. Please refer to the PCIS-DASK function reference manual, which included on the ADLINK CD, for the descriptions of the Windows 98/NT/2000 DLL functions.

The function prototypes and some useful constants are defined in the header files LIB directory (DOS) and INCLUDE directory (Windows 95). For the Windows 95 DLL, the developing environment can be Visual Basic 4.0 or above, Visual C/C++ 4.0 or above, Borland C++ 5.0 or above, Borland Delphi 2.x (32-bit) or above, or any Windows programming language that allows calls to a DLL. C/C++, VB, and Delphi files are included.

### 5.1 Libraries Installation

Please refer to the "Software Installation Guide" for the detailed information about how to install the software libraries for DOS, or Windows 95 DLL, or PCIS-DASK for Windows 98/NT/2000.

Device drivers and DLL functions of Windows 98/NT/2000 are included in the PCIS-DASK. Please refer to the PCIS-DASK user's guide and function reference, which included on the ADLINK CD, for detailed programming information.

# 5.2 Programming Guide

# 5.2.1 Naming Convention

The functions of the NuDAQ PCI cards or NuIPC CompactPCI cards' software drivers use full-names to represent the functions' real meaning. The naming convention rules are:

In DOS:

```

{hardware model} {action name}. e.g. _7200_Initial().

```

All functions in the PCI-7200 driver are named with 7200 as {hardware\_model}. But they can be used by PCI-7200, cPCI-7200 and LPCI-7200S.

In order to recognize the difference between DOS library and Windows 95 library, a capital "W" is put on the head of each function name of the Windows 95 DLL driver (e.g. w\_7200\_Initial()).

# 5.2.2 Data Types

Some data types are definded in Pci\_7200.h (DOS) and Acl\_pci.h (Windows 95). These data types are used by NuDAQ Cards' library. We suggest using these data types. The following table shows the data type names and their range.

| Type Name | Description                            | Range                                           |

|-----------|----------------------------------------|-------------------------------------------------|

| U8        | 8-bit ASCII character                  | 0 to 255                                        |

| I16       | 16-bit signed integer                  | -32768 to 32767                                 |

| U16       | 16-bit unsigned integer                | 0 to 65535                                      |

| 132       | 32-bit signed integer                  | -2147483648 to 2147483647                       |

| U32       | 32-bit single-precision floating point | 0 to 4294967295                                 |

| F32       | 32-bit single-precision floating point | -3.402823E38 to 3.402823E38                     |

| F64       | 64-bit double-precision floating point | -1.797683134862315E308 to 1.797683134862315E309 |

| Boolean   | Boolean logic value                    | TRUE, FALSE                                     |

# 5.3 \_7200\_Initial

### @ Description

A PCI-7200 card is initialized according to the card number.

Because the PCI-7200 is PCI bus architecture and meets the Plug and Play design, the *IRQ* and *base\_address* (pass-through address) are assigned by system BIOS directly. Every PCI-7200 card has to be initialized by this function before calling other functions.

**Note:** Because the configuration of PCI-7200 is handled by the system, there are no jumpers or DMA selection on the PCI boards that need to be set up by the users.

### @ Syntax

### Visual C++ (Windows 95)

```

int W_7200_Initial (U8 card_number, U16 *base_addresss, U8

*irq_no)

```

### Visual Basic (Windows 95)

```

W_7200_Initial (ByVal card_number As Byte, base_addresss As Integer, irq_no As Byte) As Long

```

### C/C++ (DOS)

```

int _7200_Initial (U8 card_number, U16 *base_addresss,

U8 *irq_no)

```

### @ Argument

**card\_number:** the card number to be initialized, only four cards can be initialized, the card number must be CARD\_1, CARD\_2, CARD\_3 or CARD 4.

**base\_address:** the I/O port base address of the card, it is assigned by the system BIOS.

**irq\_no:** the system will give an available interrupt number to this card automatically.

#### @ Return Code

```

ERR_NoError

ERR_InvalidBoardNumber

ERR_PCIBiosNotExist

ERR_PCICardNotExist

ERR_PCIIrqNotExist

ERR_BaseAddressError

```

# 5.4 \_7200\_Switch\_Card\_No

### @ Description

After initializing more than one PCI-7200 card, this function is used to select which card is currently used.

### @ Syntax

# Visual C++ (Windows 95)

int W\_7200\_Switch\_Card\_No (U8 card\_number)

### Visual Basic (Windows 95)

W\_7200\_Switch\_Card\_No (ByVal card\_number As Byte) As Long

### C/C++ (DOS)

int \_7200\_Switch\_Card\_No (U8 card\_number)

### @ Argument

**card\_number:** The card number to be initialized, four cards can be initialized, the card number must be CARD\_1, CARD\_2, CARD\_3, or CARD 4, but only one card is active.

#### @ Return Code

ERR\_NoError

ERR InvalidBoardNoInit

# 5.5 7200 AUX DI

# @ Description

Read data from auxiliary digital input port of cPCI-7200 card. You can get all 4 bits input data by using this function.

# @ Syntax

### Visual C++ (Windows 95)

int W\_7200\_AUX\_DI (U32 \*aux\_di)

## Visual Basic (Windows 95)

W\_7200\_DI (aux\_di As Long) As Long

# C/C++ (DOS)

int \_7200\_DI (U32 \*aux\_di)

# @ Argument

aux\_di: returns 4-bit value from auxiliary digital input port.

### @ Return Code

ERR\_NoError

ERR\_FunctionNotAvailable

#### 40 . C/C++ Libraries

# 5.6 \_7200\_AUX\_DI\_Channel

### @ Description

Read data from the auxiliary digital input channel of cPCI-7200 card. There are 4 digital input channels on the cPCI-7200 auxiliary digital input port. When performing this function, the auxiliary digital input port is read and the value of the corresponding channel is returned.

\* channel means each bit of digital input port.

### @ Syntax

### Visual C++( Windows 95)

int W\_7200\_AUX\_DI\_Channel (U8 di\_ch\_no, Boolean

\*aux data)

### Visual Basic (Windows 95)

W\_7200\_AUX\_DI\_Channel (ByVal di\_ch\_no As Byte, aux\_data As Byte) As Long

### C/C++ ( DOS)

int \_7200\_AUX\_DI\_Channel (U8 di\_ch\_no, Boolean

\*aux\_data)

### @ Argument

**di\_ch\_no:** the DI channel number, the value is between 0 and 3. **aux data:** return value, either 0 or 1.

#### @ Return Code

ERR NoError, ERR InvalidDIChannel, ERR FunctionNotAvailable

# 5.7 \_7200\_AUX\_DO

### @ Description

Write data to auxiliary digital output port. There are 4 auxiliary digital outputs on the cPCI-7200.

### @ Syntax

#### Visual C++ (Windows 95)

int W\_7200\_AUX\_DO (U32 aux\_do)

### Visual Basic (Windows 95)

W\_7200\_AUX\_DO (ByVal aux\_do As Long) As Long

### C/C++ (DOS)

int \_7200\_AUX\_DO (U32 aux\_do)

### @ Argument

aux\_do: value will be written to auxiliary digital output port.

#### @ Return Code

ERR\_NoError

ERR\_FunctionNotAvailable

# 5.8 \_7200\_AUX\_DO\_Channel

### @ Description

Write data to auxiliary digital output channel (bit). There are 4 auxiliary digital output channels on the cPCI-7200. When performing this function, the digital output data is written to the corresponding channel.

\* channel means each bit of digital input port

### @ Syntax

### Visual C++ (Windows 95)

int W\_7200\_AUX\_DO\_Channel (U8 do\_ch\_no, Boolean aux\_data)

### Visual Basic (Windows 95)

W\_7200\_AUX\_DO\_Channel (ByVal do\_ch\_no As Byte, ByVal aux\_data As Byte) As Long

### C/C++ (DOS)

int \_7200\_AUX\_DO\_Channel (U8 do\_ch\_no, Boolean aux\_data)

### @ Argument

do\_ch\_no: the auxiliary DO channel number, the value is between 0 and 3. aux\_data: either 0 (OFF) or 1 (ON).

### @ Return Code

ERR\_NoError

ERR\_InvalidDOChannel

ERR\_FunctionNotAvailable

# 5.9 \_7200\_DI

# @ Description

This function is used to read data from digital input port. There are 32-bit digital inputs on the PCI-7200. Use this function to get all 32 inputs data from \_7200\_DI.

### @ Syntax

# Visual C++ (Windows 95)

int W\_7200\_DI (U32 \*di\_data)

#### Visual Basic (Windows 95)

W\_7200\_DI (di\_data As Long) As Long

#### C/C++ (DOS)

int \_7200\_DI (U32 \*di\_data)

#### @ Argument

di\_data: returns all 32-bit value from digital port.

### @ Return Code

ERR NoError

### 42 • C/C++ Libraries

# 5.10 \_7200\_DI\_Channel

### @ Description

This function is used to read data from digital input channels (bit). There are 32 digital input channels on the PCI-7200. When performs this function, the digital input port is read and the value of the corresponding channel is returned.

\* channel means each bit of digital input port.

### @ Syntax

### Visual C++ (Windows 95)

int W\_7200\_DI\_Channel (U8 di\_ch\_no, Boolean \*di\_data)

# Visual Basic (Windows 95)

W\_7200\_DI\_Channel (ByVal di\_ch\_no As Byte, di\_data As Byte) As Long

### C/C++ (DOS)

int \_7200\_DI\_Channel (U8 di\_ch\_no, Boolean \*di\_data)

# @ Argument

di\_ch\_no: the DI channel number, the value has to be set within 0 and 31.

di\_data: return value, either 0 or 1.

### @ Return Code

ERR\_NoError

ERR\_InvalidDIChannel

# 5.11 7200 DO

### @ Description

This function is used to write data to the digital output port. There are 32 digital outputs on the PCI-7200.

# @ Syntax

### Visual C++ (Windows 95)

int W 7200 DO (U32 do data)

#### Visual Basic (Windows 95)

W 7200 DO (ByVal do data As Long) As Long

#### C/C++ (DOS)

int \_7200\_DO (U32 do\_data)

#### @ Argument

do\_data: value will be written to digital output port

#### @ Return Code

ERR\_NoError

# 5.12 \_7200\_DO\_Channel

### @ Description

This function is used to write data to digital output channels (bit). There are 32 digital output channels on the PCI-7200. When performing this function, the digital output data is written to the corresponding channel.

\* channel means each bit of digital input port

### @ Syntax

### Visual C++ (Windows 95)

int W\_7200\_DO\_Channel (U8 do\_ch\_no, Boolean do\_data)

### Visual Basic (Windows 95)

$W_7200_DO_Channel$  (ByVal do\_ch\_no As Byte, ByVal do\_data As Byte) As Long

### C/C++ (DOS)

int \_7200\_DO\_Channel (U8 do\_ch\_no, Boolean do\_data)

### @ Argument

do\_ch\_no: the DO channel number, the value has to be set within 0 and 31. do\_data: either 0 (OFF) or 1 (ON).

### @ Return Code

ERR\_NoError ERR\_InvalidDOChannel

# 5.13 \_7200\_Alloc\_DMA\_Mem

### @ Description

Contact Windows 95/98 system to allocate a block of contiguous memory for single-buffered DMA transfer. This function is only available in Windows 95/98.

### @ Syntax

### Visual C++ (Windows 95)

```

int W_7200_Alloc_DMA_Mem (U32 *buff, U32 *handle, U32

buf_size, U32 *actual_size)

```

### Visual Basic (Windows 95)

W\_7200\_Alloc\_DMA\_Mem (buff As Long, handle As Long, ByVal buf\_size As Long, actual\_size As Long ) As Long

# @ Argument

**buff:** The start address of the user buffer for DMA data transfer. This buffer will be attached to the DMA memory allocated by this function. When using this DMA memory handle as an argument of the W\_7200\_DI\_DMA\_Start function, DI data will be copied to this buffer. When using this DMA memory handle as an argument of the W\_7200\_DO\_DMA\_Start function, the data stored in this buffer will be the DO data.

**handle:** The handle of system DMA memory returned from system. Use this handle in 7200 DI DMA Start or 7200 DO DMA Start.

**buf\_size:** Bytes to allocate. Please be careful, the unit of this parameter is BYTE. not SAMPLE.

**actual\_size:** The actual size system allocate for DMA memory. The unit is BYTE. If system is not able to get a block of contiguous memory of specified <code>buf\_size</code>, it will allocate a block of memory as large as it can. In this case, this function returns ERR\_SmallerDMAMemAllocated, and <code>actual\_size</code> denotes the actual size of allocated memory.

#### @ Return Code

ERR\_NoError

ERR SmallerDMAMemAllocated

# 5.14 \_7200\_Free\_DMA\_Mem

### @ Description

Releases system DMA memory. This function is only available in Windows 95/98.

### @ Syntax

### Visual C++ (Windows 95)

```

int W_7200_Free_DMA_Mem (U32 handle)

```

#### Visual Basic (Windows 95)

W\_7200\_Free\_DMA\_Mem (ByVal handle As Long ) As Long

### @ Argument

handle: The handle of system DMA memory to release.

### @ Return Code

ERR NoError

# 5.15 \_7200\_Alloc\_DBDMA\_Mem

### @ Description

Contact Windows 95/98 system to allocate a block of contiguous memory as circular buffer for double-buffered DMA DI transfer. This function is only available in Windows 95/98 version. For double-buffered transfering, please refer to Section 6 "Double Buffered Mode Principle".

### @ Syntax

### Visual C++ (Windows 95)

```

int W_7200_Alloc_DBDMA_Mem (U32 *buff,U32 *handle, U32

buf_size, U32 *actual_size)

```

### Visual Basic (Windows 95)

W\_7200\_Alloc\_DBDMA\_Mem (buff As Long, handle As Long, ByVal buf\_size As Long, actual\_size As Long) As Long

#### @ Argument

**buff:** There is a dummy buffer attached to the DMA memory this function will allocate. But this buffer needs to have size equal to or more than *buf\_size* bytes.

**handle:** The handle of system DMA memory returned from system. Use this handle in 7200 DI DMA Start.

**buf\_size:** Bytes to allocate. This is the half size of circular buffer in byte. That is, this is the size of each half buffer in byte.

actual\_size: The actual DMA memory size system allocate for each half buffer. If system is not able to get a block of contiguous memory of specified buf\_size, it will allocate a block of memory as large as it can. In this case, this function returns ERR\_SmallerDMAMemAllocated, and actual\_size

#### 46 . C/C++ Libraries

denotes the actual size of allocated memory for each half of circular buffer.

#### @ Return Code

ERR\_NoError

ERR\_SmallerDMAMemAllocated

# 5.16 \_7200\_Free\_DBDMA\_Mem

### @ Description

Releases a system's circular buffer DMA memory. This function is only available in Windows 95/98. For double-buffered transfer principle, please refer to Section 6 "Double Buffered Mode Principle".

### @ Syntax

### Visual C++ (Windows 95)

int W\_7200\_Free\_DBDMA\_Mem (U32 handle)

### Visual Basic (Windows 95)

W 7200 Free DBDMA Mem (ByVal handle As Long ) As Long

### @ Argument

handle: The handle of system DMA memory to release.

#### @ Return Code

ERR\_NoError

# 5.17 \_7200\_DI\_DMA\_Start

# @ Description

The function will perform digital input N times with DMA data transfer by using one of the following four sampling modes:

- 1. pacer trigger (internal timer trigger)

- external rising edge I REQ

- 3. external falling edge I REQ

- 4.1 REQ & I ACK handshaking

It will take place in the background which will not stop until the Nth input data is transferred or your program execute \_7200\_DI\_DMA\_Stop function to stop the process.

After executing this function, it is necessary to check the status of the operation by using the function \_7200\_DI\_DMA\_Status. The PCI-7200 Bus mastering DMA is different from traditional PC style DMA. Its description is as follows:

Bus Mastering DMA mode of the PCI-7200:

PCI bus mastering offers the highest possible speed available on the PCI-7200. When the function \_7200\_DI\_DMA\_Start is executed, it will enable PCI bus master operation. This is conceptually similar to DMA (Direct Memory Access) transfers in a PC but it is really PCI bus mastering. It does not use an 8237-style DMA controller in the host computer and therefore isn't blocked in 64k max groups. PCI-7200 bus mastering works as follows:

- 1. To set up bus mastering, first do all normal PCI-7200 initialization necessary to control the board in status mode. This includes testing for the presence of the PCI BIOS, determining the base addresses, slot number, vendor and device ID's, I/O, or memory, space allocation, etc. Please make sure the PCI-7200 is plugged in a bus master slot, otherwise this function will not be workable.

- 2. Load the PCI controller with the count and 32-bit physical address of the start of previously allocated destination memory, which will accept data. This count is the number of *bytes* (not long words) transferred during the bus master operation and can be a large number up to 64 million (2^26) bytes. Since PCI-7200 transfers are always long words, this equals 16 million long words (2^24).

- 3. After the input sampling is started, the input data is stored in the FIFO of PCI controller. Each bus mastering data transfer continually tests if any data in the FIFO and then blocks transfer, the system will continuously loop until the conditions are satisfied again but will not exit the block transfer cycle if the block count is not complete. If there is momentarily no input data, the PCI-7200 will relinquish the bus temporarily but returns immediately when more input data appears. This operation continues until the whole block is done.

- 4. This operation proceeds transparently until the PCI controller transfer byte count is reached. All normal PCI bus operations applied here, such as a receiver that cannot accept the transfers, higher priority devices requesting the PCI bus, etc. Remember that only one PCI initiator can have bus mastering at any one time. However, review the PCI priority and "fairness" rules. Also study the effects of the Latency Timer. Additionally, be aware that the PCI priority strategy (round robin rotated, fixed priority, custom, etc.) is unique to each host PC and is explicitly not defined by the PCI standard. You must determine this priority scheme for your own PC (or replace it).

The interrupt request from the PCI controller can be optionally set up to indicate that this loanword count is complete although this can also be determined by polling the PCI controller.

### @ Syntax

### Visual C++ (Windows 95)

int W\_7200\_DI\_DMA\_Start (U8 mode, U32 count, U32 handle,

Boolean wait\_trg, U8 trg\_pol, Boolean clear\_fifo, Boolean

disable\_di)

### Visual Basic (Windows 95)

W\_7200\_DI\_DMA\_Start (ByVal mode As Byte, ByVal count As Long, ByVal handle As Long, ByVal wait\_trg as Byte, ByVal trg\_pol As Byte, ByVal clear\_fifo As Byte, ByVal disable\_di As Byte) As Long

### C/C++ (DOS)

int \_7200\_DI\_DMA\_Start (U8 mode, U32 count, U32 \*di\_buffer, Boolean wait\_trig, U8 trig\_pol, Boolean clear\_fifo, Boolean disable di)

### @ Argument

mode: Digital Input trigger modes

DI\_MODE0: Internal timer pacer (TIME 0)

DI\_MODE1: External signal I\_REQ rising edge

DI\_MODE2: External signal I\_REQ falling edge

DI\_MODE3: I\_REQ & I\_ACK handshaking

**count:** For non-double-buffered DI, this parameter denotes the number of digital input samples to read. For double-buffered DI, it is the size of circular buffer (in samples, not in bytes).

handle (Win95): The handle of system DMA memory. In Windows 95, before calling \_7200\_DI\_DMA\_Start, depending on using double-buffer mode or not, either \_7200\_Alloc\_DMA\_Mem or \_7200\_Alloc\_DBDMA\_Mem must be called to allocate a contiguous DMA memory and get the handle.

di\_buffer (DOS): If double buffer mode is disabled, this is the start address of the memory buffer to store the DI data. If double buffer mode is enabled, this memory buffer is actually of no use. But the buffer size still must be larger than the number of *count* (count\*4 bytes). Use this buffer as transfer buffer in 7200 DblBufferTransfer to make use of this buffer.

\*\*This memory should be double-word alignment.

wait\_trig: The waiting status of trigger

DI\_NONWAITING: the input sampling will be start immediately DI\_WAITING: the input samples waiting rising or falling edge trigger to start DI

trig\_pol: trigger polarity

DI\_RISING: rising edge trigger DI\_FALLING: falling edge trigger

### clear\_fifo:

- 0: retain the FIFO data

- 1: clear FIFO data before perform digital input

### disable di:

- **0:** digital input operation still active after DMA transfer complete

- 1: disable digital input operation immediately when DMA transfer complete

#### @ Return Code

ERR\_NoError

ERR\_BoardNoInit

ERR\_InvalidDIOMode

ERR\_InvalidDIOCnt

ERR\_NotDWordAlign

ERR\_DMATransferNotAllowed

# 5.18 \_7200\_DI\_DMA\_Status

### @ Description

Since the \_7200\_DI\_DMA\_Start function is executed in background, users can issue this function to check its operation status. This function only works when double-buffer mode is set as disable.

# @ Syntax

### Visual C++ (Windows 95)

```

int W_7200_DI_DMA_Status (U8 *status, U32 *count)

```

### Visual Basic (Windows 95)

$W_7200\_AD\_Status$  (status As Byte, count As Long ) As Long **C/C++ (DOS)**

int \_7200\_AD\_DMA\_Status (U8 \*status, U32 \*count)

### @ Argument

status: status of the DMA data transfer

0: DI DMA STOP: DMA is completed

1: DI DMA RUN: DMA is not completed

count: the numbers of DI data which has been transferred.

#### @ Return Code

ERR NoError

# 5.19 \_7200\_DI\_DMA\_Stop

### @ Description

This function is used to stop the DMA data transferring. After executing this function, the \_7200\_DI\_DMA\_Start function is stopped. The function returns the number of the data which has been transferred, no matter if the digital input DMA data transfer is stopped by this function or by the DMA terminal count, ISR.

### @ Syntax

```

Visual C++ (Windows 95)

int W_7200_DI_DMA_Stop (U32 * count)

Visual Basic (Windows 95)

W_7200_DI_DMA_Stop ( count As Long ) As Long

C/C++ (DOS)

int _7200_DI_DMA_Stop (U32 *count)

```

### @ Argument

count: the number of DI data which has been transferred.

#### @ Return Code

ERR\_NoError ERR BoardNoInit

# 5.20 7200 DblBufferMode

### @ Description

This function is used to enable or disable double buffer mode for DMA DI operation.

# @ Syntax

```

Visual C++ (Windows 95)

int W_7200_DblBufferMode (Boolean db_flag)

Visual Basic (Windows 95)

W_7200_DblBufferMode (ByVal db_flag As Byte) As Long

C/C++ (DOS)

int _7200_CheckHalfReady (Boolean db_flag)

```

# @ Argument

**db\_flag:** 1: double buffer mode enabled 0: double buffer mode disabled

#### @ Return Code

ERR\_NoError

# 5.21 \_7200\_CheckHalfReady

### @ Description

When you use \_7200\_DI\_DMA\_Start to sample digital input data and double buffer mode is set as enable. Users must use \_7200\_CheckHalfReady to check data ready (data half full) or not in the circular buffer, and using \_7200\_DblBufferTransfer to get data.

### @ Syntax

```

Visual C++ (Windows 95)

```

int W\_7200\_CheckHalfReady (Boolean \* halfReady)

### **Visual Basic (Windows 95)**

W\_7200\_CheckHalfReady (halfReady As Byte) As Long

# C/C++ (DOS)

int \_7200\_CheckHalfReady (Booelan \*halfReady)

### @ Argument

halfReady: 1 (TRUE) or 0 (FALSE)

### @ Return Code

ERR NoError

# 5.22 \_7200\_DblBufferTransfer

# @ Description

Use this function to copy the input data in the circular buffer to the transfer buffer. It copies half of the circular buffer, either first half or second half, to the transfer buffer.

# @ Syntax

### Visual C++ (Windows 95)

int W\_7200\_DblBufferTransfer (U32 \*userBuffer)

### Visual Basic (Windows 95)

W\_7200\_DblBufferTransfer (userBuffer As Long) As Long

#### C/C++ (DOS)

int \_7200\_DblBufferTransfer (U32 \*userBuffer)

# @ Argument

**userBuffer:** the start address of the transfer buffer. The W\_7200\_DblBufferTransfer function copies half of the circular buffer to userBuffer.

#### @ Return Code

ERR\_NoError, ERR\_NotHalfReady

#### 52 • C/C++ Libraries

# 5.23 \_7200\_GetOverrunStatus

### @ Description

When using \_7200\_DI\_DMA\_Start to convert Digital I/O data with double buffer mode enabled, and not using \_7200\_DblBufferTransfer to move converted data then double buffer overrun will occur. Use this function to check overrun count.

### @ Syntax

### Visual C++ (Windows 95)

int W\_7200\_GetOverrunStatus (U32 \* overrunCount)

### **Visual Basic (Windows 95)**

int  $W_7200\_GetOverrunStatus$  (overrunCount As Long) As Long **C/C++ (DOS)**

int \_7200\_GetOverrunStatus (U32 \*overrunCount )

### @ Argument

overrunCount: number of overruns.

#### @ Return Code

ERR\_NoError

# 5.24 7200 DO DMA Start

### @ Description

The function will perform digital output N times with DMA data transfer by using the following four sampling modes:

- 1. Pacer trigger (internal timer trigger, TIME 1)

- 2. Internal timer pacer with O REQ enabled

- 3. O REQ & O ACK handshaking

It takes place in the background which will not be stop until the Nth conversion has been completed or the program executes the \_7200\_DO\_DMA\_Stop function to stop the process. After executing this function, it is necessary to check the status of the operation by using the function 7200 DO DMA Status.

# @ Syntax

### Visual C++ (Windows 95)

int  $W_7200_DO_DMA_Start$  (U8 mode, U32 count, U32 handle, Boolean repeat)

#### Visual Basic (Windows 95)

W\_7200\_DO\_DMA\_Start (ByVal mode As Byte, ByVal count As Long, ByVal handle As Long, ByVal repeat as Byte) As Long

### C/C++ (DOS)

int \_7200\_DO\_DMA\_Start (U8 mode, U32 count, U32 \*do\_buffer, Boolean repeat)

### @ Argument

mode: Digital output trigger modes

DO\_MODE\_0: Internal timer pacer (TIME 1)

DO MODE 1: Internal timer pacer with O REQ enable

DO MODE 2: O REQ & I REQ handshaking

**count:** the sample number of digital output data (in samples, not in bytes) **handle (Win 95):** the handle of system DMA memory. In Windows 95, before calling W\_7200\_DO\_DMA\_Start, W\_7200\_Alloc\_DMA\_Mem must be called to allocate a contiguous DMA memory and get the handle of it. Also W\_7200\_Alloc\_DMA\_Mem will attach a buffer to DMA memory. The DO data is stored in the buffer attached to this handle.

do\_buffer (DOS): the start address of the memory buffer to store the DO data.

**repeat:** The digital output will be continuous or only one shot.

CONTINUOUS: digital output will be continuous until 7200 DO DMA STOP is called.

ONE\_SHOT: digital output only one-shot.

### @ Return Code

ERR\_NoError

ERR\_InvalidDIMode

ERR\_InvalidBoardNumber

ERR BoardNoInit

ERR\_InvalidDIOCnt

ERR\_NotDWordAlign

ERR\_DMATransferNotAllowed

# 5.25 \_7200\_DO\_DMA\_Status

### @ Description

Since the \_7200\_DO\_DMA\_Start function is executed in background, users can issue the function \_7200\_DO\_DMA\_Status to check its operation status.

### @ Syntax

### Visual C++ (Windows 95)

int W\_7200\_DO\_DMA\_Status (U8 \*status, U32 \* count)

#### Visual Basic (Windows 95)

W\_7200\_DO\_Status ( status As Byte, count As Long ) As Long

#### 54 • C/C++ Libraries

<sup>\*\*</sup> This memory should be double-word alignment

### C/C++ (DOS)

int \_7200\_DO\_DMA\_Status (U8 \*status , U32 \*count)

### @ Argument

**status:** status of the DMA data transfer. 0: DO\_DMA\_STOP: DMA is completed 1: DO\_DMA\_RUN: DMA is not completed

**count:** the amount of DO data which has been transferred.

#### @ Return Code

ERR\_NoError

# 5.26 \_7200\_DO\_DMA\_Stop

### @ Description

This function is used to stop the DMA DO operation. After executing this function, the \_7200\_DO\_DMA\_Start function is stopped. The function returns the number of the data which has been transferred, regardless if the digital output DMA data transfer is stopped by this function or by the DMA terminal count ISR.

### @ Syntax

### Visual C++ (Windows 95)

int W\_7200\_DO\_DMA\_Stop (U32 \*count)

# Visual Basic (Windows 95)

W\_7200\_DO\_DMA\_Stop (count As Long) As Long

#### C/C++ (DOS)

int \_7200\_DO\_DMA\_Stop (U32 \*count)

### @ Argument

**count:** the number of digital output data which has been transferred.

#### @ Return Code

ERR\_NoError

ERR BoardNoInit

# 5.27 \_7200\_DI\_Timer

### @ Description

This function is used to set the internal timer pacer for digital input. There are two configurations for the internal timer pacer:

1. Non-cascaded (One COUNTER 0 only)

Timer pacer frequency = 4Mhz / C0

2. Cascaded (TIME2 cascaded with COUNTER0)

Timer pacer frequency = 4Mhz / (C0 \* C2)

### @ Syntax

### Visual C++ (Windows 95)

int W\_7200\_DI\_Timer (U16 c0, U16 c2, Boolean mode)

#### Visual Basic (Windows 95)

$\mbox{W}_{-}7200\_\mbox{DI}_{-}\mbox{Timer}$  (  $\mbox{ByVal}$  c0 As Integer,  $\mbox{ByVal}$  c2 As Integer,  $\mbox{ByVal}$  mode As  $\mbox{Byte}$  ) As Long

#### C/C++ (DOS)

int \_7200\_DI\_Timer (U16 c0, U16 c2, Boolean mode)

### @ Argument

- **c0:** frequency divider of Counter #0. Valid value ranges from 2 to 65535.

- c2: frequency divider of Counter #2. Valid value ranges from 2 to 65535.

**Note**: Since the Integer type in Visual Basic is a signed integer. Its range is within -32768 and 32767. In Visual Basic, to set c0 or c2 to a value larger than 32767, set it as the intended value minus 65536. For example, to set c0 as 40000, set c0 as 40000-65536=-25536.

### 56 • C/C++ Libraries

mode: TIMER\_NONCASCADE or TIMER\_CASCADE

#### @ Return Code

ERR\_NoError

ERR\_InvalidBoardNumber

ERR\_InvalidTimerMode

ERR\_BoardNoInit

# 5.28 \_7200\_DO\_Timer