# OCPRF100 MP Server System

Supporting Up To Eight Intel<sup>®</sup>

Pentium<sup>®</sup> III Xeon<sup>™</sup> Processors

# **Technical Product Specification**

Intel Order #753674-001 Revision 1.0

# Revision History

| Date            | Rev. | Modifications    |

|-----------------|------|------------------|

| September, 1999 | 1.0  | Initial release. |

|                 |      |                  |

|                 |      |                  |

# **Disclaimers**

Except as provided in Intel's Terms and Conditions of Sale for such products, INTEL DISCLAIMS ALL LIABILITIES AND WARRANTIES (EXPRESS, IMPLIED OR OTHERWISE) ASSOCIATED WITH THE INFORMATION CONTAINED WITHIN THIS DOCUMENT, OR FOR ANY PROD-UCTS OR DEVICES REFERRED TO HEREIN, INCLUDING, WITHOUT LIMITATION, LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS RELATING TO THIS DOCUMENT, OR ANY PRODUCTS OR DEVICES REFERENCED HEREIN, OR FOR THE IMPLEMENTATION OF INFORMATION IN THIS DOCUMENT INTEL IS NOT OBLIGATED TO PROVIDE ANY SUP-PORT, INSTALLATION, OR OTHER ASSISTANCE WITH REGARD TO THESE DEVICES, NOR ANY UPDATES, CORRECTIONS OR MODIFICATIONS TO THIS DOCUMENT OR THE INFORMATION CONTAINED HEREIN.

THE INTEL® PRODUCT REFERRED TO IN THIS DOCUMENT IS INTENDED FOR STAN-DARD COMMERCIAL USE ONLY. CUSTOMERS ARE SOLELY RESPONSIBLE FOR ASSESSING THE SUITABILITY OF THE PRODUCT AND/OR DEVICES FOR USE IN PARTIC-ULAR APPLICATIONS. THE REFERENCED INTEL PRODUCT IS NOT INTENDED FOR USE IN CRITICAL CONTROL OR SAFETY SYSTEMS OR IN NUCLEAR FACILITY APPLICATIONS. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

Information in this document is provided in connection with Intel products. This document is provided "as is" with no warranties whatsoever. Intel specifically disclaims any implied or express warranties of any kind whatsovever, associated with this document, including without limitation: (i) liability for infrinement of any proprietary rights (including without limitation, any intellectual property right), merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any product or testing proposal, specification or sample; (ii) sufficiency, reliability, accuracy, completeness or usefulness of same, and (iii) ability or sufficiency of same to function accurately as a representation of any standard. No license, express, implied, or otherwise, to any intellectual property rights is granted by this document or by the sale of Intel products. Furthermore, Intel makes no commitment to update the information contained in this document or any test report, provided that Intel may make changes to this document, the test reports, specifications and product descriptions at any time, without notice.

Third parties may have intellectual property rights which may be relevant to this document and the technologies discussed herein, accordingly the reader is advised to seek the advice of competent counsel, as required withhout obligation to Intel.

Only approved software drivers and accessories that are recommended for the revision number of the boards and system being operated should be used with Intel products. Please note that, as a result of warranty repairs or replacements, alternate software and firmware versions may be required for proper operation of the equipment.

The hardware vendor remains solely responsible for the design, sale and functionality of its product, including any liability arising from product infringement or product warranty.

The **OPRF100 MP Board Set** and the **OCPRF100 MP Server System** product may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are available on request.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Copyright © 1999 Intel Corporation.

\*Other brands and names are the property of their respective owners.

# **Table of Contents**

| Introduction                         |    |

|--------------------------------------|----|

| Server System Chassis and Assemblies | 3  |

| Front Panel Assembly                 |    |

| Peripheral Bay                       | 4  |

| Top Cover Assembly                   | 5  |

| Hot-plug PCI Access Door             |    |

| Fan Bay                              |    |

| Front Panel Board                    |    |

| Processor Mezzanine Board            |    |

| Processor Retention Mechanism        | 9  |

| Profusion® Carrier Tray              | 11 |

| Midplane Assembly                    | 13 |

| I/O Carrier                          |    |

| Power Supply                         | 16 |

| OCPRF100 MP Server System Chassis    | 16 |

| System Overview                      | 17 |

| Introduction                         | 17 |

| External Chassis Features            | 20 |

| Front View of Chassis                |    |

| Rear View of Chassis                 |    |

| Riser Board External I/O Connectors  |    |

| Peripheral Bay                       |    |

| 3.5-inch User-accessible Drive Bay   |    |

| 5.25-inch User-accessible Drive Bay  |    |

| 3.5-inch SCSI Hot-swap Drive Bays    |    |

| Internal Chassis Features            |    |

| Power System                         |    |

| Cooling System                       |    |

| PCI Hot-plug                         |    |

| Server Management                    |    |

| Front Panel Controller               |    |

| Baseboard Management Controller      |    |

| Hot-swap Controller                  |    |

| Expansion Support                    |    |

| Specifications                       |    |

| Environmental Specifications         |    |

| Physical Specifications              |    |

| Cables and Connectors                |    |

| Cables                               |    |

| Connectors                           |    |

| User-accessible I/O Connectors       |    |

| Serial Ports                         |    |

| Parallel Port                        |    |

| VGA Video Port                       |    |

| Universal Serial Bus Interface       |    |

| ICMB Connectors                      | 46 |

| Fan Connector                               |    |

|---------------------------------------------|----|

| Peripheral Bay Power Connector              |    |

| Peripheral Bay Backplane Header             |    |

| LED Board Connector                         | 50 |

| SCSI Connector                              | 51 |

| IDE Connectors                              | 52 |

| Floppy Connectors                           | 53 |

| Power Supply                                | 54 |

| Mechanical Requirements                     | 54 |

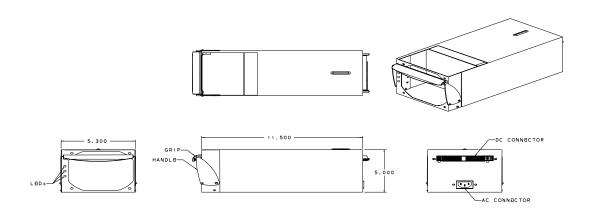

| Mechanical Outline                          | 54 |

| Fan Requirements                            | 55 |

| Interface Requirements                      | 55 |

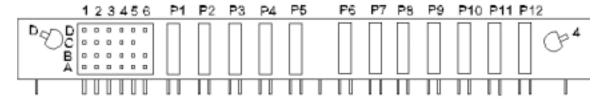

| AC Inlet Connector                          | 55 |

| DC Output Connector(s)                      | 55 |

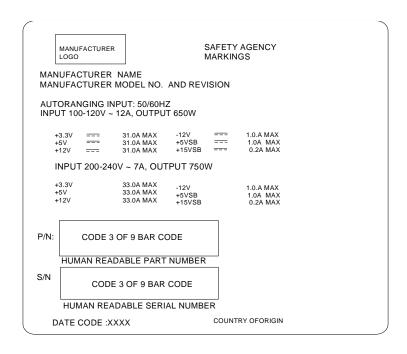

| Marking and Identification                  | 56 |

| LED Labeling                                | 56 |

| Internal System Marking                     | 56 |

| Electrical Requirements                     |    |

| Efficiency                                  | 58 |

| AC Input Voltage Specification              | 58 |

| AC Input Voltage Ranges                     | 58 |

| DC Output Specification                     | 59 |

| Control Signals                             | 62 |

| Power Supply On (Input)                     | 62 |

| AC OK Signal (Output)                       | 62 |

| Power Good (Output)                         | 63 |

| Power Supply Present Indicator (Output)     | 64 |

| Predictive Failure Signal (Output)          |    |

| Power Supply Failure Signal (Output)        | 64 |

| Power Supply Kill (Input)                   |    |

| Power Supply Field Replacement Unit Signals |    |

| LED Indicators                              |    |

| Fan Speed Control                           | 67 |

| Environmental Requirements                  | 67 |

| Physical Environment                        | 67 |

| Thermal Protection                          |    |

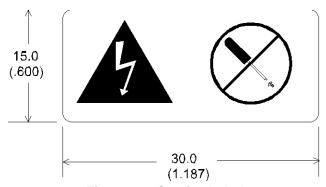

| Regulatory Agency Requirements              | 67 |

| System Software                             |    |

| System Hardware                             | 69 |

| Processors                                  | 69 |

| Profusion® Chip Set                         | 70 |

| I/O Subsystem                               |    |

| Intelligent Platform Management Bus         |    |

| Industry Standards                          | 71 |

| ACPI                                        | 71 |

| Boot Devices and Peripherals                | 72 |

| Management                                  | 73 |

| Configuration                               | 73 |

| BIOS Setup Utility                          | 74 |

| Main Menu                                   | 75 |

| Advanced Menu                                         | 78  |

|-------------------------------------------------------|-----|

| Security Menu                                         | 82  |

| Server Menu                                           |     |

| Boot Menu                                             | 85  |

| Exit Menu                                             |     |

| Flash Utility                                         |     |

| Regulatory Specifications                             |     |

| Safety Compliance                                     |     |

| Electromagnetic Compatibility                         |     |

| CE Mark                                               |     |

| Electromagnetic Compatibility Notice (USA)            |     |

| Electromagnetic Compatibility Notices (International) |     |

| Peripheral Bay Backplane Board                        |     |

| Peripheral Bay Backplane Overview                     |     |

| Architectural Overview                                |     |

| Placement Diagram                                     |     |

| Deviations from SAF-TE Specification                  |     |

| Functional Description                                |     |

| Hot-swap Connectors                                   |     |

| SCSI Interface                                        |     |

| LVD/SE Active Termination                             |     |

| Power Control                                         |     |

| FET Short Protection                                  |     |

| Microcontroller                                       |     |

| LED Arrangement                                       |     |

| IPMB (I2C bus)                                        |     |

| Temperature Sensor                                    |     |

| Serial EEPROM                                         |     |

| Board Functions                                       |     |

| Reset                                                 |     |

| Microcontroller                                       |     |

| SCSI Controller                                       |     |

| LVDS SCSI Termination                                 |     |

| LVDS Termination                                      |     |

| Single Ended Termination                              |     |

|                                                       |     |

| Programmable Logic                                    |     |

| Memory Map                                            |     |

| Memory Map                                            |     |

| I/O Ports                                             |     |

| Signal Descriptions                                   |     |

| Power Good Signal                                     |     |

| CONN_EN_L                                             |     |

| CONN_SDI                                              |     |

| CONN_SDO                                              |     |

| CONN_MODE                                             |     |

| CONN_SCLK                                             |     |

| Electrical, Mechanical Specifications                 |     |

| Connectors                                            |     |

| Peripheral Bay Board (Chassis Side)                   |     |

| Introduction                                          | 111 |

| ** 1 · 1 · 1 · 1 · 1 · 1 · 1 · 1 · 1 · 1 |     |

|------------------------------------------|-----|

| Mechanical Description                   | 111 |

| Board Layout                             |     |

| Front Panel                              | 113 |

| Introduction                             | 113 |

| Board Overview                           | 113 |

| Functional Description                   | 114 |

| Microcontroller                          |     |

| Memory Maps                              |     |

| Memory                                   |     |

| Front Panel Indicator LEDs               |     |

| Front Panel LCD                          |     |

| System Power                             |     |

| Reset                                    |     |

| Speaker                                  | 126 |

| Fan Control                              |     |

| ICMB and COM2 Redirection                | 126 |

| Front Panel Push Buttons                 | 129 |

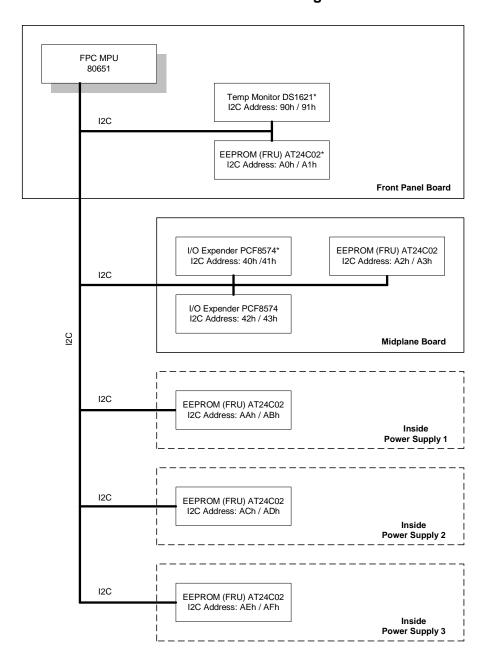

| I2C Interfaces                           |     |

| Miscellaneous                            |     |

| Appendix A: Glossary                     |     |

| Appendix B: References                   |     |

| , .pp                                    |     |

# 1. Introduction

This document provides an overview of the OCPRF100 MP server system and includes information on cabling, connectors, power supply, and regulatory requirements.

### **Document Structure and Outline**

This document is organized into ten chapters:

Chapter 1: Introduction

Provides an overview of this document.

Chapter 2: **Server System Chassis and Assemblies**

Provides an overview of the chassis hardware.

Chapter 3: **System Overview**

Provides an overview of the system hardware.

**Cables and Connectors** Chapter 4:

Describes the cables and connectors used to interconnect the OPRF100

board set and the server system components.

**Power Supply** Chapter 5:

Describes the specifications for the 750-W power supply.

Chapter 6: **OCPRF100 MP Server Software**

Provides an overview of the system software.

Chapter 7: **Regulatory Specifications**

Describes system compliance to regulatory specifications.

Peripheral Bay Backplane Board Chapter 8:

Describes the features and functionality of the peripheral bay backplane

board.

Chapter 9: Peripheral Bay Board (Chassis Side)

Describes the design of the peripheral bay board (chassis side).

**Front Panel** Chapter 10:

Describes the design and external interface of the OCPRF100 MP server

system front panel.

This page intentionally left blank.

# **Server System Chassis and Assemblies**

This chapter describes the chassis and assembly pieces that reside within the chassis. This chapter is divided into the following areas:

- Front panel assembly

- Peripheral bay

- Top cover assembly

- Fan bay

- Front panel board

- Processor mezzanine board

- Processor retention mechanism

- Profusion® carrier tray

- Midplane assembly

- I/O carrier assembly

- Power supply

- OCPRF100 MP server system chassis

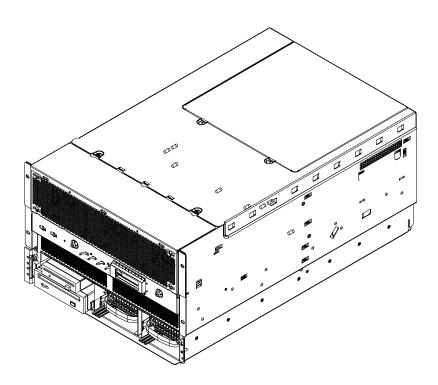

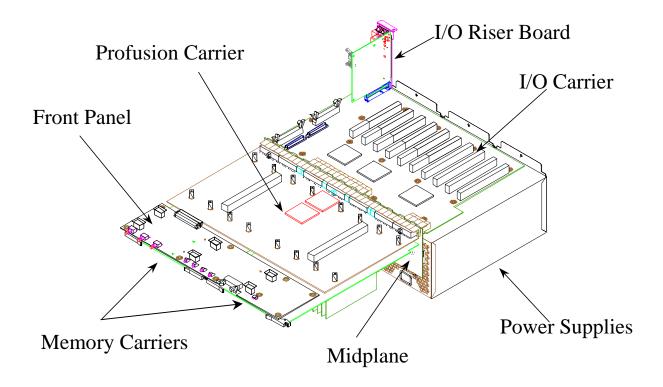

Figure 2-1: OCPRF100 MP Server System Chassis

# 2.1 Front Panel Assembly

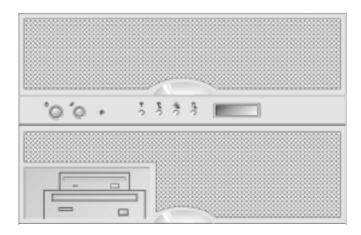

The front panel assembly consists of an upper and lower bezel. The bezels serve as cosmetic pieces only, and can be integrator specific. Finger grips are provided to make it easy to remove the bezels. Removing the bezels exposes the front side of the fan bay, the front panel controller (FPC) switches (power, reset, and nonmaskable interrupt (NMI)), as well as the indicator lights (power indicator, predictive power supply failure, predictive fan failure, and hard drive failure). From this location, the hot-swap hard drives and/or the peripheral bay may be removed from the system.

Figure 2-2: Front Panel

# 2.2 Peripheral Bay

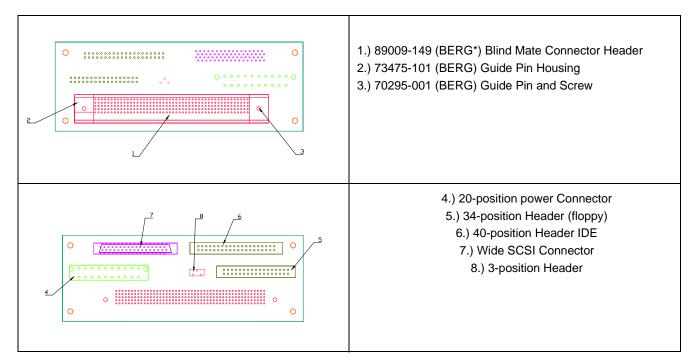

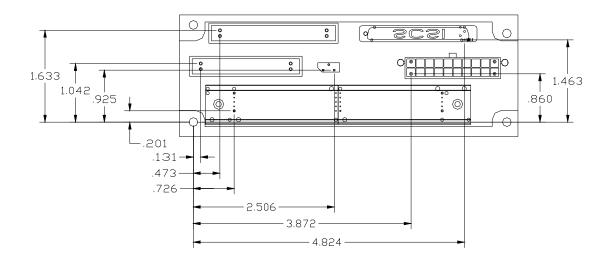

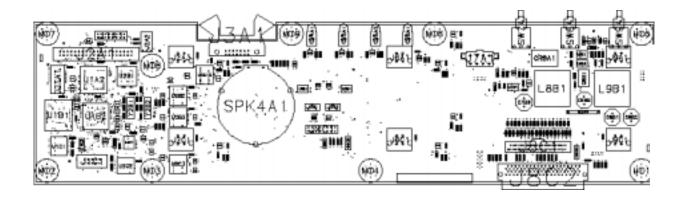

The peripheral bay is defined to be a customer specific, removable device capable of supporting a floppy drive, dual hot-swap hard drives, and a low-voltage differential SCSI (LVDS) or single ended SCSI device. The integrator has the option of defining the size and capacity of the hard drives, as well as deciding whether the LVDS will support CD-ROM, tape, or other device. A single ended SCSI channel is provided for support of a SCSI device, should the integrator so desire.

The peripheral bay is designed to be easily added and removed from the front of the server by removing the front cover and four mounting screws. The peripheral bay connects to the OPRF100 I/O carrier and the power supply via a blind mate board connector and cabling. The blind mate board is located in front of the midplane board, on the left side of the server (when viewing the server from the front). The blind mate connector connects to the peripheral bay's LVDS board upon insertion, thus connecting all peripheral devices to the I/O carrier.

The peripheral bay will contain a 1.4 MB floppy drive, space for a half-height 5 ¼ inch device (typically a CD-ROM), and has two bays designed to accommodate either a 1-inch or a 1.6-inch SCA hard drive.

Figure 2-3: Peripheral Bay

# 2.3 Top Cover Assembly

The top cover assembly is released by removing the two retaining screws located on the top toward the front (E in Figure 2-4: Hot-plug PCI Access Door), between the fan bay assembly and the top cover assembly marked with the AC caution icon. The cover slides toward the rear of the server and then lifts straight up off of the server chassis, exposing the upper portion of the server for maintenance, upgrades, or adding components.

Tape and sheet metal work were done to the sides of the top cover assembly to provide a better gripping surface for easier removal and replacement of the top cover assembly. Care should be taken to avoid damage to the electromagnetic compatibility (EMC) gasket material on the inside of the top cover.

# 2.3.1 Hot-plug PCI Access Door

The hot-plug PCI access door is released by removing the two retaining screws (A in Figure 2-4: Hot-plug PCI Access Door) located on the top, middle area of the server. The cover slides toward the rear of the server and lifts straight up off of the server chassis, exposing the hot-plug PCI cards.

The hot-plug PCI access door is designed to maintain a flush surface with the top cover assembly, such that a vacuum-based hoist may be used during the assembly process.

Figure 2-4: Hot-plug PCI Access Door

# 2.4 Fan Bay

The fan bay is a mechanical structure designed to contain six separate 120-mm cooling fans. These fans operate at a nominal voltage of 8.4 Vdc (2% tolerance) under normal conditions. Each fan produces a tachometer-based output to indicate the revolutions per minute (RPM) reading of the motor. Should a fan's tachometer output drop below a predefined normal range of operation, the FPC notifies the server management software that a fan has entered into the predictive fan failure condition. At this point, the fans will operate at an elevated voltage of approximately 12 Vdc.

The fan bay will operate at high speed on the following conditions:

- Internal temperature has reached an elevated, but noncritical set-point.

- Ambient temperate exceeds 30°C.

- A fan has entered into the predictive failure mode.

- A fan has failed.

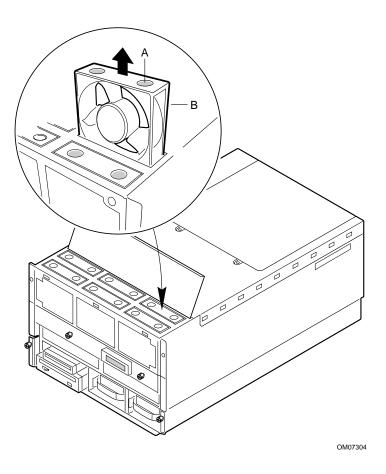

If the FPC detects a fan entering the predictive fan failure mode, the speed of all of the fans will be increased to maintain thermal requirements. The individual fans within the fan bay are all hotswappable, meaning that they can be removed and inserted while the server is running. Server management will identify that a fan has either failed or has entered into the predictive failure mode. In both cases, the fan should be replaced immediately. Removal of a fan is accomplished by opening the fan bay cover and pulling (A) to lift the malfunctioning fan (B) out through the top of the server as shown in Figure 2-5: Fan Bay. The malfunctioning fan should then be replaced with a new fan. The system will detect that the fan has been replaced, and as long as no other thermal violations are currently occurring, the fan will resume operation at the reduced speed.

Figure 2-5: Fan Bay

Fans are installed with the connector on the left side facing down. The cavities in the fan bay are keyed to prevent a fan from being installed backwards.

The fan bay is installed after the Profusion carrier assembly is installed and completely seated into the midplane. The fan bay is lowered into the chassis until it is seated on the flanges of the Profusion tray. Two screw holes, one on each side, should now be aligned on the sides of the chassis. Insert screws into these holes to secure the fan bay into the chassis.

The fan bay cover is hinged at the rear and captivated by the system top cover assembly. Tabs in the rear of the fan bay cover engage with slots on the rear of the fan bay to secure the cover in normal operation. The fan bay cover is secured by one noncaptive screw located on the center of the cover's front flange. Remove the screw, slide the cover forward and lift. The cover remains open while servicing the fans.

To remove the fan bay from the chassis, it is first necessary to remove all individual fans from the fan bay. The fans plug directly into the front panel board and must be removed before the fan bay can be lifted out.

The fan bay cover provides critical electromagnetic interference (EMI) containment. To avoid electrical interference with adjacent equipment, close and secure the fan bay cover during normal system operation.

In systems with only one processor mezzanine board, an air baffle needs to be installed on the vacant side of the CPU retention cage to ensure proper cooling for the installed processors.

# 2.5 Front Panel Board

The FPC board provides power and monitors the tachometer readings from each individual fan within the fan bay. The FPC also serves as a platform for the server controller switches, and supports circuitry required for server management.

The FPC board is located on the same plane as, and connects to the Profusion carrier board via a connector. Both the FPC and Profusion carrier board are mounted to the topside of the Profusion carrier tray. On the left front edge of the FPC board are three push button switches—power, reset, and NMI. Each switch plunger has a small black cap on its end, which is necessary for the proper operation of the buttons on the front bezel.

To install an FPC board, tilt the board forward as shown in Figure 2-6: Front Panel Board Installation, and insert the switches into the openings on the front flange of the Profusion carrier tray. Lower the back of the board onto the standoffs on the tray. Align the board-to-board connectors and slide the board back to engage the connectors. Secure with nine screws. Reverse this operation to remove the board.

Figure 2-6: Front Panel Board Installation

# 2.6 Processor Mezzanine Board

The base configuration of an OCPRF100 MP server system consists of a single processor mezzanine board. The processor mezzanine board is designed to support one to four Pentium<sup>®</sup> III Xeon™ processors, providing power, ground and other connections to the processor(s) and to the Profusion carrier. The processor mezzanine board incorporates integrated voltage regulator modules (VRMs) to supply the internal voltage requirements to the processor cartridge.

# 2.7 Processor Retention Mechanism

The processors and termination cards are secured in their respective slots by means of the processor retention mechanism. The processor retention mechanism holds up to eight processors or termination cards. In the event the server is populated with only a single processor mezzanine card, the processor retention mechanism will be populated with a total of four contiguous processors and/or terminators.

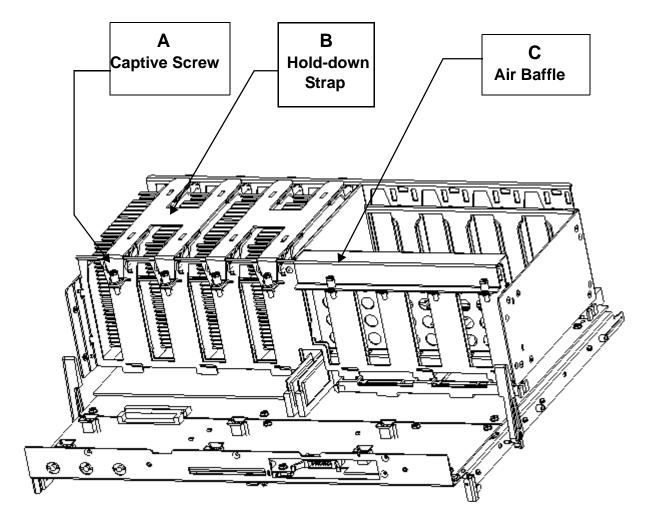

Figure 2-7: Processor Retention Mechanism

A processor/termination card pair is secured with a hold-down strap (B) that hooks into the back of the retention mechanism and is fastened at the front with two captive screws (A). (The retention strap is for a pair of processors or terminators). See Figure 2-7: Processor Retention Mechanism.

The processor retention mechanism is secured to the mezzanine boards with the same four lock bars that secure the mezzanine boards to the Profusion carrier board. In the event the server is populated with only a single processor mezzanine card, an air baffle (C) must be installed on the vacant side of the processor retention mechanism.

To remove or add a processor, first release the captive screws (A), then swing the retention strap (B) upward. Remove the terminator card, and install the processor. Replace the retention strap (B), and tighten the captive screw (A).

Due to space restrictions in the system, the Profusion carrier tray assembly must be removed from the chassis to install and service the mezzanine boards. The fan bay assembly must be removed prior to removing the Profusion carrier tray.

# 2.8 Profusion® Carrier Tray

The processor mezzanine boards plug into the Profusion carrier tray. The Profusion carrier tray serves as a platform to provide power and signals to the processor mezzanine board, route signals through the 1008-pin grand connector, and carry components of the Profusion chip set. Components of the Profusion chip set that reside on the Profusion carrier are the memory access controller (MAC) and the data interface buffer (DIB).

The Profusion chip set allows a five-port system data bus, with concurrent switching taking place. This is a requirement for an efficient eight-way server. The Profusion chip set will support two processor buses (each bus containing between one and four processors), two memory buses, and a single I/O bus. All of the buses operate at 100 MHz for maximum throughput. The data is routed through the Profusion tray, into the midplane connector for distribution to the appropriate source (memory carriers or the I/O carrier).

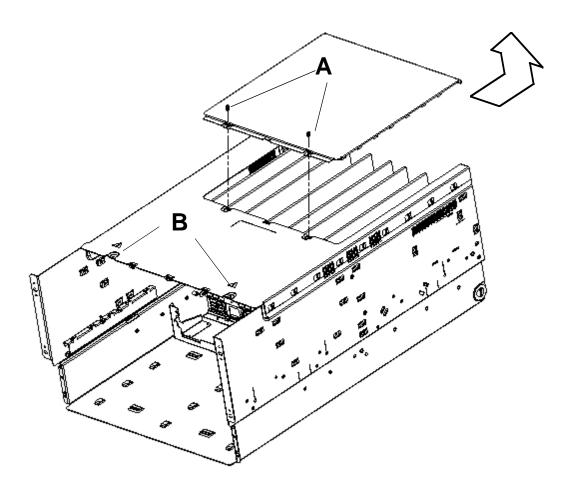

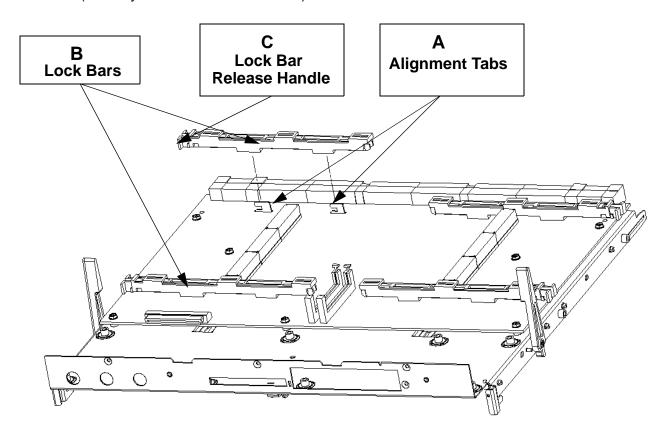

Figure 2-8: Profusion® Carrier Tray

Assembly of the Profusion carrier board, and mezzanine boards to the Profusion carrier tray, is performed outside the chassis. To start the assembly, install the Profusion carrier to the Profusion tray by aligning the eight tabs on the tray with the slots on the board (See Figure 2-8 (A)). Next, install the FPC board by passing the FPC switches through the switch openings in the tray and

then moving back into place for connection to the Profusion carrier board. Place the four lock bars over the protruding tabs and onto the Profusion carrier board (B). The release handles of the lock bars (C) should be pointed to the outside of the board and they should be in the unlocked position. Place the first mezzanine board on the left side of the Profusion carrier board, oriented so the mezzanine board does not extend over the 1008-pin grand connector on the Profusion carrier board. Press down in the center of the mezzanine board until it is seated down onto the lock bars. If the configuration calls for a second mezzanine board, install it on the right side of the Profusion carrier board by following the same steps as described for the first board.

Figure 2-9: Profusion® Carrier Tray

Lower the processor retention mechanism onto the mezzanine board(s), aligning the hooks on its bottom with the slots in the mezzanine board(s). The processor retention mechanism should be oriented such that the center notch for the coherency filters is facing forward. Engage the four lock bars by pushing in on their ends until they click. The Profusion carrier tray assembly is now ready for installation in the chassis.

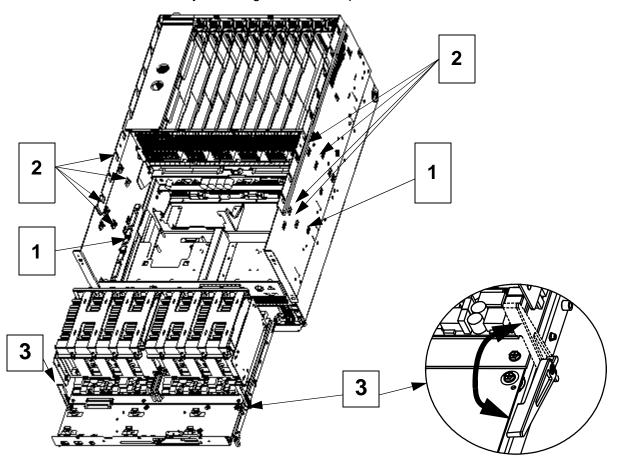

To install the Profusion carrier tray assembly into the chassis, set the tray on the tray supports on the inside walls of the chassis and slide it towared the midplane. The tray and chassis have self-aligning features to help guide the tray as it approaches the grand connector on the midplane. When the connectors are within approximately 1" from connecting, check under the Profusion carrier tray for proper engagement of the center supports. The insertion/extraction levers (3) on the side of the tray should be tilted forward as the connectors approach each other. As the con-

nectors begin to engage, rotate the levers back until the connectors are fully engaged. Levers should be in an upright or near upright position. Secure the tray and the processor retention mechanism to the sides of the chassis with screws (1) and (2) as indicated in Figure 2-9.

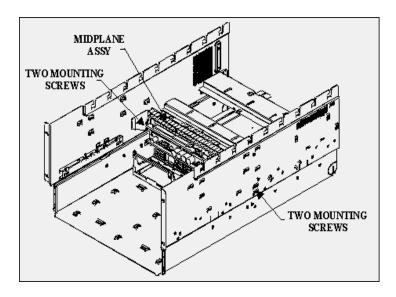

# 2.9 Midplane Assembly

The midplane assembly serves as an interconnect between the power supplies, memory boards, Profusion carrier, and the I/O carrier. With the exception of limited server management and field replaceable unit (FRU) components, the midplane assembly serves merely as an interconnection device, routing the signals between the boards, while maintaining the signal integrity required for the 100-MHz buses.

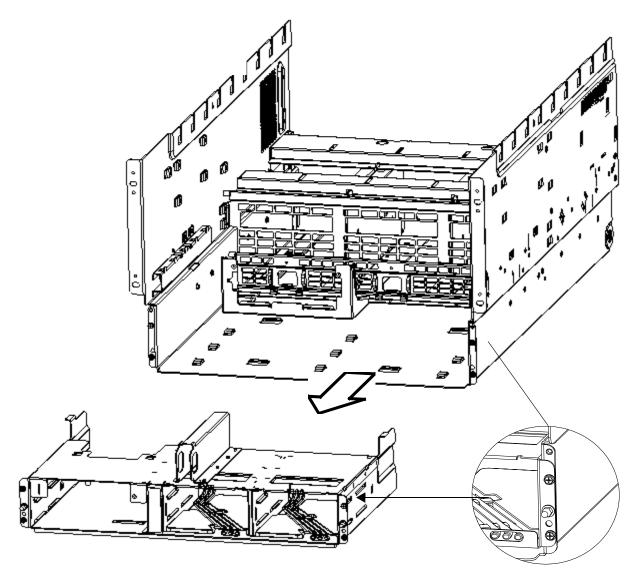

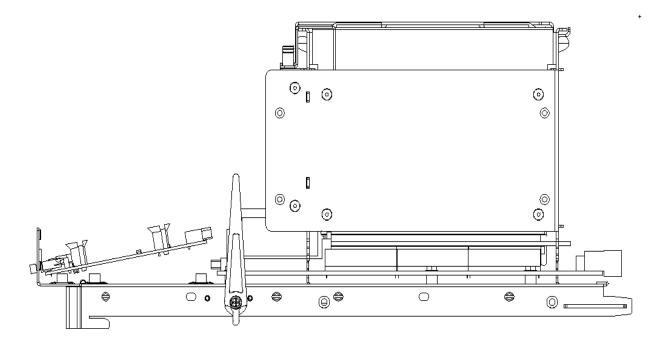

Figure 2-10: Midplane Assembly

The midplane assembly is installed into the OCPRF100 MP server system chassis by rotating the assembly about two alignment structures. The assembly is secured by a total of four screws, two screws are located on each side of the system. All four screws must be removed to extract the midplane assembly. The tab on the midplane assembly is used to manage the cables between the I/O baseboard and the peripheral blind-mate board.

Figure 2-11: Midplane Assembly Installed in System

# 2.10 I/O Carrier

The I/O carrier is the interface that connects the I/O port of the Profusion chip set to the following:

- Ten hot-swappable PCI slots (four of which support 66-MHz transactions).

- Legacy connector (video, keyboard, serial, parallel, USB, and Intelligent Chassis Management Bus (ICMB) ports).

- Dual LVDS.

- Internal IDE buses, floppy disk, disk drives, and SCSI connectors for peripheral support.

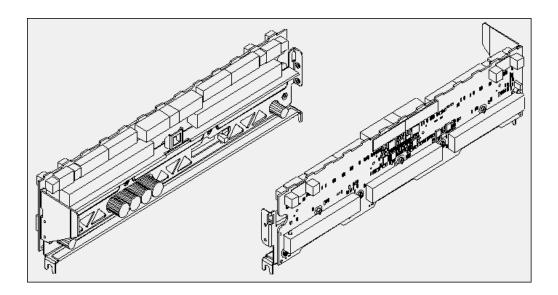

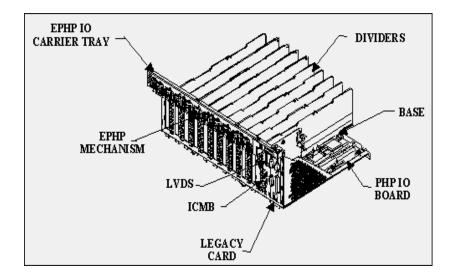

The PCI hot-plug (PHP) I/O carrier, legacy connector, LVDS connectors, ICMB board, and enhanced PCI hot-plug board are assembled onto the I/O carrier tray. The PCI hot-plug base shield is assembled and mounted over the PHP I/O board, and secured by six screws. The PHP slot dividers snap onto the PHP base shield.

Figure 2-12: I/O Carrier Tray

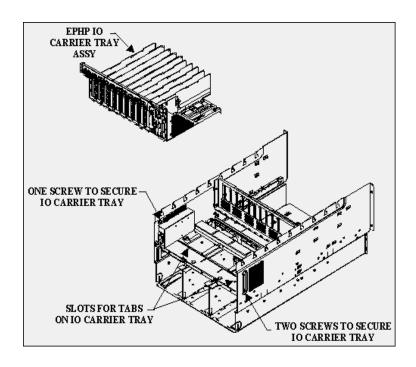

The I/O carrier tray features tabs on the base of the tray that engage into slots on the horizontal members in the chassis. Lower the tray from the top of the system and slide the tray toward the center of the chassis using the two insert/extract handles located on the back of the tray. Secure the I/O carrier tray to the chassis with the four screws located on the sides and back of the chassis.

Figure 2-13: Installing the I/O Carrier Tray

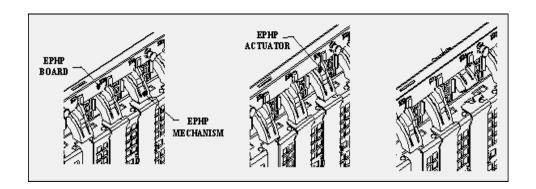

The PHP mechanism is a rotating part that actuates a switch located on the PHP board. There are four light emitting diodes (LEDs) per slot--two can be viewed from the rear of the system and two from inside the system. Once the LED shows which slot is powered down, the PHP mechanism can be depressed on the PHP actuator and the mechanism can be rotated out of place to remove the PCI card. Once the new PCI card is installed, rotate the PHP mechanism back into place to activate the switch and secure the PCI card.

Figure 2-14: PHP Mechanism

# 2.11 Power Supply

The OCPRF100 MP server system power supply operates at 208 - 220 Vac, or 100 - 115 Vac is rated at 750 watts, and is designed to be hot-swappable, with a 2+1 redundancy factor. Each power supply has indicators showing correct operation, failure, and predictive failure. A power supply displaying the predictive failure LED still will operate corectly, but needs to be sent out for repair as quickly as possible. The predictive failure feature is designed to warn the operator of an impending power supply failure.

# 2.12 OCPRF100 MP Server System Chassis

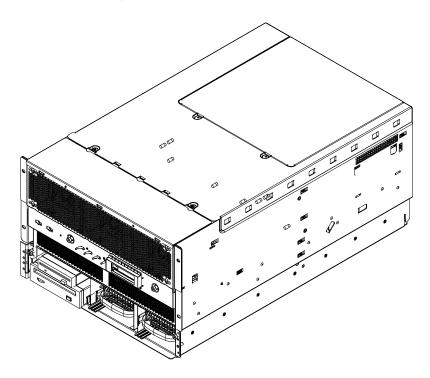

The system chassis is the rack-mount chassis used in the system. The system chassis is designed to house all of the components listed above within a 7Ux 32" (+/-) deep space, and mount in a 19-inch rack. The chassis itself is 28" deep with the extra 4" to account for cable management. The chassis was engineered to provide easy access to perform maintenance, upgrades, add memory, and add or remove PCI cards.

The functional server weighs between 120 and 140 pounds, depending on internal configurations. The chassis is designed to provide adequate thermal cooling of all devices within an ambient temperature of 10° to 40°C, while maintaining noise levels below 57 dB. If the ambient temperature exceeds 30°C, the fans in the fan bay will switch to high speed, cooling the system to operational values. Server management will log that a thermal excursion has occurred. Several internal heat sensors will monitor the temperature at key points inside the server. Should any of these sensors indicate that the temperature has exceeded a critical thermal set-point, server management will log the event, and the server will be shut down gracefully, according to user setup.

# **System Overview**

This chapter describes the features of the OCPRF100 MP server system chassis.

### **System Features**

Table 3-1 provides a list and brief description of the features of the OCPRF100 MP server system, which utilizes the OPRF100 board set.

Table 3-1: OCPRF100 MP Server System Feature List

| Feature                                                     | Description                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Upgradeability                                              | The system can be upgraded to future processors within the Pentium <sup>®</sup> III Xeon™ processor family.                                                                                                                                                                      |

| PCI hot plug                                                | The chassis with the OPRF100 board set supports 10 64-bit PCI hot-plug slots (four at 66 MHz, six at 33 MHz).                                                                                                                                                                    |

| Compact, high-density system                                | The system size is a 7U (12.25-inch) rack-mount server.                                                                                                                                                                                                                          |

| Redundant power                                             | The system supports three 750-W power supplies in a redundant (2 + 1) configuration.                                                                                                                                                                                             |

| Redundant cooling                                           | Six system fans in a redundant (5+1) configuration cool the upper system (CPU and I/O). Three internal power supply fans cool the lower system (memory, peripheral bay, and power supplies) in a redundant configuration when the power supply configuration is redundant (2+1). |

| Modular peripheral bay                                      | The peripheral bay supports one floppy disk drive, one 5.25-inch half-height device, and two 3.5-inch by 1.0- or 1.6-inch hot-swappable LVDS SCSI hard drives.                                                                                                                   |

| Front panel liquid crystal display (LCD)                    | A two line LCD provides the system status.                                                                                                                                                                                                                                       |

| Intelligent Management Platform Initiative (IPMI) compliant | Intelligent Platform Management Bus (IPMB) for intrachassis communication is provided. Emergency management port (EMP) is used for remote management.                                                                                                                            |

#### 3.1 Introduction

The scalable architecture of the OCPRF100 MP server system supports symmetrical multiprocessing (SMP) and a variety of operating systems (OS). The server provides 10 PCI card slots.

The Profusion carrier contains connectors for installing up to eight Pentium III Xeon processors packaged in single-edge contact cartridges (SECC). Each of the two memory carriers supports

up to 16 GB of error correction code (ECC) PC-100 compatible registered DIMMs. The I/O carrier contains four 66-MHz and six 33-MHz 64-bit hot-swap PCI slots, I/O ports, and various controllers.

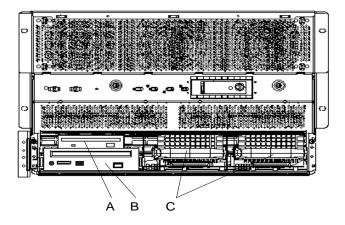

Figure 3-1: OCPRF100 MP Server System Chassis with Peripheral Bay shows an isometric view of the chassis with the peripheral bay installed.

Figure 3-1: OCPRF100 MP Server System Chassis with Peripheral Bay

Figure 3-2: OPRF100 Board Set/System Board Locations within Server Chassis displays the layout of the OPRF100 board set with respect to location within the chassis. The Profusion carrier and I/O carrier are mounted horizontally, with the Profusion carrier toward the front of the chassis and the I/O carrier immediately behind at the rear of the chassis. The midplane distributes power and signal connections to all boards. The midplane resides between the Profusion carrier and the I/O carrier, and interconnects these carriers with the memory carriers and system power supplies. The front panel resides in front of the Profusion carrier in the same plane and provides the user interface, system management, and cooling system power and control.

Figure 3-2: OPRF100 Board Set/System Board Locations within Server Chassis

The peripheral bay mounted at the lower front of the chassis supports a 3.5-inch floppy drive, a half-height 5.25-inch device (e.g., CD-ROM) and two 3.5-inch by 1.0- or 1.6-inch hot-swap hard drives. SCSI drives in the hot-swap hard drive bays can be hot-swapped without shutting down the server.

The chassis supports up to three hot-swap, redundant power supplies in a 2+1 configuration. These supplies provide redundant and hot-swappable cooling to the memory carriers and peripherals when the power supplies are in a redundant configuration. A cover plate for the unoccupied power supply location is supplied for systems without redundancy, and should be used to provide adequate cooling and EMI shielding.

The system design provides a hot-swap, redundant (5+1) cooling system for the Profusion and I/ O carriers. Basic controls and indicators are located on the front panel.

The front bezel can be customized for integrators to meet their industrial design requirements. The front bezel contains openings to provide adequate cooling for the chassis components and access to the peripherals.

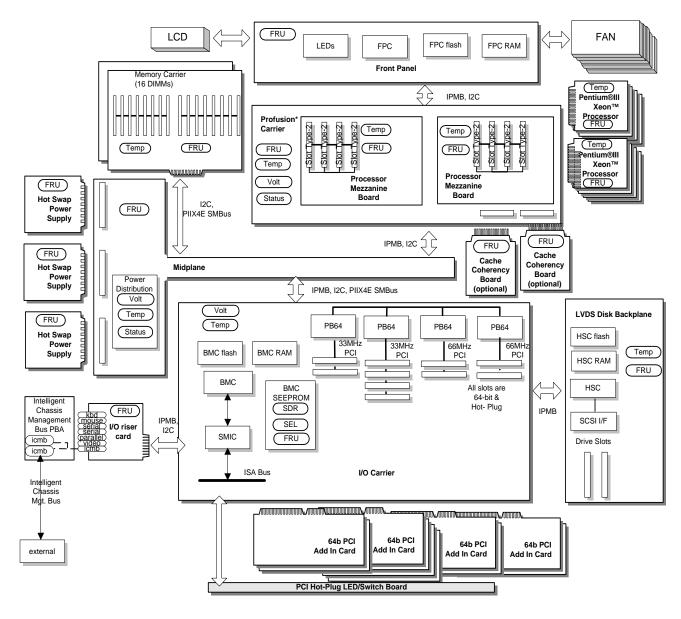

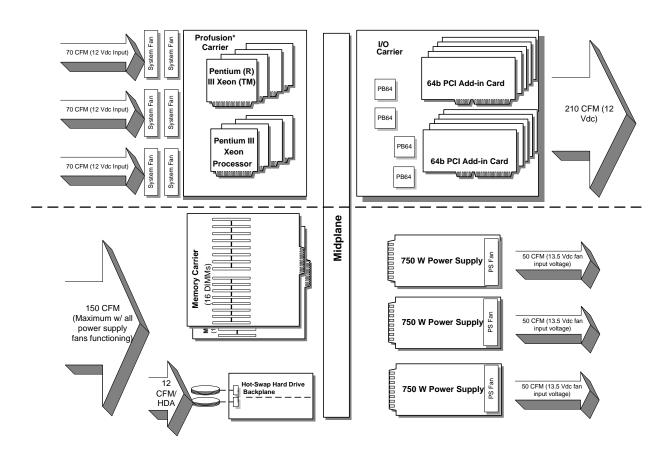

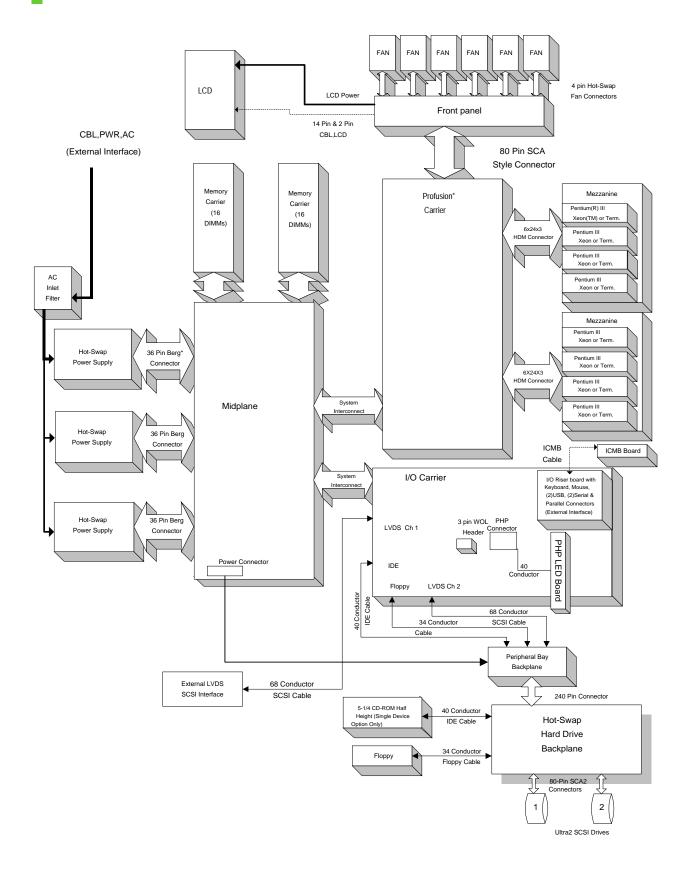

Figure 3-3: OCPRF100 MP Server System Chassis Block Diagram shows a block diagram of the server system.

Figure 3-3: OCPRF100 MP Server System Chassis Block Diagram

# 3.2 External Chassis Features

# 3.2.1 Front View of Chassis

The front bezel of the server has two main user-accessible areas:

Front panel liquid crystal display (LCD), switches and indicators.

Replaceable media bays—floppy drive and 5.25-inch half-height bay.

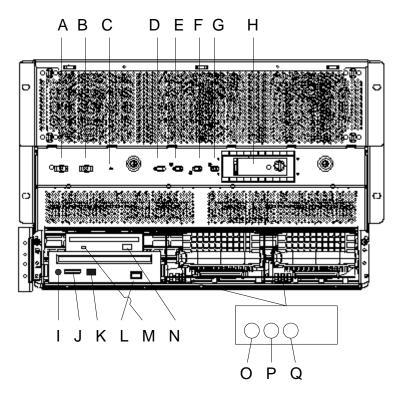

Figure 3-4: Front View of Chassis with No Bezel

# Table 3-2: System Features – Front

| Item                                | Feature                  | Description                                                                                                                                                                                                                                                                                   |

|-------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Front Panel Controls and Indicators |                          |                                                                                                                                                                                                                                                                                               |

| А                                   | Power switch             | When pressed, turns the DC power inside the server on or off.                                                                                                                                                                                                                                 |

| В                                   | Reset switch             | When pressed, resets the server and causes the power-on self-test (POST) to run.                                                                                                                                                                                                              |

| С                                   | NMI switch               | When pressed, causes a nonmaskable interrupt (NMI). This switch is recessed behind the front panel to prevent inadvertent activation. (The switch must be pressed with a narrow tool.)                                                                                                        |

| D                                   | Power (LED) (green)      | When continuously lit, indicates the presence of DC power in the server.  The light emitting diode (LED) goes out when the power is turned off or when the power source is disrupted. When flashing, indicates the system is in advanced configuration and power interface (ACPI) sleep mode. |

| Е                                   | Power fault LED (yellow) | When continuously lit, indicates a power supply failure. When flashing, indicates a 240 VA overload shutdown and power control failure.                                                                                                                                                       |

# Table 3-2: System Features – Front

| F                          | Fan fault LED (yellow)                                                                                                  | When lit, indicates either a fan failure, or that a predictive fan failure has been detected in the server.                                                                |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| G                          | Drive fault LED (yellow)                                                                                                | When continuously lit, indicates an asserted fault status on one or more hard disk drives in the hot-swap bay. When flashing, indicates drive rebuild in progress.         |  |

| Н                          | Front panel LCD                                                                                                         | Displays information about processor type and failure codes.                                                                                                               |  |

| (Items I thr<br>facturer.) | (Items I through L on are control buttons for the CD-ROM, and the location may vary from manufacturer to manufacturer.) |                                                                                                                                                                            |  |

| 3.5-inch Fl                | oppy Diskette Drive Descrip                                                                                             | otions                                                                                                                                                                     |  |

| М                          | Activity LED                                                                                                            | When lit, indicates the drive is in use.                                                                                                                                   |  |

| N                          | Ejector button                                                                                                          | When pressed, ejects the diskette.                                                                                                                                         |  |

| Status LE                  | Status LEDs for SCSI Drives in Hot-swap Bays                                                                            |                                                                                                                                                                            |  |

| 0                          | Drive power LED (green)                                                                                                 | When continuously lit, indicates the presence of the drive and that drive is powered on.                                                                                   |  |

| Р                          | Drive activity LED (green)                                                                                              | When flashing, indicates drive activity.                                                                                                                                   |  |

| Q                          | Drive fault LED (yellow)                                                                                                | When continuously lit, indicates an asserted fault status on one or more hard disk drives in the hot-swap bay. When flashing, indicates that drive rebuild is in progress. |  |

|                            |                                                                                                                         |                                                                                                                                                                            |  |

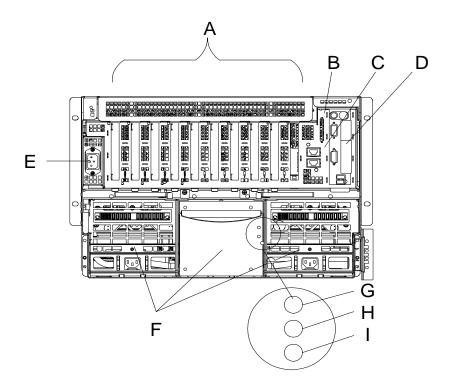

#### **Rear View of Chassis** 3.2.2

Figure 3-5: Rear View of Chassis

Table 3-3: System Features – Rear

| Item | Description               |

|------|---------------------------|

| Α    | PCI add-in board slots.   |

| В    | External LVDS connector.  |

| С    | ICMB connectors in/out.   |

| D    | I/O riser board.          |

| E    | AC input power connector. |

| F    | Three power supplies.     |

Table 3-3: System Features – Rear

| G | PWR LED (green) – power condition – refer to Chapter Power Supply for details.                        |

|---|-------------------------------------------------------------------------------------------------------|

| Н | FAIL LED (yellow) – failure condition – refer to Chapter Power Supply for details.                    |

| ı | PR_FL LED (yellow) – power supply fan predictive failure – refer to Chapter Power Supply for details. |

# 3.2.3 Riser Board External I/O Connectors

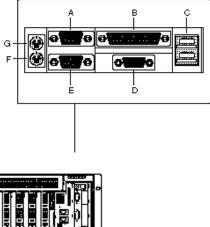

Figure 3-6: Riser Board External I/O Connectors

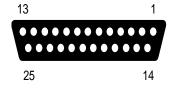

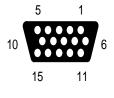

Table 3-4: Riser Board External I/O Connectors

| Item | Description                                    |

|------|------------------------------------------------|

| A.   | Serial port 1 (COM1), 9-pin RS-232 connector.  |

| В.   | Parallel port, 25-pin bidirectional connector. |

Table 3-4: Riser Board External I/O Connectors

| C. | USB ports 0 (upper) and 1 (lower).            |  |

|----|-----------------------------------------------|--|

| D. | Super VGA compatible, 15-pin video connector. |  |

| E. | Serial port 2 (COM2), 9-pin RS-232 connector. |  |

| F. | PS/2-compatible keyboard port.                |  |

| G. | PS/2-compatible mouse port.                   |  |

| H. | ICMB port, SEMCONN* 6-pin connector.          |  |

| I. | ICMB port, SEMCONN 6-pin connector.           |  |

#### 3.2.4 **Peripheral Bay**

An optional peripheral bay provides the following:

- One 3.5-inch floppy drive bay

- One 5.25-inch user-accessible drive bay for removable media

- Two 3.5-inch by 1.0- or 1.6-inch hot-swap bays for SCSI SCA hard disk drives

Figure 3-7: Chassis Drive Bays

### Table 3-5: I/O External Connectors

| Item | Bay                               | Description                             |

|------|-----------------------------------|-----------------------------------------|

| А    | 3.5-inch bay                      | 3.5-inch floppy drive.                  |

| В    | 5.25-inch half-height bay         | 5.25-inch half-height peripheral drive. |

| С    | 3.5-inch by 1.0- or 1.6-inch bays | Two hot-swap capable hard drives.       |

## 3.2.5 3.5-inch User-accessible Drive Bay

The system ships from the factory without the peripheral bay installed.

### 3.2.6 5.25-inch User-accessible Drive Bay

The system ships from the factory without the peripheral bay installed.

**Note:** Installation of hard disk drives in the 5.25-inch user-accessible bay is not recommended due to cooling and EMI constraints.

### 3.2.7 3.5-inch SCSI Hot-swap Drive Bays

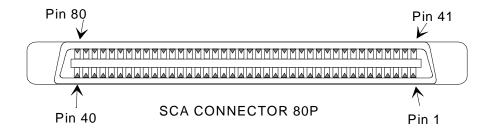

Two 3.5-inch hot-swap capable bays support either 1.0- or 1.6-inch high SCA SCSI hard disk drives. These bays are accessible following removal of the lower bezel section. The wide LVDS SCSI hot-swap backplane provides industry standard 80-pin SCA-2 connectors for two drives. Two wide/fast-20 SCSI III SCA type hard disk drives can be installed in these bays. The wide LVDS SCSI hot-swap backplane is designed to accept drives that consume up to 28 watts of power and run at a maximum ambient temperature of 50°C (112°F).

Extruded aluminum drive carriers with integral heat sinks that accommodate 3.5-inch wide by either 1.0- or 1.6-inch high drives are required as part of the hot-swap implementation. The carrier is attached to the drive with four fasteners, and is retained in the chassis by a locking handle.

The LEDs below each drive display individual drive status. There are three LEDs for each drive: a power on (green) LED; an activity (green) LED; and a fault (yellow) LED. A fault LED on the front panel board also indicates a fault on these drives.

**Note:** Because all hard drives have different cooling, power and vibration characteristics, Intel will not validate hard drive types in the system chassis. Refer to the *OCPRF100 MP Server System Validation Summary* document for a list of these drives.

#### 3.3 **Internal Chassis Features**

#### 3.3.1 **Power System**

Three 750-W supplies in a standard configuration provide the modular power system for the system. The power system may be configured with three power supplies (2+1) for power redundancy, or with two supplies in a nonredundant configuration. The power supplies are mounted in a row at the rear bottom of the chassis. A single AC power cord provides power to the daisychained supplies.

When the server is configured with three power supplies, the user can hot swap a failed supply without affecting system functionality.

The midplane provides power distribution of the internal power system with minimal active circuitry. The power distribution circuitry reports quantity and location of the installed power supplies through I<sup>2</sup>C\* server management.

Two 750-W, 208-Vac supplies are capable of handling power requirements for the OPRF100 board set and peripherals. For the OPRF100 board set, this includes eight Pentium III Xeon processors, 32 GB of memory and two 1.6-inch hard drives.

The Profusion carrier provides headers for two processor mezzanine boards, each providing four slots for Pentium III Xeon processors. Each mezzanine board has six integrated VRM 8.3 compatible voltage converters. The converter input is +12 Vdc from the power supply. Each Pentium III Xeon processor core has its own converter. One converter provides power for a pair of Pentium III Xeon processor L2 caches.

The total power requirement for the OPRF100 board set exceeds the 240 VA energy hazard limit that defines an operator accessible area. As a result, only qualified technical individuals should access the processor, memory, and non-hot-plug I/O carrier areas while the system is energized.

Refer to Chapter Power Supply Power Supply of this document for detailed power specifications.

| Table 3-6: System Power Budget – Current (A) and Power (W) |       |        |      |       |       |           |       |  |  |  |

|------------------------------------------------------------|-------|--------|------|-------|-------|-----------|-------|--|--|--|

| OCPRF100 MP Server<br>System Power Budget                  | Units | +3.3 V | +5 V | +12 V | -12 V | +5<br>VSB | Power |  |  |  |

| Board       | Spec           | Units | +3.3 V | +5 V  | +12 V | -12 V | +5<br>VSB | Power  |

|-------------|----------------|-------|--------|-------|-------|-------|-----------|--------|

| I/O Carrier | Min. Load      | Adc   | 0.20   | 0.70  | 0.00  | 0.20  | 0.65      | 9.81   |

|             | Max. Load      | Adc   | 7.99   | 45.20 | 5.00  | 1.20  | 0.75      | 330.52 |

|             | Max. Step Load | Adc   | 2.00   | 12.17 | 4.50  | 0.25  | 0.10      |        |

Table 3-6: System Power Budget – Current (A) and Power (W)

|                          |                |      | uugu  | 0 0111 0110 (111, | ,      | . ()  |      |        |

|--------------------------|----------------|------|-------|-------------------|--------|-------|------|--------|

|                          |                |      |       |                   |        |       |      |        |

| Profusion®               | Min. Load      | Adc  | 4.60  | 0.75              | 0.25   | 0.000 | 0.00 | 21.93  |

| Carrier w/               | Max. Load      | Adc  | 12.00 | 1.50              | 46.00  | 0.000 | 0.00 | 599.10 |

| Mezzanines               | Max. Step Load | Adc  | 2.00  | 0.75              | 18.00  |       |      |        |

|                          |                |      |       |                   |        |       |      |        |

| Front Panel              | Min. Load      | Adc  | 0.00  | 0.05              | 2.00   | 0.001 | 0.10 | 24.76  |

|                          | Max. Load      | Adc  | 0.00  | 0.23              | 5.40   | 0.010 | 0.25 | 67.32  |

| Plugs into               | Max. Step Load | Adc  |       | 0.18              | 0.10   | 0.001 | 0.15 |        |

| <b>Profusion Carrier</b> |                |      |       |                   |        |       |      |        |

|                          |                |      |       |                   |        |       |      |        |

| Memory Carrier 1         | Min. Load      | Adc  | 1.20  | 0.00              | 0.00   | 0.000 | 0.00 | 3.96   |

|                          | Max. Load      | Adc  | 23.00 | 0.00              | 0.00   | 0.000 | 0.00 | 75.90  |

|                          | Max. Step Load | Adc  | 8.00  |                   |        |       |      |        |

|                          |                |      |       |                   |        |       |      |        |

| Memory Carrier 2         | Min. Load      | Adc  | 0.00  | 0.00              | 0.00   | 0.000 | 0.00 | 0.00   |

| (Note: 2)                | Max. Load      | Adc  | 23.00 | 0.00              | 0.00   | 0.000 | 0.00 | 75.90  |

|                          | Max. Step Load | Adc  | 8.00  |                   |        |       |      |        |

|                          |                |      |       |                   |        |       |      |        |

| Peripherals              | Min. Load      | Adc  | 0.00  | 0.70              | 0.25   | 0.000 | 0.00 | 6.50   |

| (SCSI Backplane)         | Max. Load      | Adc  | 0.00  | 4.50              | 5.99   | 0.000 | 0.00 | 94.38  |

|                          | Max. Step Load | Adc  |       | 0.90              | 5.40   |       |      |        |

|                          |                |      |       |                   |        |       |      |        |

| Midplane                 | Min. Load      | Adc  |       |                   |        |       |      |        |

|                          | Max. Load      | Adc  | 0.01  | 0.01              | 0.01   |       |      | 0.20   |

|                          |                |      |       |                   |        |       |      |        |

| Total min. load          |                | Adc  | 6.00  | 2.20              | 2.50   | 0.20  | 0.75 | 66.96  |

| Total max. step load     |                | Adc  | 20.00 | 14.00             | 28.00  | 0.25  | 0.25 |        |

| Max. step di/dt          |                | A/uS | 0.50  | 1.00              | 0.60   | 0.10  | 0.10 |        |

| Total max.<br>load       |                | Adc  | 66.00 | 51.44             | 62.40  | 1.21  | 1.00 |        |

| Total load power:        | 1243.32        | W    | 217.8 | 257.2             | 748.80 | 14.52 | 5    | 1243.3 |

### Table 3-6: System Power Budget – Current (A) and Power (W)

|  | Total power (includes 2% distribution loss) | 1268.1 |

|--|---------------------------------------------|--------|

|  |                                             | 9      |

Notes:

- 1. There is no 240 VA protection circuit in the OCPRF100 MP server system.

- 2. Minimum load for second memory carrier is zero; assumes no carrier is installed.

### 3.3.2 Cooling System

### 3.3.2.1 Description

There are two independent cooling subsystems:

The upper system, encompassing the front panel, Profusion carrier, and I/O carrier.

The lower systems, encompassing the memory carriers, peripheral bay, and power supplies.

Air flows in through the bezel and exhausts out the rear of the chassis.

Cooling system redundancy to the upper system is provided by the 5+1 redundant fans at the front top of the system. All systems come with redundant cooling for the upper area in standard factory configuration with six upper system fans. Each fan provides tachometer signal output to the front panel to indicate a fan failure. There may be time limit restrictions on the service time for fan and PCI hot-plug card replacement.

Cooling system redundancy of the lower system is provided by the 2+1 system power supplies. Each power supply fan provides tachometer signal output. A power supply fan failure is indicated at the front panel as a predictive power supply failure. There may be time restrictions on the service time for power supply hot swap replacement.

### 3.3.2.2 Redundancy and Ambient Temperature Control

### 3.3.2.2.1 System Fans

The front panel provides either of two fan input voltages to the system fans. Under normal ambient room conditions (less than 30°C), the front panel supplies 8.4 Vdc to the system fans. When a system fan fails or when the room ambient temperature exceeds 30°C, the fan input voltage is increased to 12 Vdc. Following a room temperature excursion above 30°C, the fan voltage does not change back to 8.4 Vdc until the room temperature drops below 28°C and all system fans are operational.

### 3.3.2.2.2 Power Supply Fans

The power supply fans are controlled independently by each supply. The ambient temperature sensed at the inlet to each supply is used as the input to a control circuit, which continuously var-

ies the fan input voltage. At 28°C ambient temperature, the fan input voltage is  $8.0 \pm 0.5$  Vdc, and at 35°C, the fan input voltage is 13.5 Vdc.

## 3.3.2.3 Cooling Summary

The system fans are sized to provide cooling for up to eight Pentium III Xeon processors. The power supply fans are sized to cool both fully populated SDRAM board sets, two hot-swap hard drives, and for maintaining power supply function under a full load condition. The cooling system is designed using a worst case analysis with no margin under a single fan failure (system or power supply fan) condition. The environmental conditions are summarized in Section Specifications. Figure 3-8: OCPRF100 MP Server System Cooling summarizes the cooling provided to the system components when system and power supply fans are operating with 12 Vdc input. The lower fan speed settings were chosen to meet acoustic and thermal requirements.

Figure 3-8: OCPRF100 MP Server System Cooling

#### 3.3.3 **PCI Hot-plug**

#### 3.3.3.1 **Description**

PCI hot plug (PHP) is the concept of removing or inserting a standard PCI adapter card from a system without stopping the software or powering down the system as a whole.

"Hot Replace" means the user can replace a PCI card with an identical card. The replacement card will use the same PCI resources assigned to the previous card. OS support is required for this function.

"Hot Add" means the user can add a PCI card to a previously unoccupied slot. The system BIOS needs to reserve PCI resource space for the added adapter card upon boot.

"Hot Upgrade" means to replace an existing adapter card with a new version of the card and/or driver. A hot upgrade is not actually a unique operation. It is implemented as a hot removal followed by a hot addition.

#### 3.3.3.2 **Hardware Components**

Intel has licensed the hardware technology and methods for the implementation of PHP, which conform to the *PCI Hot-plug Specification*. The basic components are:

- Power cycling and reset generation hardware that complies with the PCI Local Bus Specification, Rev. 2.1.

- Bus isolation switches to physically disconnect the PHP capable card from the PCI bus (these switches are located on the I/O carrier between each PHP PCI card).

- Indicators (LEDs), located on the PHP LED/switch board, provide service personnel with positive slot identification (these LEDs are visible when viewed from above the I/O carrier, and can be seen from the rear of the system through holes in the chassis).

- Electromechanical hardware to prevent accidental insertion/removal from a live slot (a PHP switch is provided for each slot; when disengaged this switch immediately removes power from that slot. Normal slot power down should be through the control utility

- Protection hardware to isolate the live components of the system from the card being inserted/removed (a mechanical barrier prevents access to the I/O carrier and Profusion carrier components, and is present between PCI cards; each PHP PCI connector is limited to 240 VA).

- A controller element which controls the above hardware and provides an interface for system software.

#### 3.3.3.3 **Software Components**

The main software components for a PHP system are:

### **Hot-plug User Interface**

Provides user with access to the hot-plug control panel

- Receives user input and sends requests to the service layer

- · Displays the status of the PCI slot

- Provides user with access to PHP functions that may be available through multiple interfaces

## **Hot-plug Service**

- Provides communication between the user interface and the hot-plug controller driver and is responsible for configuring, loading, and unloading the adapter driver component

- Puts the system into a quiescent state through the hot-plug adapter card by making standard system calls

- Provides communication to the hot-plug controller

- Reports status to the hot-plug user interface

## **Hot-plug Driver**

- Communicates a hot-plug request from the system's service layer

- Provides a software bridge to the PCI hot-plug hardware

- Drives the hot-plug controller

### **BIOS**

- Supplies initialization of the hot-plug hardware components

- Provides DIMM ID monitoring and presence detection

- Provides Advanced Configuration and Power Interface (ACPI) table generation

### **Adapter Drivers**

- For Windows NT\* 4.0, changes need to be made to standard miniport drivers.

- For SCO\* UnixWare\* Version 7.01, the driver must be DDI-8 compliant.

- For Novell\* NetWare\* Version 5.0, the driver must comply with the NWPA 2.32 or ODI 3.31 specifications.

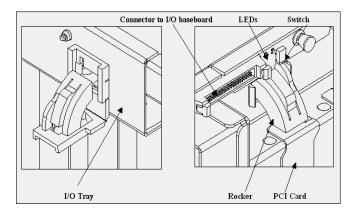

### 3.3.3.4 PCI Hot Plug Mechanical Implementation

- . The mechanical retention solution includes the following items:

- LED PC board

- Cable between LED board and the I/O carrier baseboard

- Rocker mechanism

- Plastic card guide/retention mechanism to secure the rear of each installed PCI card

A 240 VA protective shield on the I/O baseboard and the plastic dividers between PCI slots

The LED PC board contains both the green and amber LEDs, as well as the switch that controls the PCI slot power. These items will no longer reside on the I/O carrier baseboard. This LED board is mounted in the I/O tray directly above where the PCI cards were previously screwed into the tray ledge. The LEDs can be seen from both inside and outside of the chassis. Each switch hangs down off of the LED board so that it can be activated by the rocker mechanism as it is folded into the chassis. See Figure 3-9: Rocker Mechanism.

Figure 3-9: Rocker Mechanism

The rocker mechanism activates the slot power switch as it enters the I/O tray. The rocker can be released only from within the chassis. This is to prevent unintentional power down of PCI slots when the system is powered up and the chassis has not yet been pulled out of the rack. The rocker also acts as a retention mechanism for the PCI card. An additional retention mechanism at the back edge of the PCI card is currently being developed.

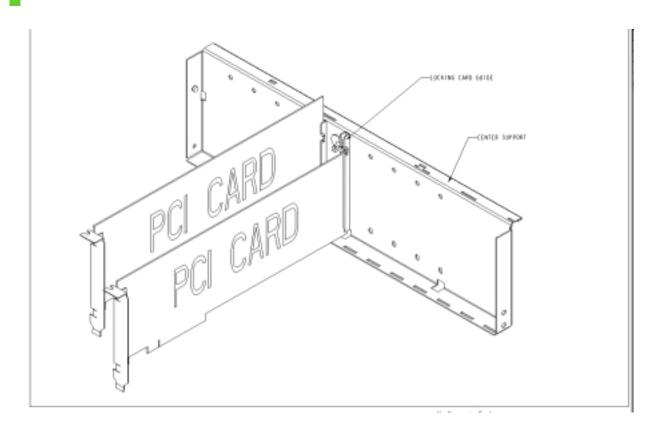

The opposite end of the PCI card is held in place by a plastic, snap-in, locking card guide. The guide, installed on the center support bracket, has a built in retention mechanism that secures the top-rear edge of the PCI card. (See Figure 3-10.)

Figure 3-10: PCI Card Retention Mechanism

Revised non-hot plug, hot plug, and top covers are required to accommodate the additional hardware used in this enhanced solution.

# 3.4 Server Management

The server system management architecture features several management controllers, which autonomously monitor server status and provide the interface to server management control functions. The controllers communicate via an I<sup>2</sup>C-based serial bus referred to as the Intelligent Platform Management Bus (IPMB).

The functions of each controller are summarized in the following sections. The firmware of all the controllers is field upgradeable, using the Server Management Firmware Update Utility. Refer to the OCPRF100 MP Server Management External Architecture Specification for more details.

### 3.4.1 Front Panel Controller

The FPC on the OCPRF100 MP server system chassis front panel board manages the front panel operations. Since this controller is responsible for system power control, it is powered from

the +5 V standby output of the power supply. The FPC takes part in implementing the following system functions:

- Power and reset switch interfaces

- Fan failure detection

- Chassis FRU inventory

- System hard reset generation

- System power fault indication

- ICMB bridge device

- Emergency management port (EMP)

- LCD interface

### 3.4.2 **Baseboard Management Controller**

The baseboard management controller (BMC) on the OPRF100 board set I/O carrier provides server management monitoring capabilities. Associated with the BMC is a flash memory that holds the operation code and the BMC configuration defaults. The various server management functions provided by the BMC are listed below.

- Baseboard voltage monitoring

- Processor voltage monitoring

- Processor voltage ID (VID) monitoring

- Processor presence detection

- Processor internal error (IERR) and thermal trip monitoring

- Fault resilient booting (FRB)

- Processor disable control

- Watchdog timer

- Periodic system management interrupt (SMI) timer

- I<sup>2</sup>C master controller

- Private management bus interface

- System management software (SMS) and SMM IPMB message receiver

- Event message receiver

- System event log management and access

- Sensor data record (SDR) repository management and access

- Processor NMI monitoring

- Processor SMI monitoring

- Time-stamp clock

- POST code log

- Secure mode, video blank, and floppy write protect

- Front panel NMI monitoring

- Software front panel NMI generation

# 3.4.3 Hot-swap Controller

The hot-swap controller (HSC) on the LVDS SCSI hot-swap backplane is connected to other system boards via the IPMB. The HSC provides server management information through both the IPMB and the SCSI Accessed Fault-Tolerant Enclosures (SAF-TE). SAF-TE is an industry standard for communicating drive and slot status.

### The HSC:

- implements the SAF-TE command set accessed through SCSI;

- provides an IPMB path for drive presence, drive fault status, backplane temperature, and fan failure;

- controls the fault lights and drive power on the OCPRF100 MP server system chassis hot-swap backplane;

- · monitors the power distribution backplane for power supply status; and

- controls drive power on and off, facilitating hot-swapping of drives.

# 3.5 Expansion Support

Table 3-7: OCPRF100 MP Server System Expansion Support summarizes the expansion support provided by the server system.

Table 3-7: OCPRF100 MP Server System Expansion Support

| Quantity | Туре                                                                      |  |

|----------|---------------------------------------------------------------------------|--|

| 10       | 64-bit PCI hot-plug expansion bus slots                                   |  |

| 2        | Single connector attachment (SCA-2) SCSI hard disk drive bays             |  |

| 1        | 5.25-inch half-height drive bays                                          |  |

| 1        | External LVDS connector                                                   |  |

| 32       | 72-bit SDRAM PC-100 registered DIMM module sockets (16 per memory module) |  |

### **Specifications** 3.6

### **Environmental Specifications** 3.6.1

The system will be tested to the environmental specifications as indicated in Table 3-8.

Table 3-8: Environmental Specifications Summary

| Environmental Feature         | Specification                                                                                                                                                                        |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating temperature         | 10° to 35°C (50° to 95°F). See Altitude exception.                                                                                                                                   |

| Nonoperating temperature      | -40°C to 70°C (-40°F to 158°F).                                                                                                                                                      |

| Altitude                      | 0 to 3048 m (0 to 10000 ft.). Note: Maximum ambient temperature is linearly derated between 1520 m (5000 ft.) and 3050 m (10000 ft.) by 1°C per 305 m (1000 ft.).                    |

| Operating humidity            | 85%, noncondensing at 40°C (104°F).                                                                                                                                                  |

|                               | <33°C (91.4°F) wet bulb at 40°C (104°F) without peripherals.                                                                                                                         |

| Nonoperating humidity         | 95%, noncondensing at +55°C (131°F).                                                                                                                                                 |

| Safety                        | UL 1950, CSA 950, IEC 950, TUV EN60 950, NEMKO.                                                                                                                                      |

| Emissions                     | Certified to FCC Class B; tested to CISPR 22B, EN 55022, and registered with VCCI.                                                                                                   |

| Immunity                      | Verified to comply with EN 50082-2.                                                                                                                                                  |

| Electrostatic discharge (ESD) | Tested to ESD levels up to 20 kilovolts (kV) air discharge without physical damage as per the Intel <sup>®</sup> environmental test specification.                                   |

| Acoustic                      | Sound pressure: < 57 dbA at ambient temperatures. < 28°C measured at bystander positions in operating mode. Sound power: < 6.5 BA at ambient temperatures. < 28°C in operating mode. |

### **Physical Specifications** 3.6.2

Table 3-8 describes the physical specifications of the system.

## Table 3-8: Dimensions and Weight

| Specification            | Value                                                                           |

|--------------------------|---------------------------------------------------------------------------------|

| Height                   | 31.12 cm (12.25 inches, 7u)                                                     |

| Width                    | 44.45 cm (17.5 inches)                                                          |

| Depth                    | 71.12 cm (28.0 inches)                                                          |

| Weight                   | 51.4 kg (113 lbs.) minimum configuration 63 kg (140 lbs.) maximum configuration |

| Required front clearance | 10 inches (inlet airflow <35 °C / 95 °F)                                        |

| Required rear clearance  | 8 inches (no airflow restriction)                                               |

## Notes:

- 1. The system weight listed above is only an approximation and can vary depending on number of peripherals and add-in cards in the system.

- 2. The system dimensions exclude the power supply handles for depth.

### **Cables and Connectors** 4.

This chapter describes cables and connectors that interconnect various components of the OCPRF100 MP server system.

The block diagram in Figure 4-1: OCPRF100 Server System Interconnect Diagram shows cables that connect the boards used in the OCPRF100 MP server system.

Figure 4-1: OCPRF100 Server System Interconnect Diagram

### **Cables** 4.1

Table 4-1 through Table 4-3 list flat ribbon cables and wire bundles that are used in the assembly of the OCPRF100 MP server system.

Table 4-1: Flat Ribbon Cables

| Quantity | Number of Pins | Туре                                                     | Path                                                                                                                                                                         |

|----------|----------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

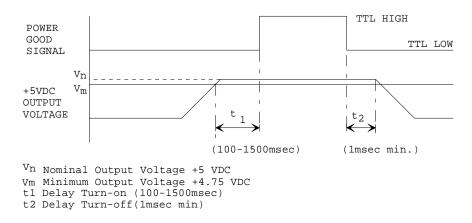

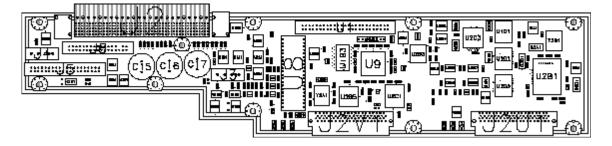

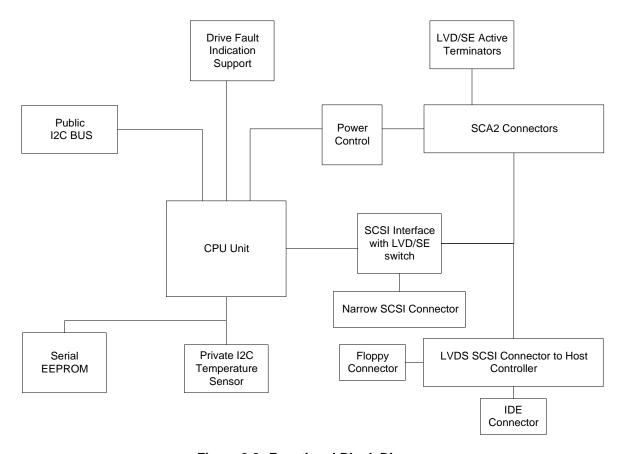

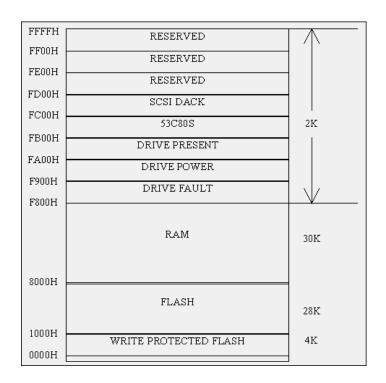

| 1        | 68             | Wide SCSI cable w/VHDCI interconnect module (solid core) | Routes from the PHP I/O carrier to a panel cut in the back of the system, where a VHDCI interconnect module can link an external VHDCI cable with the internal SCSI devices. |