# PCI/PCI-X Family of Gigabit Ethernet Controllers Software Developer's Manual

82540EP/EM, 82541xx, 82544GC/EI, 82545GM/EM, 82546GB/EB, and 82547xx

317453-005 Revision 3.8

#### Legal Notice

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This product has not been tested with every possible configuration/setting. Intel is not responsible for the product's failure in any configuration/setting, whether tested or untested.

The Intel product(s) discussed in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937 Denver, CO 80217-9808

or call in North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other Countries 708-296-9333.

Intel<sup>®</sup> is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation, 2008

# **Revision History**

| Date       | Version | Comments                                                                                                                                                                                                  |

|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2008  | 3.8     | Updated EEPROM Word 21h bit descriptions (section 5.6.18).                                                                                                                                                |

| June 2008  | 3.7     | Updated Sections 13.4.30 and 13.4.31 (added text stating to use the Interrupt Throttling Register (ITR) instead of registers RDTR and RADV for applications requiring an interrupt moderation mechanism). |

| Jan 2007   | 3.6     | Added a note to sections 13.4.20 and 13.4.21 for the 82547Gi/EI.                                                                                                                                          |

| Sept 2007  | 3.5     | Updated section 13.4.16.                                                                                                                                                                                  |

| May 2007   | 3.4     | Updated section 6.4.1. Changed acronym "WCR" to "WUC".                                                                                                                                                    |

| Dec 2006   | 3.3     | Updated Table 13-87. Changed bit 24 settings to:<br>0b = Cache line granularity.<br>1b = Descriptor granularity.                                                                                          |

| June 2006  | 3.2     | Updated Table 13.47. Changed the default setting of reserved bit 3 from 0b to 1b.                                                                                                                         |

| April 2006 | 3.1     | Added bit definitions (bits 9:8) to PHY register PSCON (16d).<br>Updated Figure 3.2 (added Receive Queue artwork).<br>Changed 81541ER-C0 to 82541ER-CO in Table 5-1.                                      |

| Nov 2005   | 3.0     | Updated Device Control/Status, EEPROM Flash Control & Data, Extended Device Control, and TCTL register bit assignments.<br>Updated PHY register 00d - 03d, 07d, 09d, 17d - 21d, and 23d bit assignments.  |

| July 2005  | 2.5     | Initial Public Release.                                                                                                                                                                                   |

*Note:* This page is intentionally left blank.

Software Developer's Manual

| 1 | Intro       | oduction  | l                                                                    | 1  |

|---|-------------|-----------|----------------------------------------------------------------------|----|

|   | 1.1         | Scope.    |                                                                      | 1  |

|   | 1.2         | Overvie   | ew                                                                   | 1  |

|   | 1.3         | Etherne   | et Controller Features                                               | 2  |

|   |             | 1.3.1     | PCI Features                                                         | 2  |

|   |             | 1.3.2     | CSA Features (82547GI/EI Only)                                       | 2  |

|   |             | 1.3.3     | Network Side Features                                                | 2  |

|   |             | 1.3.4     | Host Offloading Features                                             | 3  |

|   |             | 1.3.5     | Additional Performance Features                                      | 4  |

|   |             | 1.3.6     | Manageability Features (Not Applicable to the 82544GC/EI or 82541ER) | 5  |

|   |             | 1.3.7     | Additional Ethernet Controller Features                              | 5  |

|   |             | 1.3.8     | Technology Features                                                  | 5  |

|   | 1.4         | Conven    | itions                                                               |    |

|   |             | 1.4.1     | Register and Bit References                                          | 6  |

|   |             | 1.4.2     | Byte and Bit Designations                                            |    |

|   | 1.5         | Related   | Documents                                                            |    |

|   | 1.6         |           | y Alignment Terminology                                              |    |

| 2 | Arch        | nitectura | I Overview                                                           | 7  |

|   | 2.1         | Introduc  | ction                                                                | 7  |

|   | 2.2         |           | al Architecture                                                      |    |

|   | 2.3         |           | chitecture                                                           |    |

|   | 2.0         | 2.3.1     | PCI/PCI-X Core Interface                                             |    |

|   |             | 2.3.2     | 82547GI/EI CSA Interface                                             |    |

|   |             | 2.3.3     | DMA Engine and Data FIFO                                             |    |

|   |             | 2.3.4     | 10/100/1000 Mb/s Receive and Transmit MAC Blocks                     |    |

|   |             | 2.3.5     | MII/GMII/TBI/Internal SerDes Interface Block                         |    |

|   |             | 2.3.6     | 10/100/1000 Ethernet Transceiver (PHY)                               |    |

|   |             | 2.3.7     | EEPROM Interface                                                     |    |

|   |             | 2.3.8     | FLASH Memory Interface                                               |    |

|   | 2.4         |           | ddressing                                                            |    |

|   | 2.5         |           | et Addressing                                                        |    |

|   | 2.6         |           | ots                                                                  |    |

|   | 2.7         |           | are Acceleration Capability                                          |    |

|   | <b>_</b> ., | 2.7.1     | Checksum Offloading                                                  |    |

|   |             | 2.7.2     | TCP Segmentation                                                     |    |

|   | 2.8         |           | and Descriptor Structure                                             |    |

| 3 |             |           | I Transmit Description                                               |    |

| - |             |           | -                                                                    |    |

|   | 3.1         |           | ction                                                                |    |

|   | 3.2         |           | Reception                                                            |    |

|   |             | 3.2.1     | Packet Address Filtering                                             |    |

|   |             | 3.2.2     | Receive Data Storage                                                 |    |

|   |             | 3.2.3     | Receive Descriptor Format                                            |    |

|   |             | 3.2.4     | Receive Descriptor Fetching                                          | 25 |

|            | 3.2.5               | Receive Descriptor Write-Back                      |    |

|------------|---------------------|----------------------------------------------------|----|

|            | 3.2.6               | Receive Descriptor Queue Structure                 |    |

|            | 3.2.7               | Receive Interrupts                                 |    |

|            | 3.2.8               | 82544GC/EI Receive Interrupts                      |    |

|            | 3.2.9               | Receive Packet Checksum Offloading                 | 31 |

| 3.3        | Packet <sup>-</sup> | Transmission                                       |    |

|            | 3.3.1               | Transmit Data Storage                              |    |

|            | 3.3.2               | Transmit Descriptors                               | 35 |

|            | 3.3.3               | Legacy Transmit Descriptor Format                  |    |

|            | 3.3.4               | Transmit Descriptor Special Field Format           |    |

|            | 3.3.5               | TCP/IP Context Transmit Descriptor Format          |    |

|            | 3.3.6               | TCP/IP Context Descriptor Layout                   |    |

|            | 3.3.7               | TCP/IP Data Descriptor Format                      |    |

| 3.4        |                     | it Descriptor Ring Structure                       |    |

|            | 3.4.1               | Transmit Descriptor Fetching                       |    |

|            | 3.4.2               | Transmit Descriptor Write-back                     |    |

|            | 3.4.3               | Transmit Interrupts                                |    |

| 3.5        |                     | gmentation                                         |    |

| 0.0        | 3.5.1               | Assumptions                                        |    |

|            | 3.5.2               | Transmission Process                               |    |

|            | 3.5.3               | TCP Segmentation Performance                       |    |

|            | 3.5.4               | Packet Format                                      |    |

|            | 3.5.5               | TCP Segmentation Indication                        |    |

|            | 3.5.6               | TCP Segmentation Use of Multiple Data Descriptors  |    |

|            | 3.5.7               | IP and TCP/UDP Headers                             |    |

|            | 3.5.8               | Transmit Checksum Offloading with TCP Segmentation |    |

|            | 3.5.9               | IP/TCP/UDP Header Updating                         |    |

| 3.6        |                     | UDP Transmit Checksum Offloading                   |    |

|            |                     | -                                                  |    |

| PCI        | Local Bu            | us Interface                                       | 71 |

| 4.1        | PCI Cor             | nfiguration                                        | 71 |

|            | 4.1.1               | PCI-X Configuration Registers                      |    |

|            | 4.1.2               | Reserved and Undefined Addresses                   |    |

|            | 4.1.3               | Message Signaled Interrupts                        |    |

| 4.2        | Comma               | nds                                                |    |

| 4.3        | PCI/PCI             | I-X Command Usage                                  |    |

|            | 4.3.1               | Memory Write Operations                            |    |

|            | 4.3.2               | Memory Read Operations                             |    |

| 4.4        | Cache L             | ine Information                                    | 90 |

|            | 4.4.1               | Target Transaction Termination                     | 91 |

| 4.5        | Interrup            | t Assignment (82547GI/EI Only)                     |    |

| 4.6        |                     | sable                                              |    |

| 4.7        |                     | s Application (82541PI/GI/EI Only)                 |    |

| EEP        |                     | erface                                             |    |

| 5.1        |                     | Overview                                           |    |

| 5.1<br>5.2 |                     | nent Identification Via Programming Interface      |    |

| 5.2<br>5.3 |                     |                                                    |    |

| 5.3        |                     | M Device and Interface                             |    |

| E 4        | 5.3.1               | Software Access                                    |    |

| 5.4        | Signatu             | re and CRC Fields                                  |    |

5

4

| 5.5  | EEUPDA     | TE Utility                                                   | 97   |

|------|------------|--------------------------------------------------------------|------|

|      | 5.5.1      | Command Line Parameters                                      |      |

| 5.6  | EEPROM     | Address Map                                                  | . 98 |

|      | 5.6.1      | Ethernet Address (Words 00h-02h)                             | 103  |

|      | 5.6.2      | Software Compatibility Word (Word 03h)                       |      |

|      | 5.6.3      | SerDes Configuration (Word 04h)                              |      |

|      | 5.6.4      | EEPROM Image Version (Word 05h)                              |      |

|      | 5.6.5      | Compatibility Fields (Word 05h - 07h)                        |      |

|      | 5.6.6      | PBA Number (Word 08h, 09h)                                   |      |

|      | 5.6.7      | Initialization Control Word 1 (Word 0Ah)                     |      |

|      | 5.6.8      | Subsystem ID (Word 0Bh)                                      |      |

|      | 5.6.9      | Subsystem Vendor ID (Word 0Ch)                               |      |

|      | 5.6.10     | Device ID (Word 0Dh, 11h)                                    |      |

|      | 5.6.11     | Vendor ID (Word 0Eh)                                         |      |

|      | 5.6.12     | Initialization Control Word 2 (Word 0Fh)                     |      |

|      | 5.6.13     | PHY Register Address Data (Words 10h, 11h, and 13h - 1Eh)    |      |

|      | 5.6.14     | OEM Reserved Words (Words 10h, 11h, 13h - 1Fh)               |      |

|      | 5.6.15     | EEPROM Size (Word 12h)                                       |      |

|      | 5.6.16     | Common Power (Word 12h)                                      |      |

|      | 5.6.17     | Software Defined Pins Control (Word 10h, 20h)                |      |

|      | 5.6.18     | CSA Port Configuration 2 (Word 21h)                          |      |

|      | 5.6.19     | Circuit Control (Word 21h)                                   |      |

|      | 5.6.20     | D0 Power (Word 22h high byte)                                |      |

|      | 5.6.21     | D3 Power (Word 22h low byte)                                 |      |

|      | 5.6.22     | Reserved Words (23h - 2Eh)                                   |      |

|      | 5.6.23     | Reserved Words (23h - 2Fh)                                   |      |

|      | 5.6.24     | Management Control (Word 13h, 23h)                           |      |

|      | 5.6.25     | SMBus Slave Address (Word 14h low byte, 24h low byte)        |      |

|      | 5.6.26     | Initialization Control 3 (Word 14h high byte, 24h high byte) |      |

|      | 5.6.27     | IPv4 Address (Words 15h - 16h and 25h - 26h)                 |      |

|      | 5.6.28     | IPv6 Address (words 17h - 1Eh <sup>1</sup> and 27h - 2Eh)    |      |

|      | 5.6.29     | LED Configuration Defaults (Word 2Fh)                        |      |

|      | 5.6.30     | Boot Agent Main Setup Options (Word 30h)                     |      |

|      | 5.6.31     | Boot Agent Configuration Customization Options (Word 31h)    |      |

|      | 5.6.32     | Boot Agent Configuration Customization Options (Word 32h)    |      |

|      | 5.6.33     | IBA Capabilities (Word 33h)                                  |      |

|      | 5.6.34     | IBA Secondary Port Configuration (Words 34h-35h)             |      |

|      | 5.6.35     | Checksum Word Calculation (Word 3Fh)                         |      |

|      | 5.6.36     | 82546GB/EB Dual-Channel Fiber Wake on LAN (WOL) Mode and     |      |

|      |            | Functionality (Word 0Ah, 20h).                               | 122  |

|      | 5.6.37     | EEPROM Images                                                | 122  |

| 5.7  | Parallel F | LASH Memory                                                  | 123  |

| FLAS | H Memo     | ry Interface                                                 | 125  |

| 7.1  | FLASH In   | terface Operation                                            | 125  |

| 7.2  |            | ontrol and Accesses                                          |      |

|      | 7.2.1      | Read Accesses                                                | 126  |

|      | 7.2.2      | Write Accesses                                               | 126  |

7

| 6  | Powe                                 | r Manago                        | ement                                                  | . 129 |  |  |  |  |

|----|--------------------------------------|---------------------------------|--------------------------------------------------------|-------|--|--|--|--|

|    | 6.1 Introduction to Power Management |                                 |                                                        |       |  |  |  |  |

|    | 6.2                                  |                                 | ons                                                    |       |  |  |  |  |

|    | 6.3                                  | D3cold su                       | pport                                                  | . 130 |  |  |  |  |

|    |                                      | 6.3.1                           | Power States                                           | . 130 |  |  |  |  |

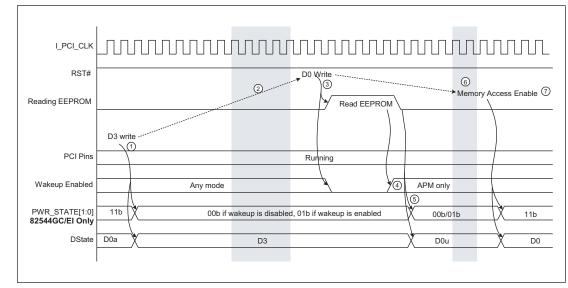

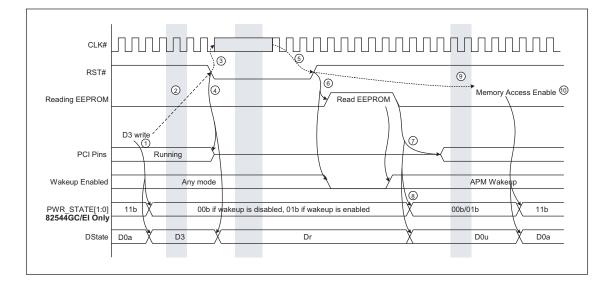

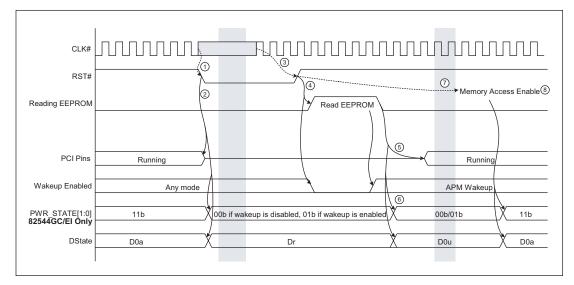

|    |                                      | 6.3.2                           | Timing                                                 |       |  |  |  |  |

|    |                                      | 6.3.3                           | PCI Power Management Registers                         |       |  |  |  |  |

|    | 6.4                                  | •                               |                                                        |       |  |  |  |  |

|    |                                      | 6.4.1                           | Advanced Power Management Wakeup                       |       |  |  |  |  |

|    |                                      | 6.4.2                           | ACPI Power Management Wakeup                           |       |  |  |  |  |

|    |                                      | 6.4.3                           | Wakeup Packets                                         | . 143 |  |  |  |  |

| 8  | Ether                                | net Inter                       | face                                                   | . 153 |  |  |  |  |

|    | 8.1                                  | Introductio                     | on                                                     | . 153 |  |  |  |  |

|    | 8.2                                  | Link Interf                     | aces Overview                                          | . 153 |  |  |  |  |

|    |                                      | 8.2.1                           | Internal SerDes Interface/TBI Mode- 1Gb/s              | .154  |  |  |  |  |

|    |                                      | 8.2.2                           | GMII – 1 Gb/s                                          |       |  |  |  |  |

|    |                                      | 8.2.3                           | MII – 10/100 Mb/s                                      |       |  |  |  |  |

|    | 8.3                                  |                                 | terface                                                |       |  |  |  |  |

|    | 8.4                                  | • •                             | peration                                               |       |  |  |  |  |

|    |                                      | 8.4.1                           | Full Duplex                                            |       |  |  |  |  |

|    |                                      | 8.4.2                           | Half Duplex                                            |       |  |  |  |  |

|    | 8.5                                  | Auto-Negotiation and Link Setup |                                                        |       |  |  |  |  |

|    | 8.6                                  | -                               | otiation and Link Setup                                |       |  |  |  |  |

|    |                                      | 8.6.1                           | Link Configuration in Internal Serdes/TBI Mode         |       |  |  |  |  |

|    |                                      | 8.6.2                           | Internal GMII/MII Mode                                 |       |  |  |  |  |

|    |                                      | 8.6.3                           | Internal SerDes Mode Control Bit Resolution            |       |  |  |  |  |

|    |                                      | 8.6.4                           | Internal PHY Mode Control Bit Resolution               |       |  |  |  |  |

|    | 07                                   | 8.6.5                           | Loss of Signal/Link Status Indication                  |       |  |  |  |  |

|    | 8.7                                  | 8.7.1                           | o/s Specific Performance Enhancements                  |       |  |  |  |  |

|    |                                      | 8.7.2                           | Adaptive IFS Flow Control                              |       |  |  |  |  |

|    |                                      | 8.7.3                           | MAC Control Frames & Reception of Flow Control Packets |       |  |  |  |  |

|    |                                      | 8.7.4                           | Discard PAUSE Frames and Pass MAC Control Frames       |       |  |  |  |  |

|    |                                      | 8.7.5                           | Transmission of PAUSE Frames                           |       |  |  |  |  |

|    |                                      | 8.7.6                           | Software Initiated PAUSE Frame Transmission            |       |  |  |  |  |

|    |                                      | 8.7.7                           | External Control of Flow Control Operation             |       |  |  |  |  |

| 9  | 802.1                                | a VI AN S                       | Support                                                |       |  |  |  |  |

| •  |                                      | -                               | AN Packet Format                                       |       |  |  |  |  |

|    | 9.1                                  | 9.1.1                           | 802.1g Tagged Frames                                   |       |  |  |  |  |

|    | 9.2                                  |                                 | ng and Receiving 802.1g Packets                        |       |  |  |  |  |

|    | 9.2                                  | 9.2.1                           | Adding 802.1q Tags on Transmits                        |       |  |  |  |  |

|    |                                      | 9.2.2                           | Stripping 802.1q Tags on Receives                      |       |  |  |  |  |

|    | 9.3                                  | • • = • =                       | AN Packet Filtering                                    |       |  |  |  |  |

| 10 |                                      |                                 | LED Outputs                                            |       |  |  |  |  |

|    |                                      | •                               | •                                                      |       |  |  |  |  |

|    | 10.1                                 |                                 | ble LED Outputs                                        |       |  |  |  |  |

|    |                                      | 10.1.1                          | Selecting an LED Output Source                         |       |  |  |  |  |

|    |                                      | 10.1.2                          | Polarity Inversion                                     | 100   |  |  |  |  |

|    |       | 10.1.3      | Blink Control                                       | 180 |

|----|-------|-------------|-----------------------------------------------------|-----|

| 11 | PHY I | Functior    | nality and Features                                 |     |

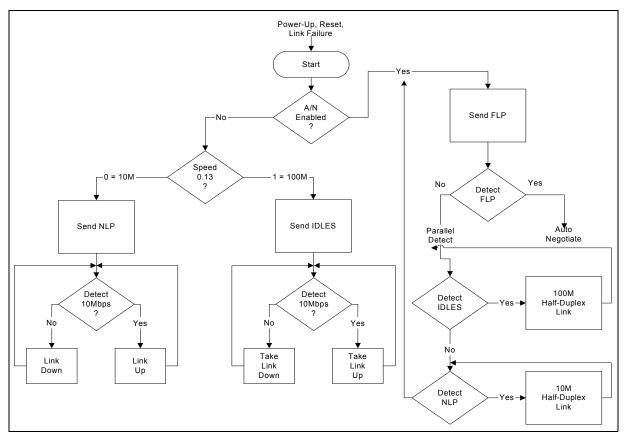

|    | 11.1  | Auto-Neg    | gotiation                                           |     |

|    |       | 11.1.1      | Overview                                            |     |

|    |       | 11.1.2      | Next Page Exchanges                                 |     |

|    |       | 11.1.3      | Register Update                                     |     |

|    |       | 11.1.4      | Status                                              |     |

|    | 11.2  | MDI/MDI     | -X Crossover (copper only)                          |     |

|    |       | 11.2.1      | Polarity Correction (copper only)                   |     |

|    |       | 11.2.2      | 10/100 Downshift (82540EP/EM Only)                  |     |

|    | 11.3  | Cable Le    | ngth Detection (copper only)                        |     |

|    | 11.4  | PHY Pov     | ver Management (copper only)                        |     |

|    |       | 11.4.1      | Link Down – Energy Detect (copper only)             | 187 |

|    |       | 11.4.2      | D3 State, No Link Required (copper only)            |     |

|    |       | 11.4.3      | D3 Link-Up, Speed-Management Enabled (copper only)  |     |

|    |       | 11.4.4      | D3 Link-Up, Speed-Management Disabled (copper only) |     |

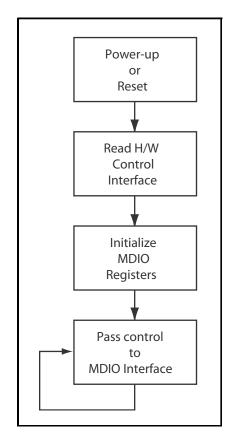

|    | 11.5  | Initializat | ion                                                 |     |

|    |       | 11.5.1      | MDIO Control Mode                                   | 189 |

|    | 11.6  | Determin    | ing Link State                                      | 190 |

|    |       | 11.6.1      | False Link                                          |     |

|    |       | 11.6.2      | Forced Operation                                    | 191 |

|    |       | 11.6.3      | Auto Negotiation                                    |     |

|    |       | 11.6.4      | Parallel Detection                                  | 192 |

|    | 11.7  | Link Crite  | eria                                                | -   |

|    |       | 11.7.1      | 1000BASE-T                                          |     |

|    |       | 11.7.2      | 100BASE-TX                                          |     |

|    |       | 11.7.3      | 10BASE-T                                            |     |

|    | 11.8  | Link Enh    | ancements                                           |     |

|    |       | 11.8.1      | SmartSpeed                                          |     |

|    |       | 11.8.2      | Flow Control                                        |     |

|    | 11.9  | •           | nent Data Interface                                 |     |

|    | 11.10 |             | er Operation                                        |     |

|    |       | 11.10.1     | Powerdown via the PHY Register                      |     |

|    |       | 11.10.2     | Smart Power-Down                                    |     |

|    | 11.11 |             | ps Operation                                        |     |

|    |       | 11.11.1     | Introduction                                        |     |

|    |       | 11.11.2     |                                                     |     |

|    |       | 11.11.3     | Transmit FIFO                                       |     |

|    |       | 11.11.4     | Receive Functions                                   |     |

|    | 11.12 | •           | s Operation                                         |     |

|    | 11.13 | •           | Operation                                           |     |

|    |       | 11.13.1     | Link Test                                           |     |

|    |       | 11.13.2     | 10Base-T Link Failure Criteria and Override         |     |

|    |       | 11.13.3     | Jabber                                              |     |

|    |       | 11.13.4     | Polarity Correction                                 |     |

|    |       | 11.13.5     | Dribble Bits                                        |     |

|    | 11.14 | PHY Line    | e Length Indication                                 | 201 |

| 12 | Dual  | Port Cha           | aracteristics                                            | 203 |

|----|-------|--------------------|----------------------------------------------------------|-----|

|    | 12.1  | Introduct          | on                                                       |     |

|    | 12.2  |                    | of Each MAC                                              |     |

|    |       | 12.2.1             | PCI/PCI-X interface                                      |     |

|    |       | 12.2.2             | MAC Configuration Register Space                         |     |

|    |       | 12.2.3             | SDP, LED, INT# output                                    |     |

|    | 12.3  | Shared E           | EPROM                                                    |     |

|    |       | 12.3.1             | EEPROM Map                                               | 206 |

|    |       | 12.3.2             | EEPROM Arbitration                                       |     |

|    | 12.4  | Shared F           | LASH                                                     | 207 |

|    |       | 12.4.1             | FLASH Access Contention                                  | 207 |

|    | 12.5  | LAN Disa           | ıble                                                     | 208 |

|    |       | 12.5.1             | Overview                                                 | 208 |

|    |       | 12.5.2             | Values Sampled on Reset                                  | 208 |

|    |       | 12.5.3             | Multi-Function Advertisement                             |     |

|    |       | 12.5.4             | Interrupt Use                                            | 209 |

|    |       | 12.5.5             | Power Reporting                                          | 209 |

|    |       | 12.5.6             | Summary                                                  | 210 |

| 13 | Rogie | stor Doci          | criptions                                                | 211 |

| 15 | •     |                    | -                                                        |     |

|    | 13.1  |                    | on                                                       |     |

|    | 13.2  | •                  | Conventions                                              |     |

|    |       | 13.2.1             | Memory and I/O Address Decoding                          |     |

|    | 40.0  | 13.2.2             | I/O-Mapped Internal Register, Internal Memory, and Flash |     |

|    | 13.3  |                    | egister Access Split                                     |     |

|    | 13.4  |                    | gister Descriptions                                      |     |

|    |       | 13.4.1             | Device Control Register                                  |     |

|    |       | 13.4.2             | Device Status Register                                   |     |

|    |       | 13.4.3             | EEPROM/Flash Control & Data Register                     |     |

|    |       | 13.4.4             | EEPROM Read Register                                     |     |

|    |       | 13.4.5             | Flash Access                                             |     |

|    |       | 13.4.6             | Extended Device Control Register                         |     |

|    |       | 13.4.7             | MDI Control Register                                     |     |

|    |       | 13.4.8             | Flow Control Address Low                                 |     |

|    |       | 13.4.9             | Flow Control Address High                                |     |

|    |       | 13.4.10            | Flow Control Type                                        |     |

|    |       | 13.4.11<br>13.4.12 | VLAN Ether Type<br>Flow Control Transmit Timer Value     |     |

|    |       | 13.4.12            | Transmit Configuration Word Register                     |     |

|    |       | 13.4.13            | Receive Configuration Word Register                      |     |

|    |       | 13.4.14            | LED Control                                              |     |

|    |       | 13.4.15            | Packet Buffer Allocation                                 |     |

|    |       | 13.4.10            | Interrupt Cause Read Register                            |     |

|    |       | 13.4.17            | Interrupt Cause Read Register                            |     |

|    |       | 13.4.18            | Interrupt Cause Set Register                             |     |

|    |       | 13.4.19            | Interrupt Mask Set/Read Register                         |     |

|    |       | 13.4.20            | Interrupt Mask Clear Register                            |     |

|    |       | 13.4.21            | Receive Control Register                                 |     |

|    |       | 13.4.22            | Flow Control Receive Threshold Low                       |     |

|    |       | 13.4.23            | Flow Control Receive Threshold Low                       |     |

|    |       | 10. 1.27           |                                                          |     |

|      | 13.4.25    | Receive Descriptor Base Address Low        | .302  |

|------|------------|--------------------------------------------|-------|

|      | 13.4.26    | Receive Descriptor Base Address High       | .302  |

|      | 13.4.27    | Receive Descriptor Length                  | .303  |

|      | 13.4.28    | Receive Descriptor Head                    | .303  |

|      | 13.4.29    | Receive Descriptor Tail                    | .304  |

|      | 13.4.30    | Receive Delay Timer Register               |       |

|      | 13.4.31    | Receive Interrupt Absolute Delay Timer     |       |

|      | 13.4.32    | Receive Small Packet Detect Interrupt      |       |

|      | 13.4.33    | Transmit Control Register                  | .306  |

|      | 13.4.34    | Transmit IPG Register                      | .308  |

|      | 13.4.35    | Adaptive IFS Throttle - AIT                | .310  |

|      | 13.4.36    | Transmit Descriptor Base Address Low       | .311  |

|      | 13.4.37    | Transmit Descriptor Base Address High      | .312  |

|      | 13.4.38    | Transmit Descriptor Length                 | .312  |

|      | 13.4.39    | Transmit Descriptor Head                   | .313  |

|      | 13.4.40    | Transmit Descriptor Tail                   | .314  |

|      | 13.4.41    | Transmit Interrupt Delay Value             | .314  |

|      | 13.4.42    | TX DMA Control (82544GC/EI only)           | .315  |

|      | 13.4.43    | Transmit Descriptor Control                | .315  |

|      | 13.4.44    | Transmit Absolute Interrupt Delay Value    | .317  |

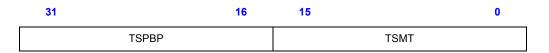

|      | 13.4.45    | TCP Segmentation Pad And Minimum Threshold | .318  |

|      | 13.4.46    | Receive Descriptor Control                 | .320  |

|      | 13.4.47    | Receive Checksum Control                   | .321  |

| 13.5 | Filter Reg | isters                                     | .323  |

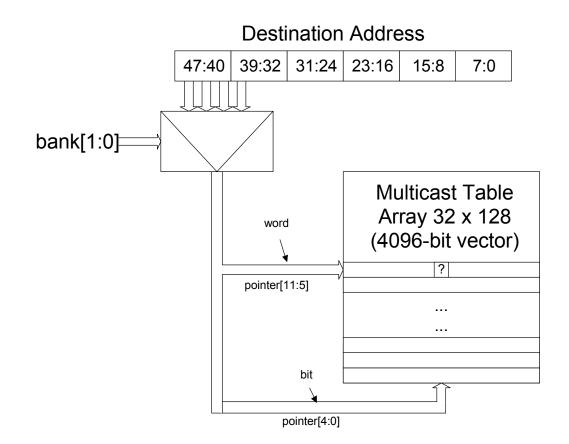

|      | 13.5.1     | Multicast Table Array                      | .323  |

|      | 13.5.2     | Receive Address Low                        | .325  |

|      | 13.5.3     | Receive Address High                       | .325  |

|      | 13.5.4     | VLAN Filter Table Array                    | .326  |

| 13.6 | Wakeup F   | Registers                                  | . 327 |

|      | 13.6.1     | Wakeup Control Register                    | .327  |

|      | 13.6.2     | Wakeup Filter Control Register             | .328  |

|      | 13.6.3     | Wakeup Status Register                     | .329  |

|      | 13.6.4     | IP Address Valid                           | .331  |

|      | 13.6.5     | IPv4 Address Table                         | .332  |

|      | 13.6.6     | IPv6 Address Table                         | .333  |

|      | 13.6.7     | Wakeup Packet Length                       |       |

|      | 13.6.8     | Wakeup Packet Memory (128 Bytes)           |       |

|      | 13.6.9     | Flexible Filter Length Table               | . 334 |

|      | 13.6.10    | Flexible Filter Mask Table                 |       |

|      | 13.6.11    | Flexible Filter Value Table                |       |

| 13.7 |            | Registers                                  |       |

|      | 13.7.1     | CRC Error Count                            |       |

|      | 13.7.2     | Alignment Error Count                      |       |

|      | 13.7.3     | Symbol Error Count                         |       |

|      | 13.7.4     | RX Error Count                             |       |

|      | 13.7.5     | Missed Packets Count                       |       |

|      | 13.7.6     | Single Collision Count                     |       |

|      | 13.7.7     | Excessive Collisions Count                 |       |

|      | 13.7.8     | Multiple Collision Count                   |       |

|      | 13.7.9     | Late Collisions Count                      | .341  |

|      | 13.7.10 | Collision Count                                   | . 341 |

|------|---------|---------------------------------------------------|-------|

|      | 13.7.11 | Defer Count                                       | . 342 |

|      | 13.7.12 | Transmit with No CRS                              | . 342 |

|      | 13.7.13 | Sequence Error Count                              | . 343 |

|      | 13.7.14 | Carrier Extension Error Count                     |       |

|      | 13.7.15 | Receive Length Error Count                        |       |

|      | 13.7.16 | XON Received Count                                |       |

|      | 13.7.17 | XON Transmitted Count                             |       |

|      | 13.7.18 | XOFF Received Count                               |       |

|      | 13.7.19 | XOFF Transmitted Count                            |       |

|      | 13.7.20 | FC Received Unsupported Count                     |       |

|      | 13.7.21 | Packets Received (64 Bytes) Count                 |       |

|      | 13.7.22 | Packets Received (65-127 Bytes) Count             |       |

|      | 13.7.23 | Packets Received (128-255 Bytes) Count            |       |

|      | 13.7.24 | Packets Received (256-511 Bytes) Count            |       |

|      | 13.7.25 | Packets Received (512-1023 Bytes) Count           |       |

|      | 13.7.26 | Packets Received (1024 to Max Bytes) Count        |       |

|      | 13.7.27 | Good Packets Received Count                       |       |

|      | 13.7.28 | Broadcast Packets Received Count                  |       |

|      | 13.7.29 | Multicast Packets Received Count                  |       |

|      | 13.7.30 | Good Packets Transmitted Count                    |       |

|      | 13.7.31 | Good Octets Received Count                        |       |

|      | 13.7.32 | Good Octets Transmitted Count                     |       |

|      | 13.7.33 | Receive No Buffers Count                          |       |

|      | 13.7.34 | Receive Undersize Count                           |       |

|      | 13.7.35 | Receive Fragment Count                            |       |

|      | 13.7.36 | Receive Oversize Count                            |       |

|      | 13.7.37 | Receive Jabber Count                              |       |

|      | 13.7.38 | Management Packets Received Count                 |       |

|      | 13.7.39 | Management Packets Dropped Count                  |       |

|      | 13.7.40 | Management Pkts Transmitted Count                 |       |

|      | 13.7.41 | Total Octets Received                             |       |

|      | 13.7.42 | Total Octets Transmitted                          |       |

|      | 13.7.43 | Total Packets Received                            |       |

|      | 13.7.44 | Total Packets Transmitted                         |       |

|      | 13.7.45 | Packets Transmitted (64 Bytes) Count              |       |

|      | 13.7.46 | Packets Transmitted (65-127 Bytes) Count          |       |

|      | 13.7.47 | Packets Transmitted (128-255 Bytes) Count         |       |

|      | 13.7.48 | Packets Transmitted (256-511 Bytes) Count         |       |

|      | 13.7.49 | Packets Transmitted (512-1023 Bytes) Count        |       |

|      | 13.7.50 | Packets Transmitted (1024 Bytes or Greater) Count |       |

|      | 13.7.51 | Multicast Packets Transmitted Count               |       |

|      | 13.7.52 | Broadcast Packets Transmitted Count               |       |

|      | 13.7.53 | TCP Segmentation Context Transmitted Count        |       |

|      | 13.7.54 | TCP Segmentation Context Transmit Fail Count      |       |

| 13.8 |         | cs Registers                                      |       |

| 10.0 | 13.8.1  | Receive Data FIFO Head Register                   |       |

|      | 13.8.2  | Receive Data FIFO Tail Register                   |       |

|      | 13.8.3  | Receive Data FIFO Head Saved Register             |       |

|      | 13.8.4  | Receive Data FIFO Tail Saved Register             |       |

|      | 10.0.4  | 1.000110 Data I II O Tali Daven 1.0913101         | . 505 |

|    |       | 13.8.5        | Receive Data FIFO Packet Count           |  |

|----|-------|---------------|------------------------------------------|--|

|    |       | 13.8.6        | Transmit Data FIFO Head Register         |  |

|    |       | 13.8.7        | Transmit Data FIFO Tail Register         |  |

|    |       | 13.8.8        | Transmit Data FIFO Head Saved Register   |  |

|    |       | 13.8.9        | Transmit Data FIFO Tail Saved Register   |  |

|    |       | 13.8.10       | Transmit Data FIFO Packet Count          |  |

|    |       | 13.8.11       | Packet Buffer Memory                     |  |

| 14 | Gene  | eral Initial  | ization and Reset Operation              |  |

|    | 14.1  | Introductio   | วท                                       |  |

|    | 14.2  | Power Up      | State                                    |  |

|    | 14.3  | General C     | Configuration                            |  |

|    | 14.4  | Receive I     | nitialization                            |  |

|    | 14.5  | Transmit      | Initialization                           |  |

|    |       | 14.5.1        | Signal Interface                         |  |

|    |       | 14.5.2        | GMII/MII Features not Supported          |  |

|    |       | 14.5.3        | Avoiding GMII Test Mode(s)               |  |

|    |       | 14.5.4        | MAC Configuration                        |  |

|    |       | 14.5.5        | Link Setup                               |  |

|    | 14.6  |               | lization (10/100/1000 Mb/s Copper Media) |  |

|    | 14.7  |               | eration                                  |  |

|    | 14.8  | Initializatio | on of Statistics                         |  |

| 15 | Diag  | nostics a     | nd Testability                           |  |

|    | 15.1  | Diagnosti     | CS                                       |  |

|    |       | 15.1.1        | FIFO State                               |  |

|    |       | 15.1.2        | FIFO Data                                |  |

|    |       | 15.1.3        | Loopback                                 |  |

|    | 15.2  | Testability   | /                                        |  |

|    |       | 15.2.1        | EXTEST Instruction                       |  |

|    |       | 15.2.2        | SAMPLE/PRELOAD Instruction               |  |

|    |       | 15.2.3        | IDCODE Instruction                       |  |

|    |       | 15.2.4        | BYPASS Instruction                       |  |

| Α  | Арре  | endix (Ch     | anges From 82544El/82544GC)              |  |

| в  | Appe  | endix (82     | 540EP/EM and 82545GM/EM Differences)     |  |

|    | 1,1,4 |               | · · · · · · · · · · · · · · · · · · ·    |  |

#### Contents

*Note:* This page intentionally left blank.

# 1.1 Scope

This document serves as a software developer's manual for **82546GB/EB**, **82545GM/EM**, **82544GC/EI**, **82541(PI/GI/EI)**, **82541ER**, **82547GI/EI**, and **82540EP/EM** Gigabit Ethernet Controllers. Throughout this manual references are made to the PCI/PCI-X Family of Gigabit Ethernet Controllers or Ethernet controllers. Unless specifically noted, these references apply to all the Ethernet controllers listed above.

## 1.2 Overview

The PCI/PCI-X Family of Gigabit Ethernet Controllers are highly integrated, high-performance Ethernet LAN devices for 1000 Mb/s, 100 Mb/s and 10 Mb/s data rates. They are optimized for LAN on Motherboard (LOM) designs, enterprise networking, and Internet appliances that use the Peripheral Component Interconnect (PCI) and PCI-X bus.

*Note:* The **82541xx** and **82540EP/EM** do not support the PCI-X bus.

The **82547GI(EI)** connects to the motherboard chipset through a Communications Streaming Architecture (CSA) port. CSA is designed for low memory latency and higher performance than a comparable PCI interface.

The remaining Ethernet controllers provide a 32-/64-bit, 33/66 MHz direct interface to the PCI Local Bus Specification (revision 2.2 or 2.3), as well as the emerging PCI-X extension to the PCI Local Bus (revision 1.0a).

The Ethernet controllers provide an interface to the host processor by using on-chip command and status registers and a shared host memory area, set up mainly during initialization. The controllers provide a highly optimized architecture to deliver high performance and PCI/CSA/PCI-X bus efficiency. By implementing hardware acceleration capabilities, the controllers enable offloading various tasks such as TCP/UDP/IP checksum calculations from the host processor. They also minimize I/O accesses and interrupts required to manage the Ethernet controllers and provide a highly configurable design that can be used effectively in various environments.

The PCI/PCI-X Family of Gigabit Ethernet Controllers handle all IEEE 802.3 receive and transmit MAC functions. They contain fully integrated physical-layer circuitry for 1000 Base-T, 100 Base-TX, and 10 Base-T applications (IEEE 802.3, 802.3u, and 802.3ab) as well as on-chip Serializer/ Deserializer (SerDes)<sup>T</sup> functionality that fully complies with IEEE 802.3z PCS.

<sup>1.</sup> The 82541xx, 82547GI/EI, and 82540EP/EM do not support any SerDes functionality.

For the **82544GC/EI**, when connected to an appropriate SerDes, it can alternatively provide an Ethernet interface for 1000 Base-SX or LX applications (IEEE 802.3z).

*Note:* The **82546EB/82545EM** is SerDes PICMG 2.16 compliant. The **82546GB/82545GM** is SerDes PICMG 3.1 compliant.

**82546GB/EB** Ethernet controllers also provide features in an integrated dual-port solution comprised of two distinct MAC/PHY instances. As a result, they appear as multi-function PCI devices containing two identically-functioning Ethernet controllers. See Section 12 for details.

# 1.3 Ethernet Controller Features

This section describes the features of the PCI/PCI-X Family of Gigabit Ethernet Controllers.

### 1.3.1 PCI Features

- 32/64-bit 33/66 MHz, PCI Rev 2.3 and PCI-X 1.0a compliant Host interface (82546GB/ 82545GM)

- 32/64-bit 33/66 MHz, PCI Rev 2.2 and PCI-X 1.0a compliant Host interface (82546EB, 82545EM, and 82544GC/EI)

- 32/64-bit 33/66 MHz, PCI Rev 2.3 compliant Host interface (82541xx)

- 32/64-bit 33/66 MHz, PCI Rev 2.2 compliant Host interface (82540EP/EM)

- 64-bit addressing for systems with more than 4 GB of physical memory

- Efficient PCI bus master operation

- · Command usage optimization for advanced PCI commands

## 1.3.2 CSA Features (82547GI/EI Only)

- Uses dedicated port for client LAN controller directly on an MCH device

- High-speed interface with twice the peak bandwidth of a 32-bit 33 MHz PCI bus

- PCI power management registers recognized by the MCH

- Interface only uses 13 signals

#### 1.3.3 Network Side Features

- Auto-Negotiation and Link Setup

- Automatic link configuration including speed, duplex and flow control under IEEE 802.3ab for copper media

- For GMII/MII mode, the driver complies with the IEEE 802.3ab standard requirements for speed, duplex, and flow control Auto-Negotiation capabilities

- Supports half and full duplex operation at 10 Mb/s and 100 Mb/s speeds while working with the internal PHY

- IEEE 802.3x compliant flow control support

- Enables control of the transmission of Pause packets through software or hardware triggering

- Provides indications of receive FIFO status

- State-of-the-art internal transceiver (PHY) with DSP architecture implementation

- Digital adaptive equalization and crosstalk

- Echo and crosstalk cancellation

- Automatic MDI/MDI-X crossover at all speeds and compensation for cable length

- Media Independent Interfaces (MII) IEEE 802.3e for supporting 10/10BASE-T transceivers

- Integrated dual-port solution comprised of two distinct MAC/PHY instances (82546GB/EB)

- Provides on-chip IEEE 802.3z PCS SerDes functionality (82546GB/EB and 82545GM/EM)

## 1.3.4 Host Offloading Features

- Receive and transmit IP and TCP/UDP checksum offloading capabilities

- Transmit TCP Segmentation (operating system support required)

- Packet filtering based on checksum errors

- Support for various address filtering modes:

- 16 exact matches (unicast, or multicast)

- 4096-bit hash filter for multicast frames

- Promiscuous, unicast and promiscuous multicast transfer modes

- IEEE 802.1q VLAN support<sup>1</sup>

- Ability to add and strip IEEE 802.1q VLAN tags

- Packet filtering based on VLAN tagging, supporting 4096 tags

- SNMP and RMON statistic counters

- Support for IPv6 including (not applicable to the **82544GC/EI**):

- IP/TCP and IP/UDP receive checksum offload

- Wake up filters

- TCP segmentation

<sup>1.</sup> Not applicable to the **82541ER**.

## 1.3.5 Additional Performance Features

- Provides adaptive Inter Frame Spacing (IFS) capability, enabling collision reduction in half duplex networks (82544GC/EI)

- Programmable host memory receive buffers (256 B to 16 KB)

- Programmable cache line size from 16 B to 128 B for efficient usage of PCI bandwidth

- Implements a total of 64 KB (40 KB for the **82547GI/EI**) of configurable receive and transmit data FIFOs. Default allocation is 48 KB for the receive data FIFO and 16 KB for the transmit data FIFO

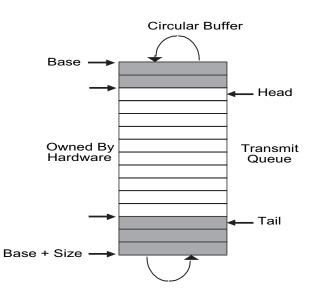

- Descriptor ring management hardware for transmit and receive. Optimized descriptor fetching and write-back mechanisms for efficient system memory and PCI bandwidth usage

- Provides interrupt coalescing to reduce the number of interrupts generated by receive and transmit operations (82544GC/EI)

- Supports reception and transmission of packets with length up to 16 KB

- New intelligent interrupt generation features to enhance driver performance (not applicable to the **82544GC/EI**):

- Packet interrupt coalescing timers (packet timers) and absolute-delay interrupt timers for both transmit and receive operation

- Short packet detection interrupt for improved response time to TCP acknowledges

- Transmit Descriptor Ring "Low" signaling

- Interrupt throttling control to limit maximum interrupt rate and improve CPU utilization

# 1.3.6 Manageability Features (Not Applicable to the 82544GC/EI or 82541ER)

- Manageability support for ASF 1.0 and AoL 2.0 by way of SMBus 2.0 interface and either:

- TCO mode SMBus-based management packet transmit / receive support

- Internal ASF-compliant TCO controller

## 1.3.7 Additional Ethernet Controller Features

- Implements ACPI<sup>1</sup> register set and power down functionality supporting D0 and D3 states

- Supports Wake on LAN (WoL)<sup>1</sup>

- Provides four wire serial EEPROM interface for loading product configuration information

- Allows use of either 3.3 V dc or 5 V dc powered EEPROM

- Provides external parallel interface for up to 512 KB of FLASH memory for support of Pre-Boot Execution Environment (PXE)

- Provides seven general purpose user mode pins

- Provides Activity and Link LED indications

- Supports little-endian byte ordering for 32- and 64-bit systems

- Provides loopback capabilities under TBI (82544GC/EI)<sup>2</sup> (internal SerDes for the 82546GB/ EB and 82545GM/EM) and GMII/MII modes of operation

- Provides IEEE JTAG boundary scan support

- Four programmable LED outputs (Not applicable to the 82544GC/EI).

- For the 82546GB/EB, four programmable LED outputs for each port

- Detection and improved power-management with LAN cable unconnected (82546GB/EB)

## 1.3.8 Technology Features

- Implemented in 0.15µ CMOS process (0.13µ for the 82541xx and 82547GI/EI)

- Packaged in 364 PBGA.

- For the **82544EI**, packaged in 416 PBGA.

- For the 82540EP/EM, 82541xx, and 82547GI/EI, packaged in 196 PBGA.

- Implemented in low power (3.3 V dc or 5 V dc compatible PCI signaling) CMOS process

<sup>1.</sup> Not applicable to the **82541ER**.

<sup>2.</sup> Not applicable to the 82541xx, 82547GI/EI or 82540EP/EM.

# 1.4 Conventions

This document uses notes that call attention to important comments:

*Note:* Indicates details about the hardware's operations that are not immediately obvious. Read these notes to get information about exceptions, unusual situations, and additional explanations of some PCI/PCI-X Family of Gigabit Ethernet Controller features.

#### 1.4.1 Register and Bit References

This document refers to Ethernet controller register names using all capital letters. To refer to a specific bit in a register the convention REGISTER.BIT is used. For example, CTRL.ASDE refers to the Auto-Speed Detection Enable bit in the Device Control Register (CTRL).

### 1.4.2 Byte and Bit Designations

This document uses "B" to abbreviate quantities of bytes. For example, a 4 KB represents 4096 bytes. Similarly, "b" is used to represent quantities of bits. For example, 100 Mb/s represents 100 Megabits per second.

## 1.5 Related Documents

- IEEE Std. 802.3, 2000 Edition. Incorporates various IEEE standards previously published separately.

- PCI Local Bus Specification, Revision 2.2 and 2.3, PCI Local Bus Special Interest Group.

## 1.6 Memory Alignment Terminology

Some PCI/PCI-X Family of Gigabit Ethernet Controller data structures have special memory alignment requirements. This implies that the starting physical address of a data structure must be aligned as specified in this manual. The following terms are used for this purpose:

- **BYTE** alignment: Implies that the physical addresses can be odd or even. Examples: 0FECBD9A1h, 02345ADC6h.

- WORD alignment: Implies that physical addresses must be aligned on even boundaries. For example, the last nibble of the address can only end in 0, 2, 4, 6, 8, Ah, Ch, or Eh (0FECBD9A2h).

- **DWORD** (Double-Word) alignment: Implies that the physical addresses can only be aligned on 4-byte boundaries. For example, the last nibble of the address can only end in 0, 4, 8, or Ch (0FECBD9A8h).

- **QWORD** (Quad-Word) alignment: Implies that the physical addresses can only be aligned on 8-byte boundaries. For example, the last nibble of the address can only end in 0 or 8 (0FECBD9A8h).

- **PARAGRAPH** alignment: Implies that the physical addresses can only be aligned on 16-byte boundaries. For example, the last nibble must be a 0 (02345ADC0h).

# 2.1 Introduction

This section provides an overview of the PCI/PCI-X Family of Gigabit Ethernet Controllers. The following sections give detailed information about the Ethernet controller's functionality, register description, and initialization sequence. All major interfaces of the Ethernet controllers are described in detail.

The following principles shaped the design of the PCI/PCI-X Family of Gigabit Ethernet Controllers:

- 1. Provide an Ethernet interface containing a 10/100/1000 Mb/s PHY that also supports 1000 Base-X implementations.

- 2. Provide the highest performance solution possible, based on the following:

- Provide direct access to all memory without using mapping registers

- Minimize the PCI target accesses required to manage the Ethernet controller

- Minimize the interrupts required to manage the Ethernet controller

- Off-load the host processor from simple tasks such as TCP checksum calculations

- Maximize PCI efficiency and performance

- Use mixed signal processing to assure physical layer characteristics surpass specifications for UTP copper media

- 3. Provide a simple software interface for basic operations.

- 4. Provide a highly configurable design that can be used effectively in different environments.

The PCI/PCI-X Family of Gigabit Ethernet Controllers architecture is a derivative of the 82542 and 82543 designs. They take the MAC functionality and integrated copper PHY from their predecessors and adds SMBus-based manageability and integrated ASF controller functionality to the MAC<sup>1</sup>. In addition, the **82546GB/EB** features this architecture in an integrated dual-port solution comprised of two distinct MAC/PHY instances.

<sup>1.</sup> Not applicable to the **82544GC/EI** or **82541ER**.

# 2.2 External Architecture

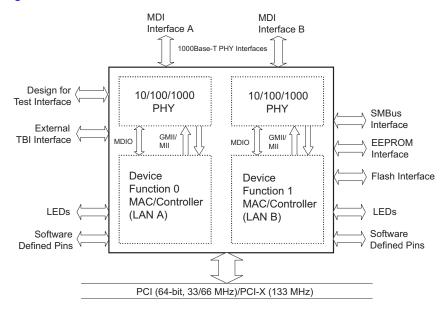

Figure 2-1 shows the external interfaces to the 82546GB/EB.

#### Figure 2-1. 82546GB/EB External Interface

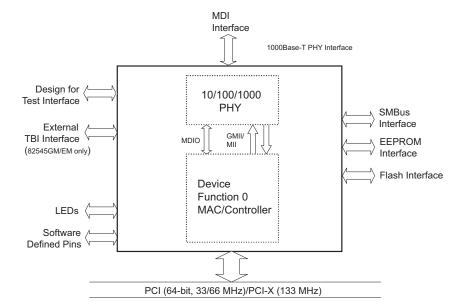

Figure 2-2 shows the external interfaces to the 82545GM/EM, 82544GC/EI, 82540EP/EM, and 82541xx.

Note: 82540EP/EM and 82541xx do not support PCI-X; 82544GC/EI and 82541ER do not support SMBus interface

#### Figure 2-2. 82545GM/EM, 82544GC/EI, 82540EP/EM, and 82541xx External Interface

Software Developer's Manual

Software Developer's Manual

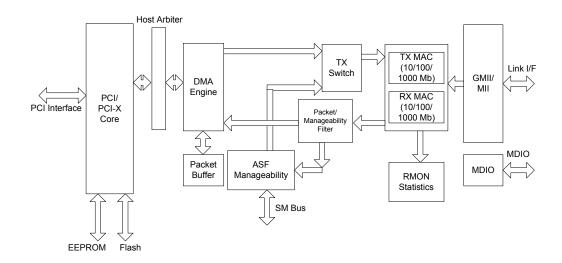

Figure 2-3. 82547GI(EI) External Interface

# 2.3 Microarchitecture

Compared to its predecessors, the PCI/PCI-X Family of Gigabit Ethernet Controller's MAC adds improved receive-packet filtering to support SMBus-based manageability, as well as the ability to transmit SMBus-based manageability packets. In addition, an ASF-compliant TCO controller is integrated into the controller's MAC for reduced-cost basic ASF manageability.

Note: The 82544GC/EI and 82541ER do not support SMBus-based manageability.

For the **82546GB/EB**, this new functionality is packaged in an integrated dual-port combination. The architecture includes two instances of both the MAC and PHY along with a single PCI/PCI-X interface. As a result, each of the logical LAN devices appear as a distinct PCI/PCI-X bus device.

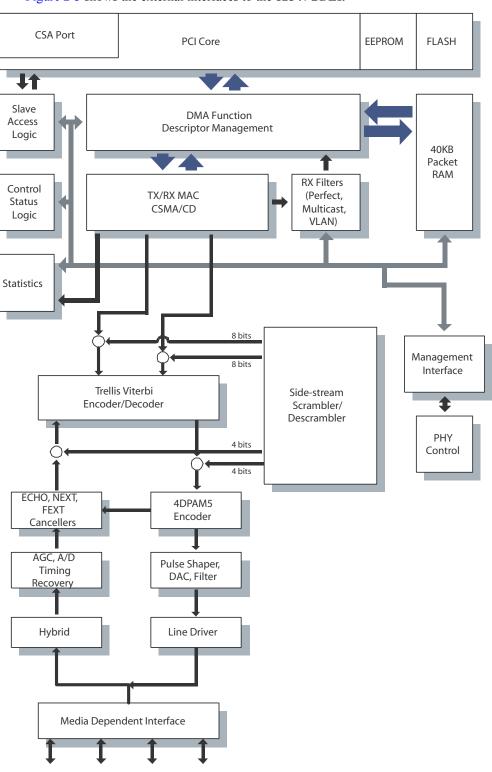

The following sections describe the hardware building blocks. Figure 2-4 shows the internal microarchitecture.

# 2.3.1 PCI/PCI-X Core Interface

The PCI/PCI-X core provides a complete glueless interface to a 33/66 MHz, 32/64-bit PCI bus or a 33/66/133 MHz, 32/64 bit PCI-X bus. It is compliant with the PCI Bus Specification Rev 2.2 or 2.3 and the PCI-X Specification Rev. 1.0a. The Ethernet controllers provide 32 or 64 bits of addressing and data, and the complete control interface to operate on a 32-bit or 64-bit PCI or PCI-X bus. In systems with a dedicated bus for the Ethernet controller, this provides sufficient bandwidth to support sustained 1000 Mb/s full-duplex transfer rates. Systems with a shared bus (especially the 32-bit wide interface) might not be able to maintain 1000 Mb/s, but can sustain multiple hundreds of Mbps.

Figure 2-4. Internal Architecture Block Diagram

When the Ethernet controller serves as a PCI target, it follows the PCI configuration specification, which allows all accesses to it to be automatically mapped into free memory and I/O space at initialization of the PCI system.

When processing transmit and receive frames, the Ethernet controller operates as master on the PCI bus. As a master, transaction burst length on the PCI bus is determined by several factors, including the PCI latency timer expiration, the type of bus transfer being made, the size of the data transfer, and whether the data transfer is initiated by receive or transmit logic.

The PCI/PCI-X bus interfaces to the DMA engine.

# 2.3.2 82547GI/EI CSA Interface

CSA is derived from the Intel® Hub Architecture. The 82547EI Controller CSA port consists of 11 data and control signals, two strobes, a 66 MHz clock, and driver compensation resistor connections. The operating details of these signals and the packet data protocol that accompanies them are proprietary. The CSA port has a theoretical bandwidth of 266 MB/s — approximately twice the peak bandwidth of a 32-bit 33 MHz PCI bus.

The CSA port architecture is invisible to both system software and the operating system, allowing conventional PCI-like configuration.

# 2.3.3 DMA Engine and Data FIFO

The DMA engine handles the receive and transmit data and descriptor transfers between the host memory and the on-chip memory.

In the receive path, the DMA engine transfers the data stored in the receive data FIFO buffer to the receive buffer in the host memory, specified by the address in the descriptor. It also fetches and writes back updated receive descriptors to host memory.

In the transmit path, the DMA engine transfers data stored in the host memory buffers to the transmit data FIFO buffer. It also fetches and writes back updated transmit descriptors.

The Ethernet controller data FIFO block consists of a 64 KB (40 KB for the **82547GI/EI**) on-chip buffer for receive and transmit operation. The receive and transmit FIFO size can be allocated based on the system requirements. The FIFO provides a temporary buffer storage area for frames as they are received or transmitted by the Ethernet controller.

The DMA engine and the large data FIFOs are optimized to maximize the PCI bus efficiency and reduce processor utilization by:

- Mitigating instantaneous receive bandwidth demands and eliminating transmit underruns by buffering the entire out-going packet prior to transmission

- Queuing transmit frames within the transmit FIFO, allowing back-to-back transmission with the minimum interframe spacing

- Allowing the Ethernet controller to withstand long PCI bus latencies without losing incoming data or corrupting outgoing data

- Allowing the transmit start threshold to be tuned by the transmit FIFO threshold. This adjustment to system performance is based on the available PCI bandwidth, wire speed, and latency considerations

- Offloading the receiving and transmitting IP and TCP/UDP checksums

- Directly retransmitting from the transmit FIFO any transmissions resulting in errors (collision detection, data underrun), thus eliminating the need to re-access this data from host memory

# 2.3.4 10/100/1000 Mb/s Receive and Transmit MAC Blocks

The controller's CSMA/CD unit handles all the IEEE 802.3 receive and transmit MAC functions while interfacing between the DMA and TBI/internal SerDes/MII/GMII interface block. The CSMA/CD unit supports IEEE 802.3 for 10 Mb/s, IEEE 802.3u for 100 Mb/s and IEEE 802.3z and IEEE 802.3ab for 1000 Mb/s.

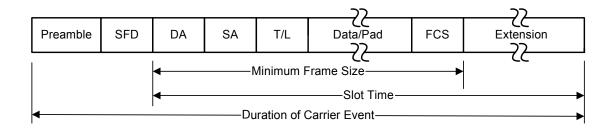

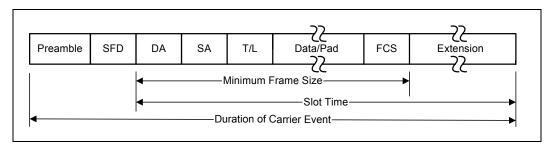

The Ethernet controller supports half-duplex 10/100 Mb/s MII or 1000 Mb/s GMII mode and all aspects of the above specifications in full-duplex operation. In half-duplex mode, the Ethernet controller supports operation as specified in IEEE 802.3z specification. In the receive path, the Ethernet controller supports carrier extended packets and packets generated during packet bursting operation. The **82554GC/EI**, in the transmit path, also supports carrier extended packets and can be configured to transmit in packet burst mode.

The Ethernet controller offers various filtering capabilities that provide better performance and lower processor utilization as follows:

- Provides up to 16 addresses for exact match unicast/multicast address filtering.

- Provides multicast address filtering based on 4096 bit vectors. Promiscuous unicast and promiscuous multicast filtering are supported as well.

- The Ethernet controller strips IEEE 802.1q VLAN tag and filter packets based on their VLAN ID. Up to 4096 VLAN tags are supported<sup>1</sup>.

In the transmit path, the Ethernet controller supports insertion of VLAN tag information, on a packet-by-packet basis.

The Ethernet controller implements the flow control function as defined in IEEE 802.3x, as well as specific operation of asymmetrical flow control as defined by IEEE 802.3z. The Ethernet controller also provides external pins for controlling the flow control function through external logic.

# 2.3.5 MII/GMII/TBI/Internal SerDes Interface Block

The Ethernet controller provides the following serial interfaces:

- A GMII/MII interface to the internal PHY.

- Internal SerDes interface<sup>2</sup> (82546GB/EB and 82545GM/EM)/Ten Bit Interface (TBI)<sup>2</sup> for the 82544GC/EI: The Ethernet controller implements the 802.3z PCS function, the Auto-Negotiation function and 10-bit data path interface (TBI) for both receive and transmit operations. It is used for 1000BASE-SX, -LX, and -CX configurations, operating only at 1000 Mb/s full-duplex. The on-chip PCS circuitry is only used when the link interface is configured for TBI mode and it is bypassed in internal PHY modes.

<sup>1.</sup> Not applicable to the **82541ER**.

<sup>2.</sup> Not applicable to the 82544GC/EI, 82540EP/EM, 82541xx, and 82547GI/EI.

*Note:* Refer to the Extended Device Control Register (bits 23:22) for mode selection (see Section 13.4.6).

The link can be configured by several methods. Software can force the link setting to Auto-Negotiation by setting either the MAC in TBI mode (internal SerDes for the **82546GB/EB** and **82545GM/EM**), or the PHY in internal PHY mode.

The speed of the link in internal PHY mode can be determined by several methods:

- Auto speed detection based on the receive clock signal generated by the PHY.

- Detection of the PHY link speed indication.

- Software forcing the configuration of link speed.

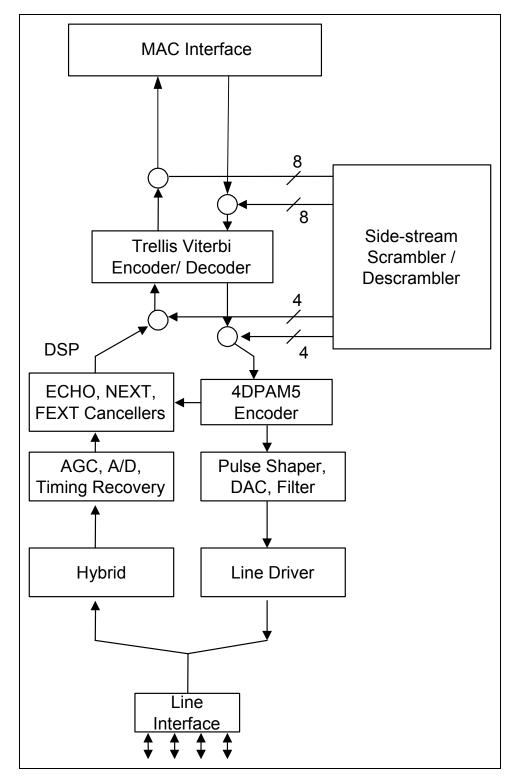

# 2.3.6 10/100/1000 Ethernet Transceiver (PHY)

The Ethernet controller provides a full high-performance, integrated transceiver for 10/100/1000 Mb/s data communication. The physical layer (PHY) blocks are 802.3 compliant and capable of operating in half-duplex or full-duplex modes.

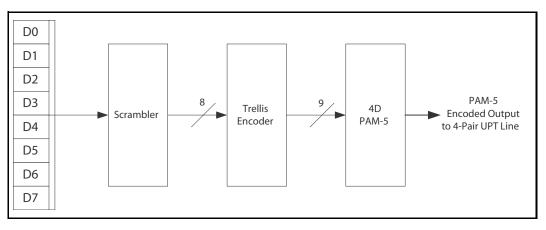

Highlights of the PHY blocks are as follows:

- Data stream serializers and encoders. Encoding techniques include Manchester, 4B/5B and 4D/PAM5. These blocks also perform data scrambling for 100/1000 Mb/s transmission as a technique to minimize radiated Electromagnetic Interference (EMI).

- A multi-mode transmit digital to analog converter, which produces filtered waveforms appropriate for the 10BASE-T, 100BASE-TX or 1000BASE-T Ethernet standards.

- Receiver Analog-to-Digital Converter (ADC). The ADC uses a 125 MHz sampling rate.

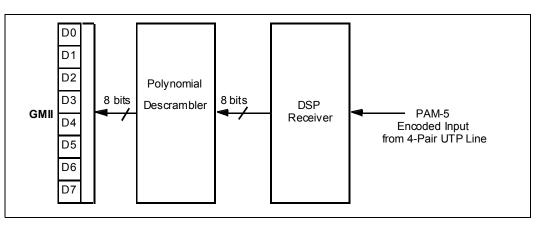

- Receiver decoders. These blocks perform the inverse operations of serializers, encoders and scramblers.

- Active hybrid and echo canceller blocks. The active hybrid and echo canceller blocks reduce the echo effect of transmitting and receiving simultaneously on the same analog pairs.

- NEXT canceller. This unit removes high frequency Near End Crosstalk induced among adjacent signal pairs.

- Additional wave shaping and slew rate control circuitry to reduce EMI.

Because the Ethernet controller is IEEE-compliant, the PHY blocks communicate with the MAC blocks through an internal GMII/MII bus operating at clock speeds of 2.5 MHz up to 125 MHz.

The Ethernet controller also uses an IEEE-compliant internal Management Data interface to communicate control and status information to the PHY.

## 2.3.7 EEPROM Interface

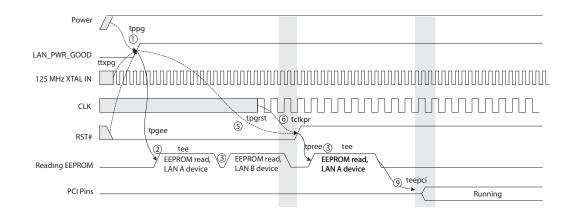

The PCI/PCI-X Family of Gigabit Ethernet Controllers provide a four-wire direct interface to a serial EEPROM device such as the 93C46 or compatible for storing product configuration information. Several words of the data stored in the EEPROM are automatically accessed by the Ethernet controller, after reset, to provide pre-boot configuration data to the Ethernet controller before it is accessible by the host software. The remainder of the stored information is accessed by various software modules to report product configuration, serial number and other parameters.

# 2.3.8 FLASH Memory Interface

The Ethernet controller provides an external parallel interface to a FLASH device. Accesses to the FLASH are controlled by the Ethernet controller and are accessible to software as normal PCI reads or writes to the FLASH memory mapping area. The Ethernet controller supports FLASH devices with up to 512 KB of memory.

*Note:* The **82540EP/EM** provides an external interface to a serial FLASH or Boot EEPROM device. See Appendix B for more information.

# 2.4 DMA Addressing

In appropriate systems, all addresses mastered by the Ethernet controller are 64 bits in order to support systems that have larger than 32-bit physical addressing. Providing 64-bit addresses eliminates the need for special segment registers.

*Note:* The PCI 2.2 or 2.3 Specification requires that any 64-bit address whose upper 32 bits are all 0b appear as a 32-bit address cycle. The Ethernet controller complies with the PCI 2.2 or 2.3 Specification.

PCI is little-endian; however, not all processors in systems using PCI treat memory as little-endian. Network data is fundamentally a byte stream. As a result, it is important that the processor and Ethernet controller agree about the representation of memory data. The default is little-endian mode.

Descriptor accesses are not byte swapped.

The following example illustrates data-byte ordering for little endian. Bytes for a receive packet arrive in the order shown from left to right.

01 02 03 04 05 06 07 08 09 0a 0b 0c 0d 0e 0f 10 11 12 13 14 15 16 17 18 19 1a 1b 1c 1d 1e

#### Example 2-1. Byte Ordering

There are no alignment restrictions on packet-buffer addresses. The byte address for the major words is shown on the left. The byte numbers and bit numbers for the PCI bus are shown across the top.

#### Table 2-1. Little Endian Data Ordering

|         |    | 63 |    |    |    |    |    |    | 0  |

|---------|----|----|----|----|----|----|----|----|----|

|         |    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Byte    | 0  | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 |

| Address | 8  | 10 | Of | 0e | 0d | 0c | 0b | 0a | 09 |

|         | 10 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 |

|         | 18 | 20 | 1f | 1e | 1d | 1c | 1b | 1a | 19 |

# 2.5 Ethernet Addressing

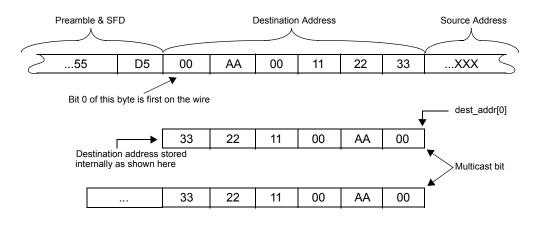

Several registers store Ethernet addresses in the Ethernet controller. Two 32-bit registers make up the address: one is called "high", and the other is called "low". For example, the Receive Address Register is comprised of Receive Address High (RAH) and Receive Address Low (RAL). The least significant bit of the least significant byte of the address stored in the register (for example, bit 0 of RAL) is the multicast bit. The LS byte is the first byte to appear on the wire. This notation applies to all address registers, including the flow control registers.

Figure 2-5 shows the bit/byte addressing order comparison between what is on the wire and the values in the unique receive address registers.

#### Figure 2-5. Example of Address Byte Ordering

The address byte order numbering shown in Figure 2-5 maps to Table 2-2. Byte #1 is first on the wire.

#### Table 2-2. Intel® Architecture Byte Ordering

| IA Byte #        | 1 (LSB) | 2  | 3  | 4  | 5  | 6 (MSB) |

|------------------|---------|----|----|----|----|---------|

| Byte Value (Hex) | 00      | AA | 00 | 11 | 22 | 33      |

*Note:* The notation in this manual follows the convention shown in Table 2-2. For example, the address in Table 2-2 indicates 00\_AA\_00\_11\_22\_33h, where the first byte (00h\_) is the first byte on the wire, with bit 0 of that byte transmitted first.

# 2.6 Interrupts

The Ethernet controller provides a complete set of interrupts that allow for efficient software management. The interrupt structure is designed to accomplish the following:

- Make accesses "thread-safe" by using 'set' and 'clear-on-read' rather than 'read-modify-write' operations.

- Minimize the number of interrupts needed relative to work accomplished.

- Minimize the processing overhead associated with each interrupt.

Intel accomplished the first goal by an interrupt logic consisting of four interrupt registers. More detail about these registers is given in sections 13.4.17 through 13.4.21.

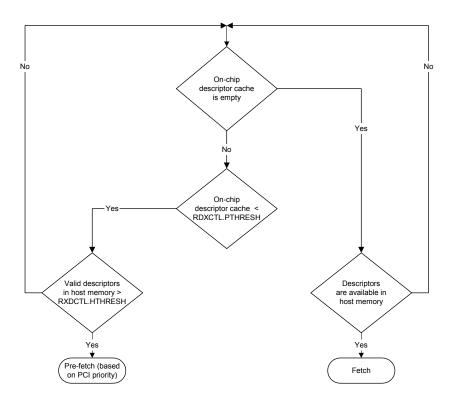

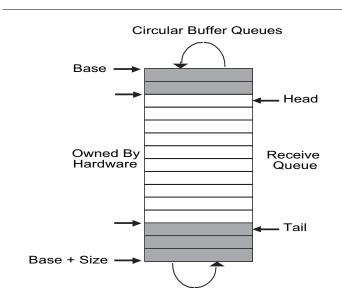

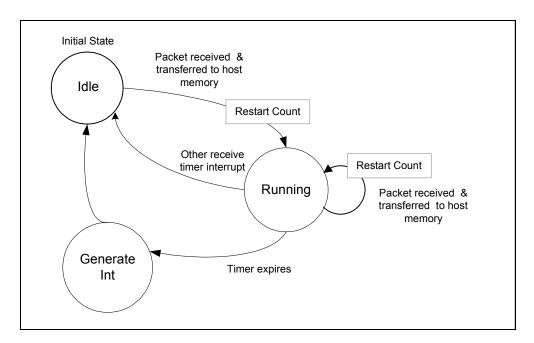

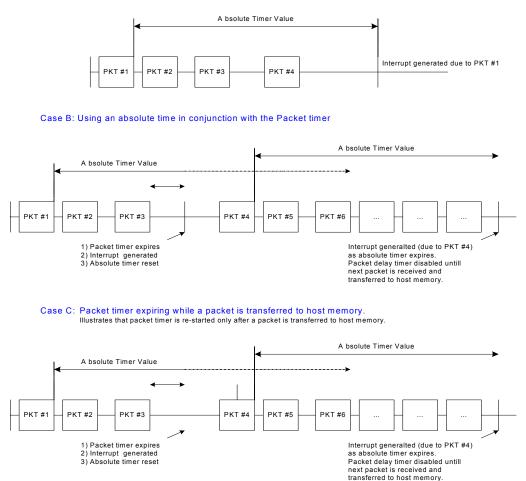

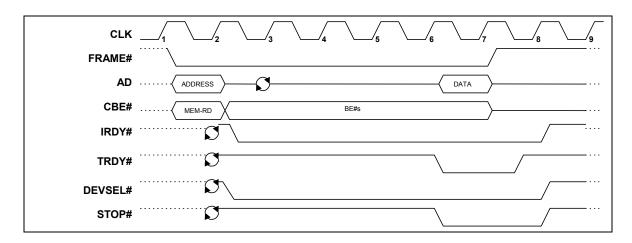

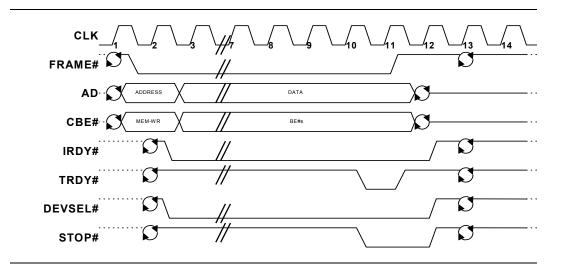

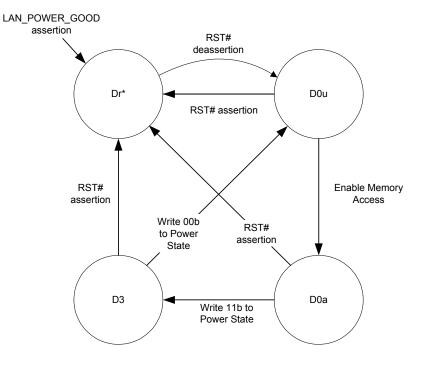

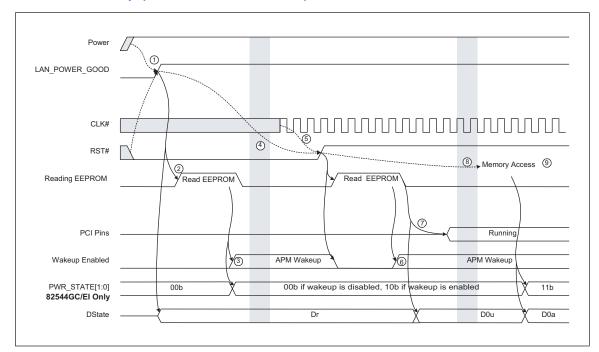

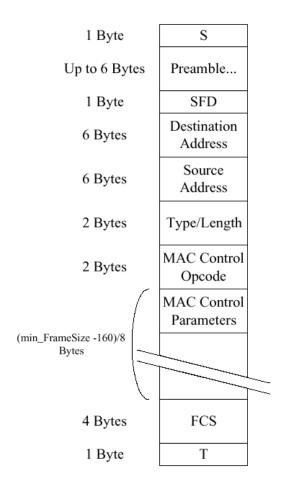

• Interrupt Cause 'Set' and 'Read' Registers