## DiamondMax<sup>™</sup> 2160

88400D8, 86480D6, 84320D4 83240D3 and 82160D2 Part #1384/A

All material contained herein Copyright © 1997 Maxtor Corporation. CrystalMax<sup>TM</sup>, CrystalMax<sup>TM</sup> 1080, DiamondMax<sup>TM</sup>, DiamondMax<sup>TM</sup> 1750, DiamondMax<sup>TM</sup> 2160 and MaxFax<sup>TM</sup> are trademarks of Maxtor Corporation. No Quibble® Service is a registered trademark of Maxtor Corporation. Other brands or products are trademarks or registered trademarks of their respective holders. Contents and specifications subject to change without notice. All rights reserved. Printed in the U.Š.A. 9/97

Corporate Headquarters 510 Cottonwood Drive Milpitas, California 95035 Tel: 408-432-1700 Fax: 408-432-4510

Research and Development **Engineering Center** 2190 Miller Drive Longmont, Colorado 80501 Tel: 303-651-6000

Fax: 303-678-2165

Revisions Manual No. 1384

| REV | EC NO. | SECTION | DESCRIPTION     | DATE     |

|-----|--------|---------|-----------------|----------|

| А   | 78641B | All     | Initial release | 09/16/97 |

## **Before You Begin**

Thank you for your interest in the Maxtor DiamondMax<sup>™</sup> 2160 AT hard disk drives. This manual provides technical information for OEM engineers and systems integrators regarding the installation and use of the 88400D8, 86480D6, 84320D4, 83240D3 and 82160D2.

Drive repair should be performed only at an authorized repair center. For repair information, contact the Maxtor Customer Service Center at 800-2MAXTOR or 408-432-1700.

Before unpacking the hard drive, please review Sections 1 through 4.

#### **CAUTION**

Maxtor DiamondMax 2160 hard drives are precision products. Failure to follow these precautions and guidelines outlined here may lead to product failure, damage and invalidation of all warranties.

- **1**BEFORE unpacking or handling a drive, take all proper electro-static discharge (ESD) precautions, including personnel and equipment grounding. Stand-alone drives are sensitive to ESD damage.

- **2** BEFORE removing drives from their packing material, allow them to reach room temperature.

- **3** During handling, *NEVER* drop, jar, or bump a drive.

- Once a drive is removed from the Maxtor shipping container, *IMMEDIATELY* secure the drive through its mounting holes within a chassis. Otherwise, store the drive on a padded, grounded, antistatic surface.

- NEVER switch DC power onto the drive by plugging an electrically live DC source cable into the drive's connector. NEVER connect a live bus to the drive's interface connector.

Please do not remove or cover up Maxtor factory-installed drive labels. They contain information required should the drive ever need repair.

## **Contents**

4092 Cylinder Limitation

| Section 1 — Introduction                        |       |

|-------------------------------------------------|-------|

| Maxtor Corporation                              | 1 - 1 |

| Products                                        | 1 - 1 |

| Support                                         | 1 - 1 |

| Manual Organization                             | 1 - 1 |

| Abbreviations                                   | 1 - 1 |

| Conventions                                     | 1 - 2 |

| Key Words                                       | 1 - 2 |

| Numbering                                       | 1 - 2 |

| Signal Conventions                              | 1 - 2 |

| Section 2 — Product Description                 |       |

| The DiamondMax™ 2160                            |       |

| Product Features                                | 2 - 2 |

| Functional/Interface                            | 2 - 2 |

| Zone Density Recording                          | 2 - 2 |

| Read/Write Multiple Mode                        | 2 - 2 |

| UltraDMA - Mode 2                               | 2 - 2 |

| Multi-word DMA (EISA Type B) - Mode 2           | 2 - 2 |

| Sector Address Translation                      | 2 - 2 |

| Logical Block Addressing                        | 2 - 3 |

| Defect Management Zone                          | 2 - 3 |

| On-the-Fly Hardware Error Correction Code (ECC) | 2 - 3 |

| Software ECC Correction                         | 2 - 3 |

| Automatic Head Park and Lock Operation          | 2 - 3 |

| Cache Management                                | 2 - 4 |

| Buffer Segmentation                             | 2 - 4 |

| Read-Ahead Mode                                 | 2 - 4 |

| Automatic Write Reallocation (AWR)              | 2 - 4 |

| Write Cache Stacking                            | 2 - 4 |

| Major HDA Components                            | 2 - 5 |

| Drive Mechanism                                 | 2 - 5 |

| Rotary Actuator                                 | 2 - 5 |

| Read/Write Electronics                          | 2 - 5 |

| Read/Write Heads and Media                      | 2 - 5 |

| Air Filtration System                           | 2 - 5 |

| Microprocessor                                  | 2 - 5 |

| Subsystem Configuration                         | 2 - 6 |

| Dual Drive Support                              | 2 - 6 |

| Cable Select Option                             | 2 - 6 |

| Jumper Location/Configuration                   | 2 - 6 |

2 - 6

## **Section 3 — Product Specifications**

| • • • • • • • • • • • • • • • • • • •    |        |

|------------------------------------------|--------|

| Configuration                            | 3 - 1  |

| Performance                              | 3 - 1  |

| Physical Dimensions                      | 3 - 2  |

| Power Requirements                       | 3 - 3  |

| Power Mode Definitions                   | 3 - 3  |

| Environmental                            | 3 - 3  |

| Shock and Vibration                      | 3 - 4  |

| Reliability and Maintenance              | 3 - 4  |

| Data Reliability                         | 3 - 4  |

| Acoustic Noise                           | 3 - 4  |

| EPA Energy Star Compliance               | 3 - 4  |

| EMC/EMI                                  | 3 - 5  |

| Standard Test Methods                    | 3 - 5  |

| Safety Regulatory Compliance             | 3 - 5  |

| Section 4 — Handling and Installation    |        |

| Pre-formatted Drive                      | 4 - 1  |

| Important Notice                         | 4 - 1  |

| Hard Drive Handling Precautions          | 4 - 1  |

| Electro-Static Discharge (ESD)           | 4 - 1  |

| Unpacking and Inspection                 | 4 - 2  |

| Repacking                                | 4 - 3  |

| Physical Installation                    | 4 - 3  |

| Drive Jumper Settings                    | 4 - 4  |

| Mounting Drive in System                 | 4 - 4  |

| Attaching IDE Interface and Power Cables | 4 - 6  |

| Attaching System Cables                  | 4 - 7  |

| System Setup                             | 4 - 8  |

| Hard Drive Preparation                   | 4 - 10 |

| Section 5 — AT Interface Description     |        |

| Interface Connector                      | 5 - 1  |

| Pin Description Summary                  | 5 - 1  |

| Pin Description Table                    | 5 - 2  |

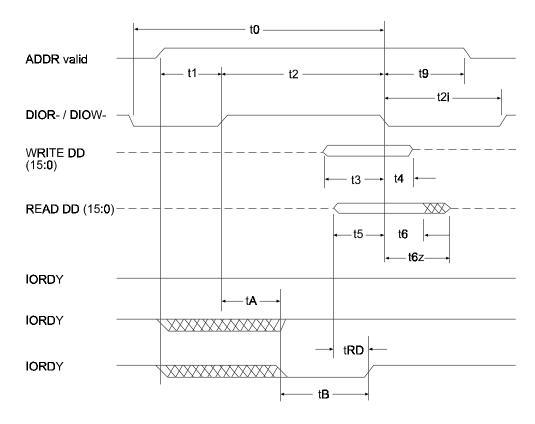

| PIO Timing                               | 5 - 3  |

| DMA Timing                               | 5 - 4  |

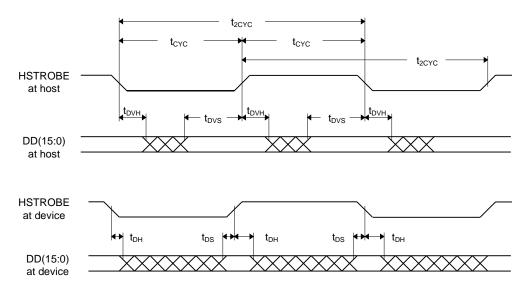

Ultra DMA Timing Parameters

5 - 5

## **Section 6 — Host Software Interface**

| Task File Registers                   | 6 - 1 |

|---------------------------------------|-------|

| Data Register                         | 6 - 1 |

| Error Register                        | 6 - 1 |

| Features Register                     | 6 - 1 |

| Sector Count Register                 | 6 - 2 |

| Sector Number Register                | 6 - 2 |

| Cylinder Number Registers             | 6 - 2 |

| Device/Head Register                  | 6 - 2 |

| Status Register                       | 6 - 2 |

| Command Register                      | 6 - 3 |

| Read Commands                         | 6 - 3 |

| Write Commands                        | 6 - 3 |

| Mode Set/Check Commands               | 6 - 3 |

| Power Mode Commands                   | 6 - 3 |

| Initialization Commands               | 6 - 3 |

| Seek, Format, and Diagnostic Commands | 6 - 3 |

| S.M.A.R.T. Commands                   | 6 - 3 |

| Summary                               | 6 - 4 |

| Control Diagnostic Registers          | 6 - 5 |

| Alternate Status Register             | 6 - 5 |

| Device Control Register               | 6 - 5 |

| Digital Input Register                | 6 - 5 |

| Reset and Interrupt Handling          | 6 - 6 |

## **Section 7 — Interface Commands**

| Command Summary                       | 7 - 1  |

|---------------------------------------|--------|

| Read Commands                         | 7 - 2  |

| Read Sector(s)                        | 7 - 2  |

| Read Verify Sector(s)                 | 7 - 2  |

| Read Sector Buffer                    | 7 - 2  |

| Read DMA                              | 7 - 3  |

| Read Multiple                         | 7 - 3  |

| Set Multiple                          | 7 - 3  |

| Write Commands                        | 7 - 4  |

| Write Sector(s)                       | 7 - 4  |

| Write Verify Sector(s)                | 7 - 4  |

| Write Sector Buffer                   | 7 - 4  |

| Write DMA                             | 7 - 5  |

| Write Multiple                        | 7 - 5  |

| Ultra DMA                             | 7 - 5  |

| Set Feature Commands                  | 7 - 5  |

| Set Features Mode                     | 7 - 5  |

| Power Mode Commands                   | 7 - 7  |

| Standby Immediate                     | 7 - 7  |

| Idle Immediate                        | 7 - 7  |

| Standby                               | 7 - 7  |

| Idle                                  | 7 - 7  |

| Check Power Mode                      | 7 - 7  |

| Set Sleep Mode                        | 7 - 7  |

| Default Power-on Condition            | 7 - 7  |

| Initialization Commands               | 7 - 9  |

| Identify Drive                        | 7 - 9  |

| Initialize Drive Parameters           | 7 - 12 |

| Seek, Format, and Diagnostic Commands | 7 - 13 |

| S.M.A.R.T. Command Set                | 7 - 14 |

| Section 8 — Service and Support       |        |

| Service Policy                        | 8 - 1  |

| No Quibble Service                    | 8 - 1  |

| Support                               | 8 - 1  |

| Glossary                              |        |

| Glossary                              | GL - 1 |

# **Figures**

| Figure | Title                                          | Page   |

|--------|------------------------------------------------|--------|

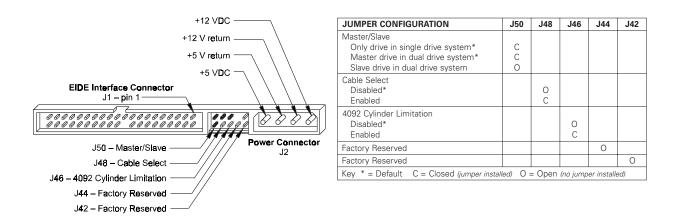

| 2 - 1  | PCBA Jumper Locations and Configuration        | 2 - 6  |

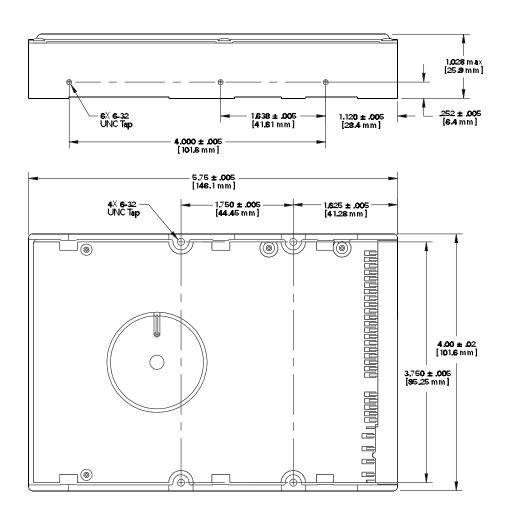

| 3 - 1  | Outline and Mounting Dimensions                | 3 - 2  |

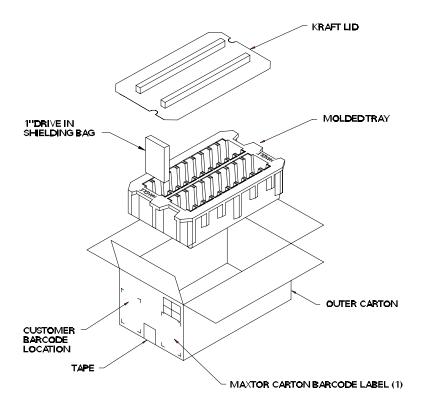

| 4 - 1  | Multi-pack Shipping Container                  | 4 - 2  |

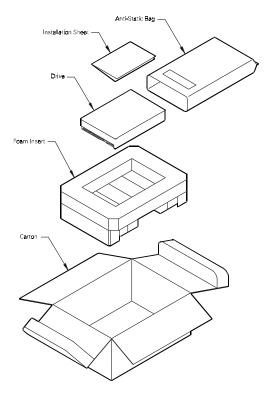

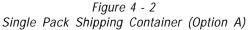

| 4 - 2  | Single-pack Shipping Container (Option A)      | 4 - 3  |

| 4 - 3  | Single-pack Shipping Container (Option B)      | 4 - 3  |

| 4 - 4  | Master/Slave Jumper Detail                     | 4 - 4  |

| 4 - 5  | 5.25-inch Mounting Brackets/Slider Rails       | 4 - 4  |

| 4 - 6  | 5.25-inch Installation                         | 4 - 5  |

| 4 - 7  | 3.5-inch Installation                          | 4 - 5  |

| 4 - 8  | IDE Interface and Power Cabling Detail         | 4 - 6  |

| 4 - 9  | System Interface Card Cabling                  | 4 - 7  |

| 4 - 10 | System Mother Board Cabling                    | 4 - 7  |

| 4 - 11 | J46 (4092 Cylinder Limitation) Detail          | 4 - 9  |

| 5 - 1  | Data Connector                                 | 5 - 1  |

| 5 - 2  | PIO Data Transfer to/from Device               | 5 - 3  |

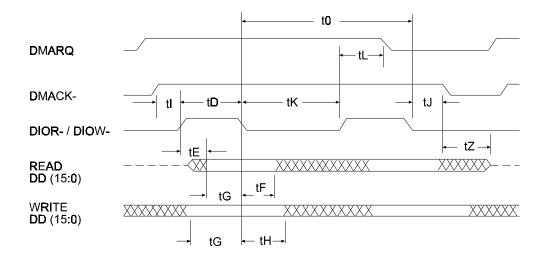

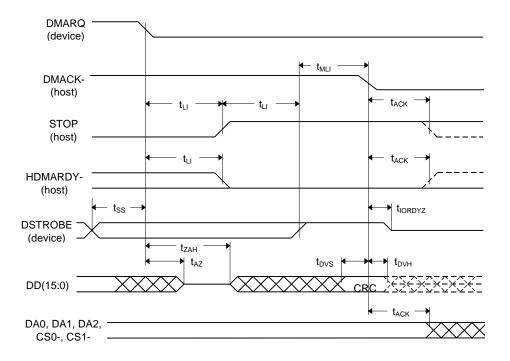

| 5 - 3  | Multi-word DMA Data Transfer                   | 5 - 4  |

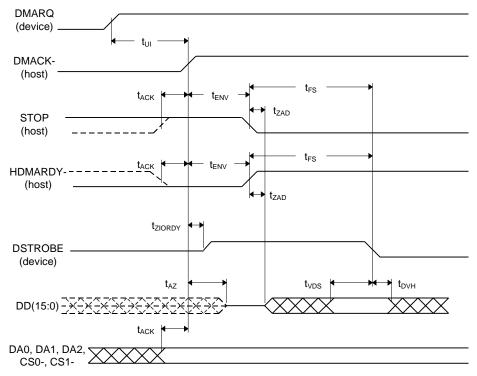

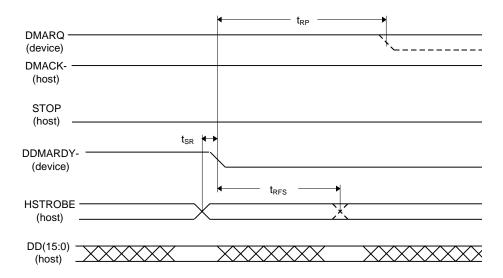

| 5 - 4  | Initiating an Ultra DMA Data In Burst          | 5 - 5  |

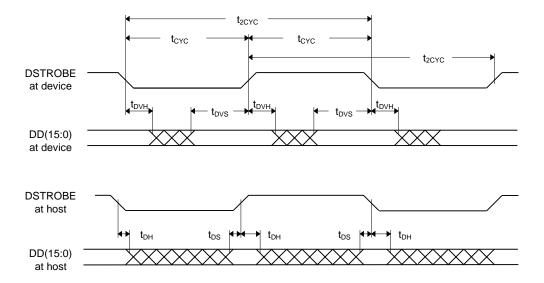

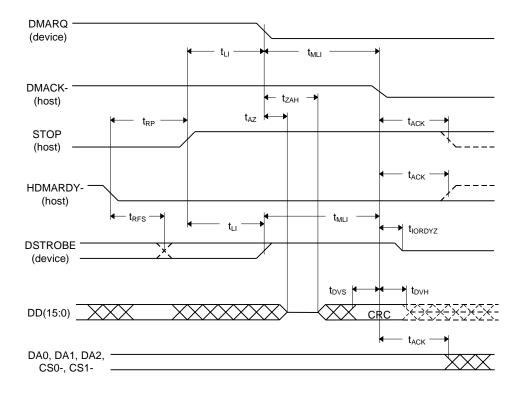

| 5 - 5  | Sustained Ultra DMA Data In Burst              | 5 - 6  |

| 5 - 6  | Host Pausing an Ultra DMA Data In Burst        | 5 - 6  |

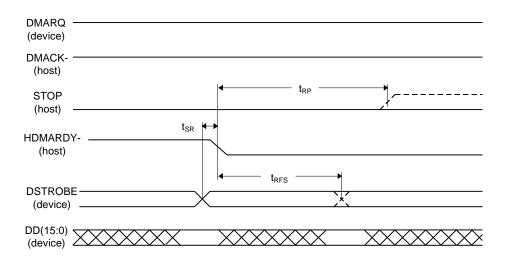

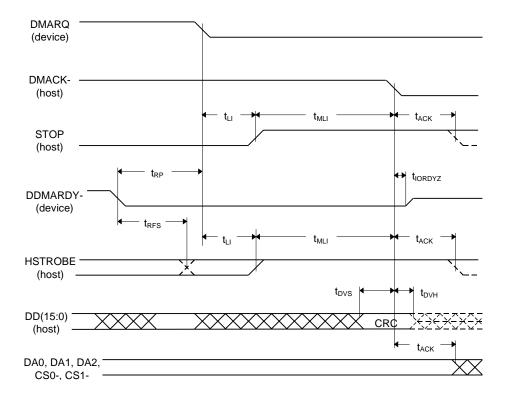

| 5 - 7  | Device Terminating an Ultra DMA Data In Burst  | 5 - 7  |

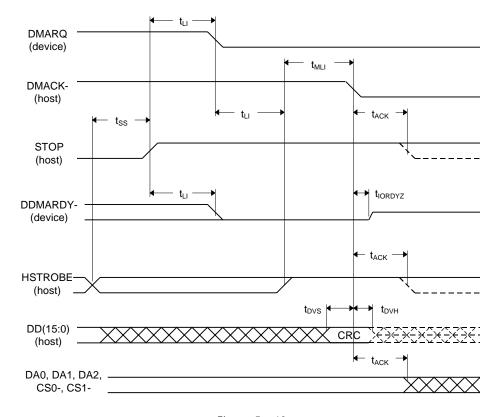

| 5 - 8  | Host Terminating an Ultra DMA Data In Burst    | 5 - 7  |

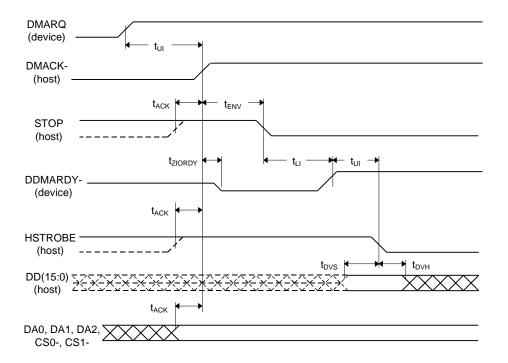

| 5 - 9  | Initiating an Ultra DMA Data Out Burst         | 5 - 8  |

| 5 - 10 | Sustained Ultra DMA Data Out Burst             | 5 - 8  |

| 5 - 11 | Device Pausing an Ultra DMA Data Out Burst     | 5 - 9  |

| 5 - 12 | Host Terminating an Ultra DMA Data Out Burst   | 5 - 9  |

| 5 - 13 | Device Terminating an Ultra DMA Data Out Burst | 5 - 10 |

## Introduction

### **Maxtor Corporation**

Maxtor Corporation has been providing high-quality computer storage products since 1982. Along the way, we've seen many changes in data storage needs. Not long ago, only a handful of specific users needed more than a couple hundred megabytes of storage. Today, downloading from the Internet and CD-ROMs, multimedia, networking and advanced office applications are driving storage needs even higher. Even home PC applications need capacities measured in gigabytes, not megabytes.

#### **Products**

Maxtor's products meet those demanding storage capacity requirements with room to spare. They feature proven compatibility and reliability. While **DiamondMax**<sup>TM</sup> **2160** is the latest addition to our family of high performance desktop hard drives, the DiamondMax<sup>TM</sup> 1750 and CrystalMax<sup>TM</sup> 1080 series hard drives deliver industry-leading capacity, performance and value for many PC applications.

#### **Support**

No matter which capacity, all Maxtor hard drives are supported by our commitment to total customer satisfaction and our *No Quibble®* Service guarantee. One call – or a visit to our home page on the Internet (http://www.maxtor.com) – puts you in touch with either technical support or customer service. We'll provide you the information you need quickly, accurately and in the form you prefer – a fax, a downloaded file or a conversation with a representative.

## **Manual Organization**

This hard disk drive reference manual is organized in the following method:

| Section 1 – Introduction            |

|-------------------------------------|

| Section 2 – Description             |

| Section 3 – Specifications          |

| Section 4 – Installation            |

| Section 5 – AT Interface            |

| Section 6 - Host Software Interface |

| Section 7 – Interface Commands      |

| Section 8 – Service and Support     |

| Appendix - Glossary                 |

#### **Abbreviations**

| ABBRV | DESCRIPTION              | ABBRV     | DESCRIPTION                |

|-------|--------------------------|-----------|----------------------------|

| ATA   | AT attachment            | MB        | megabyte                   |

| bpi   | bits per inch            | Mbits/sec | megabits per second        |

| CHS   | cylinder - head - sector | MB/sec    | megabytes per second       |

| db    | decibels                 | MHz       | megahertz                  |

| dBA   | decibels, A weighted     | ms        | millisecond                |

| DMA   | direct memory access     | MSB       | most significant bit       |

| ECC   | error correction code    | mV        | millivolts                 |

| fci   | flux changes per inch    | ns        | nanoseconds                |

| G     | acceleration             | PIO       | programmed input/output    |

| GB    | gigabyte                 | RPM       | revolutions per minute     |

| Hz    | hertz                    | tpi       | tracks per inch            |

| KB    | kilobyte                 | UDMA      | ultra direct memory access |

| LBA   | logical block address    | μsec      | microsecond                |

| LSB   | least significant bit    | V         | volts                      |

| mA    | milliamperes             | W         | watts                      |

### Conventions

If there is a conflict between text and tables, the table shall be accepted as being correct.

#### **Key Words**

The names of abbreviations, commands, fields and acronyms used as signal names are in all uppercase type (e.g., IDENTIFY DRIVE). Fields containing only one bit are usually referred to as the "name" bit instead of the "name" field.

Names of drive registers begin with a capital letter (e.g., Cylinder High register).

#### Numbering

Numbers that are **not** followed by a lowercase "b" or "h" are decimal values. Numbers that are followed by a lowercase "b" (e.g., 01b) are binary values. Numbers that are followed by a lowercase "h" (e.g., 3Ah) are hexadecimal values.

#### **Signal Conventions**

Signal names are shown in all uppercase type.

All signals are either high active or low active signals. A dash character (-) at the end of a signal name indicates that the signal is low active. A low active signal is true when it is below ViL and is false when it is above ViH. A signal without a dash at the end indicates that the signal is high active. A high active signal is true when it is above ViH and is false when it is below ViL.

When a signal is asserted, it means the signal is driven by an active circuit to its true state.

When a signal is negated, it means the signal is driven by an active circuit to its false state.

When a signal is released, it means the signal is not actively driven to any state. Some signals have bias circuitry that pull the signal to either a true or false state when no signal driver is actively asserting or negating the signal. These instances are noted under the description of the signal.

## **Product Description**

Maxtor DiamondMax<sup>™</sup> 2160 AT disk drives are 1-inch high, 3.5-inch diameter random access storage devices which incorporate an on-board Ultra DMA/ATA controller. High capacity is achieved by a balanced combination of high areal recording density and the latest data encoding and servo techniques.

Maxtor's latest advancements in electronic packaging and integration methods have lowered the drive's power consumption and increased its reliability. Advanced magneto-resistive read/write heads, an state-of-the-art head/disk assembly using an integrated motor/spindle design allow up to four disks in a 3.5-inch package.

Exceptionally high data transfer rates and < 9.7 ms access times make these performance series disk drives especially well-suited to high speed desktop and server applications.

## DiamondMax 2160 Key Features

ANSI ATA-4 compliant PIO Mode 4 interface (Enhanced IDE)

Supports Ultra DMA Mode 2 for 33 MB/sec data transfers

256 KB buffer with multi-adaptive cache manager

< 9.7 ms seek time

Zone density and I.D.-less recording

High reliability with > 500,000 hour MTBF

Outstanding shock resistance at 150 Gs

High durability with 50K constant start/stop cycles

Advanced multi-burst on-the-fly Error Correction Code (ECC)

Extended data integrity with ECC protected data and fault tolerant servo synchronization fields

Supports EPA Energy Star Standards (Green PC Friendly) with ATA powering savings commands

Auto park and lock actuator mechanism

Low power consumption

S.M.A.R.T. Capability

Note: Maxtor defines one megabyte as 10<sup>6</sup> or one million bytes and one gigabyte as 10<sup>9</sup> or one billion bytes.

## **Product Features**

#### Functional / Interface

Maxtor DiamondMax<sup>™</sup> 2160 hard drives contain all necessary mechanical and electronic parts to interpret control signals and commands from an AT-compatible host computer. See Section 3 Product Specifications, for complete drive specifications.

#### **Zone Density Recording**

The disk capacity is increased with bit density management – common with Zone Density Recording. Each disk surface is divided into 16 circumferential zones. All tracks within a given zone contain a constant number of data sectors. The number of data sectors per track varies in different zones; the outermost zone contains the largest number of data sectors and the innermost contains the fewest.

#### Read/Write Multiple Mode

This mode is implemented per ANSI ATA/ATAPI-4 specification. Read/Write Multiple allows the host to transfer a set number of sectors without an interrupt request between them, reducing transfer process overhead and improving host performance.

#### UltraDMA - Mode 2

Maxtor DiamondMax 2160 hard drives fully comply with the new ANSI Ultra DMA protocol, which greatly improves overall AT interface performance by significantly improving burst and sustained data throughput.

#### Multi-word DMA (EISA Type B) - Mode 2

Supports multi-word Direct Memory Access (DMA) EISA Type B mode transfers.

#### **Sector Address Translation**

All DiamondMax 2160 drives feature a universal translate mode. In an AT/EISA-class system, the drive may be configured to any specified combination of cylinders, heads and sectors (within the range of the drive's formatted capacity). DiamondMax 2160 drives power-up in a translate mode:

| MODEL   | CYLINDERS | HEADS | SECTORS | CAPACITY |

|---------|-----------|-------|---------|----------|

| 88400D8 | 16,278    | 16    | 63      | 8,400 MB |

| 86480D6 | 13,395    | 15    | 63      | 6,480 MB |

| 84320D4 | 8,930     | 15    | 63      | 4,320 MB |

| 83240D3 | 6,697     | 15    | 63      | 3,240 MB |

| 82160D2 | 4 465     | 15    | 63      | 2 160 MB |

#### **Logical Block Addressing**

The Logical Block Address (LBA) mode can only be utilized in systems that support this form of translation. The cylinder, head and sector geometry of the drive, as presented to the host, differs from the actual physical geometry.

The host AT computer may access a drive of set parameters: number of cylinders, heads and sectors per track, plus cylinder, head and sector addresses. However, the drive can't use these host parameters directly because of zoned recording techniques. The drive translates the host parameters to a set of logical internal addresses for data access.

The host drive geometry parameters are mapped into an LBA based on this formula:

```

LBA = (HSCA - 1) + HHDA x HSPT + HNHD x HSPT x HCYA (1)

= (HSCA - 1) + HSPT x (HHDA + HNHD x HCYA) (2)

where HSCA = Host Sector Address, HHDA = Host Head Address

HCYA = Host Cylinder Address, HNHD = Host Number of Heads

HSPT = Host Sectors per Track

```

The LBA is checked for violating the drive capacity. If it does not, the LBA is converted to physical drive cylinder, head and sector values. The physical address is then used to access or store the data on the disk and for other drive related operations.

#### **Defect Management Zone (DMZ)**

Each drive model has a fixed number of spare sectors per drive, all of which are located at the end of the drive. Upon detection of a bad sector that has been reassigned, the next sequential sector is used.

For example, if sector 3 is flagged, data that would have been stored there is "pushed down" and recorded in sector 4. Sector 4 then effectively becomes sector 3, as sequential sectors are "pushed down" across the entire drive. The first spare sector makes up for the loss of sector 3, and so maintains the sequential order of data. This push down method assures maximum performance.

#### On-the-Fly Hardware Error Correction Code (ECC)

10 bits, single burst, guaranteed

#### **Software ECC Correction**

64 bits, single burst, guaranteed28 bits, double bursts, guaranteed

#### **Automatic Park and Lock Operation**

Immediately following power down, dynamic braking of the spinning disks delays momentarily allowing the read/write heads to move to an inner mechanical stop. A small fixed magnet holds the rotary actuator in place as the disk spins down. The rotary actuator is released only when power is again applied.

## **Cache Management**

#### **Buffer Segmentation**

The data buffer is organized into two segments: the data buffer and the micro controller scratch pad. The data buffer is dynamically allocated for read and write data depending on the commands received. A variable number of read and write buffers may exist at the same time.

#### Read-Ahead Mode

Normally, this mode is active. Following a read request, disk read-ahead begins on the first sector and continues sequentially until the allocated buffer is full. If a read request is received during the read-ahead operation, the buffer is examined to determine if the request is in the cache. If a cache hit occurs, read-ahead mode continues without interruption and the host transfer begins immediately.

#### **Automatic Write Reallocation (AWR)**

This feature is part of the write cache and reduces the risk of data loss during deferred write operations. If a disk error occurs during the disk write process, the disk task stops and the suspect sector is reallocated to a pool of alternate sectors located at the end of the drive. Following reallocation, the disk write task continues until it is complete.

#### Write Cache Stacking

Normally, this mode is active. Write cache mode accepts the host write data into the buffer until the buffer is full or the host transfer is complete. A command complete interrupt is generated at the end of the transfer.

A disk write task begins to store the host data to disk. Host write commands continue to be accepted and data transferred to the buffer until either the write command stack is full or the data buffer is full. The drive may reorder write commands to optimize drive throughput.

## **Major HDA Components**

#### **Drive Mechanism**

A brush-less DC direct drive motor rotates the spindle at 5,200 RPM ( $\pm 0.1\%$ ). The dynamically balanced motor/spindle assembly ensures minimal mechanical run-out to the disks. A dynamic brake provides a fast stop to the spindle motor upon power removal. The speed tolerance includes motor performance and motor circuit tolerances.

#### **Rotary Actuator**

All DiamondMax<sup>TM</sup> 2160 drives employ a rotary voice coil actuator which consists of a moving coil, an actuator arm assembly and stationary magnets. The actuator moves on a low-mass, low-friction center shaft. The low friction contributes to fast access times and low power consumption.

#### Read/Write Electronics

An integrated circuit mounted within the sealed head disk assembly (near the read/write heads) provides up to eight head selection (depending on the model), read pre-amplification and write drive circuitry.

#### Read/Write Heads and Media

Low mass, low force magneto-resistive read/write heads record data on 3.5-inch diameter disks. Maxtor uses a sputtered thin film medium on all disks for DiamondMax 2160 drives.

#### Air Filtration System

All DiamondMax 2160 drives are assembled in a Class 100 controlled environment. Over the life of the drive, a 0.1 micron filter and breather filter located within the sealed head disk assembly (HDA) maintain a clean environment to the heads and disks. DiamondMax 2160 drives are designed to operate in a typical office environment with minimum environmental control.

#### Microprocessor

The microprocessor controls the following functions for the drive electronics:

Command execution

Cache management

Data correction and error recovery

Diagnostic execution

Data sequencing

Head positioning (including error recovery)

Host interface

Index detection

Spin speed control

Seeks

Servo

S.M.A.R.T.

## **Subsystem Configuration**

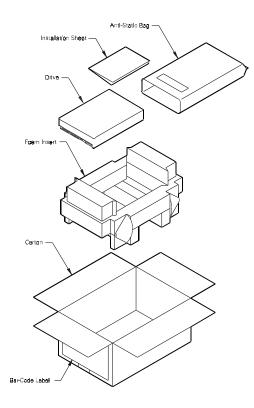

#### **Dual Drive Support**

Two drives may be accessed via a common interface cable, using the same range of I/O addresses. The drives are jumpered as device 0 or 1 (Master/Slave), and are selected by the drive select bit in the Device/Head register of the task file.

All Task File registers are written in parallel to both drives. The interface processor on each drive decides whether a command written to it should be executed; this depends on the type of command and which drive is selected. Only the drive selected executes the command and activates the data bus in response to host I/O reads; the drive not selected remains inactive.

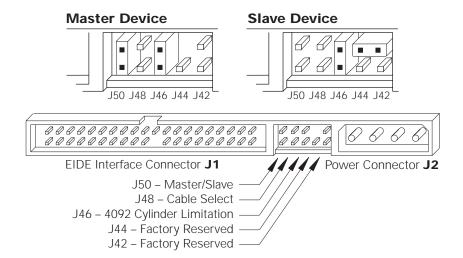

A master/slave relationship exists between the two drives: device 0 is the master and device 1 the slave. When J50 is closed (factory default, figure 2-1), the drive assumes the role of master; when open, the drive acts as a slave. In single drive configurations, J50 must be closed.

#### **Cable Select Option**

CSEL (cable select) is an optional feature per ANSI ATA specification. Drives configured in a multiple drive system are identified by CSEL's value:

- If CSEL is grounded, then the drive address is 0.

- If CSEL is open, then the drive address is 1.

### **Jumper Location/Configuration**

Darkened jumper pins indicate factory-installed (default) shunts.

Figure 2-1 PCBA Jumper Location and Configuration

## 4092 Cylinder Limitation

On some older BIOS', primarily those that auto-configure the disk drive, a hang may occur when the drive cylinder value exceeds 4096. The 4092 Cylinder Limitation jumper reduces the capacity in the Identify Drive to 4092 allowing large capacity drives to work with older BIOS'. A software driver is required to access the full capacity of the drive.

# **Product Specifications**

## **Models and Capacities**

| MODEL                                                                                                 | 88400D8  | 86480D6  | 84320D4  | 83240D3  | 82160D2  |  |

|-------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|--|

| Formatted Capacity (LBA Mode)                                                                         | 8,400 MB | 6,480 MB | 4,320 MB | 3,240 MB | 2,160 MB |  |

| Maxtor defines one megabyte as 10° or one million bytes and one gigabyte as 10° or one billion bytes. |          |          |          |          |          |  |

## **Drive Configuration**

| MODEL                             | 88400D8                    | 86480D6    | 84320D4     | 83240D3   | 82160D2   |  |

|-----------------------------------|----------------------------|------------|-------------|-----------|-----------|--|

| Integrated Controller / Interface | ATA-4 / EIDE               |            |             |           |           |  |

| Encoding Method                   |                            | Е          | PR4 RLL 16/ | 17        |           |  |

| Interleave                        |                            |            | 1:1         |           |           |  |

| Servo System                      |                            |            | Embedded    |           |           |  |

| Buffer Size / Type                |                            | 256        | KB / EDO DF | RAM       |           |  |

| Data Zones per Surface            |                            |            | 16          |           |           |  |

| Data Surfaces / Heads             | 8                          | 6          | 4           | 3         | 2         |  |

| Aerial Density                    | 1,500 Mb / in <sup>2</sup> |            |             |           |           |  |

| Tracks per Surface (Cylinders)    | 7,825                      |            |             |           |           |  |

| Track Density                     | 7,777 tpi                  |            |             |           |           |  |

| Flux Density                      | 164-209 kfci               |            |             |           |           |  |

| Recording Density                 | 155-197 kbpi               |            |             |           |           |  |

| Bytes per Sector / Block          | 512                        |            |             |           |           |  |

| Sectors per Track                 | 195-312                    |            |             |           |           |  |

| Sectors per Drive                 | 16,481,808                 | 12,658,776 | 8,439,184   | 6,329,388 | 4,219,592 |  |

# **Performance Specifications**

| MODEL                                                | 88400D8             | 86480D6 | 84320D4  | 83240D3 | 82160D2 |

|------------------------------------------------------|---------------------|---------|----------|---------|---------|

| Seek Times (typical)                                 |                     | •       | •        | •       |         |

| Track-to-track                                       |                     |         | < 1.0 ms |         |         |

| Average                                              |                     |         | < 9.7 ms |         |         |

| Maximum                                              |                     |         | 18 ms    |         |         |

| Average Latency                                      |                     |         | 5.77 ms  |         |         |

| Rotational Speed (±0.1%)                             | 5,200 RPM           |         |          |         |         |

| Controller Command Overhead                          | < 0.3 ms            |         |          |         |         |

| Data Transfer Rate                                   |                     |         |          |         |         |

| To/from Interface<br>(Ultra DMA - Mode 2)            | up to 33.0 MB/sec   |         |          |         |         |

| To/from Interface<br>(PIO 4/Multi-word DMA - Mode 2) | up to 16.7 MB/sec   |         |          |         |         |

| To/from Media                                        | 10.6 to 17.0 MB/sec |         |          |         |         |

| Start Time (0 to Drive Ready)                        | 7.3 sec typical     |         |          |         |         |

## **Physical Dimensions**

| PARAMETER | STANDARD    | METRIC            |

|-----------|-------------|-------------------|

| Height    | 1.00 inch   | 25.4 millimeters  |

| Length    | 5.75 inches | 146.1 millimeters |

| Width     | 4.00 inches | 101.6 millimeters |

| Weight    | 1.2 pounds  | 0.5 kilograms     |

Figure 3 - 1 Outline and Mounting Dimensions

## Power Requirements (Average)

| MODE           | 12V ± 8% | 5V ± 5% | POWER  |

|----------------|----------|---------|--------|

| Spin-up (peak) | 1070 mA  | 390 mA  | 14.0 W |

| Seek           | 530 mA   | 415 mA  | 8.5 W  |

| Read/Write     | 255 mA   | 445 mA  | 5.0 W  |

| Idle           | 250 mA   | 250 mA  | 4.0 W  |

| Standby        | 2 mA     | 140 mA  | 0.7 W  |

#### **Power Mode Definitions**

#### Spin-up

The drive is spinning up following initial application of power and has not yet reached full speed.

#### Seek

A random access operation by the disk drive.

#### Read/Write

Data is being read from or written to the drive.

#### Idle

The drive is spinning, the actuator is parked and powered off and all other circuitry is powered on. The drive is capable of responding to read commands within 40 ms.

#### Standby

The spin motor is not spinning. The drive will leave this mode upon receipt of a command that requires disk access. The time-out value for this mode is programmable. The buffer is active to accept write data.

## **EPA Energy Star Compliance**

Maxtor Corporation supports the goals of the U.S. Environmental Protection Agency's Energy Star program to reduce the electrical power consumption of computer equipment.

#### **Environmental Limits**

| PARAMETER                                                                           | OPERATING NON-OPERATING/STORAGE                                                                             |                                                                                                                                                     |  |  |  |  |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Temperature                                                                         | 5° C to 55° C                                                                                               | low temperature (-40° C) per MIL-STD-810E, method 502.3.                                                                                            |  |  |  |  |

|                                                                                     | high temperature (71° C) per MIL-STD-810E, method 50 climatic category; hot-induced conditions.             |                                                                                                                                                     |  |  |  |  |

| Thermal Gradient                                                                    |                                                                                                             | 25° C per hour ( <i>maximum</i> )                                                                                                                   |  |  |  |  |

| Relative Humidity                                                                   | 5                                                                                                           | 5% to 95% (non-condensing)                                                                                                                          |  |  |  |  |

| Wet Bulb                                                                            |                                                                                                             | 27° C (maximum)                                                                                                                                     |  |  |  |  |

| Altitude                                                                            | -200 to 10,000 feet<br>(with any naturally occurring<br>temperature and humidity rate within<br>this range) | Per MIL-STD-810E, method 500.3, low pressure (altitude) test procedure I. storage; test condition 2, transport aircraft cargo compartment pressure. |  |  |  |  |

| Acoustic Noise (Idle mode) 37 dBA average sound power (per ISO 7779, 10 microphone) |                                                                                                             |                                                                                                                                                     |  |  |  |  |

### **Shock and Vibration**

| PARAMETER OPERATING                                                                                                          |                                                       | NON-OPERATING                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mechanical Shock 20 Gs, 2.0 ms, no errors                                                                                    |                                                       | 150 Gs, 2.0 ms, no damage                                                                                                                                                                            |

| transportation, Vertical axis PSD profile. tra<br>10 Hz at 0.0125 G²/Hz<br>40 Hz at 0.0125 G²/Hz<br>500 Hz at 0.000125 G²/Hz |                                                       | Per MILSTD-810E, Method 514.4, Basic<br>transportation, Vertical axis PSD profile.<br>10 Hz at 0.015 G <sup>2</sup> /Hz<br>40 Hz at 0.015 G <sup>2</sup> /Hz<br>500 Hz at 0.00015 G <sup>2</sup> /Hz |

| Swept Sine Vibration<br>5 - 20 Hz<br>21 - 300 Hz                                                                             | 0.049 inches double amplitude<br>1.0 G peak amplitude |                                                                                                                                                                                                      |

## **Reliability Specifications**

#### **AFR**

< 1.7%

The annualized average failure rate (AFR) applies to the period prior to the expiration of component design life, and is based on failures chargeable to Maxtor. Determination of the AFR takes into account: a.) in-warranty field failure returns less quality acceptance-related failures and b.) an AFR equaling an exponentially weighted moving and average monthly failure rate multiplied by 12.

#### **MTBF**

> 500,000 hours

Maxtor does not differentiate between various usage profiles (e.g., power-on hours, power saving modes, non-operating periods or operating temperatures within the published specification.)

#### **Quality Acceptance Rate**

**99.85**% (< 1,500 DPPM)

The quality acceptance rate indicates the percentage of Maxtor products successfully installed by our customers, and/or the number of defective parts per million (DPPM) encountered during the entire installation process.

#### Start/Stop Cycles

**50,000** (minimum)

This indicates the minimum cycles for reliable start/stop function at a  $\geq 60\%$  confidence level.

#### **Data Reliability**

< 1 per 1013 bits read

Data errors (non-recoverable). Average data error rate allowed with all error recovery features activated.

< 1 per 10<sup>6</sup> seeks Seek errors

#### Component Design Life

5 years (minimum)

Component design life is defined as a.) the time period before identified wear-out mechanisms impact the failure rate, or b.) the time period up to the wear-out point at which useful component life expires.

#### **EMC/EMI**

#### Radiated Electromagnetic Field Emissions - EMC Compliance

The hard disk drive mechanism is designed as a subassembly for installation into a suitable enclosure and is therefore not subject to Subpart J of Part 15 of FCC Rules (47CFR15) or the Canadian Department of Communications Radio Interference Regulations. Although not required, the disk mechanism has been tested within a suitable end-use product and found to comply with Class B limits of the FCC Rules and Regulations of the Canadian Department of Communications.

The CE Marking indicates conformity with the European Union Low Voltage Directive (73/23/EEC) when the disk mechanism is installed in a typical personal computer. Maxtor recommends that testing and analysis for EMC compliance be performed with the disk mechanism installed within the user's end-use application.

#### **Canadian Emissions Statement**

This digital apparatus does not exceed the Class B limits for radio noise emissions from digital apparatus as set out in the radio interference regulations of the Canadian department of communications.

Le present appareil numerique n'emet pas de bruit radioelectriques depassant les limites applicables aux appareils numeriques de Class B prescrites dans le reglement sur le brouillage radioelectrique edicte par le ministere des communications du Canada.

#### **Radiated Magnetic Field Emissions**

Minimum of VDE Class B and MIL-STD-461/462, Method RE01 (stand-alone test configuration).

#### Radiated Electromagnetic Field Immunity

IEC 801-3, Class 2 compliance.

#### **Radiated Magnetic Field Immunity**

Per MIL-STD-461/462, Method RD01(15 Hz to 100 kHz, stand-alone test configuration).

#### Standard Test Methods

Traditional hard drive specifications are open to incorrect interpretation, but MIL-STD test methods accurately measure how products perform in real-world conditions. These methods have gained worldwide acceptance since they reflect actual environments, have well-defined test requirements, are easily understood and provide repeatable results. They objectively demonstrate to our customers the reliable, durable design of Maxtor hard drives. Each MIL-STD specification provides the basic method and condition information needed for reference by a knowledgeable Test and Qualification Engineer.

Acoustic specifications such as sound pressure are misleading because the test methods used are not controlled by recognizable standards. The sound pressure measurement itself is the least meaningful indicator of noise emissions as it relates to the human ear. The specification of sound power, loudness and sharpness are considered the most accurate acoustic measurement methodologies recognized by the leading acoustic measurement experts. ISO 7779, sound power, ISO 532B, loudness and sharpness (proposed ANSI standard by Eberhard Zwicker) are repeatable test methods providing results reproducible in any properly equipped acoustic lab.

## Safety Regulatory Compliance

All Maxtor DiamondMax™ 2160 drives comply with relevant product safety standards such as CE, CUL, TUV and UL rules and regulations. As delivered, DiamondMax 2160 hard disk drives are designed for system integration before they are used.

## Handling and Installation

#### **Pre-formatted Drive**

This Maxtor hard drive has been formatted at the factory. Do not use a low-level formatting program.

## **Important Notice**

There are a number of system BIOS's currently in use which do not support hard drives with more than 4095 cylinders (2.1 gigabytes). This section contains information describing the conditions which may identify this limitation. In order to obtain the full capacity of your Maxtor drive, you will need to follow the recommended installation instructions.

## **Hard Drive Handling Precautions**

- ◆ During handling, NEVER drop, jar, or bump a drive. Handle the drive by its sides and avoid touching the printed circuit board assembly (PCBA).

- ◆ Hard drives are sensitive to electrostatic discharge (ESD) damage. Use proper ESD practices by grounding yourself and the computer system the hard drive will be installed in.

- ◆ Allow the hard drive to reach room temperature *BEFORE* installing it in your computer system.

- ◆ NEVER switch DC power onto the drive by plugging an electrically live DC source cable into the drive's connector.

NEVER connect a live connector to the hard drive's IDE interface connector.

## **Electro-Static Discharge (ESD)**

To avoid some of the problems associated with ESD, Maxtor advises that anyone handling a disk drive use a wrist strap with an attached wire connected to an earth ground. Failure to observe these precautions voids the product warranty.

Manufacturers frequently experience "unsolved" component/hardware malfunctions often caused by ESD. To reduce the incidence of ESD-related problems, Maxtor recommends that any electronics manufacturing plans include a comprehensive ESD program, the basic elements and functions of which are outlined here:

ESD Program Element

Management

Chief coordinator

Multi-department committee

Employee training

ESD Program Function

Institute and maintain

Organize and enforce

Evaluate and improve

Educate and inform

ESD program supplies typically include: wrist- and foot-worn grounding straps; counter-top and floor antistatic matting; wrist strap testers; ESD video and training materials. Sources for such supplies include:

Static Control Systems – 3M Charleswater 225-4S, 3M Center 93 Border St.

St. Paul, MN 55144 West Newton, MA 02165-9990

Maxtor also offers a complete video training package, "Care and Handling of Maxtor Disk Drives." Contact your Maxtor representative for details.

## **Unpacking and Inspection**

Retain any packing material for reuse. Inspect the shipping container for evidence of damage in transit. Notify the carrier immediately in case of damage to the shipping container.

As they are removed, inspect drives for evidence of shipping damage or loose hardware. If a drive is damaged (and no container damage is evident), notify Maxtor immediately for drive disposition.

Figure 4 - 1 Multi-pack Shipping Container

Figure 4 - 3 Single Pack Shipping Container (Option B)

## Repacking

If a Maxtor drive requires return, repack it using Maxtor packing materials, including the antistatic bag.

## **Physical Installation**

### **Recommended Mounting Configuration**

The DiamondMax $^{\text{TM}}$  2160 drive design allows greater shock tolerance than that afforded by larger, heavier drives. The drive may be mounted in any attitude using four size 6-32 screws with 1/8-inch maximum penetration and a maximum torque of 5-inch pounds. See Figure 3-1 for mounting dimensions. Allow adequate ventilation to the drive to ensure reliable operation.

### **Drive Jumper Settings**

Figure 4-4 shows the valid jumper settings for the Maxtor hard drive.

Figure 4 - 4 Master/Slave Jumper Detail

## **Mounting Drive in System**

Turn the computer OFF, disconnect the power cord and remove the cover. Refer to your computer user's manual for additional information.

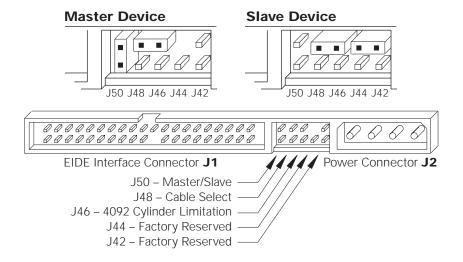

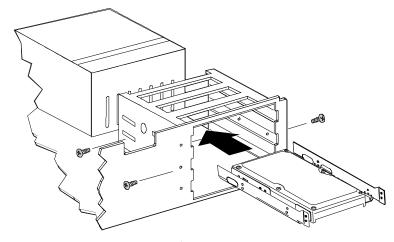

#### Installing 5.25-inch Mounting Brackets

Mounting brackets are only needed when the drive will be installed in a 5.25-inch drive bay. This step is not necessary when installing the drive in a 3.5-inch bay. See Figure 4-5 below.

#### **Mounting Rails**

Mounting rails are attached to the mounting bracket for systems requiring this feature. See Figure 4-5 below.

Figure 4 - 5 5.25-inch Mounting Brackets/Slider Rails

**Note:** The following figures are examples of typical computer systems and mounting placements. The computer system the Maxtor hard drive is being installed in may have implemented a different mounting and placement methodology.

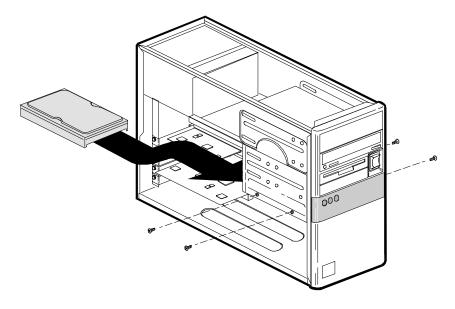

#### Mounting Drive in 5.25-inch Bay

If the Maxtor hard drive will be mounted in a 5.25-inch bay, install it as shown in Figure 4-6 below.

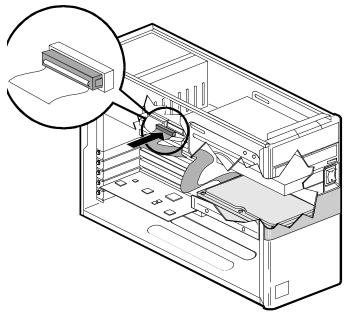

Figure 4 - 6 5.25-inch Installation

### Mounting Drive in 3.5-inch Bay

If the Maxtor hard drive will be mounted in a 3.5-inch bay, install it as shown in Figure 4-7 below.

Figure 4 - 7 3.5-inch Installation

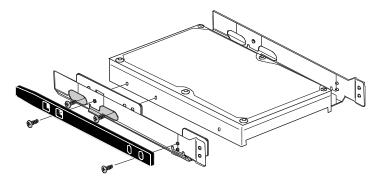

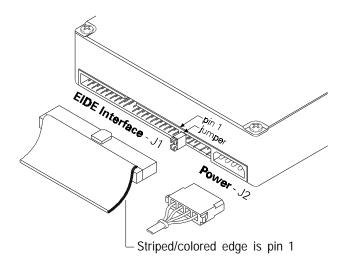

## Attaching IDE Interface and Power Cables

In order for your computer to recognize that the Maxtor hard drive is in the system, the IDE interface and power cables must be connected to the hard drive, the mother board or the IDE hard drive interface card.

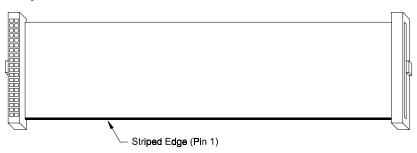

**1** Attach an available IDE interface connector to **J1** (see Figure 4-8 below) on the Maxtor hard drive. This connector is keyed and will only fit in one orientation. Do not force the connector.

The striped or colored edge of the IDE interface cable indicates pin 1. Pin 1 on the IDE interface cable should match pin 1 on the drive connector. On the Maxtor hard drive, pin 1 is closest to the power connector.

**2** Connect an available power connector to **J2** (see Figure 4-8 below) on the Maxtor hard drive. This connector is keyed and will only fit in one orientation. Do not force the connector.

Figure 4 - 8 IDE Interface and Power Cabling Detail

**IMPORTANT**: After attaching the IDE interface cable and the power cable to the Maxtor hard drive, verify that all other cables connected to other devices, the mother board or interface cards are correctly seated.

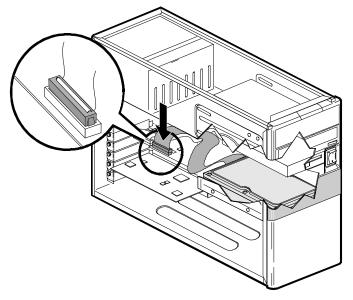

## **Attaching System Cables**

$At tach the \, 40-pin\, IDE\, interface\, cable\, from\, the\, Maxtor\, hard\, drive\, to\, the\, IDE\, connector\, on\, the\, IDE\, interface\, card.$

Figure 4 - 9 System Interface Card Cabling

Attach the 40-pin IDE interface cable from the Maxtor hard drive to the IDE connector on the mother board.

Figure 4 - 10 System Mother board Cabling

### System Setup

The following procedures are designed for systems using the DOS 5.0 (or higher) or Windows 95 operating systems. For other operating systems (e.g., OS2\*, UNIX\*, LINUX and Novell NetWare\*), refer to the operating system user's manual for the BIOS setting and other installation requirements

#### **Setting the BIOS (CMOS)**

In order for the computer system to recognize the new Maxtor hard drive, it is necessary to set the system BIOS with the correct information about the hard drive. To do this, run the system SETUP (BIOS) program.

The SETUP (BIOS) program identifies the system configuration information (e.g., floppy disk drives, hard disk drives, video, etc.) used by the computer during system boot. This includes the information about what kind and how many hard drives are attached to the system.

If you are unsure of how to access the system BIOS and/or program the BIOS settings, refer to the computers user's manual for detailed instructions.

WARNING: When entering the settings for the new Maxtor hard drive, be careful not to change any of the other BIOS settings, or other parts of the system may not work correctly.

**Note**: Most of the systems with newer BIOS' (typically with a date of July 1994 or newer), support large capacity hard drives. It is necessary to determine if the system provides support for large capacity hard drives before entering the settings, as this affects how to correctly set the BIOS parameters for the Maxtor hard drive.

#### Set the BIOS (CMOS) parameters as follows:

**IMPORTANT**: Major BIOS manufacturers like AMI, Award and Phoenix provide their core BIOS programs to system board manufacturers and OEM's who have the capability of making modifications to some of the descriptions and definitions to meet their unique requirements. These changes include, but are not limited to, how to access the BIOS, the apeearance of the information on the screens and the location of parameters within the BIOS. Refer to the system or BIOS manufacturers documentation for the correct procedure to enter the BIOS setup program for your system.

A Turn the system ON. During the system start-up sequence, run the SETUP (BIOS) program or similar commands to access the system BIOS.

**Note:** Newer systems will typically display a message (e.g., press DEL to Enter Setup) identifying how to access the SETUP (BIOS) program.

- B Once the SETUP (BIOS) program is active, do one of the following to set the hard drive BIOS parameters.

- If the SETUP program provides an "AUTO DETECT" capability, use this feature to detect the Maxtor hard drive.

**Note**: After the SETUP program has detected the hard drive, verify that the Logical Block Addressing (LBA) mode is enabled for this drive.

If the SETUP program does not provide an "AUTO DETECT" capability, set the drive parameters as defined in step 2).

**Comment:** When LBA is enabled, some BIOS programs will change the values of the cylinders and heads by dividing the cylinders by 2, 4, 8 or 16 and multiplying the heads by the same value. This does not change the capacity of the hard drive.

If the SETUP program does not provide an "AUTO DETECT" capability, the drive parameters must be set using the User Definable Type (UDT). Select the appropriate UDT for the Maxtor hard drive and set the cylinder, head and sector values for the model being installed from the table below.

#### **Drive Paramters**

| MODEL   | CYL    | HD | SPT | LZone | WPcom | CAPACITY |

|---------|--------|----|-----|-------|-------|----------|

| 88400D8 | 16,278 | 16 | 63  | (*)   | (*)   | 8,400 MB |

| 86480D6 | 13,395 | 15 | 63  | (*)   | (*)   | 6,480 MB |

| 84320D4 | 8,930  | 15 | 63  | (*)   | (*)   | 4,320 MB |

| 83240D3 | 6,697  | 15 | 63  | (*)   | (*)   | 3,240 MB |

| 82160D2 | 4,465  | 15 | 63  | (*)   | (*)   | 2,160 MB |

(\*) The fields LZone (Landing Zone) and WPcom (Write Pre-comp) are not used by the Maxtor hard drive and the values may be either 0 or the values set by the BIOS. All capacities listed in the parameters table are based on 10° or one million bytes.

Only the values for cylinders, heads and sectors listed in the table must be entered. All other values may be zero (0). Set the LBA mode to enabled for this drive. If the SETUP program does not provide the UDT, set the BIOS to the drive type with the largest capacity of those listed in the BIOS.

**C** After the drive parameters are entered, follow the SETUP program procedures to save the settings and exit the SETUP program. After changing BIOS settings, saving the values and exiting, the SETUP program should force the system to re-boot.

**Note**: Each BIOS manufacturer uses different methods of identifying the UDT. Newer BIOS' from all manufacturers will usually include an entry called "User" or "User 1." Older BIOS' vary in the method used to identify the UDT: AMI = Type 47, Award = Type 47 and Phoenix = Type 48.

#### **System Hangs During Boot**

If the system hangs after installing the Maxtor hard drive, either before or after setting the system BIOS, the system many have a BIOS with a cylinder limitation. This may occur for hard drives with capacities larger than 2.1 GB. If this happens, do the following:

1 Turn the system OFF.

- 2 Install the cylinder reduction jumper (J46) on the drive using the spare jumper shipped across pins J46 and J48; or, if the drive is installed as a Slave, store the spare jumper across J42 and J44.

- 3 If the BIOS was set to AUTO DETECT, boot the system with the MaxBlast installation software diskette to complete the hard drive installation. If other BIOS settings were used, access the system BIOS SETUP program and set the BIOS parameters to a **User Definable Type** with 4,092 cylinders, 16 heads and 63 sectors per track for the Maxtor hard drive. Then boot the system with the MaxBlast installation software diskette to complete the hard drive installation.

**IMPORTANT:** When jumper J46 is installed, the Maxtor hard drive must be prepared using the MaxBlast installation software.

## **Hard Drive Preparation**

To complete the Maxtor hard drive installation, the drive must be partitioned and formatted.

- 1 Boot the system to the bootable MaxBlast software installation diskette received with the hard drive and proceed to step 2.

- 2 The MaxBlast installation software will load and the first screen of the program will display. Complete the information in the System Configuration Information table and follow the on-screen prompts to complete the hard drive installation. To complete the installation of the Maxtor hard drive, the drive must be partitioned and formatted.

#### System/Drive Information

The first time MaxBlast installation software is run, it will display information in a format similar to the System Configuration Information table. Subsequent executions start at the main menu and allow the user to optionally display this information.

The information in the System Configuration table **must** be completed for your records. This information will be requested by the Maxtor Technical Assistance representative in the event that you call for assistance.

The Maxtor hard drive model number and serial number are also located on the top cover label of the hard drive. System information should be available in the computer users's manual or in the documentation for the different devices attached to the system.

| SYSTEM/DRIVE INFORMATION  |            |                     |  |  |

|---------------------------|------------|---------------------|--|--|

| Maxtor Hard Disk Drive    |            |                     |  |  |

| Model Number              | Serial Num | nber                |  |  |

| Computer System           |            |                     |  |  |

| Manufacturer              | Model      |                     |  |  |

| Processor (i.e., Pentium) |            | Speed (i.e., 90MHz) |  |  |

| Interface Card            |            |                     |  |  |

| Manufacturer              | Model      |                     |  |  |

| BIOS (CMOS/Setup)         |            |                     |  |  |

| Manufacturer              | Version    | Date                |  |  |

| Other Hard Disk Drive     |            |                     |  |  |

| Manufacturer              | Model      |                     |  |  |

| BIOS Setting: Cylinders   | Heads      | SPT                 |  |  |

| Other IDE Devices         |            |                     |  |  |

| Type (i.e., CD-ROM)       |            |                     |  |  |

| Manufacturer              | Model      |                     |  |  |

Once the information in this table is copied from the screen, continue with the installation or exit the MaxBlast installation software as shown on the screen. EZMAX is a menu-driven program with on-line help to guide you through the installation process.

# **AT Interface Description**

### **Interface Connector**

All DiamondMax<sup>™</sup> 2160 AT drives have a 40-pin ATA interface connector mounted on the PCBA. The drive may connect directly to the host; or it can also accommodate a cable connection (max cable length: 18 inches).

Figure 5-1 Data Connector

## **Pin Description Summary**

| PIN | SIGNAL                 | PIN | SIGNAL             |

|-----|------------------------|-----|--------------------|

| 01  | Reset -                | 02  | Ground             |

| 03  | DD7                    | 04  | DD8                |

| 05  | DD6                    | 06  | DD9                |

| 07  | DD5                    | 08  | DD10               |

| 09  | DD4                    | 10  | DD11               |

| 11  | DD3                    | 12  | DD12               |

| 13  | DD2                    | 14  | DD13               |

| 15  | DD1                    | 16  | DD14               |

| 17  | DD0                    | 18  | DD15               |

| 19  | Ground                 | 20  | (keypin)           |

| 21  | DMARQ                  | 22  | Ground             |

| 23  | DIOW -:STOP            | 24  | Ground             |

| 25  | DIOR -:HDMARDY:HSTROBE | 26  | Ground             |

| 27  | IORDY:DDMARDY:DSTROBE  | 28  | CSEL               |

| 29  | DMACK -                | 30  | Ground             |

| 31  | INTRQ                  | 32  | IOCS16<br>Obsolete |

| 33  | DA1                    | 34  | PDIAG -            |

| 35  | DA0                    | 36  | DA2                |

| 37  | CS0 -                  | 38  | CS1 -              |

| 39  | DASP -                 | 40  | Ground             |

## **Pin Description Table**

| PIN NAME                     | PIN | I/O  | SIGNAL NAME                     | SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------|-----|------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET -                      | 01  | 1    | Host Reset                      | Reset signal from the host system. Active during power up and inactive after.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DD0                          | 17  | I/O  | Host Data Bus                   | 16 bit bi-directional data bus between host and drive. Lower 8 bits used for register and ECC byte transfers. All 16 bits used for data transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DD1                          | 15  | I/O  |                                 | and Edd byte transfers. All to bits asea for data transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DD2                          | 13  | 1/0  |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |