#### **PRELIMINARY**

August 1992

# HPC167064/HPC467064 High-Performance microController with a 16k UV Erasable CMOS EPROM General Description

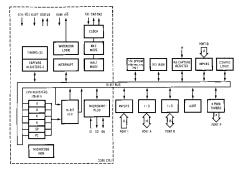

The HPC167064 is a member of the HPC family of High Performance microControllers. Each member of the family has the same core CPU with a unique memory and I/O configuration to suit specific applications. The HPC167064 has a 16 kbyte, high-speed, UV-erasable, electrically programmable CMOS EPROM. This is ideally suited for applications where fast turnaround, pattern experimentation, and code confidentiality are important requirements. The HPC167064 can serve as a stand-alone emulator for either the HPC16064 or the HPC16083. Two configuration registers have been added for emulation of the different chips. The on-chip EPROM replaces the presently available user ROM space. The on-chip EPROM can be programmed via a DATA I/O UNISITE. There are security features added to the chip to implement READ, ENCRYPTED READ, and WRITE privileges for the on-chip EPROM. These defined privileges are intended to deter theft, alteration, or unintentional destruction of user code. Each part is fabricated in National's advanced microCMOS technology. This process combined with an advanced architecture provides fast, flexible I/O control, efficient data manipulation, and high speed

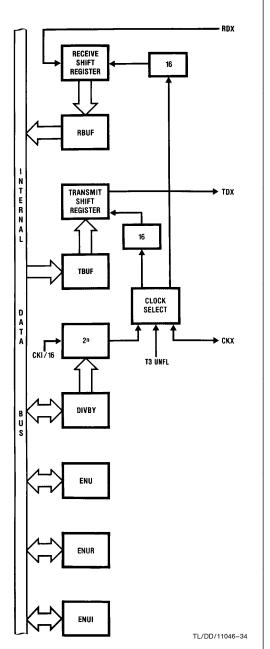

The HPC devices are complete microcomputers on a single chip. All system timing, internal logic, EPROM, RAM, and I/O are provided on the chip to produce a cost effective solution for high performance applications. On-chip functions such as UART, up to eight 16-bit timers with 4 input capture registers, vectored interrupts, WATCHDOG™ logic and MICROWIRE/PLUS™ provide a high level of system integration. The ability to address up to 64k bytes of external memory enables the HPC to be used in powerful applications typically performed by microprocessors and expensive peripheral chips.

The microCMOS process results in very low current drain and enables the user to select the optimum speed/power product for his system. The IDLE and HALT modes provide

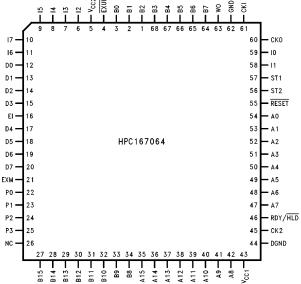

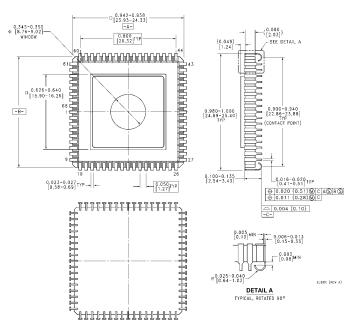

further current savings. The HPC167064 is available only in 68-pin LDCC package.

#### **Features**

- HPC family—core features:

- 16-bit architecture, both byte and word operations

- 16-bit data bus, ALU, and registers

- 64 kbytes of direct memory addressing

- FAST—200 ns for fastest instruction when using 20.0 MHz clock, 134 ns at 30.0 MHz

- High code efficiency—most instructions are single byte

- 16 x 16 multiply and 32 x 16 divide

- Eight vectored interrupt sources

- Four 16-bit timer/counters with 4 synchronous outputs and WATCHDOG logic

- MICROWIRE/PLUS serial I/O interface

- CMOS—very low power with two power save modes:

IDLE and HALT

- 16 kbytes high speed UV erasable: electrically programmable CMOS EPROM

- Stand-alone emulation of HPC16083 and HPC16064 family

- EPROM and configuration bytes programmable by DATA I/O UNISITE with Pinsite Module

- Four selectable levels of security to protect on-chip EPROM contents

- UART—full duplex, programmable baud rate

- Four additional 16-bit timer/counters with pulse width modulated outputs

- Four input capture registers

- 52 general purpose I/O lines (memory mapped)

- Commercial (0°C to +70°C), and military (-55°C to +125°C) temperature ranges for 20.0 MHz, commercial (0°C to +70°C) for 30.0 MHz

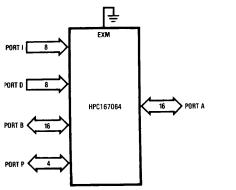

#### Block Diagram (HPC167064 with 16k EPROM shown)

TL/DD/11046-1

Series 32000® and TRI-STATE® are registered trademarks of National Semiconductor Corporation. MICROWIRE/PLUS™ and WATCHDOG™ are trademarks of National Semiconductor Corporation. UNIX® is a registered trademark of AT & T = Bell Laboratorics. IBM® and PC-AT® are registered trademarks of International Business Machines Corp.

©1995 National Semiconductor Corporation TL/DD1104

SunOS™ is a trademark of Sun Microsystems

RRD-B30M105/Printed in U. S. A.

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Total Allowable Source or Sink Current 100 mA Storage Temperature Range  $-65^{\circ}$ C to  $+150^{\circ}$ C Lead Temperature (Soldering, 10 sec.) 300°C

V<sub>CC</sub> with Respect to GND -0.5V to 7.0V

All Other Pins (V<sub>CC</sub> + 0.5V) to (GND - 0.5V)

Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. PC and AC electri-

which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

#### ad Temperature (Soldering, 10 sec.)

## **DC Electrical Characteristics**

$V_{CC}=5.0V~\pm5\%$  unless otherwise specified,  $T_A=-55^{\circ}C$  to  $+125^{\circ}C$  for HPC167064 and  $V_{CC}=5.0V~\pm~10\%$  unless otherwise specified,  $T_A=0^{\circ}C$  to  $70^{\circ}C$  for HPC467064

| Symbol                               | Parameter                                                                         | Test Conditions                                                                                                                                                                                                                    | Min                   | Max                 | Units          |

|--------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|----------------|

| I <sub>CC1</sub>                     | Supply Current                                                                    | $\begin{split} &V_{CC} = \text{max, f}_{\text{IN}} = 30.0 \text{ MHz (Note 1)} \\ &V_{CC} = \text{max, f}_{\text{IN}} = 20.0 \text{ MHz (Note 1)} \\ &V_{CC} = \text{max, f}_{\text{IN}} = 2.0 \text{ MHz (Note 1)} \end{split}$   |                       | 85<br>70<br>40      | mA<br>mA<br>mA |

| I <sub>CC2</sub>                     | IDLE Mode Current                                                                 | $\begin{array}{l} V_{CC} = \text{max, f}_{\text{IN}} = 30.0 \text{ MHz (Note 1)} \\ V_{CC} = \text{max, f}_{\text{IN}} = 20.0 \text{ MHz, (Note 1)} \\ V_{CC} = \text{max, f}_{\text{IN}} = 2.0 \text{ MHz, (Note 1)} \end{array}$ |                       | 6.0<br>4.5<br>1     | mA<br>mA<br>mA |

| I <sub>CC3</sub>                     | HALT Mode Current                                                                 | $V_{CC} = max$ , $f_{IN} = 0$ kHz, (Note 1)<br>$V_{CC} = 2.5V$ , $f_{IN} = 0$ kHz, (Note 1)                                                                                                                                        |                       | 400<br>100          | μA<br>μA       |

| INPUT VO                             | LTAGE LEVELS FOR SCHMITT TRIGGERED I                                              | NPUTS $\overline{	ext{RESET}}$ , NMI, AND $\overline{	ext{WO}}$ ; AND AL                                                                                                                                                           | SO CKI                |                     |                |

| V <sub>IH1</sub>                     | Logic High                                                                        |                                                                                                                                                                                                                                    | 0.9 V <sub>CC</sub>   |                     | V              |

| $V_{IL1}$                            | Logic Low                                                                         |                                                                                                                                                                                                                                    |                       | 0.1 V <sub>CC</sub> | ٧              |

| ALL OTHE                             | R INPUTS                                                                          |                                                                                                                                                                                                                                    |                       |                     |                |

| V <sub>IH2</sub>                     | Logic High                                                                        |                                                                                                                                                                                                                                    | 0.7 V <sub>CC</sub>   | *                   | V              |

| V <sub>IL2</sub>                     | Logic Low                                                                         |                                                                                                                                                                                                                                    | *                     | 0.2 V <sub>CC</sub> | ٧              |

| I <sub>LI1</sub>                     | Input Leakage Current                                                             | V <sub>IN</sub> = 0 and V <sub>IN</sub> = V <sub>CC</sub> (Note 4)                                                                                                                                                                 |                       | ±2                  | μΑ             |

| I <sub>LI2</sub>                     | Input Leakage Current RDY/HLD, EXUI                                               | V <sub>IN</sub> = 0                                                                                                                                                                                                                | -3                    | -50                 | μΑ             |

| I <sub>LI3</sub>                     | Input Leakage Current B12                                                         | RESET = 0, V <sub>IN</sub> = V <sub>CC</sub>                                                                                                                                                                                       | 0.5                   | 7                   | μΑ             |

| I <sub>LI4</sub>                     | Input Leakage Current EXM                                                         | V <sub>IN</sub> = 0 and V <sub>IN</sub> = V <sub>CC</sub> (Note 4)                                                                                                                                                                 | ±10                   |                     | μΑ             |

| Cl                                   | Input Capacitance                                                                 | (Note 2)                                                                                                                                                                                                                           |                       | 10                  | pF             |

| C <sub>IO</sub>                      | I/O Capacitance                                                                   | (Note 2)                                                                                                                                                                                                                           |                       | 20                  | pF             |

| OUTPUT V                             | OLTAGE LEVELS                                                                     |                                                                                                                                                                                                                                    |                       |                     |                |

| V <sub>OH1</sub><br>V <sub>OL1</sub> | Logic High (CMOS)<br>Logic Low (CMOS)                                             | $I_{OH} = -10 \mu A \text{ (Note 2)}$<br>$I_{OH} = 10 \mu A \text{ (Note 2)}$                                                                                                                                                      | V <sub>CC</sub> - 0.1 | 0.1                 | V              |

| V <sub>OH2</sub><br>V <sub>OL2</sub> | Port A/B Drive, CK2<br>(A0-A15, B10, B11, B12, B15)                               | $I_{OH} = -7 \text{ mA}$<br>$I_{OL} = 3 \text{ mA}$                                                                                                                                                                                | 2.4                   | 0.4                 | V              |

| V <sub>OH3</sub>                     | Other Port Pin Drive, WO (open drain)<br>(B0-B9, B13, B14, P0-P3)                 | $I_{OH} = -1.6 \text{ mA (except } \overline{WO})$ $I_{OL} = 0.5 \text{ mA}$                                                                                                                                                       | 2.4                   | 0.4                 | V              |

| V <sub>OH4</sub><br>V <sub>OL4</sub> | ST1 and ST2 Drive                                                                 | $I_{OH} = -6 \text{ mA}$<br>$I_{OL} = 1.6 \text{ mA}$                                                                                                                                                                              | 2.4                   | 0.4                 | ٧              |

| V <sub>OH5</sub><br>V <sub>OL5</sub> | Port A/B Drive (A0-15, B10, B11, B12, B15) when used as External Address/Data Bus | $I_{OH} = -1 \text{ mA}$<br>$I_{OL} = 3 \text{ mA}$                                                                                                                                                                                | 2.4                   | 0.4                 | V              |

| $V_{RAM}$                            | RAM Keep-Alive Voltage                                                            | (Note 3)                                                                                                                                                                                                                           | 2.5                   | V <sub>CC</sub>     | V              |

| loz                                  | TRI-STATE® Leakage Current                                                        | $V_{IN} = 0$ and $V_{IN} = V_{CC}$                                                                                                                                                                                                 |                       | ±5                  | μΑ             |

Note 1:  $|_{CC_1}$ ,  $|_{CC_2}$ ,  $|_{CC_3}$  measured with no external drive ( $I_{OH}$  and  $I_{OL}=0$ ,  $I_{IH}$ ,  $I_{IL}=0$  and EXM  $=V_{CC}$ ).  $I_{CC1}$  is measured with  $\overline{\text{RESET}}=\text{GND}$ .  $I_{CC3}$  is measured with NMI  $=V_{CC}$ . CKI driven to  $V_{IH1}$  and  $V_{IL1}$  with rise and fall times less than 10 ns.

Note 2: This is guaranteed by design and not tested.

Note 3: Test duration is 100 ms.

Note 4: The EPROM mode of operation for this device requires high voltage input on pins EXM/V<sub>PP</sub>, I3, I4, I5, I6 and I7. This will increase the input leakage current above the normal specification when driven to voltages greater than V<sub>CC</sub> +0.3V.

\*See NORMAL RUNNING MODE.

## **AC Electrical Characteristics**

(See Notes 1 and 4 and Figures 1 thru 5 ).  $V_{CC}=5V~\pm5\%^*$ ,  $T_A=-55^\circ\text{C}$  to  $+125^\circ\text{C}$  for HPC167064 and  $V_{CC}=5V~\pm10\%$ ,  $T_A=0^\circ\text{C}$  to  $+70^\circ\text{C}$  for HPC467064

|                | Symbol and Formula Parameter                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                 | Min                                                | Max               | Units                                        | Notes                            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|----------------------------------------------|----------------------------------|

|                | $f_{C}$ $t_{C1} = 1/f_{C}$ $t_{CKIH}$                                                                                                           | CKI Operating Frequency CKI Clock Period CKI High Time                                                                                                                                                                                                                                                                                                          | 2<br>50<br>22.5                                    | 20<br>500         | MHz<br>ns<br>ns                              |                                  |

| Clocks         | $t_{CKIL}$ $t_{C} = 2/f_{C}$ $t_{WAIT} = t_{C}$ $t_{DC1C2R}$                                                                                    | CKI Low Time CPU Timing Cycle CPU Wait State Period Delay of CK2 Rising Edge after CKI Falling Edge                                                                                                                                                                                                                                                             | 22.5<br>100<br>100<br>0                            | 55                | ns<br>ns<br>ns                               | (Note 2)                         |

|                | t <sub>DC1C2F</sub>                                                                                                                             | Delay of CK2 Falling Edge after CKI Falling Edge                                                                                                                                                                                                                                                                                                                | 0                                                  | 55                | ns                                           | (Note 2)                         |

|                | $f_U = f_C/8$<br>$f_{MW}$                                                                                                                       | External UART Clock Input Frequency External MICROWIRE/PLUS Clock Input Frequency                                                                                                                                                                                                                                                                               |                                                    | 2.5**<br>1.25     | MHz<br>MHz                                   |                                  |

| Timers         | $f_{XIN} = f_C/22$ $t_{XIN} = t_C$                                                                                                              | External Timer Input Frequency Pulse Width for Timer Inputs                                                                                                                                                                                                                                                                                                     | 100                                                | 0.91              | MHz<br>ns                                    |                                  |

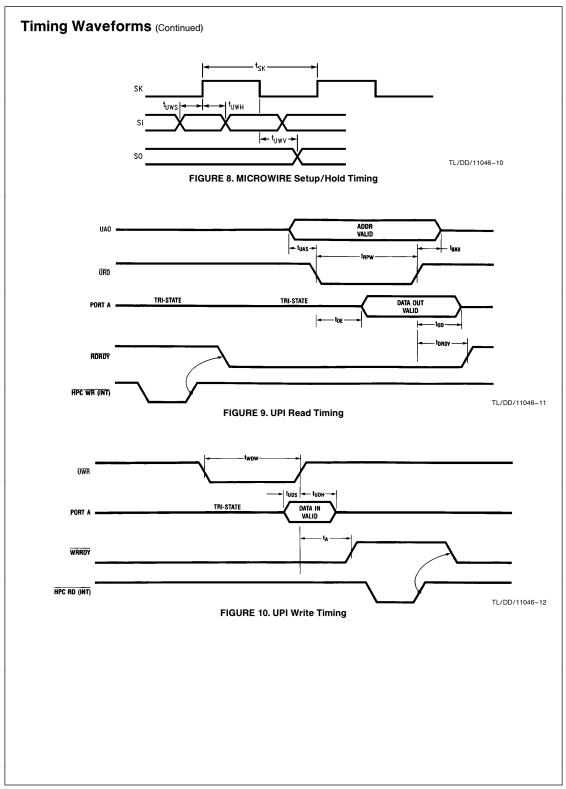

| /Plus          | t <sub>UWS</sub>                                                                                                                                | MICROWIRE Setup Time—Master MICROWIRE Setup Time—Slave                                                                                                                                                                                                                                                                                                          | 100<br>20                                          |                   | ns                                           |                                  |

| Microwire/Plus | t <sub>UWH</sub>                                                                                                                                | MICROWIRE Hold Time—Master MICROWIRE Hold Time—Slave                                                                                                                                                                                                                                                                                                            | 20<br>50                                           |                   | ns                                           |                                  |

| Mic            | t <sub>UWV</sub>                                                                                                                                | MICROWIRE Output Valid Time—Master<br>MICROWIRE Output Valid Time—Slave                                                                                                                                                                                                                                                                                         |                                                    | 50<br>150         | ns                                           |                                  |

| External Hold  | tsale = 3/4 tc + 40 thwp = tc + 10 thab = 3/4 tc + 85 the thab = 1/2 tc + 66 the the thab = 1/2 tc + 66 the |                                                                                                                                                                                                                                                                                                                                                                 | 115<br>110                                         | 200<br>160<br>116 | ns<br>ns<br>ns<br>ns<br>ns                   | (Note 3)<br>(Note 5)<br>(Note 5) |

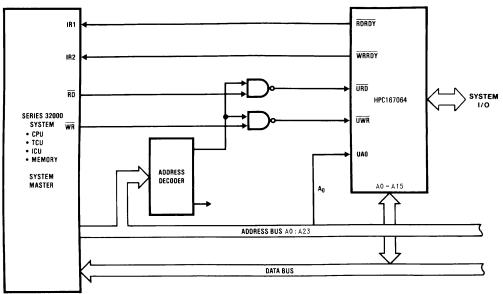

| UPI Timing     | tuas tuah tapw toe tod                                                                                      | Address Setup Time to Falling Edge of URD Address Hold Time from Rising Edge of URD URD Pulse Width URD Falling Edge to Output Data Valid Rising Edge of URD to Output Data Invalid RDRDY Delay from Rising Edge of URD UWR Pulse Width Input Data Valid before Rising Edge of UWR Input Data Hold after Rising Edge of UWR WRRDY Delay from Rising Edge of UWR | 10<br>10<br>100<br>0<br>5<br>40<br>10<br>20<br>25* | 60<br>45<br>70    | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns | (Note 6)                         |

<sup>\*</sup>See NORMAL RUNNING MODE.

Note:  $C_L = 40 \text{ pF}.$

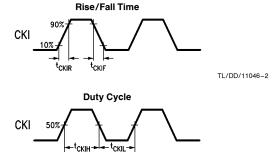

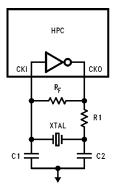

Note 1: These AC Characteristics are guaranteed with external clock drive on CKI having 50% duty cycle and with less than 15 pF load on CKO with rise and fall times (t<sub>CKIR</sub> and t<sub>CKIL</sub>) on CKI input less than 2.5 ns.

Note 2: Do not design with this parameter unless CKI is driven with an active signal. When using a passive crystal circuit, its stability is not guaranteed if either CKI or CKO is connected to any external logic other than the passive components of the crystal circuit.

Note 3: t<sub>HAE</sub> is spec'd for case with HLD falling edge occurring at the latest time can be accepted during the present CPU cycle being executed. If HLD falling edge occurs later, t<sub>HAE</sub> may be as long as (3t<sub>C</sub> + 4 WS + 72t<sub>C</sub> + 100) depending on the following CPU instruction cycles, its wait states and ready input.

Note 4: WS =  $t_{WAIT} \times$  (number of pre-programmed wait states). Minimum and maximum values are calculated at maximum operating frequency,  $t_c = 20.00$  MHz, with one wait state programmed.

Note 5: Due to emulation restrictions—actual limits will be better.

Note 6: Due to tester limitations—actual limits will be better.

<sup>\*\*</sup>This maximum frequency is attainable provided that this external baud clock has a duty cycle such that the high period includes two (2) falling edges of the CK2 clock.

AC Electrical Characteristics (Continued) (See Notes 1 and 4 and Figures 1 thru 5 .)  $V_{CC}=5V\pm5\%^*$ ,  $T_A=-55^\circ\text{C}$  to  $\pm125^\circ\text{C}$  for HPC167064 and  $V_{CC}=5V\pm10\%$ ,  $T_A=0^\circ\text{C}$  to  $\pm70^\circ\text{C}$  for HPC467064 (Continued)

|                | Symbol and Formula                                                   | Parameter                                                                                    | Min      | Max      | Units    | Notes                        |

|----------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------|----------|----------|------------------------------|

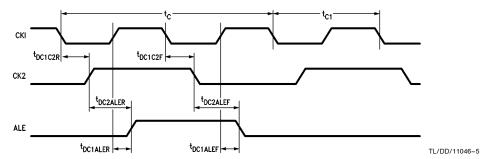

| ses            | <sup>†</sup> DC1ALER<br><sup>†</sup> DC1ALEF                         | Delay from CKI Rising Edge to ALE Rising Edge Delay from CKI Rising Edge to ALE Falling Edge |          | 35<br>35 | ns<br>ns | (Notes 1, 2)<br>(Notes 1, 2) |

| Š              | $t_{DC2ALER} = \frac{1}{4}t_{C} + 20$                                | Delay from CK2 Rising Edge to ALE Rising Edge                                                |          | 45       | ns       |                              |

| Address Cycles | $t_{DC2ALEF} = \frac{1}{4} t_{C} + 20$                               | Delay from CK2 Falling Edge to ALE Falling Edge                                              | 44       | 45       | ns       |                              |

| dre            | $t_{LL} = \frac{1}{2} t_{C} - 9$<br>$t_{ST} = \frac{1}{4} t_{C} - 7$ | ALE Pulse Width Setup of Address Valid before ALE Falling Edge                               | 41<br>18 |          | ns<br>ns |                              |

| ¥              | $t_{VP} = \frac{1}{4} t_{C} - 5$                                     | Hold of Address Valid after ALE Falling Edge                                                 | 20       |          | ns       |                              |

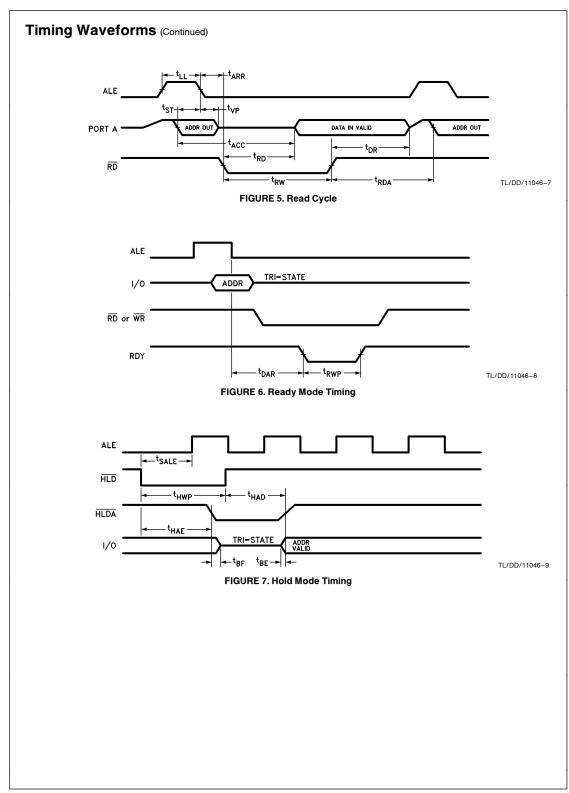

|                | $t_{ARR} = \frac{1}{4}t_{C} - 5$                                     | ALE Falling Edge to RD Falling Edge                                                          | 20       |          | ns       |                              |

| <u>e</u> s     | $t_{ACC} = t_C + WS - 55$                                            | Data Input Valid after Address Output Valid                                                  |          | 145      | ns       |                              |

| Cyc            | $t_{RD} = \frac{1}{2} t_{C} + WS - 65$                               | Data Input Valid after RD Falling Edge                                                       |          | 85       | ns       |                              |

| Read Cycles    | $t_{RW} = \frac{1}{2} t_{C} + WS - 10$                               | RD Pulse Width                                                                               | 140      |          | ns       |                              |

| Ě              | $t_{DR} = \frac{3}{4} t_{C} - 15$                                    | Hold of Data Input Valid after RD Rising Edge                                                | 0        | 60       | ns       |                              |

|                | $t_{RDA} = t_{C} - 15$                                               | Bus Enable after RD Rising Edge                                                              | 85       |          | ns       |                              |

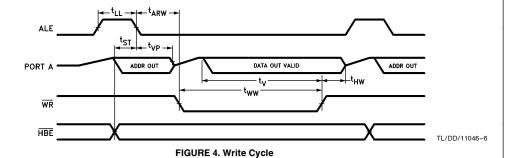

| <u>es</u>      | $t_{ARW} = \frac{1}{2}t_{C} - 5$                                     | ALE Falling Edge to WR Falling Edge                                                          | 45       |          | ns       |                              |

| Ç              | $t_{WW} = \frac{3}{4} t_{C} + WS - 15$                               | WR Pulse Width                                                                               | 160      |          | ns       |                              |

| Write Cycles   | $t_V = \frac{1}{2}t_C + WS - 5$                                      | Data Output Valid before WR Rising Edge                                                      | 145      |          | ns       |                              |

| >              | $t_{HW} = \frac{1}{4} t_{C} - 5$                                     | Hold of Data Valid after WR Rising Edge                                                      |          |          | ns       |                              |

| ≥ +-           | $t_{DAR} = \frac{1}{4} t_{C} + WS - 50$                              | Falling Edge of ALE to Falling Edge of RDY                                                   |          | 75       | ns       |                              |

| Ready          | $t_{RWR} = t_{C}$                                                    | RDY Pulse Width                                                                              | 100      |          | ns       |                              |

AC Electrical Characteristics (See Notes 1 and 4 and Figures 1 thru 5 ). V $_{CC}=5$ V  $\pm 10\%$ , T $_{A}=0$ °C to +70°C for HPC467064.

| Symbol and Formula                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                   | Parameter                                                                                                                                                                                                                                                                                                                                                       | Min                                         | Max                                   | Units                                        | Notes                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------|----------------------------------------------|----------------------------------|

| $\begin{array}{c} \textbf{f}_{C} \\ \textbf{t}_{C1} = 1/f_{C} \\ \textbf{t}_{CKIH} \\ \textbf{t}_{C} = 2/f_{C} \\ \textbf{t}_{WAIT} = \textbf{t}_{C} \\ \textbf{t}_{DC1C2R} \\ \textbf{t}_{DC1C2F} \\ \hline \textbf{f}_{U} = \textbf{f}_{C}/8 \\ \end{array}$ |                                                                                                                                                                                                                                   | CKI Operating Frequency CKI Clock Period CKI High Time CKI Low Time CPU Timing Cycle CPU Wait State Period Delay of CK2 Rising Edge after CKI Falling Edge Delay of CK2 Falling Edge after CKI Falling Edge External UART Clock Input Frequency                                                                                                                 | 2<br>33<br>22.5<br>22.5<br>66<br>66<br>0    | 30<br>500<br>55<br>55<br>55<br>3.75** | MHz ns ns ns ns ns ns ns ns MHz              | (Note 2)<br>(Note 2)             |

| Timers                                                                                                                                                                                                                                                         | f <sub>MW</sub> External MICROWIRE/PLUS Clock Input Frequency                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                 | 66                                          | 1.875                                 | MHz<br>MHz<br>ns                             |                                  |

| Plus                                                                                                                                                                                                                                                           | tuws                                                                                                                                                                                                                              | MICROWIRE Setup Time—Master MICROWIRE Setup Time—Slave                                                                                                                                                                                                                                                                                                          | 100<br>20                                   |                                       | ns                                           |                                  |

| Microwire/Plus                                                                                                                                                                                                                                                 | tuwh                                                                                                                                                                                                                              | MICROWIRE Hold Time—Master MICROWIRE Hold Time—Slave                                                                                                                                                                                                                                                                                                            | 20<br>50                                    |                                       | ns                                           |                                  |

| Micr                                                                                                                                                                                                                                                           | t <sub>UWV</sub>                                                                                                                                                                                                                  | MICROWIRE Output Valid Time—Master<br>MICROWIRE Output Valid Time—Slave                                                                                                                                                                                                                                                                                         |                                             | 50<br>150                             | ns                                           |                                  |

| External Hold                                                                                                                                                                                                                                                  | $\begin{aligned} t_{SALE} &= \frac{3}{4} t_{C} + 40 \\ t_{HWP} &= t_{C} + 10 \\ t_{HAE} &= t_{C} + 85 \\ t_{HAD} &= \frac{3}{4} t_{C} + 85 \\ t_{BF} &= \frac{1}{2} t_{C} + 66 \\ t_{BE} &= \frac{1}{2} t_{C} + 66 \end{aligned}$ | HLD Falling Edge before ALE Rising Edge HLD Pulse Width HLDA Falling Edge after HLD Falling Edge HLDA Rising Edge after HLD Rising Edge Bus Float after HLDA Falling Edge Bus Enable after HLDA Rising Edge                                                                                                                                                     | 90<br>76<br>99                              | 151<br>135<br>99                      | ns<br>ns<br>ns<br>ns<br>ns                   | (Note 3)<br>(Note 5)<br>(Note 5) |

| UPI Timing                                                                                                                                                                                                                                                     | tuas tuah tapw toe tob tod tbrdy twdw tuds tudh                                                                                                                                                                                   | Address Setup Time to Falling Edge of URD Address Hold Time from Rising Edge of URD URD Pulse Width URD Falling Edge to Output Data Valid Rising Edge of URD to Output Data Invalid RDRDY Delay from Rising Edge of URD UWR Pulse Width Input Data Valid before Rising Edge of UWR Input Data Hold after Rising Edge of UWR WRRDY Delay from Rising Edge of UWR | 10<br>10<br>100<br>0<br>5<br>40<br>10<br>20 | 60<br>45<br>70                        | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns | (Note 6)                         |

| Address Cycles                                                                                                                                                                                                                                                 | tDC1ALER tDC1ALEF tDC2ALER = 1/4 t <sub>C</sub> + 20 tDC2ALEF = 1/4 t <sub>C</sub> + 20 t <sub>LL</sub> = 1/2 t <sub>C</sub> - 9 t <sub>ST</sub> = 1/4 t <sub>C</sub> - 7 t <sub>VP</sub> = 1/4 t <sub>C</sub> - 5                | Delay from CKI Rising Edge to ALE Rising Edge Delay from CKI Rising Edge to ALE Falling Edge Delay from CK2 Rising Edge to ALE Rising Edge Delay from CK2 Falling Edge to ALE Falling Edge ALE Pulse Width Setup of Address Valid before ALE Falling Edge Hold of Address Valid after ALE Falling Edge                                                          | 0<br>0<br>24<br>9<br>11                     | 35<br>35<br>37<br>37                  | ns<br>ns<br>ns<br>ns<br>ns<br>ns             | (Notes 1, 2)<br>(Notes 1, 2)     |

## **AC Electrical Characteristics** (Continued)

(See Notes 1 and 4 and Figures 1 thru 5).  $V_{CC} = 5V \pm 10\%$ ,  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$  for HPC467064. (Continued)

|                | Symbol and Formula                     | Parameter                                           |     | Max | Units | Notes |

|----------------|----------------------------------------|-----------------------------------------------------|-----|-----|-------|-------|

|                | $t_{ARR} = \frac{1}{4}t_{C} - 5$       | ALE Falling Edge to RD Falling Edge                 | 12  |     | ns    |       |

| es             | $t_{ACC} = t_C + WS - 32$              | Data Input Valid after Address Output Valid         |     | 100 | ns    |       |

| Read Cycles    | $t_{RD} = \frac{1}{2} t_{C} + WS - 39$ | Data Input Valid after RD Falling Edge              |     | 60  | ns    |       |

| ead            | $t_{RW} = \frac{1}{2} t_{C} + WS - 14$ | RD Pulse Width                                      | 85  |     | ns    |       |

| č              | $t_{DR} = \frac{3}{4}t_{C} - 15$       | Hold of Data Input Valid after RD Rising Edge       | 0   | 35  | ns    |       |

|                | $t_{RDA} = t_{C} - 15$                 | Bus Enable after $\overline{\text{RD}}$ Rising Edge | 51  |     | ns    |       |

| es             | $t_{ARW} = \frac{1}{2}t_{C} - 5$       | ALE Falling Edge to WR Falling Edge                 | 28  |     | ns    |       |

| Cycles         | $t_{WW} = \frac{3}{4} t_{C} + WS - 15$ | WR Pulse Width                                      | 101 |     | ns    |       |

| Write (        | $t_V = \frac{1}{2} t_C + WS - 5$       | Data Output Valid before WR Rising Edge             | 94  |     | ns    |       |

| Š              | $t_{HW} = \frac{1}{4} t_{C} - 10$      | Hold of Data Valid after WR Rising Edge             | 7   |     | ns    |       |

| t J            | $t_{DAR} = \frac{1}{4}t_{C} + WS - 50$ | Falling Edge of ALE to Falling Edge of RDY          |     | 33  | ns    |       |

| Ready<br>Input | $t_{RWR} = t_{C}$                      | RDY Pulse Width                                     | 66  |     | ns    |       |

<sup>\*\*</sup>This maximum frequency is attainable provided that this external baud clock has a duty cycle such that the high period includes two (2) falling edges of the CK2 clock.

Note:  $C_L = 40 pF$ .

Note 1: These AC Characteristics are guaranteed with external clock drive on CKI having 50% duty cycle and with less than 15 pF load on CKO with rise and fall times (t<sub>CKIR</sub> and t<sub>CKIL</sub>) on CKI input less than 2.5 ns.

Note 2: Do not design with this parameter unless CKI is driven with an active signal. When using a passive crystal circuit, its stability is not guaranteed if either CKI or CKO is connected to any external logic other than the passive components of the crystal circuit.

Note 3: t<sub>HAE</sub> is spec'd for case with HLD falling edge occurring at the latest time can be accepted during the present CPU cycle being executed. If HLD falling edge occurs later, t<sub>HAE</sub> may be as long as (3t<sub>C</sub> + 4 WS + 72t<sub>C</sub> + 100) depending on the following CPU instruction cycles, its wait states and ready input.

Note 4: WS =  $t_{WAIT} \times$  (number of pre-programmed wait states). Minimum and maximum values are calculated at maximum operating frequency,  $t_c = 30.00$  MHz, with one wait state programmed.

Note 5: Due to emulation restrictions—actual limits will be better.

Note 6: Due to tester limitations—actual limits will be better.

## **CKI Input Signal Characteristics**

TL/DD/11046-3

FIGURE 1. CKI Input Signal

# **CKI Input Signal Characteristics**

TL/DD/11046-4

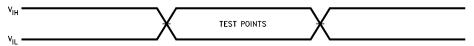

Note: AC testing inputs are driven at V<sub>IH</sub> for logic "1" and V<sub>IL</sub> for a logic "0". Output timing measurements are made at V<sub>CC</sub>/2 for both logic "1" and logic "0".

## FIGURE 2. Input and Output for AC Tests

# **Timing Waveforms**

FIGURE 3. CK1, CK2, ALE Timing Diagram

## **Functional Modes of Operation**

There are two primary functional modes of operation for the HPC167064.

- EPROM Mode

- · Normal Running Mode

#### **EPROM MODE**

In the EPROM mode, the HPC167064 is configured to "approximately emulate" a standard NMC27C256 EPROM. Some dissimilarities do exist. The most significant one is that HPC167064 contains only 16 kbytes of programmable memory, rather than the 32 kbytes in 27C256. An HPC167064 in the EPROM mode can be programmed with a Data I/O machine.

Given below is the list of functions that can be performed by the user in the EPROM mode.

Programming

CAUTION: Exceeding 14V on pin 1 (V<sub>PP</sub>) will damage the HPC167064

Initially, and after each erasure, all bits of the HPC EPROM are in the "1" state. Data is introduced by selectively programming "0s" into the desired bit locations. Although only "0s" will be programmed, both "1s" and "0s" can be presented in the data word. The only way to change a "0" to a "1" is by ultraviolet light erasure.

Program/verify EPROM registers

To read data (verify) during the programming process,  $V_{PP}$  must be at 13V. When reading data after the programming process,  $V_{PP}$  can be either 13V or at  $V_{CC}$ .

Program/verify ECON registers

There are two configuration registers ECON6 and ECON7 to emulate different family members and also to enable/disable different features in the chip. These registers are not mapped in the EPROM user space. These bytes must be programmed through a pointer register FCONA

To prevent unintentional programming, the ECON6, 7 registers must be programmed with the assistance of this pointer register. ECONA, and externally presented address, both identify the same ECON register may be programmed.

#### NORMAL RUNNING MODE

In this mode, the HPC167064 executes user software in the normal manner. By default, its arcitecture imitates that of the HPC16064. It may be configured to emulate the HPC16083. The addressable memory map will be exactly as for the HPC16083. The WATCHDOG function monitors addresses accordingly. Thus, the HPC167064 can be used as a stand-alone emulator for both HPC16064 and HPC16083. Within this mode, the on-chip EPROM cell acts as read only memory. Each memory fetch is 16-bits wide. The HPC167064 operates to 20 MHz with 1 wait state for the on-chip memory.

The HPC167064 emulates the HPC16064 and HPC16083, except as described here.

- The value of EXM is latched on the rising edge of RESET. Thus, the user may not switch from ROMed to ROMless operation or vice-versa, without another RESET pulse.

- The security logic can be used to control access to the on-chip EPROM. This feature is unique to the HPC167064. There is no corresponding mode of operation on the HPC16064 or the HPC16083.

- Specific inputs are allowed to be driven at high voltage (13V) to configure the device for programming. These high voltage inputs are unique to the HPC167064. The same inputs cannot be driven to high voltage on the HPC16064 and HPC16083 without damage to the part.

- The Port D input structure on this device is slightly different from the masked ROM HPC16083 and HPC16064. V<sub>IH2</sub> min and V<sub>IL2</sub> max are the same as for the masked ROM HPC16083 and HPC16064. There is a V<sub>IH2</sub> max requirement for this device equal to V<sub>CC</sub> + 0.05V. There is also a V<sub>IL2</sub> min requirement for this device equal to GND-0.05V. The V<sub>IH2</sub> max and V<sub>IL2</sub> min requirement for the masked ROM devices is the Absolute Maximum Ratings of V<sub>CC</sub> + 0.5V and GND-0.5V respectively.

- The D.C. Electrical Characteristics and A.C. Electrical Characteristics for the HPC167064, where  $T_A=-55^{\circ}C$  to  $+125^{\circ}C$ , are guaranteed over a reduced operating voltage range of  $V_{CC}$   $\pm5\%$ . This is different from the masked ROM devices that it simulates which is  $V_{CC}$   $\pm10\%$ . These characteristics for the HPC467064, where  $T_A=-0^{\circ}C$  to  $+70^{\circ}C$ , are guaranteed over the masked ROM operating voltage range which is  $V_{CC}$   $\pm10\%$ .

- In addition to the reduced operating voltage range for the HPC167064, the A.C. timing parameter t<sub>UDH</sub> is required to be a mimimum value of 25 ns. The masked ROM devices require a mimimum t<sub>UDH</sub> 0f 20 ns. This A.C. timing parameter for the HPC467064 is required to be the same as the masked ROM devices.

#### **HPC167064 EPROM SECURITY**

The HPC167064 includes security logic to provide READ and WRITE protection of the on-chip EPROM. These defined privileges are intended to deter theft, alteration, or unintentional destruction of user code. Two bits are used to define four levels of security on the HPC167064 to control access to on-chip EPROM.

#### Security Level 3

This is the default configuration of an erased HPC167064. READ and WRITE accesses to the on-chip EPROM or ECON registers may be accomplished without constraint in EPROM mode. READ accesses to the on-chip EPROM may be accomplished without constraint in NORMAL RUNNING mode.

## Functional Modes of Operation (Continued)

#### Security Level 2

This security level prevents programming of the on-chip EPROM or the ECON registers thereby providing WRITE protection. Read accesses to the on-chip EPROM or ECON registers may be accomplished without constraint in EPROM. Read accesses to the on-chip EPROM may be accomplished without constraint in NORMAL RUNNING mode.

#### Security Level 1

This security level prevents programming of the on-chip EPROM or ECON registers—thereby providing registers write protection. Read accesses to the on-chip ECON-registers may be accomplished without constraint in EPROM mode. Read accesses to the on-chip EPROM will produce ENCRYPTED data in EPROM. READ accesses to the onchip EPROM, during NORMAL RUNNING mode, are subject to Runtime Memory Protection. Under Runtime Memory Protection, only instruction opcodes stored within the on-chip EPROM are allowed to access the EPROM as operand. If any other instruction opcode attempts to use the contents of EPROM as an operand, it will receive the hex value "FF". The Runtime Memory Protection feature is designed to prevent hostile software, running from external memory or on-chip RAM, from reading secured EPROM data. Transfers of control into, or out of the on-chip EPROM (such as jump or branch) are not affected by Runtime Memory Protection. Interrupt vector fetches from EPROM proceed normally, and are not affected by Runtime Memory Protection.

#### Security Level 0

This security level prevents programming of the on-chip EPROM or ECON registers, thereby providing write protection. Read accesses to the on-chip ECON registers may be accomplished without constraint in EPROM mode. READ accesses to the on-chip EPROM are NOT ALLOWED in EPROM mode. Such accesses will return data value "FF" hex. Runtime Memory Protection is enforced as in security level 1.

These four levels of security help ensure that the user EPROM code is not tampered with in a test fixture and that code executing from RAM or external memory does not dump the user algorithm.

#### **Erasure Characteristics**

The erasure characteristics of the HPC167064 are such that erasure begins to occur when exposed to light with wavelengths shorter than approximately 4000 Angstroms (Å). It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000Å–4000Å range.

After programming, opaque labels should be placed over the HPC167064's window to prevent unintentional erasure. Covering the window will also prevent temporary functional failure due to the generation of photo currents.

The recommended erasure procedure for the HPC167064 is exposure to short wave ultraviolet light which has a wavelength of 2537 Angstroms (Å). The integrated dose (i.e., UV intensity × exposure time) for erasure should be a minimum of 30W-sec/cm².

The HPC167064 should be placed within 1 inch of the lamp tubes during erasure. Some lamps have a filter on their tubes which should be removed before erasure. The erasure time table shows the minimum HPC167064 erasure time for various light intensities.

An erasure system should be calibrated periodically. The distance from lamp to unit should be maintained at one inch. The erasure time increases as the square of the distance. (If distance is doubled the erasure time increases by a factor of 4.) Lamps lose intensity as they age. When a lamp is changed, the distance has changed or the lamp has aged, the system should be checked to make certain full erasure is occurring.

Incomplete erasure will cause symptoms that can be misleading. Programmers, components, and even system designs have been erroneously suspected when incomplete erasure was the problem.

Minimum HPC167064 Erasure Time

| Light Intensity<br>(Micro-Watts/cm <sup>2</sup> ) | Erasure Time<br>(Minutes) |

|---------------------------------------------------|---------------------------|

| 15,000                                            | 36                        |

| 10,000                                            | 50                        |

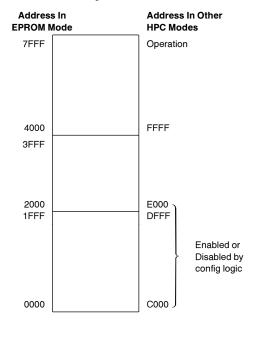

## Memory Map of the HPC167064

The HPC167064 has 256 bytes of on-chip user RAM and chip registers located at address 0000-01FF that is always enabled, and 256 bytes of on-chip RAM located at 0200-02FF that can be enabled or disabled. It has 8 kbytes of on-chip EPROM located at address 0E000-0FFFF that is always enabled and 8 kbytes of EPROM located at address 0C000-0DFFF that can be enabled or disabled.

The ECON6 contains two bits ROM0 and RAM0. When these bits are "1" (erased default), full 16 kbytes of ROM and 512 bytes of RAM are enabled. Programming a "0" to these bits disables the lower 8k for the EPROM and upper 256 bytes for the RAM. The ECON registers are only accessible to the user during EPROM mode.

## **Pin Descriptions**

The HPC167064 is available only in 68-pin LDCC package.

#### I/O PORTS

Port A is a 16-bit bidirectional I/O port with a data direction register to enable each separate pin to be individually defined as an input or output. When accessing external memory, port A is used as the multiplexed address/data bus.

Port B is a 16-bit port with 12 bits of bidirectional I/O similar in structure to Port A. Pins B10, B11, B12 and B15 are general purpose outputs only in this mode. Port B may also be configured via a 16-bit function register BFUN to individually allow each pin to have an alternate function.

| anow                                                    | cacii piii | to have an alternate fariotion.        |  |  |

|---------------------------------------------------------|------------|----------------------------------------|--|--|

| B0:                                                     | TDX        | UART Data Output                       |  |  |

| B1:                                                     |            |                                        |  |  |

| B2:                                                     | CKX        | UART Clock (Input or Output)           |  |  |

| B3:                                                     | T2IO       | Timer2 I/O Pin                         |  |  |

| B4:                                                     | T3IO       | Timer3 I/O Pin                         |  |  |

| B5:                                                     | SO         | MICROWIRE/PLUS Output                  |  |  |

| B6:                                                     | SK         | MICROWIRE/PLUS Clock (Input or Output) |  |  |

| B7:                                                     | HLDA       | Hold Acknowledge Output                |  |  |

| B8:                                                     | TS0        | Timer Synchronous Output               |  |  |

| B9:                                                     | TS1        | Timer Synchronous Output               |  |  |

| B10:                                                    | UA0        | Address 0 Input for UPI Mode           |  |  |

| B11:                                                    | WRRDY      | Write Ready Output for UPI Mode        |  |  |

| B12:                                                    |            |                                        |  |  |

| B13:                                                    | TS2        | Timer Synchronous Output               |  |  |

| B14:                                                    | TS3        | Timer Synchronous Output               |  |  |

| B15:                                                    | RDRDY      | Read Ready Output for UPI Mode         |  |  |

| When accessing external memory, four bits of port B are |            |                                        |  |  |

| used                                                    | as follows | S:                                     |  |  |

| B10:                                                    | ALE        | Address Latch Enable Output            |  |  |

| B10: ALE | Address Latch Enable Output   |

|----------|-------------------------------|

| B11: WR  | Write Output                  |

| B12: HBE | High Byte Enable Output/Input |

|          | (sampled at reset)            |

| B15: RD  | Read Output                   |

Port I is an 8-bit input port that can be read as general purpose inputs and is also used for the following functions:

| 10:                      |                    |                                                                                                      |

|--------------------------|--------------------|------------------------------------------------------------------------------------------------------|

| 11:                      | NMI                | Nonmaskable Interrupt Input                                                                          |

| 12:                      | INT2               | Maskable Interrupt/Input Capture/URD                                                                 |

| 13:                      | INT3               | Maskable Interrupt/Input Capture/UWR                                                                 |

| 14:                      | INT4               | Maskable Interrupt/Input Capture                                                                     |

| 15:                      | SI                 | MICROWIRE/PLUS Data Input                                                                            |

| 16:                      | RDX                | UART Data Input                                                                                      |

| 17:                      |                    |                                                                                                      |

| 13:<br>14:<br>15:<br>16: | INT3<br>INT4<br>SI | Maskable Interrupt/Input Capture/UW<br>Maskable Interrupt/Input Capture<br>MICROWIRE/PLUS Data Input |

Port D is an 8-bit input port that can be used as general purpose digital inputs.

Port P is a 4-bit output port that can be used as general purpose data, or selected to be controlled by timers 4 through 7 in order to generate frequency, duty cycle and pulse width modulated outputs.

#### **POWER SUPPLY PINS**

$V_{CC1}$  and

V<sub>CC2</sub> Positive Power Supply GND Ground for On-Chip Logic DGND Ground for Output Buffers

Note: There are two electrically connected  $V_{CC}$  pins on the chip, GND and DGND are electrically isolated. Both  $V_{CC}$  pins and both ground pins must be used.

#### **CLOCK PINS**

CKI The Chip System Clock Input

CKO The Chip System Clock Output (inversion of CKI) Pins CKI and CKO are usually connected across an external crystal.

CK2 Clock Output (CKI divided by 2)

#### **OTHER PINS**

WO This is an active low open drain output that signals an illegal situation has been detected by the WATCHDOG logic.

ST1 Bus Cycle Status Output: indicates first opcode fetch

ST2 Bus Cycle Status Output: indicates machine states (skip, interrupt and first instruction cycle).

RESET is an active low input that forces the chip to restart and sets the ports in a TRI-STATE mode.

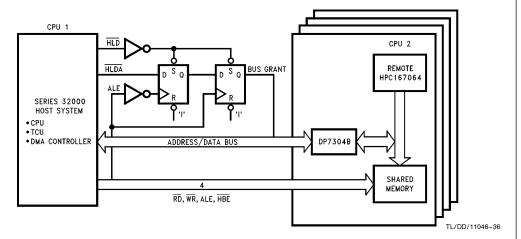

RDY/HLD has two uses, selected by a software bit. It's either an input to extend the bus cycle for slower memories, or a HOLD request input to put the bus in a high impedance state for DMA purposes

NC (no connection) do not connect anything to this

EXM Has two uses. External memory enable (active high) which disables internal EPROM and maps it to external memory, and is V<sub>PP</sub> during EPROM mode.

El External interrupt with vector address FFF1:FFF0. (Rising/falling edge or high/low level sensitive). Alternately can be configured as 4th input capture.

EXUI External interrupt which is internally OR'ed with the UART interrupt with vector address FFF3:FFF2 (Active Low).

TL/DD/11046-17 **Top View**

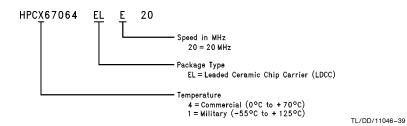

Order Number HPC167064, EL See NS Package Number EL68C

## Ports A & B

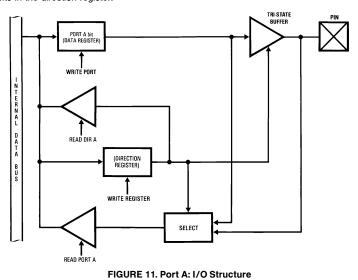

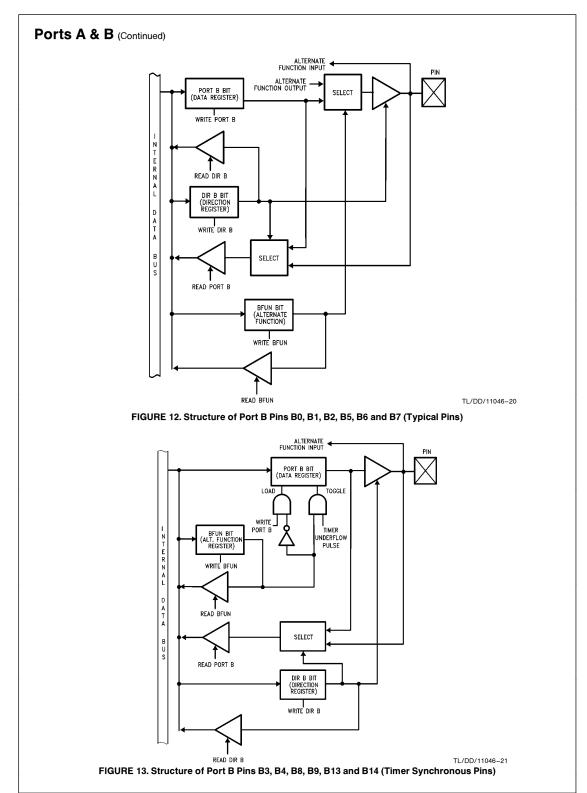

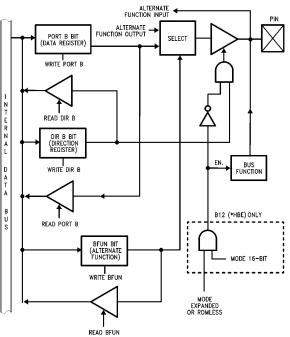

The highly flexible A and B ports are similarly structured. The Port A (see *Figure 11*), consists of a data register and a direction register. Port B (see *Figures 12* thru *Figure 14*) has an alternate function register in addition to the data and direction registers. All the control registers are read/write registers.

The associated direction registers allow the port pins to be individually programmed as inputs or outputs. Port pins selected as inputs are placed in a TRI-STATE mode by resetting corresponding bits in the direction register.

A write operation to a port pin configured as an input causes the value to be written into the data register, a read operation returns the value of the pin. Writing to port pins configured as outputs causes the pins to have the same value, reading the pins returns the value of the data register.

Primary and secondary functions are multiplexed onto Port B through the alternate function register (BFUN). The secondary functions are enabled by setting the corresponding bits in the BFUN register.

TL/DD/11046-19

13

## Ports A & B (Continued)

FIGURE 14. Structure of Port B Pins B10, B11, B12 and B15 (Pins with Bus Control Roles)

## **Operating Modes**

To offer the user a variety of I/O and expanded memory options, the HPC167064 has four operating modes. The various modes of operation are determined by the state of both the EXM pin and the EA bit in the PSW register. The state of the EXM pin determines whether on-chip EPROM will be accessed or external memory will be accessed within the address range of the on-chip EPROM. The on-chip EPROM range of the HPC167064 is C000 to FFFF (16 kbytes).

A logic "0" state on the EXM pin will cause the HPC device to address on-chip EPROM when the Program Counter (PC) contains addresses within the on-chip EPROM address range. A logic "1" state on the EXM pin will cause the HPC device to address memory that is external to the HPC when the PC contains on-chip EPROM addresses. The function of the EA bit is to determine the legal addressing range of the HPC device. A logic "0" state in the EA bit of the PSW register does two things—addresses are limited to the on-chip EPROM range and on-chip RAM and Register range, and the "illegal address detection" feature of the WATCH-

DOG logic is engaged. A logic "1" in the EA bit enables accesses to be made anywhere within the 64 kbytes address range and the "illegal address detection" feature of the WATCHDOG logic is disabled.

TL/DD/11046-22

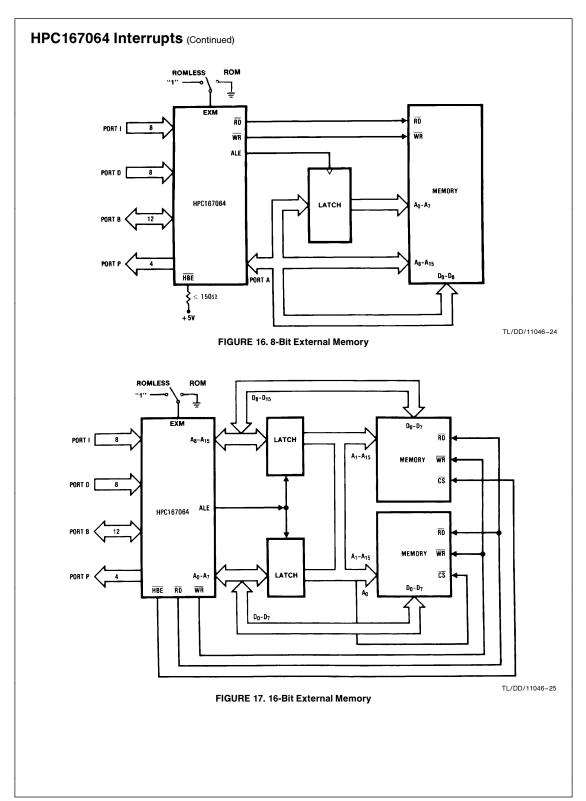

All HPC devices can be used with external memory. External memory may be any combination of RAM and EPROM. Both 8-bit and 16-bit external data bus modes are available. Upon entering an operating mode in which external memory is used, Port A becomes the Address/Data bus. Four pins of Port B become the control lines ALE, RD, WR and HBE. The High Byte Enable pin (HBE) is used in 16-bit mode to select high order memory bytes. The RD and WR signals are only generated if the selected address is off-chip. The 8-bit mode is selected by pulling HBE high at reset. If HBE is left floating or connected to a memory device chip select at reset, the 16-bit mode is entered. The following sections describe the operating modes of the HPC167064.

Note: The HPC devices use 16-bit words for stack memory. Therefore, when using the 8-bit mode, User's Stack must be in internal RAM.

## **HPC167064 Operating Modes**

#### SINGLE CHIP NORMAL MODE

In this mode, the HPC167064 functions as a self-contained microcomputer (see *Figure 15*) with all memory (RAM and EPROM) on-chip. It can address internal memory only, consisting of 16 kbytes of EPROM (C000 to FFFF) and 512 bytes of on-chip RAM and Registers (0000 to 02FF). The "illegal address detection" feature of the WATCHDOG is enabled in the Single-Chip Normal mode and a WATCHDOG Output (WO) will occur if an attempt is made to access addresses that are outside of the on-chip EPROM and RAM range of the device. Ports A and B are used for I/O functions and not for addressing external memory. The EXM pin and the EA bit of the PSW register must both be logic "0" to enter the Single-Chip Normal mode.

#### **EXPANDED NORMAL MODE**

The Expanded Normal mode of operation enables the HPC167064 to address external memory in addition to the on-chip ROM and RAM (see Table I). WATCHDOG illegal address detection is disabled and memory accesses may be made anywhere in the 64 kbyte address range without triggering an illegal address condition. The Expanded Normal mode is entered with the EXM pin pulled low (logic "0") and setting the EA bit in the PSW register to "1".

TABLE I. HPC167064 Operating Modes

| Operating Mode      | EXM<br>Pin | EA<br>Bit | Memory<br>Configuration                 |

|---------------------|------------|-----------|-----------------------------------------|

| Single-Chip Normal  | 0          | 0         | C000-FFFF On-Chip                       |

| Expanded Normal     | 0          | 1         | C000-FFFF On-Chip<br>0300-BFFF Off-Chip |

| Single-Chip ROMless | 1          | 0         | C000-FFFF Off-Chip                      |

| Expanded ROMless    | 1          | 1         | 0300-FFFF Off-Chip                      |

#### **SINGLE-CHIP ROMIess MODE**

In this mode, the on-chip EPROM of the HPC167064 is not used. The address space corresponding to the on-chip EPROM is mapped into external memory so 16k of external memory may be used with the HPC167064 (see Table I). The WATCHDOG circuitry detects illegal addresses (addresses not within the on-chip EPROM and RAM range). The Single-Chip ROMless mode is entered when the EXM pin is pulled high (logic "1") and the EA bit is logic "0".

#### **EXPANDED ROM MODE**

This mode of operation is similar to Single-Chip ROMless mode in that no on-chip ROM is used, however, a full 64 kbytes of external memory may be used. The "illegal address detection" feature of WATCHDOG is disabled. The EXM pin must be pulled high (logic "1") and the EA bit in the PSW register set to "1" to enter this mode.

## Wait States

The internal EPROM can be accessed at the maximum operating frequency with one wait state. With 0 wait states, internal ROM accesses are limited to  $^2\!\!/_3$  fC max. The HPC167064 provides four software selectable Wait States that allow access to slower memories. The Wait States are selected by the state of two bits in the PSW register. Additionally, the RDY input may be used to extend the instruction cycle, allowing the user to interface with slow memories and peripherals.

TL/DD/11046-23

FIGURE 15. Single-Chip Mode

#### **Power Save Modes**

Two power saving modes are available on the HPC167064: HALT and IDLE. In the HALT mode, all processor activities are stopped. In the IDLE mode, the on-board oscillator and timer T0 are active but all other processor activities are stopped. In either mode, all on-board RAM, registers and I/O are unaffected.

#### **HALT MODE**

The HPC167064 is placed in the HALT mode under software control by setting bits in the PSW. All processor activities, including the clock and timers, are stopped. In the HALT mode, power requirements for the HPC167064 are minimal and the applied voltage ( $V_{\rm CC}$ ) may be decreased without altering the state of the machine. There are two ways of exiting the HALT mode: via the  $\overline{\rm RESET}$  or the NMI. The  $\overline{\rm RESET}$  input reinitializes the processor. Use of the NMI input will generate a vectored interrupt and resume operation from that point with no initialization. The HALT mode can be enabled or disabled by means of a control register HALT enable. To prevent accidental use of the HALT mode the HALT enable register can be modified only once.

#### **IDLE MODE**

The HPC167064 is placed in the IDLE mode through the PSW. In this mode, all processor activity, except the onboard oscillator and Timer T0, is stopped. As with the HALT mode, the processor is returned to full operation by the RESET or NMI inputs, but without waiting for oscillator stabilization. A timer T0 overflow will also cause the HPC167064 to resume normal operation.

Note: If an NMI interrupt is received during the instruction which puts the device in Halt or Idle Mode, the device will enter that power saving mode. The interrupt will be held pending until the device exits that power saving mode. When exiting Idle mode via the TO overflow, the NMI interrupt will be serviced when the device exits Idle. If another NMI interrupt is received during either Halt of Idle the processor will exit the power saving mode and vector to the interrupt address.

## **HPC167064 Interrupts**

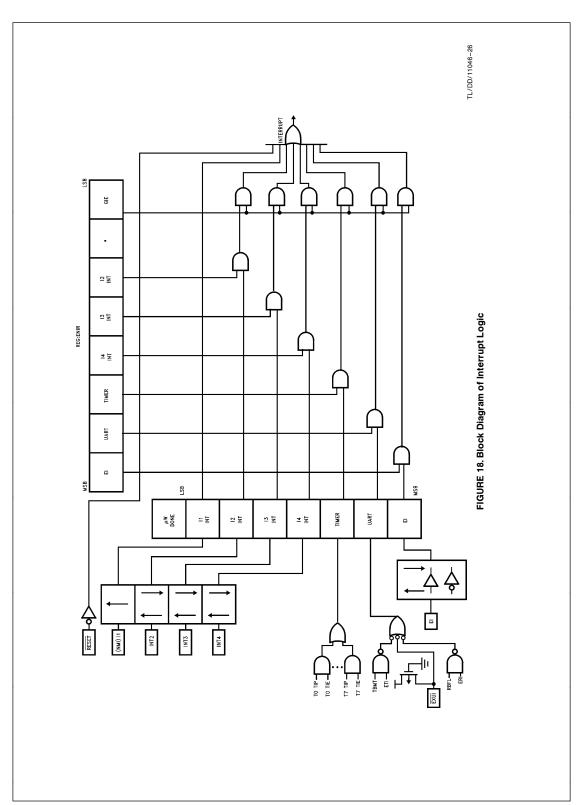

Complex interrupt handling is easily accomplished by the HPC167064's vectored interrupt scheme. There are eight possible interrupt sources as shown in Table II.

## HPC167064 Interrupts (Continued)

#### **TABLE II. Interrupts**

| Vector<br>Address | Interrupt Source                                                   | Arbitration<br>Ranking |

|-------------------|--------------------------------------------------------------------|------------------------|

| FFFF:FFFE         | RESET                                                              | 0                      |

| FFFD:FFFC         | Nonmaskable external on rising edge of I1 pin                      | 1                      |

| FFFB:FFFA         | External interrupt on I2 pin                                       | 2                      |

| FFF9:FFF8         | External interrupt on I3 pin                                       | 3                      |

| FFF7:FFF6         | External interrupt on I4 pin                                       | 4                      |

| FFF5:FFF4         | Overflow on internal timers                                        | 5                      |

| FFF3:FFF2         | Internal on the UART transmit/receive complete or external on EXUI | 6                      |

| FFF1:FFF0         | External interrupt on El pin                                       | 7                      |

## **Interrupt Arbitration**

The HPC167064 contains arbitration logic to determine which interrupt will be serviced first if two or more interrupts occur simultaneously. The arbitration ranking is given in Table II. The interrupt on RESET has the highest rank and is serviced first.

## **Interrupt Processing**

Interrupts are serviced after the current instruction is completed except for the  $\overline{\mbox{RESET}}$ , which is serviced immediately.  $\overline{\mbox{RESET}}$  and  $\overline{\mbox{EXUI}}$  are level-LOW-sensitive interrupts and EI is programmable for edge-(RISING or FALLING) or level-(HIGH or LOW) sensitivity. All other interrupts are edge-sensitive. NMI is positive-edge sensitive. The external interrupts on I2, I3 and I4 can be software selected to be rising or falling edge. External interrupt (EXUI) is shared with UART interrupt. This interrupt is level-low sensitive. To select this interrupt disable the ERI and ETI UART interrupt bits in the ENUI register. To select the UART interrupt leave this pin floating or tie it high.

## **Interrupt Control Registers**

The HPC167064 allows the various interrupt sources and conditions to be programmed. This is done through the various control registers. A brief description of the different control registers is given below.

## INTERRUPT ENABLE REGISTER (ENIR)

RESET and the External Interrupt on I1 are non-maskable interrupts. The other interrupts can be individually enabled or disabled. Additionally, a Global Interrupt Enable Bit in the ENIR Register allows the Maskable interrupts to be collectively enabled or disabled. Thus, in order for a particular interrupt to request service, both the individual enable bit and the Global Interrupt bit (GIE) have to be set.

#### INTERRUPT PENDING REGISTER (IRPD)

The IRPD register contains a bit allocated for each interrupt vector. The occurrence of specified interrupt trigger conditions causes the appropriate bit to be set. There is no indication of the order in which the interrupts have been received. The bits are set independently of the fact that the interrupts may be disabled. IRPD is a Read/Write register. The bits corresponding to the maskable, external interrupts are normally cleared by the HPC167064 after servicing the interrupts.

For the interrupts from the on-board peripherals, the user has the responsibility of resetting the interrupt pending flags through software.

The NMI bit is read only and I2, I3, and I4 are designed as to only allow a zero to be written to the pending bit (writing a one has no affect). A LOAD IMMEDIATE instruction is to be the only instruction used to clear a bit or bits in the IRPD register. This allows a mask to be used, thus ensuring that the other pending bits are not affected.

#### INTERRUPT CONDITION REGISTER (IRCD)

Three bits of the register select the input polarity of the external interrupt on I2, I3, and I4.

## **Servicing the Interrupts**

The Interrupt, once acknowledged, pushes the program counter (PC) onto the stack thus incrementing the stack pointer (SP) twice. The Global Interrupt Enable bit (GIE) is copied into the CGIE bit of the PSW register; it is then reset, thus disabling further interrupts. The program counter is loaded with the contents of the memory at the vector address and the processor resumes operation at this point. At the end of the interrupt service routine, the user does a RETI instruction to pop the stack and re-enable interrupts if the CGIE bit is set, or RET to just pop the stack if the CGIE bit is clear, and then returns to the main program. The GIE bit can be set in the interrupt service routine to nest interrupts if desired. *Figure 18* shows the Interrupt Enable Logic.

#### **RESET**

The RESET input initializes the processor and sets Ports A and B in the TRI-STATE condition and Port P in the LOW state. RESET is an active-low Schmitt trigger input. The processor vectors to FFFF:FFFE and resumes operation at the address contained at that memory location (which must correspond to an on board location). The Reset vector address must be between C000 and FFFF when emulating the HPC16064 and between E000 and FFFF when emulating the HPC16003.

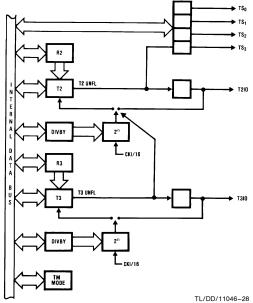

## **Timer Overview**

The HPC167064 contains a powerful set of flexible timers enabling the HPC167064 to perform extensive timer functions not usually associated with microcontrollers. The HPC167064 contains nine 16-bit timers. Timer T0 is a free-running timer, counting up at a fixed CKI/16

## Timer Overview (Continued)

(Clock Input/16) rate. It is used for WATCHDOG logic, high speed event capture, and to exit from the IDLE mode. Consequently, it cannot be stopped or written to under software control. Timer T0 permits precise measurements by means of the capture registers I2CR, I3CR, and I4CR. A control bit in the register TMMODE configures timer T1 and its associated register R1 as capture registers I3CR and I2CR. The capture registers I2CR, I3CR, and I4CR respectively, record the value of timer T0 when specific events occur on the interrupt pins I2, I3, and I4. The control register IRCD programs the capture registers to trigger on either a rising edge or a falling edge of its respective input. The specified edge can also be programmed to generate an interrupt (see *Figure 19*).

The HPC167064 provides an additional 16-bit free running timer, T8, with associated input capture register EICR (External Interrupt Capture Register) and Configuration Register, EICON. EICON is used to select the mode and edge of the EI pin. EICR is a 16-bit capture register which records the value of T8 (which is identical to T0) when a specific event occurs on the EI pin.

The timers T2 and T3 have selectable clock rates. The clock input to these two timers may be selected from the following two sources: an external pin, or derived internally by

TO WATCHDOG

CKI/16

TS

TO

TO OVFL

FICE

I 2CR

I 3CR

I 4CR

I 4CR

I 4CR

I 1 SOFTWARE

CONFIGURED

CKI/16

TL/DD/11046-27

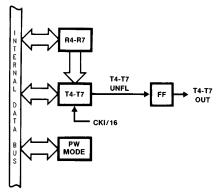

FIGURE 19. Timers T0, T1 and T8 with Four Input Capture Registers