# NI 5422 Specifications

### NI PXI-5422 16-Bit 200 MS/s Arbitrary Waveform Generator

Unless otherwise noted, the following conditions were used for each specification:

- Analog Filter enabled.

- Signals terminated with 50  $\Omega$ .

- Direct Path set to 1  $V_{pk-pk}$ , Low-Gain Amplifier Path set to 2  $V_{pk-pk}$ , and High-Gain Amplifier Path set to 12  $V_{pk-pk}$ .

- Sample rate set to 200 MS/s and the Sample Clock Source set to Divide-by-*N*.

Typical values are representative of an average unit operating at room temperature (20 °C  $\pm$ 3 °C). Specifications are subject to change without notice. For the most recent NI 5422 specifications, visit ni.com/manuals.

To access all of the NI 5422 documentation, including the *NI Signal Generators Getting Started Guide*, which contains functional descriptions of the NI 5422 signals, navigate to **Start»Programs»National Instruments»NI-FGEN»Documentation**.

**Hot Surface** If the NI 5422 has been in use, it may exceed safe handling temperatures and cause burns. Allow the NI 5422 to cool before removing it from the chassis.

# Contents

| СН 0                                    | 2 |

|-----------------------------------------|---|

| Sample Clock                            |   |

| Onboard Clock                           |   |

| Phase-Locked Loop (PLL) Reference Clock |   |

| CLK IN                                  |   |

| PFI 0 and PFI 1                         |   |

| DIGITAL DATA & CONTROL (DDC)            |   |

| Start Trigger                           |   |

| Markers                                 |   |

| Arbitrary Waveform Generation Mode      |   |

| Calibration                             |   |

| Power                                   |   |

| Software                                |   |

|                                         |   |

| Environment                                              | 32 |

|----------------------------------------------------------|----|

| Safety, Electromagnetic Compatibility, and CE Compliance | 33 |

| Physical                                                 | 35 |

| Where to Go for Support                                  | 36 |

### **CH O** (Channel O Analog Output, Front Panel Connector)

| Specification         | Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Comments |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Number of<br>Channels | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —        |

| Connector             | SMB (jack)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —        |

| Output Voltage        | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| Output Paths          | <ol> <li>The software-selectable Main Output Path setting<br/>provides full-scale voltages from 12.00 V<sub>pk-pk</sub> to<br/>5.64 mV<sub>pk-pk</sub> into a 50 Ω load. NI-FGEN uses either the<br/>Low-Gain Amplifier or the High-Gain Amplifier when<br/>the Main Output Path is selected, depending on the Gain<br/>attribute.</li> <li>The software-selectable Direct Path is optimized for<br/>IF applications and provides full-scale voltages from<br/>1.000 V<sub>pk-pk</sub> to 0.707 V<sub>pk-pk</sub>.</li> </ol> |          |

| DAC<br>Resolution     | 16 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | —        |

#### Table 1.

Table 1. (Continued)

| Specification           |                                                                              | Comments            |               |                          |                                                                                                      |  |  |

|-------------------------|------------------------------------------------------------------------------|---------------------|---------------|--------------------------|------------------------------------------------------------------------------------------------------|--|--|

| Amplitude and Offset    |                                                                              |                     |               |                          |                                                                                                      |  |  |

| Amplitude               |                                                                              |                     | Amplitu       | de (V <sub>pk-pk</sub> ) | 1. Amplitude                                                                                         |  |  |

| Range                   | Path                                                                         | Load                | Minimum Value | Maximum Value            | values assume the full scale                                                                         |  |  |

|                         | Direct                                                                       | 50 Ω                | 0.707         | 1.00                     | of the DAC is utilized. If an                                                                        |  |  |

|                         |                                                                              | 1 kΩ                | 1.35          | 1.91                     | amplitude                                                                                            |  |  |

|                         | Low-<br>Gain<br>Amplifier                                                    | Open                | 1.41          | 2.00                     | smaller than the minimum                                                                             |  |  |

|                         |                                                                              | 50 Ω                | 0.00564       | 2.00                     | <ul> <li>value is</li> <li>desired, then</li> <li>waveforms less</li> <li>than full scale</li> </ul> |  |  |

|                         |                                                                              | $1 \text{ k}\Omega$ | 0.0107        | 3.81                     |                                                                                                      |  |  |

|                         |                                                                              | Open                | 0.0113        | 4.00                     | of the DAC can be used.                                                                              |  |  |

|                         | High-<br>Gain<br>Amplifier                                                   | 50 Ω                | 0.0338        | 12.0                     | 2. NI-FGEN<br>compensates<br>for user-<br>specified<br>resistive loads.                              |  |  |

|                         |                                                                              | 1 kΩ                | 0.0644        | 22.9                     |                                                                                                      |  |  |

|                         |                                                                              | Open                | 0.0676        | 24.0                     |                                                                                                      |  |  |

| Amplitude<br>Resolution | 3 digits                                                                     |                     |               |                          |                                                                                                      |  |  |

| Offset Range            | Span of ±50% of Amplitude Range with increments <0.0028% of Amplitude Range. |                     |               |                          | Not available on the Direct Path.                                                                    |  |  |

Table 1. (Continued)

| Specification            |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Value  | Comments                              |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------|--|

| Maximum Output Voltage   |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                                       |  |

| Maximum                  | Path                                                                                                                          | The combination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                                       |  |

| Output<br>Voltage        | Direct                                                                                                                        | 50 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ±0.500 | of Amplitude and<br>Offset is limited |  |

|                          |                                                                                                                               | 1 kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ±0.953 | by the Maximum<br>Output Voltage.     |  |

|                          |                                                                                                                               | Open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ±1.000 | - Output Voluge.                      |  |

|                          | Low-                                                                                                                          | 50 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ±1.000 |                                       |  |

|                          | Gain<br>Amplifier                                                                                                             | 1 kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ±1.905 |                                       |  |

|                          | -                                                                                                                             | Open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ±2.000 |                                       |  |

|                          | High-                                                                                                                         | 50 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ±6.000 |                                       |  |

|                          | Gain<br>Amplifier                                                                                                             | 1 kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ±11.43 |                                       |  |

|                          | _                                                                                                                             | Open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ±12.00 |                                       |  |

| Accuracy                 |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                                       |  |

| DC Accuracy              | $\pm 0.2\%$ of<br>(within $\pm$<br>$\pm 0.4\%$ of<br>(0 °C to 5<br>For the D<br>Gain Acc<br>temperatu<br>Gain Acc<br>DC Offse | For the Low-Gain or High-Gain Amplifier Path:<br>$\pm 0.2\%$ of Amplitude $\pm 0.05\%$ of Offset $\pm 500 \mu\text{V}$<br>(within $\pm 10 ^{\circ}\text{C}$ of self-calibration temperature)<br>$\pm 0.4\%$ of Amplitude $\pm 0.05\%$ of Offset $\pm 1 \text{mV}$<br>(0 $^{\circ}\text{C}$ to 55 $^{\circ}\text{C}$ )<br>For the Direct Path:<br>Gain Accuracy: $\pm 0.2\%$ (within $\pm 10 ^{\circ}\text{C}$ of self-calibration<br>temperature)<br>Gain Accuracy: $\pm 0.4\%$ (0 $^{\circ}\text{C}$ to 55 $^{\circ}\text{C}$ )<br>DC Offset Error: $\pm 30 \text{mV}$ (0 $^{\circ}\text{C}$ to 55 $^{\circ}\text{C}$ ) |        |                                       |  |

| AC Amplitude<br>Accuracy | $\pm 1.0\%$ of desired Amplitude $\pm 1 \text{ mV}$                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | 50 kHz sine<br>wave.                  |  |

| Output Charac            | teristics                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                                       |  |

| Output<br>Impedance      | 50 $\Omega$ nom                                                                                                               | ninal or 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —      |                                       |  |

| Output<br>Coupling       | DC                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                                       |  |

Table 1. (Continued)

| Specification                 |                                                                                      | Comments                                                                   |            |            |

|-------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------|------------|

| Output Charac                 |                                                                                      |                                                                            |            |            |

| Output Enable                 | Software-selectable<br>CH 0 Output is terr<br>equal to the selecte                   |                                                                            |            |            |

| Maximum<br>Output<br>Overload | The CH 0 output ca<br>(±8 V for the Direc<br>damage. No damag<br>ground indefinitely |                                                                            | —          |            |

| Waveform<br>Summing           | The CH 0 output su<br>similar paths—spec<br>signal generators ca                     | of multiple NI 5422                                                        | —          |            |

| Frequency and                 | Transient Response                                                                   | 9                                                                          |            |            |

| Analog<br>Filter              | er for image                                                                         | Available on<br>Low-Gain<br>Amplifier and<br>High-Gain<br>Amplifier Paths. |            |            |

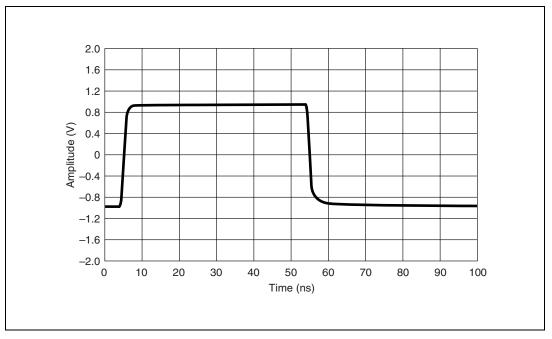

| Pulse                         |                                                                                      |                                                                            | Values are |            |

| Response                      | Direct                                                                               | typical. Analog<br>Filter disabled.<br>Measured with a                     |            |            |

| Rise/Fall Time                | 1.0 ns                                                                               | 2.1 ns                                                                     | 4.8 ns     | 1 m RG-223 |

| Aberration                    | 16%                                                                                  | 6%                                                                         | 8%         | cable.     |

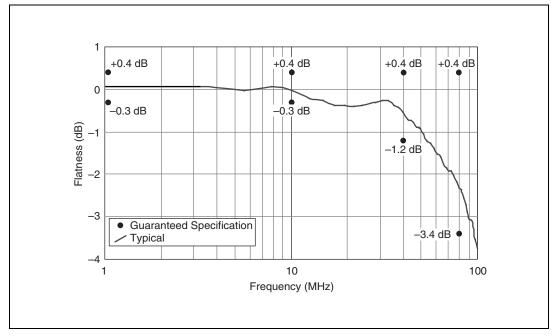

Figure 1. Normalized Passband Flatness, Direct Path

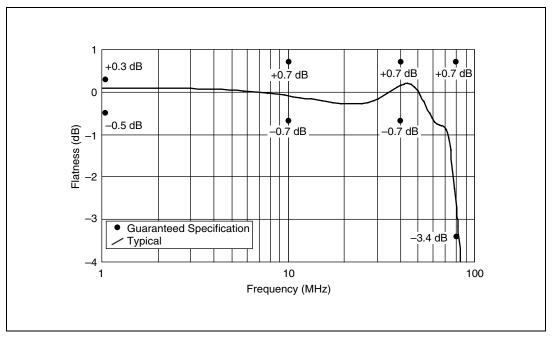

Figure 2. Normalized Passband Flatness, Low-Gain Amplifier Path

Figure 3. Normalized Passband Flatness, High-Gain Amplifier Path

Figure 4. Pulse Response, Low-Gain Amplifier Path with a 50  $\Omega$  Load

Table 1. (Continued)

| Specification |                                                    | Comments                                  |        |                                                    |  |  |  |

|---------------|----------------------------------------------------|-------------------------------------------|--------|----------------------------------------------------|--|--|--|

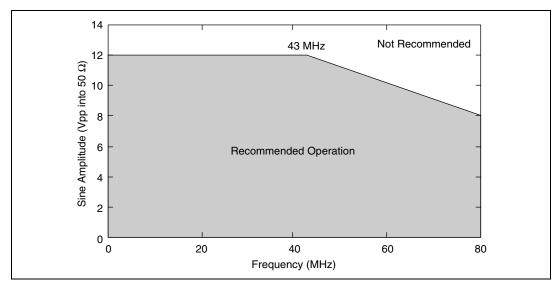

| Suggested Max | Suggested Maximum Frequencies for Common Functions |                                           |        |                                                    |  |  |  |

| Function      |                                                    | Disable the                               |        |                                                    |  |  |  |

|               | Direct                                             | Low-GainHigh-GainDirectAmplifierAmplifier |        | Analog Filter for<br>square, ramp,<br>and triangle |  |  |  |

| Sine          | 80 MHz                                             | Iz 80 MHz 43 MHz                          |        | functions.                                         |  |  |  |

| Square        | Not Recommended                                    | Recommended 50 MHz 25 MHz                 |        |                                                    |  |  |  |

| Ramp          | Not Recommended                                    | Not Recommended 10 MHz 10 MHz             |        |                                                    |  |  |  |

| Triangle      | Not Recommended                                    | 10 MHz                                    | 10 MHz |                                                    |  |  |  |

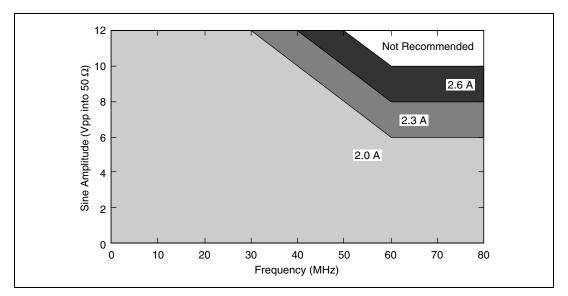

Figure 5. Recommended Sine Wave Frequency Versus Amplitude

Table 1. (Continued)

| Specification                     |         | Comments              |                        |                                                |  |  |

|-----------------------------------|---------|-----------------------|------------------------|------------------------------------------------|--|--|

| Spectral Characteristics          |         |                       |                        |                                                |  |  |

| Spurious-Free<br>Dynamic          |         | Path                  | 1                      | Amplitude<br>–1 dBFS.                          |  |  |

| Range<br>(SFDR) with<br>Harmonics | Direct  | Low-Gain<br>Amplifier | High-Gain<br>Amplifier | Measured from<br>DC to 100 MHz.<br>Also called |  |  |

| 1 MHz                             | -70 dBc | -65 dBc               | -66 dBc                | harmonic<br>distortion.                        |  |  |

| 5 MHz                             | -70 dBc | -65 dBc               | -58 dBc                | SFDR with<br>harmonics at low                  |  |  |

| 10 MHz                            | -70 dBc | -65 dBc               | -52 dBc                | amplitudes is                                  |  |  |

| 20 MHz                            | -63 dBc | -64 dBc               | -49 dBc                | limited by a<br>-148 dBm/Hz                    |  |  |

| 30 MHz                            | -57 dBc | -60 dBc               | -43 dBc                | noise floor. All                               |  |  |

| 40 MHz                            | -48 dBc | -53 dBc               | -39 dBc                | values are<br>typical and                      |  |  |

| 50 MHz                            | -48 dBc | -53 dBc               | —                      | include aliased                                |  |  |

| 60 MHz                            | -47 dBc | -52 dBc               |                        | harmonics.                                     |  |  |

| 70 MHz                            | -47 dBc | -52 dBc               |                        |                                                |  |  |

| 80 MHz                            | -41 dBc | -52 dBc               |                        |                                                |  |  |

Table 1. (Continued)

| Specification                           |                | Value              |               |                        |                        |                       |                                                                     |  |  |

|-----------------------------------------|----------------|--------------------|---------------|------------------------|------------------------|-----------------------|---------------------------------------------------------------------|--|--|

| Spectral Chara                          | cteristics (Co | ontinued           | )             |                        |                        |                       |                                                                     |  |  |

| Spurious-Free<br>Dynamic                | Path           |                    |               |                        |                        | Amplitude<br>–1 dBFS. |                                                                     |  |  |

| Range<br>(SFDR)<br>without<br>Harmonics | Direc          | et                 |               | -Gain<br>lifier        | High-Gain<br>Amplifier |                       | Measured from<br>DC to 100 MHz.<br>SFDR without<br>harmonics at low |  |  |

| 1 MHz                                   | –85 dB         | FS                 | -80 0         | dBFS                   | –77 d                  | BFS                   | amplitudes is limited by a                                          |  |  |

| 5 MHz                                   | –85 dB         | FS                 | -80 0         | dBFS                   | –77 d                  | BFS                   | -148 dBm/Hz                                                         |  |  |

| 10 MHz                                  | -80 dB         | SFS                | -80 0         | dBFS                   | –77 d                  | BFS                   | noise floor.<br>All values are                                      |  |  |

| 20 MHz                                  | -80 dB         | SFS                | -80 0         | dBFS                   | –77 d                  | BFS                   | typical and include aliased                                         |  |  |

| 30 MHz                                  | -73 dB         | SFS                | -71 0         | dBFS                   | 68 d                   | BFS                   | harmonics.                                                          |  |  |

| 40 MHz                                  | -48 dB         | SFS                | -58 0         | dBFS                   | –55 d                  | BFS                   |                                                                     |  |  |

| 50 MHz                                  | -48 dB         | SFS                | -53 0         | -53 dBFS —             |                        | -                     |                                                                     |  |  |

| 60 MHz                                  | –47 dB         | SFS                | -52 0         | dBFS                   | —                      |                       |                                                                     |  |  |

| 70 MHz                                  | -47 dB         | SFS                | –52 dBFS      |                        |                        |                       |                                                                     |  |  |

| 80 MHz                                  | -41 dB         | SFS                | -52 dBFS      |                        |                        | -                     |                                                                     |  |  |

| Average Noise<br>Density                |                | -                  | litude<br>nge | Avera                  | rage Noise Density     |                       | Average Noise<br>Density at small                                   |  |  |

|                                         | Path           | V <sub>pk-pk</sub> | dBm           | $\frac{nV}{\sqrt{Hz}}$ | dBm/Hz                 | dBFS/<br>Hz           | amplitudes is<br>limited by a<br>–168 dBm/Hz                        |  |  |

|                                         | Direct         | 1.00               | 4.0           | 19.9                   | -141                   | -145                  | noise floor.                                                        |  |  |

|                                         | Low Gain       | 0.06               | -20.5         | 1.3                    | -164                   | -144                  |                                                                     |  |  |

|                                         | Low Gain       | 0.10               | -16.0         | 2.2                    | -160                   | -144                  | ]                                                                   |  |  |

|                                         | Low Gain       | 0.40               | -4.0          | 8.9                    | -148                   | -144                  |                                                                     |  |  |

|                                         | Low Gain       | 1.00               | 4.0           | 22.3                   | -140                   | -144                  | ]                                                                   |  |  |

|                                         | Low Gain       | 2.00               | 10.0          | 44.6                   | -134                   | -144                  | ]                                                                   |  |  |

|                                         | High Gain      | 4.00               | 16.0          | 93.8                   | -128                   | -144                  | ]                                                                   |  |  |

|                                         | High Gain      | 12.00              | 25.6          | 281.5                  | -118                   | -144                  |                                                                     |  |  |

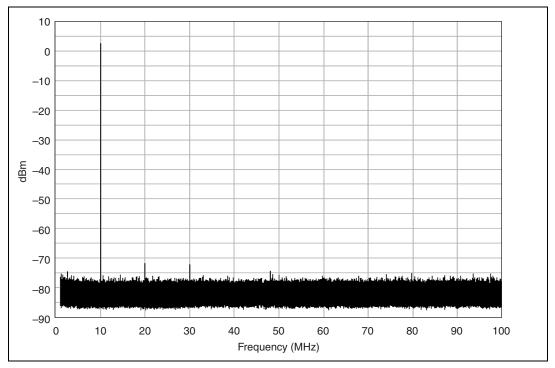

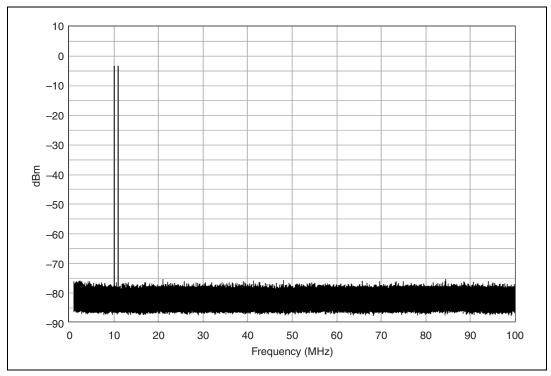

Figure 6. 10 MHz Single-Tone Spectrum, Direct Path, 200 MS/s (Typical)

**Note** The noise floor in Figure 6 is limited by the measurement device. Refer to the *Average Noise Density* specification.

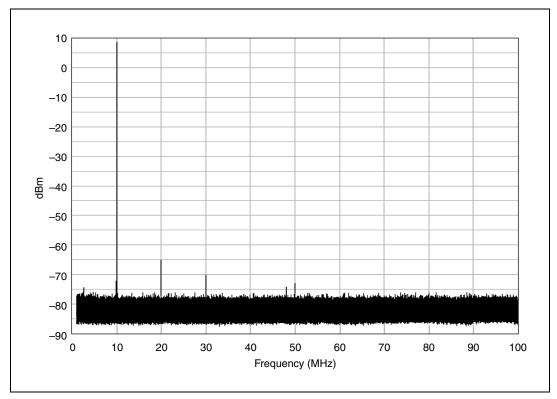

Figure 7. 10.00001 MHz Single-Tone Spectrum, Low-Gain Amplifier Path, 200 MS/s (Typical)

**Note** The noise floor in Figure 7 is limited by the measurement device. Refer to the *Average Noise Density* specification.

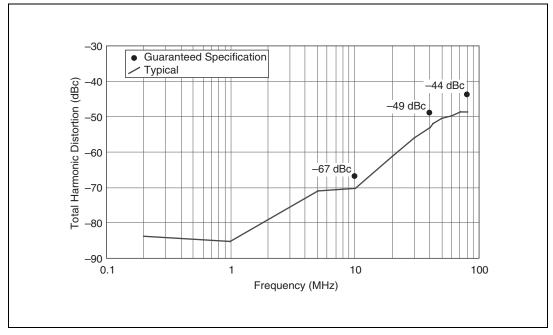

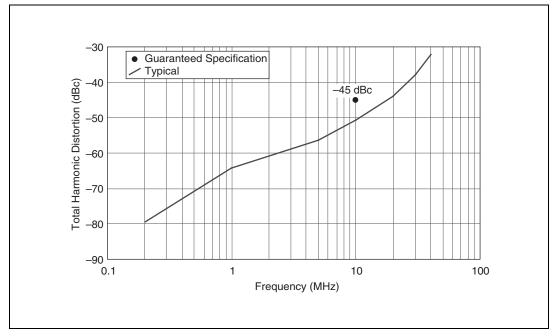

Figure 8. Total Harmonic Distortion, Direct Path

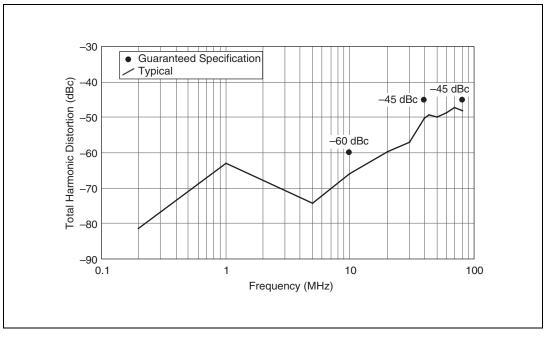

Figure 9. Total Harmonic Distortion, Low-Gain Amplifier Path

Figure 10. Total Harmonic Distortion, High-Gain Amplifier Path

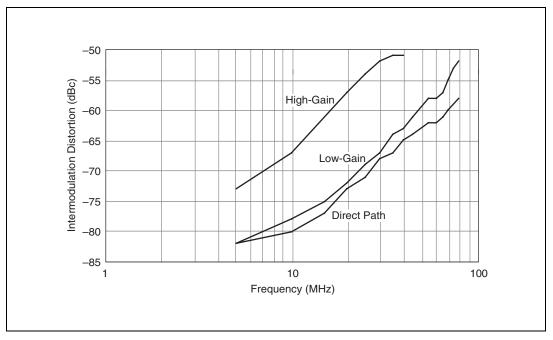

Figure 11. Intermodulation Distortion, 200 kHz Separation (Typical)

Figure 12. Direct Path, Two-Tone Spectrum (Typical)

**Note** The noise floor in Figure 12 is limited by the noise floor of the measurement device. Refer to the *Noise Floor* specification.

| Specification | Value                                                                                                                                             | Comments                                                            |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Sources       | <ol> <li>Internal, Divide-by-N (N ≥ 1)</li> <li>Internal, DDS-based, High-Resolution</li> </ol>                                                   | Refer to the<br>Onboard Clock                                       |

|               | <ol> <li>External, CLK IN (SMB front panel connector)</li> <li>External, DDC CLK IN (DIGITAL DATA &amp; CONTROL front panel connector)</li> </ol> | section for more<br>information<br>about Internal<br>Clock Sources. |

|               | <ul><li>5. External, PXI Star trigger (backplane connector)</li><li>6. External, PXI_Trig&lt;07&gt; (backplane connector)</li></ul>               |                                                                     |

# Sample Clock

R

Table 2

Table 2. (Continued)

| Specification                   | V                                           | alue                                                   | Comments |

|---------------------------------|---------------------------------------------|--------------------------------------------------------|----------|

| Sample Rate Rat                 | nge and Resolution                          |                                                        |          |

| Sample Clock<br>Source          | Sample Rate Range                           |                                                        |          |

| Divide-by-N                     | 5 MS/s to 200 MS/s                          | Settable to (200 MS/s)/N<br>( $1 \le N \le 40$ )       |          |

| High<br>Resolution              | 5 MS/s to 100 MS/s<br>>100 MS/s to 200 MS/s | 1.06 μHz<br>4.24 μHz                                   |          |

| CLK IN                          | 5 MS/s to 200 MS/s                          | Resolution determined by                               |          |

| DDC CLK IN                      | 5 MS/s to 200 MS/s                          | external clock source.                                 |          |

| PXI Star<br>Trigger             | 5 MS/s to 105 MS/s                          | External Sample Clock duty cycle tolerance 40% to 60%. |          |

| PXI_Trig<07>                    | 5 MS/s to 20 MS/s                           |                                                        |          |

| Sample Clock De                 | elay Range and Resolution                   | ·                                                      |          |

| Sample Clock<br>Source          | Delay Adjustment<br>Range                   | Delay Adjustment<br>Resolution                         | _        |

| Divide-by-N                     | ±1 sample clock period                      | <5 ps                                                  |          |

| High-<br>Resolution<br>≤100 MHz | ±1 sample clock period                      | Sample Clock<br>Period/16,384                          |          |

| High-<br>Resolution<br>>100 MHz | ±1 sample clock period                      | Sample Clock<br>Period/4,096                           |          |

| External (all)                  | 0 ns to 7.6 ns                              | <15 ps                                                 |          |

Table 2.

(Continued)

| Specification                                         | Value                                                               |                         |                            |          |                                                       | Comments                                                                                     |                                            |  |

|-------------------------------------------------------|---------------------------------------------------------------------|-------------------------|----------------------------|----------|-------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------|--|

| System Phase No                                       | System Phase Noise and Jitter (10 MHz Carrier)                      |                         |                            |          |                                                       |                                                                                              |                                            |  |

| Sample Clock<br>Source                                | System Phase Noise<br>Density<br>(dBc/Hz) Offset<br>Untegrated from |                         |                            |          | ty<br>Offset System Output Jitter<br>(Integrated from |                                                                                              | y System Output Jitter<br>(Integrated from |  |

|                                                       | 100 Hz                                                              | 1 kHz                   | 10 kHz                     |          | Hz to 100 kHz)                                        | Sample Rate.                                                                                 |                                            |  |

| Divide-by-N                                           | -110                                                                | -122                    | -138                       |          | 1.5 ps rms                                            | 2. Values are                                                                                |                                            |  |

| High-<br>Resolution <sup>1</sup><br>100 MS/s          | -109                                                                | -120                    | -120                       |          | 4.0 ps rms                                            | typical.<br>3. PXI Star<br>trigger                                                           |                                            |  |

| High-<br>Resolution <sup>1</sup><br>200 MS/s          | -108                                                                | -120                    | -122                       |          | 4.2 ps rms                                            | specification is<br>valid when the<br>Sample Clock<br>Source is                              |                                            |  |

| CLK IN <sup>2</sup>                                   | -116                                                                | -130                    | -143                       |          | 1.1 ps rms                                            | locked to                                                                                    |                                            |  |

| PXI Star<br>Trigger <sup>2,3</sup>                    | -111                                                                | 11 –128 –136 2.1 ps rms |                            |          |                                                       | PXI_CLK10.                                                                                   |                                            |  |

| External<br>Sample Clock<br>Input Jitter<br>Tolerance | Cycle-Cy<br>Period Ji                                               |                         |                            |          |                                                       |                                                                                              |                                            |  |

| Sample Clock E                                        | xporting                                                            |                         |                            |          |                                                       |                                                                                              |                                            |  |

| Exported<br>Sample Clock<br>Destinations              | 2. DDC panel                                                        | CLK OUT                 |                            | L DATA 8 | & CONTROL front                                       | Exported Sample<br>Clocks can be<br>divided by integer<br>$K$ ( $1 \le K \le$<br>4,194,304). |                                            |  |

|                                                       | 3. FAI_                                                             | 111g<002                |                            |          |                                                       | 4,194,504).                                                                                  |                                            |  |

| Exported<br>Sample Clock<br>Destinations              | Maximum<br>Frequency Jitter (Typical) Duty Cycle                    |                         |                            |          |                                                       |                                                                                              |                                            |  |

| PFI<01>                                               | 200 1                                                               | MHz                     | PFI 0: 6 ps rms 25% to 65% |          | ]                                                     |                                                                                              |                                            |  |

|                                                       |                                                                     |                         | PFI 1: 12 ps rms           |          |                                                       |                                                                                              |                                            |  |

| DDC CLK<br>OUT                                        | 200 1                                                               | MHz                     | 60 ps                      | s rms    | 35% to 65%                                            |                                                                                              |                                            |  |

| PXI_Trig<06>                                          | 20 N                                                                | <i>I</i> Hz             |                            | _        |                                                       |                                                                                              |                                            |  |

| Та | ble | : 3 |

|----|-----|-----|

|    |     |     |

| Specification         | Value                                                                                                                                                     | Comments |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Clock Source          | Internal sample clocks can either be locked to a Reference<br>Clock using a phase-locked loop or be derived from the<br>onboard VCXO frequency reference. | _        |

| Frequency<br>Accuracy | ±25 ppm                                                                                                                                                   | _        |

# Phase-Locked Loop (PLL) Reference Clock

| Specification                                      | Value                                                                                                                                                         | Comments                                                                                              |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Sources                                            | <ol> <li>PXI_CLK10 (backplane connector)</li> <li>CLK IN (SMB front panel connector)</li> </ol>                                                               | The PLL<br>Reference Clock<br>provides the<br>reference<br>frequency for the<br>phase-locked<br>loop. |

| Frequency<br>Accuracy                              | When using the PLL, the Frequency Accuracy of the NI 5422 is solely dependent on the Frequency Accuracy of the PLL Reference Clock Source.                    | _                                                                                                     |

| Lock Time                                          | ≤200 ms                                                                                                                                                       |                                                                                                       |

| Frequency<br>Range                                 | <ul><li>5 MHz to 20 MHz in increments of 1 MHz.</li><li>Default of 10 MHz.</li><li>The PLL Reference Clock Frequency has to be accurate to ±50 ppm.</li></ul> | _                                                                                                     |

| Duty Cycle<br>Range                                | 40% to 60%                                                                                                                                                    | —                                                                                                     |

| Exported PLL<br>Reference<br>Clock<br>Destinations | <ol> <li>PFI&lt;01&gt; (SMB front panel connectors)</li> <li>PXI_Trig&lt;06&gt; (backplane connector)</li> </ol>                                              |                                                                                                       |

| Та | bl | e | 4. |

|----|----|---|----|

|    |    |   |    |

### **CLK IN** (Sample Clock and Reference Clock Input, Front Panel Connector)

| Specification             | Value                                                                              | Comments |

|---------------------------|------------------------------------------------------------------------------------|----------|

| Connector                 | SMB (jack)                                                                         | —        |

| Direction                 | Input                                                                              | —        |

| Destinations              | 1. Sample Clock                                                                    | —        |

|                           | 2. PLL Reference Clock                                                             |          |

| Frequency                 | 5 MHz to 200 MHz (Sample Clock Destination)                                        | —        |

| Range                     | 5 MHz to 20 MHz (PLL Reference Clock destination)                                  |          |

| Input Voltage<br>Range    | Sine wave: 0.65 $V_{pk-pk}$ to 2.8 $V_{pk-pk}$ into 50 $\Omega$ (0 dBm to +13 dBm) | —        |

|                           | Square wave: 0.2 $V_{pk\text{-}pk}$ to 2.8 $V_{pk\text{-}pk}$ into 50 $\Omega$     |          |

| Maximum<br>Input Overload | ±10 V                                                                              | —        |

| Input<br>Impedance        | 50 Ω                                                                               | —        |

| Input Coupling            | AC                                                                                 |          |

| Table J. |

|----------|

|----------|

### **PFI 0 and PFI 1** (Programmable Function Interface, Front Panel Connectors)

| Specification             | Value                                                                                    | Comments |

|---------------------------|------------------------------------------------------------------------------------------|----------|

| Connectors                | Two SMB (jack)                                                                           |          |

| Direction                 | Bi-directional                                                                           |          |

| Frequency<br>Range        | DC to 200 MHz                                                                            | _        |

| As an Input (Tr           | igger)                                                                                   |          |

| Destinations              | Start Trigger                                                                            | —        |

| Maximum<br>Input Overload | -2 V to +7 V                                                                             | _        |

| V <sub>IH</sub>           | 2.0 V                                                                                    |          |

| V <sub>IL</sub>           | 0.8 V                                                                                    | —        |

| Input<br>Impedance        | 1 kΩ                                                                                     | _        |

| As an Output (I           | Event)                                                                                   |          |

| Sources                   | 1. Sample Clock divided by integer $K$ ( $1 \le K \le 4,194,304$ )                       | _        |

|                           | 2. Sample Clock Timebase (200 MHz) divided<br>by integer $M$ ( $4 \le M \le 4,194,304$ ) |          |

|                           | 3. PLL Reference Clock                                                                   |          |

|                           | 4. Marker                                                                                |          |

|                           | 5. Exported Start Trigger (Out Start Trigger)                                            |          |

| Output<br>Impedance       | 50 Ω                                                                                     |          |

Table 6.

Table 6. (Continued)

| Specification                  | Value                                         | Comments                                                   |

|--------------------------------|-----------------------------------------------|------------------------------------------------------------|

| As an Output (                 | Continued)                                    |                                                            |

| Maximum<br>Output<br>Overload  | -2 V to +7 V                                  | _                                                          |

| V <sub>OH</sub>                | Minimum: 2.7 V (open load), 1.3 V (50 Ω load) | Output drivers are                                         |

| V <sub>OL</sub>                | Maximum: 0.6 V (open load), 0.2 V (50 Ω load) | +3.3 V TTL<br>compatible.<br>Measured with<br>a 1 m cable. |

| Rise/Fall Time<br>(20% to 80%) | ≤2.0 ns                                       | Load of 10 pF.                                             |

### DIGITAL DATA & CONTROL (DDC) Optional Front Panel Connector

| Specification                                     |                                                                                                                                                      | Value             |                | Comments                                              |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|-------------------------------------------------------|

| Connector<br>Type                                 | 68-pin VHDCI fem                                                                                                                                     |                   |                |                                                       |

| Number of<br>Data Output<br>Signals               | 16                                                                                                                                                   |                   |                | _                                                     |

| Control<br>Signals                                | <ol> <li>DDC CLK OUT</li> <li>DDC CLK IN (d</li> <li>PFI 2 (input)</li> <li>PFI 3 (input)</li> <li>PFI 4 (output)</li> <li>PFI 5 (output)</li> </ol> | · •               |                |                                                       |

| Ground                                            | 23 pins                                                                                                                                              |                   |                | —                                                     |

| Output Signal O                                   | Characteristics (Incl                                                                                                                                | udes Data Outputs | , DDC CLK OUT, | and PFI<45>)                                          |

| Signal Type                                       | LVDS (Low-Voltage Differential Signal)                                                                                                               |                   |                | —                                                     |

| Signal<br>Characteristics                         | Minimum                                                                                                                                              | Typical           | Maximum        | 1. Tested with<br>100 Ω<br>differential               |

| V <sub>OH</sub>                                   |                                                                                                                                                      | 1.3 V             | 1.7 V          | load.                                                 |

| V <sub>OL</sub><br>Differential<br>Output Voltage | 0.8 V<br>0.25 V                                                                                                                                      | 1.0 V             | 0.45 V         | 2. Measured with<br>188143B-01<br>cable.              |

| Output<br>Common-Mode<br>Voltage                  | 1.125 V                                                                                                                                              |                   | 1.375 V        | 3. Driver and<br>receiver<br>comply with<br>ANSI/TIA/ |

| Rise/Fall Time<br>(20% to 80%)                    |                                                                                                                                                      | 0.8 ns            | 1.6 ns         | EIA-644.                                              |

Table 7.

Table 7. (Continued)

| Specification                      | Va                                                                                                                                                          | lue                 | Comments |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|

| Output Signal (                    | Characteristics (Continued)                                                                                                                                 |                     |          |

| Output Skew                        | Typical: 1 ns, maximum 2 ns. Skew between any<br>two outputs on the DIGITAL DATA & CONTROL<br>front panel connector.                                        |                     | _        |

| Output<br>Enable/Disable           | Controlled through the software on all Data Output Signals<br>and Control Signals collectively. When disabled, the outputs<br>go to a high-impedance state. |                     |          |

| Maximum<br>Output<br>Overload      | -0.3 V to +3.9 V                                                                                                                                            |                     | _        |

| Input Signal Ch                    | naracteristics (Includes DDC                                                                                                                                | CLK IN and PFI<23>) |          |

| Signal Type                        | LVDS (Low-Voltage Differen                                                                                                                                  | ntial Signal)       |          |

| Input<br>Differential<br>Impedance | 100 Ω                                                                                                                                                       |                     | _        |

| Maximum<br>Output<br>Overload      | -0.3 V to +3.9 V                                                                                                                                            |                     | _        |

| Signal<br>Characteristics          | Minimum                                                                                                                                                     | Maximum             | _        |

| Differential<br>Input Voltage      | 0.1 V                                                                                                                                                       | 0.5 V               |          |

| Input Common<br>Mode Voltage       | 0.2 V                                                                                                                                                       | 2.2 V               |          |

| DDC CLK OUT                        | Г                                                                                                                                                           |                     |          |

| Clocking<br>Format                 | Data outputs and markers change on the falling edge of DDC CLK OUT.                                                                                         |                     | _        |

| Frequency<br>Range                 | Refer to the <i>Sample Clock</i> section for more information.                                                                                              |                     | _        |

| Duty Cycle                         | 35% to 65%                                                                                                                                                  |                     | _        |

| Jitter                             | 60 ps rms (typical)                                                                                                                                         |                     |          |

Table 7. (Continued)

| Specification                    | Value                                                            | Comments |

|----------------------------------|------------------------------------------------------------------|----------|

| DDC CLK IN                       |                                                                  |          |

| Clocking<br>Format               | DDC Data Output signals change on the rising edge of DDC CLK IN. | —        |

| Frequency<br>Range               | 10 Hz to 200 MHz                                                 | _        |

| Input Duty<br>Cycle<br>Tolerance | 40% to 60%                                                       | _        |

# **Start Trigger**

| Specification          | Value                                                                                                                                  | Comments |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------|

| Sources                | 1. PFI<01> (SMB front panel connectors)                                                                                                |          |

|                        | <ol> <li>PFI&lt;23&gt; (DIGITAL DATA &amp; CONTROL front panel<br/>connector)</li> </ol>                                               |          |

|                        | 3. PXI_Trig<07> (backplane connector)                                                                                                  |          |

|                        | 4. PXI Star trigger (backplane connector)                                                                                              |          |

|                        | 5. Software (use function call)                                                                                                        |          |

|                        | 6. Immediate (does not wait for a trigger). Default.                                                                                   |          |

| Modes                  | 1. Single                                                                                                                              | —        |

|                        | 2. Continuous                                                                                                                          |          |

|                        | 3. Stepped                                                                                                                             |          |

|                        | 4. Burst                                                                                                                               |          |

| Edge Detection         | Rising                                                                                                                                 | —        |

| Minimum<br>Pulse Width | 25 ns. Refer to t <sub>s1</sub> at <b>NI Signal Generators Help»Devices»</b><br><b>NI 5422»NI PXI-5422»Triggering»Trigger Timing</b> . |          |

Table 8

Table 8. (Continued)

| Specification                                            | Value                                                                                                                                                      | Comments                                                                                                                              |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Delay from<br>Start Trigger to<br>CH 0 Analog<br>Output  | 65 Sample Clock Periods + 110 ns                                                                                                                           | Refer to t <sub>s2</sub> at<br>NI Signal<br>Generators<br>Help»Devices»<br>NI 5422»<br>NI PXI-5422»<br>Triggering»<br>Trigger Timing. |

| Delay from<br>Start Trigger to<br>Digital Data<br>Output | 41 Sample Clock periods + 110 ns                                                                                                                           | —                                                                                                                                     |

| Trigger Export                                           | ing                                                                                                                                                        |                                                                                                                                       |

| Exported<br>Trigger<br>Destinations                      | A signal used as a trigger can be routed out to any destination listed in the <i>Destinations</i> specification of Table 9.                                | _                                                                                                                                     |

| Exported<br>Trigger Delay                                | 65 ns (typical). Refer to t <sub>s3</sub> at <b>NI Signal Generators Help»</b><br><b>Devices»NI 5422»NI PXI-5422»Triggering»Trigger</b><br><b>Timing</b> . | —                                                                                                                                     |

| Exported<br>Trigger Pulse<br>Width                       | >150 ns. Refer to t <sub>s4</sub> at <b>NI Signal Generators Help»</b><br><b>Devices»NI 5422»NI PXI-5422»Triggering»Trigger</b><br><b>Timing</b> .         |                                                                                                                                       |

# Markers

#### Table 9.

| Specification | Value                                                                                    | Comments |

|---------------|------------------------------------------------------------------------------------------|----------|

| Destinations  | 1. PFI<01> (SMB front panel connectors)                                                  | —        |

|               | <ol> <li>PFI&lt;45&gt; (DIGITAL DATA &amp; CONTROL front panel<br/>connector)</li> </ol> |          |

|               | 3. PXI_Trig<06> (backplane connector)                                                    |          |

| Quantity      | One Marker per Segment.                                                                  | —        |

| Quantum       | Marker position must be placed at an integer multiple of four samples.                   | _        |

Table 9. (Continued)

| Specification | Value                                                                                                                                 |                                  |                                           | Comments                                               |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------|--------------------------------------------------------|

| Width         | >150 ns. Refer to t <sub>m2</sub> at NI Signal Generators Help»<br>Devices»NI 5422»NI PXI-5422»Waveform Generation»<br>Marker Events. |                                  |                                           |                                                        |

| Skew          | Destination                                                                                                                           | With Respect to<br>Analog Output | With Respect to<br>Digital Data<br>Output | Refer to t <sub>m1</sub> at<br>NI Signal<br>Generators |

|               | PFI<01>                                                                                                                               | ±2 Sample Clock<br>Periods       | N/A                                       | Help»Devices»<br>NI 5422»<br>NI PXI-5422»              |

|               | PFI<45>                                                                                                                               | N/A                              | <2 ns                                     | Waveform                                               |

|               | PXI_Trig<06>                                                                                                                          | ±2 Sample Clock<br>Periods       | N/A                                       | Generation»<br>Marker Events.                          |

| Jitter        | 40 ps rms (typical)                                                                                                                   |                                  |                                           | —                                                      |

# **Arbitrary Waveform Generation Mode**

| Specification                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>T</b> 7                    | luo                                 | Commente                                       |