CE

omega.com e-mail: info@omega.com For latest product manuals: omegamanual.info

# OMB-DAQBOARD-500 Series 16-Bit, 200-KHz PCI Data Acquisition Boards

|                               | net <sup>®</sup> Online Service<br>omega.com                                                                                                                                  | Internet e-mail<br>info@omega.com                                         |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|                               | Servicing North                                                                                                                                                               | America:                                                                  |

| U.S.A.:<br>ISO 9001 Certified | One Omega Drive, P.O. Box 4<br>Stamford, CT 06907-0047<br>TEL: (203) 359-1660<br>e-mail: info@omega.com                                                                       | 4047<br>FAX: (203) 359-7700                                               |

| Canada:                       | 976 Bergar<br>Laval (Quebec) H7L 5A1, Car<br>TEL: (514) 856-6928<br>e-mail: info@omega.ca                                                                                     | nada<br>FAX: (514) 856-6886                                               |

| For imm                       | nediate technical or a                                                                                                                                                        | pplication assistance:                                                    |

| U.S.A. and Canad              | <b>a:</b> Sales Service: 1-800-826-6342<br>Customer Service: 1-800-622-<br>Engineering Service: 1-800-87                                                                      | 2378 / 1-800-622-BEST®                                                    |

| Mexico:                       | En Español: (001) 203-359-780<br>FAX: (001) 203-359-7807                                                                                                                      | 3 e-mail: espanol@omega.com<br>info@omega.com.mz                          |

|                               | Servicing Eu                                                                                                                                                                  | rope:                                                                     |

| Benelux:                      | Postbus 8034, 1180 LA Amste<br>TEL: +31 (0)20 3472121<br>Toll Free in Benelux: 0800 099<br>e-mail: sales@omegaeng.nl                                                          | FAX: +31 (0)20 6434643                                                    |

| Czech Republic:               | Frystatska 184, 733 01 Karvin<br>TEL: +420 (0)59 6311899<br>Toll Free: 0800-1-66342                                                                                           | á, Czech Republic<br>FAX: +420 (0)59 6311114<br>e-mail: info@omegashop.cz |

| France:                       | 11, rue Jacques Cartier, 78280<br>TEL: +33 (0)1 61 37 2900<br>Toll Free in France: 0800 466 3<br>e-mail: sales@omega.fr                                                       | FAX: +33 (0)1 30 57 5427                                                  |

| Germany/Austria               | 1: Daimlerstrasse 26, D-75392 D<br>TEL: +49 (0)7056 9398-0<br>Toll Free in Germany: 0800 63<br>e-mail: info@omega.de                                                          | FAX: +49 (0)7056 9398-29                                                  |

| United Kingdom                | : One Omega Drive, River Ben<br>Northbank, Irlam, Mancheste<br>M44 5BD United Kingdom<br>TEL: +44 (0)161 777 6611<br>Toll Free in United Kingdom<br>e-mail: sales@omega.co.uk | FAX: +44 (0)161 777 6622                                                  |

It is the policy of OMEGA Engineering, Inc. to comply with all worldwide safety and EMC/EMI regulations that apply. OMEGA is constantly pursuing certification of its products to the European New Approach Directives. OMEGA will add the CE mark to every appropriate device upon certification.

The information contained in this document is believed to be correct, but OMEGA accepts no liability for any errors it contains, and reserves the right to alter specifications without notice.

WARNING: These products are not designed for use in, and should not be used for, human applications.

#### Warnings, Cautions, Notes, and Tips

Refer all service to qualified personnel. This symbol warns of possible personal injury or equipment damage under noted conditions. Follow all safety standards of professional practice and the recommendations in this manual. Using this equipment in ways other than described in this manual can present serious safety hazards or cause equipment damage.

This warning symbol is used in this manual or on the equipment to warn of possible injury or death from electrical shock under noted conditions.

This ESD caution symbol urges proper handling of equipment or components sensitive to damage from electrostatic discharge. Proper handling guidelines include the use of grounded anti-static mats and wrist straps, ESD-protective bags and cartons, and related procedures.

This symbol indicates the message is important, but is not of a Warning or Caution category. These notes can be of great benefit to the user, and should be read.

In this manual, the book symbol always precedes the words "Reference Note." This type of note identifies the location of additional information that may prove helpful. References may be made to other chapters or other documentation.

Tips provide advice that may save time during a procedure, or help to clarify an issue. Tips may include additional reference.

#### Specifications and Calibration

Specifications are subject to change without notice. Significant changes will be addressed in an addendum or revision to the manual. As applicable, we calibrate our hardware to published specifications. Periodic hardware calibration is not covered under the warranty and must be performed by qualified personnel as specified in this manual. Improper calibration procedures may void the warranty.

Your order was carefully inspected prior to shipment. When you receive your order, carefully unpack all items from the shipping carton and check for physical signs of damage that may have occurred during shipment. Promptly report any damage to the shipping agent and your sales representative. Retain all shipping materials in case the unit needs returned to the factory.

### CAUTION

Using this equipment in ways other than described in this manual can cause personal injury or equipment damage. Before setting up and using your equipment, you should read *all* documentation that covers your system. Pay special attention to Warnings and Cautions.

**Note:** During software installation, Adobe<sup>®</sup> PDF versions of user manuals will automatically install onto your hard drive as a part of product support. The default location is in the **Programs** group, which can be accessed from the *Windows Desktop*. Initial navigation is as follows:

Start [Desktop "Start" pull-down menu] ⇒ Programs

$\Rightarrow$  Omega DaqX Software

You can also access the PDF documents directly from the data acquisition CD by using the **<View PDFs>** button located on the opening screen.

Refer to the PDF documentation for details regarding both hardware and software.

A copy of the Adobe Acrobat Reader<sup>®</sup> is included on your CD. The Reader provides a means of reading and printing the PDF documents. Note that hardcopy versions of the manuals can be ordered from the factory.

### Table of Contents

#### **OMB-DAQBOARD-500 Series, Installation Guide**

#### 1 – Introduction

Basic Information ..... 1-1 Block Diagram ..... 1-2 Board Features ..... 1-3

#### 2 – Connections and Pinouts

Overview ..... 2-1 68-Pin SCSI Type III Connector ..... 2-2 Signal Definitions ..... 2-3 TB-100 Terminal Connector Option ..... 2-6 External Connections ..... 2-7

#### 3 – Configuration

Configuration through Software ...... 3-1 Analog Input Configuration ...... 3-1 ADC Ranges ...... 3-1 DAC Ranges ...... 3-2

#### 4 – Software and Board Operation

Overview ...... 4-1 Out-of-the-Box Software ......4-1 Drivers for Third-Party, Icon Driven Software ...... 4-2 DaqCOM Driver ...... 4-2 Theory of Operation ...... 4-3

#### 5 - CE-Compliance

Overview ...... 5-1 CE Standards and Directives ...... 5-1 Safety Conditions ...... 5-2 Emissions/Immunity Conditions ...... 5-2

#### 6 – Specifications

#### Glossary

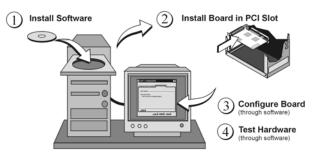

This guide tells how to complete the following steps for a successful installation.

- Step 1 Install Software ..... page 2

- Step 2 Install Boards in Available PCI Bus-Slots ..... page 3

- Step 3 Configure Boards ..... page 5

- Step 4 Test Hardware ..... page 6

#### **Reference Note:**

After you have completed the installation you should refer to the electronic documents that were automatically installed onto your hard drive as a part of product support. The default location is in the **Programs** group, which can be accessed from the Windows Desktop.

You should keep your DaqBoard's serial number and your DaqView/500 authorization code (if applicable) with this document. Space is provided below for recording up to 4 board numbers and their PCI bus-slot locations. The board serial number and board type (500 or 505) is located on the solder-side of the board.

Board Identity on "Solder-Side" of the Board

|         | Board Type<br>(e.g. /500, /505) | Serial Number | PCI Bus-Slot Location |

|---------|---------------------------------|---------------|-----------------------|

| Board 1 |                                 |               |                       |

| Board 2 |                                 |               |                       |

| Board 3 |                                 |               |                       |

| Board 4 |                                 |               |                       |

The host PC can support up to four Boards.

DaqView/500 Authorization Code \_\_\_\_\_

Customers who ordered DaqView/500 can find their authorization code on the *authorization code sheet* located inside the sleeve of the install CD.

Customers who did not order DaqView/500 can run a *30-day free trial version*, as discussed elsewhere in the User's Manual.

Each DaqBoard/500 Series plugs into a PCI bus-slot. Consult your PC owner's manual as needed.

**Reference Note**: Adobe PDF versions of user manuals will automatically install onto your hard drive as a part of product support. The default location is in the **Programs** group, which can be accessed from the *Windows Desktop*. Refer to the PDF documentation for details regarding both hardware and software. Note that hardcopy versions of the manuals can be ordered from the factory.

#### Minimum System Requirements

- PC system with Pentium<sup>®</sup> 3 Processor

- 500 MHz

- 128 M-byte RAM

- Windows 2000 or XP Operating System

Installation, A Pictorial Overview

### Step 1 – Install Software

### **<u>IMPORTANT</u>**: Software must be installed before installing hardware.

- 1. Remove previous version Daq drivers, if present. You can do this through Microsoft's **Add/Remove Programs** feature.

- 2. Place the Data Acquisition CD into the CD-ROM drive. *Wait for PC to auto-run the CD. This may take a few moments, depending on your PC.* If the CD does not auto-run, use the Desktop's Start/Run/Browse feature and run the **Setup.exe** file.

- 3. After the intro-screen appears, follow the screen prompts.

Upon completing the software installation, continue with step 2, *Install Boards in available PCI Bus-slots*.

### Step 2 – Install Boards in available PCI Bus-slots

**<u>IMPORTANT</u>**: Software must be installed before installing hardware.

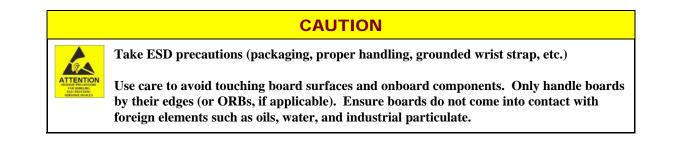

### CAUTION

Turn off power to, and UNPLUG the host PC and externally connected equipment prior to removing the PC's cover and installing the DaqBoard. Electric shock or damage to equipment can result even under low-voltage conditions.

Take ESD precautions (packaging, proper handling, grounded wrist strap, etc.)

Use care to avoid touching board surfaces and onboard components. Only handle boards by their edges (or ORBs, if applicable). Ensure boards do not come into contact with foreign elements such as oils, water, and industrial particulate.

#### **IMPORTANT:** Bus Mastering DMA must be Enabled.

For a DaqBoard/500 Series board to operate properly, Bus Mastering DMA *must be* Enabled on the PCI slot [for which the board is to be installed]. Prior to installation, verify that your computer is capable of performing Bus Mastering DMA for the applicable PCI slot. Note that some computers have BIOS settings that enable [or disable] Bus Mastering DMA. If your computer has this BIOS option, ensure that Bus Mastering DMA is *Enabled* on the appropriate PCI slot.

Refer to your PC Owner's Manual for additional information regarding your PC and enabling Bus Mastering DMA for PCI slots.

- 1. Turn off power to, and UNPLUG the host PC and externally connected equipment.

- 2. Remove the PC's cover. Refer to your PC Owner's Manual as needed.

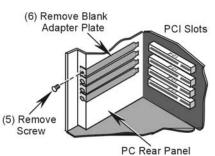

- 3. Choose an available PCI bus-slot.

- 4. Carefully remove the DaqBoard from its anti-static protective bag. If you have not already done so, write down the serial number of your board at this time.

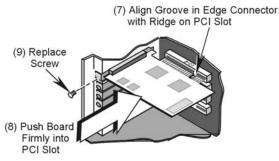

- 5. Refer to the figure at the right. Remove the screw that secures the blank adapter plate, which is associated with the PCI slot you will be using. *Refer to your PC Owner's Manual if needed*.

- 6. Remove the blank adapter plate.

Removing a Blank Adapter Plate

- 7. Refer to the figure at the right. Align the groove in the DaqBoard's PCI edge-connector with the ridge of the desired PCI slot, and with the PC's corresponding rearpanel slot.

- 8. Push the board firmly into the PCI slot. The board will snap into position.

- 9. Secure the board by inserting the rear-panel adapter-plate screw.

- 10. Using the previous steps, install additional boards into available PCI bus-slots, if applicable to your application.

- 11. Replace the computer's cover.

- 12. Plug in all cords and cables that were removed in step 1.

- 13. Apply power to, and start up the PC.

- **Note:** At this point some PCs may prompt you to insert an installation disk. While this is rare, if you do receive such a prompt simply place the install CD-ROM into the disk drive and follow additional screen prompts.

Installing a DaqBoard/500 Series Board

### Step 3 – Configure Boards

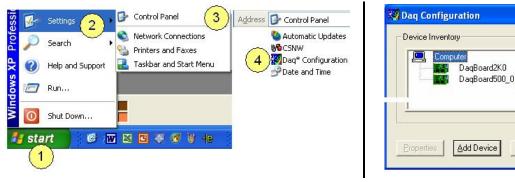

DaqBoard/500 Series Boards have no jumpers or switches to set. Configuration is performed entirely through software. Refer to the following figure and steps to complete the configuration. The numbers in the figure correspond to the numbered steps.

- 1. Open the "Start" menu from the Windows desktop.

- 2. Select "Settings."

- 3. Select "Control Panel."

- 4. Double-click "Daq Configuration." This opens the Daq Configuration window.

- 5. Double-click on the Device Inventory's DaqBoard/500 Series icon. In the figure above the DaqBoard/500 appears as "DaqBoard500\_0."

The DaqBoard's Properties tab will appear (following figure).

Note: If the DaqBoard icon is not present, skip to the upcoming section, Using 'Add Device.'

| 😻 Daq* Configuration                                                                                                                                                          | × |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| DaqBoard/500 Test Hardware Driver Versions                                                                                                                                    |   |

| Device Settings                                                                                                                                                               |   |

| Device <u>Name: DagBoard500_0</u> 6                                                                                                                                           |   |

| Device Type: DagBoard/500                                                                                                                                                     |   |

| DaqBoard/500 Series <u>H</u> ardware:                                                                                                                                         |   |

| Bus 3, Slot 1, S/N 0*, Model 500 PCI (8) 🗸                                                                                                                                    |   |

| *The serial number is shown for reference only.<br>When you have multiple boards a device name is<br>matched to a particular board by physical slot, not<br>by serial number. |   |

| OK Cancel Apply                                                                                                                                                               |   |

Accessing the DaqBoard/500 Properties Tab

- 6. Enter a "**Device Name**" in the text box, or use the default, e.g., DaqBoard500\_0. The Name is for identifying the specific DaqBoard, but actually refers to the PCI slot.

- 7. Verify that the "Device Type" shows the correct board, i.e., "DaqBoard/500 or DaqBoard/505." Other devices, if available can be viewed via the pull-down list.

- 8. Confirm that the DaqBoard's text box shows a Bus #, Slot #, and Serial Number.

*If this text box is empty*, use its pull-down list and select the serial number that matches the one for your board.

5

### Using "Add Device"

This method is for users who have accessed the **Daq Configuration** control panel applet, but have no DaqBoard/500 Series device icon.

- 1. After accessing the Daq Configuration control panel applet, click on the <**Add Device**> button (see figure, right). The *Select Device Type* window will appear.

- Using the *Device Type's* pull-down list, select the applicable board. In the example at the right DaqBoard/500 is selected.

- 3. Click the **<OK>** button. The board's Properties tab will appear. The tab applies to all boards in the series.

At this point, complete steps 6 through 8 on page IG-5.

| 1 | mputer<br>ect Device Type      |

|---|--------------------------------|

|   | Device Type                    |

|   | DaqBoard/100A                  |

|   | DaqBoard/100A<br>DaqBoard/112A |

|   | DaqBoard/200A<br>DaqBoard/216A |

|   | DagBoard/500 2<br>DagBoard/505 |

|   | DaqBoard/1000<br>DaqBoard/1005 |

|   | OK 3 Cancel                    |

|   |                                |

| - |                                |

Using "Add Device"

### Step 4 - Test Hardware

Use the following steps to test the DaqBoard. Note that these steps are continued from those listed under the previous section, "Configure Board."

- 1. Select the "Test Hardware" tab.

- 2. Click the **<Resource Test>** button.

- 3. After the test is complete, click <**OK**>."

System capability is now tested for the DaqBoard and a list of test results will appear.

**Note:** If you experience difficulties, please consult your user documentation (included on your CD) before calling for technical support.

| 🛃 Daq* Config                                                                                                           | uration 1                     | ×  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------|----|--|--|--|

| DaqBoard/500                                                                                                            | Test Hardware Driver Versions |    |  |  |  |

| Prior to testing please make sure your device is connected to the PC.                                                   |                               |    |  |  |  |

| If your computer does not respond for 30 seconds please<br>reboot and change the settings in the configuration utility. |                               |    |  |  |  |

| Test Results                                                                                                            |                               | -2 |  |  |  |

| No tests have been run.<br>To run click Test.                                                                           |                               |    |  |  |  |

| Resource Test 2                                                                                                         |                               |    |  |  |  |

|                                                                                                                         | OK Cancel Apply               |    |  |  |  |

|                                                                                                                         |                               |    |  |  |  |

|                                                                                                                         | Test Hardware Tab             |    |  |  |  |

|                                                                                                                         | (Condensed Screen Image)      |    |  |  |  |

At this point we are ready to connect signals. For DaqBoard/500 Series boards, connection is typically made via a terminal board, such as the optional TB-100.

#### **Reference Notes:**

During software installation, Adobe<sup>®</sup> PDF versions of user manuals are automatically installed onto your hard drive as a part of product support. The default location is in the **Programs** group, which can be accessed from the Windows Desktop. A copy of the Adobe Acrobat Reader<sup>®</sup> is included on your CD. The Reader provides a means of reading and printing the PDF documents. Note that hardcopy versions of manuals can be ordered from the factory.

The DaqBoard/500 and DaqBoard/505 have 16 single-ended or 8 differential analog inputs multiplexed to a 16-bit A/D converter with maximum throughput of 200 kHz, programmable gains of 1, 2, 4 or 8, one counter input channel, two timer output channels, and 24 lines of digital I/O. In addition, DaqBoard/500 includes two clocked DACs.

The boards feature a DMA engine for optimum performance in supported Windows environments. Board connections are terminated in a 68-pin "high density" SCSI III connector at the rear of the PC.

A digital calibration method is used for both analog-to-digital and digital-to-analog conversions. Please contact the factory should you believe your board to be in need of calibration.

### **Basic Information**

| Analog Inputs             | 16 Single-Ended or 8 Differential  |           |                               |  |

|---------------------------|------------------------------------|-----------|-------------------------------|--|

| Ranges                    | Unipola                            | ır        | Bipolar                       |  |

|                           | 0 to10\                            | /         | ± 10V                         |  |

|                           | 0 to 5∨                            | ,         | ± 5V                          |  |

|                           | 0 to 2.5                           | V         | ± 2.5V                        |  |

|                           | 0 to 1.25                          | SV .      | ± 1.25V                       |  |

| Resolution                | 16-bit                             |           |                               |  |

| A/D Sample Rate           | 200 kHz                            |           |                               |  |

| Gains (Programmable)      | x1, x2, x4, x8                     |           |                               |  |

| D/A Outputs (16-Bit)*     | 2 Clocked DACs (DaqBoard/500 only) |           |                               |  |

| Digital I/O               | 24                                 |           |                               |  |

| Counters (16-Bit)         | 1                                  |           |                               |  |

| Timers                    | 2                                  |           |                               |  |

| Associated Terminal Board | TB-100 (optional)                  |           |                               |  |

| Associated Cables         | CA-G55:                            | 68 Pin SC | SI III Cable, 3 ft.           |  |

|                           | CA-G56:                            | 68 Pin SC | SI III Cable, Shielded, 3 ft. |  |

|                           | CA-G56-6:                          | 68 Pin SC | SI III Cable, Shielded, 6 ft. |  |

\*D/A Outputs do not apply to DaqBoard/505.

1

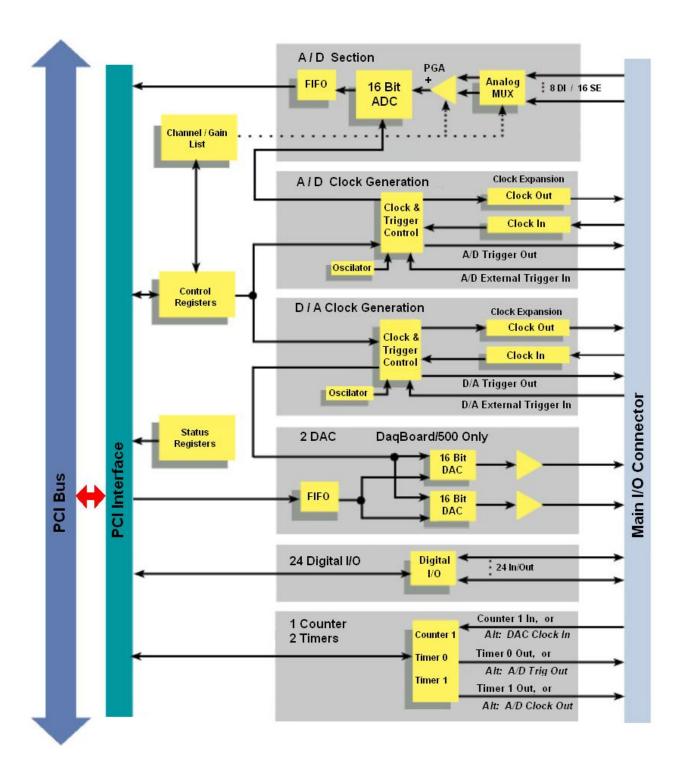

### Block Diagram

DaqBoard/500 Series Block Diagram

### **Board Features**

### Analog I/O

DaqBoard/500 Series boards support 16 single-ended or 8 differential analog inputs multiplexed to a 16-bit A/D converter. The input multiplexer is supported by a 176 element channel gain RAM which allows the board to select gain on a per channel basis and to access channels in any order. The 16-bit A/D has a maximum throughput of 200 kHz. An A/D Pacer clock is provided to allow sampling rates from 0.0009 Hz to 200 kHz. The DaqBoard/500 includes two DACs for analog output.\*

### **Digital I/O**

DaqBoard/500 Series boards have 24 lines of TTL level digital I/O programmable in three 8-bit ports as either inputs or outputs. All 24 lines are brought out via the main 68-pin SCSI III connector.

### **Counter 1**

Counter 1 (CNTR1) can provide either cumulative or incremental counting capabilities. The counter is capable of counting 5 V LSTTL rising edges to a maximum count of 131071 decimal.

### Timer 0 and Timer 1

Timer0 (TMR0) and Timer1 (TMR1) provide a 50% duty cycle square wave 5 V LSTTL output with an output frequency range of 7.7 Hz to 500 kHz. The Timer's output frequency is based on a 1 MHz oscillation with a divisor of 1 to 65536 decimal.

### **PCI Interface**

DaqBoard/500 Series boards communicate to the PCI bus through an interface controller. The boards are fully *plug-and-play* and have no switches, potentiometers, or jumpers. The boards feature digitally calibrated A/D and D/A's, and *plug-and-play* compatibility to provide automatic integration into the PC's configuration when first installed.

The PCI interface provides access to all on-board registers for software configuration of all on-board functions. For maximum performance, the boards feature a 32-bit bus-mastering DMA engine on the ADC and DAC hardware to provide high-speed transfers between the board and system memory.

### **DMA Engine**

Interrupt latency on the PCI bus can be extremely inefficient for high-speed data acquisition. For this reason, DaqBoard/500 and DaqBoard/505 each use an onboard DMA engine. The engine [analogous to the older ISA type DMA controller] supports *scatter/gather* (buffer chaining) with a pair of chain address registers. These registers point to system memory for use in the buffered transfer.

The DMA controller is loaded with the previously allocated physical addresses of the buffers and only generates interrupt requests when the current transfer buffer has been completed. This reduces the burden of CPU interrupt intervention.

Both analog input and analog output channels\* have on-board DMA engine support for high-speed data transfers. The two analog output channels have individual DMA engines and clocking methods available. The DAC1 clocking source may be set to the DAC0 clocking source to allow simultaneous DAC transfers.

All PCI bus transfers are 32-bit operations. Analog input and analog output transfers are each independently software selectable to allow either 16-bit or 32-bit data transfers. An immediate improvement *of twice the memory bandwidth* can be achieved by transferring two analog input data points [or two analog output data points] into memory as a single 32-bit PCI transfer.

\* The DAC analog output channels apply to DaqBoard/500 only.

Overview ..... 2-1 68-Pin SCSI Type III Connector ..... 2-2 Signal Definitions ..... 2-3 TB-100 Terminal Connector Option ..... 2-6 External Connections ..... 2-7

### WARNING

Always turn the computer power OFF and unplug it before connecting or disconnecting a screw terminal panel or a cable to the PCI card. Failure to do so could result in electric shock, or equipment damage.

#### CAUTION

The discharge of static electricity can damage some electronic components. Semiconductor devices are especially susceptible to ESD damage. You should always handle components carefully, and you should never touch connector pins or circuit components unless you are following ESD guidelines in an appropriate ESD controlled area. Such guidelines include the use of properly grounded mats and wrist straps, ESD bags and cartons, and related procedures.

### Overview

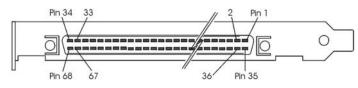

DaqBoard/500 Series boards communicate [external from the host PC] through a 68-pin SCSI III connector. An optional TB-100 terminal board offers convenient screw-terminal connections for all signal I/O.

Pinouts for both the DaqBoard/500 Series connector and the TB-100 follow.

The TB-100 option can be easily connected to a DaqBoard/500 or DaqBoard/505 via one of three 68-conductor cables. These are: CA-G55, a 3 ft. unshielded cable; CA-G56, a 3 ft. shielded cable; and CA-G56-6, a 6 ft. shielded cable.

### 68-Pin SCSI Type III Pinout

Standard 68-Pin SCSCI Type III, Socket (Female) Connector with Orb

| Pin         | Signal                              |        | Descript   | tion / Comments                               | Pin         | Sigr                             | al       | Descrip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | tion / Comme                       | nts  |

|-------------|-------------------------------------|--------|------------|-----------------------------------------------|-------------|----------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------|

| 1           | DACLKIN/<br>CNTR1<br>See Pin 39 [No | ote    |            | AC Clock In or<br>Rising or Falling<br>itive. | 35          | DGND                             |          | Digital Grour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ıd                                 |      |

| 2           | ADCLKIN<br>See Pin 5 [No            | ote 3] | External A | DC Clock In                                   | 36          | DGND                             |          | Digital Grour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ıd                                 |      |

| 3           | ADTRGOUT/<br>TMR0                   |        |            | DC Trigger Output/<br>lock Output             | 37          | ADCLKOU<br>TMR1                  | Τ/       | Internal ADC<br>Timer 1 Cloc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Clock Output/<br>k Output          |      |

| 4           |                                     |        | Reserved   |                                               | 38          | DATRGIN                          |          | DAC0 Extern<br>(Level Contro<br>External Trig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |      |

| 5           | ADCLKIN<br>See Pin 2 [No            | ote 3] | External A | DC Clock In                                   | 39          | DACLKIN/<br>CNTR1<br>See Pin 1 [ |          | External DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C Clock In, or<br>ising or Falling |      |

| 6           | ADTRGIN                             |        | ADC Trigg  | ger                                           | 40          | DGND                             |          | Digital Grour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | nd                                 |      |

| 7           | C6                                  |        | TTL Level  | Digital I/O Ch. C6                            | 41          | C7                               |          | TTL Level D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | igital I/O Ch. C7                  |      |

| 8           | C4                                  | D      | TTL Level  | Digital I/O Ch. C4                            | 42          | C5                               |          | TTL Level D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | igital I/O Ch. C5                  | D    |

| 9           | C2                                  | Ι      | TTL Level  | Digital I/O Ch. C2                            | 43          | C3                               |          | TTL Level D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | igital I/O Ch. C3                  | Ι    |

| 10          | C0                                  | G      | TTL Level  | Digital I/O Ch. C0                            | 44          | C1                               |          | TTL Level D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | igital I/O Ch. C1                  | G    |

| 11          | B6                                  | Ι      | TTL Level  | Digital I/O Ch. B6                            | 45          | B7                               |          | TTL Level D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | igital I/O Ch. B7                  | I    |

| 12          | B4                                  | Т      | TTL Level  | Digital I/O Ch. B4                            | 46          | B5                               |          | TTL Level D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | igital I/O Ch. B5                  | Т    |

| 13          | B2                                  | Α      |            | Digital I/O Ch. B2                            | 47          | B3                               |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | igital I/O Ch. B3                  | A    |

| 14          | B0                                  | L      |            | Digital I/O Ch. B0                            | 48          | B1                               |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | igital I/O Ch. B1                  | L    |

| 15          | A6                                  |        |            | Digital I/O Ch. A6                            | 49          | A7                               |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | igital I/O Ch. A7                  |      |

| 16          | A4                                  | I      |            | Digital I/O Ch. A4                            | 50          | A5                               |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | igital I/O Ch. A5                  | I    |

| 17          | A2                                  | 0      |            | Digital I/O Ch. A2                            | 51          | A3                               |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | igital I/O Ch. A3                  | 0    |

| 18          | A0                                  |        |            | Digital I/O Ch. A0                            | 52          | A1                               |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | igital I/O Ch. A1                  |      |

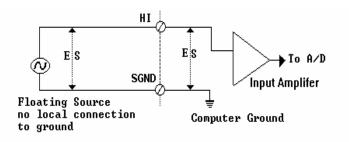

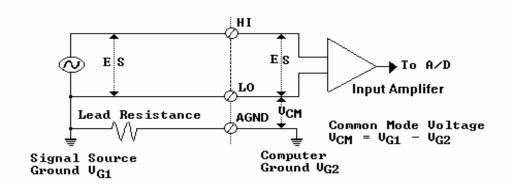

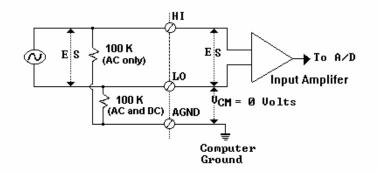

| 19          | +5 VDC                              |        | Power      |                                               | 53          | DGND                             |          | Digital Grour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |      |