# **OPOMEGA**

## DAQP-208/208H/308

## Type II PCMCIA Data Acquisition Adapters

Users Manual

INTERFACE CARDS FOR PERSONAL COMPUTERS

OMEGA ENGINEERING, INC. One Omega Drive P.O. Box 4047 Stamford, CT 06907-4047 Tel: (203) 359-1660 Fax: (203) 359-7700 Toll free: 1-800-826-6342 E-mail: das@omega.com

www.dasieee.com

Download from Www.Somanuals.com. All Manuals Search And Download.

## WARRANTY/DISCLAIMER

OMEGA ENGINEERING, INC., warrants this unit to be free of defects in materials and workmanship for a period of 13 months from the date of purchase. OMEGA warranty adds an additional one (1) month grace period to the normal one (1) year product warranty to cover shipping and handling time. This ensures that OMEGA's customers receive maximum coverage on each product. If the unit should malfunction, it must be returned to the factory for evaluation. OMEGA's Customer Service Department will issue an Authorized Return (AR) number immediately upon phone or written request. Upon examination by OMEGA, if the unit is found to be defective it will be repaired or replaced at no charge. OMEGA's warranty does not apply to defects resulting from any action of the purchaser, including but not limited to mishandling, improper interfacing, operation outside design limits, improper repair or unauthorized modification. This WARRANTY is VOID if the unit shows evidence of having been tampered with or shows evidence of being damaged as a result of excessive corrosion; or current, heat, moisture or vibration; improper specification; misapplication; misuse or other operating conditions outside of OMEGA's control. Components which wear are not warranted, including but not limited to contact points, fuses and triacs.

OMEGA is pleased to offer suggestions on the use of its various products. However, OMEGA neither assumes responsibility for any omissions or errors nor assumes liability for any damages that result from the use of its products in accordance with information provided from OMEGA, either verbal or written. OMEGA warrants only that the parts manufactured by it will be as specified and free of defects. OMEGA MAKES NO OTHER WARRANTIES OR REPRESENTATIONS OF ANY KIND WHATSOEVER, EXPRESSED OR IMPLIED, EXCEPT THAT OF TITLE, AND ALL IMPLIED WARRANTIES INCLUDING ANY WARRANTY OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE HEREBY DISCLAIMED. LIMITATION OF LIABILITY: The remedies of purchaser set forth herein are exclusive and the total liability of OMEGA with respect to this order, whether based on contract, warranty, negligence, indemnification, strict liability or otherwise, shall not exceed the purchase price of the component upon which liability is based. In no event shall OMEGA be liable for consequential, incidental or special damages.

CONDITIONS: Equipment sold by OMEGA is not intended to be used, nor shall it be used: (1) as a "Basic Component" under 10 CFR 21 (NRC), used in or with any nuclear installation or activity, medical application or used on humans. Should any Product(s) be used in or with any nuclear installation or activity, medical application, used on humans or misused in any way, OMEGA assumes no responsibility as set forth in our basic WARRANTY/DISCLAIMER language, and additionally, the purchaser will indemnify OMEGA and hold OMEGA harmless from any liability or damage whatsoever arising out of the use of the Product(s) in such a manner.

## RETURN REQUESTS/INQUIRIES

Direct all warranty and repair requests/inquiries to the OMEGA Customer Service Department. BEFORE RETURNING ANY PRODUCT(S) TO OMEGA, THE PURCHASER MUST OBTAIN AN AUTHORIZED RETURN (AR) NUMBER FROM OMEGA'S CUSTOMER SERVICE DEPARTMENT (IN ORDER TO AVOID PROCESSING DELAYS). THE ASSIGNED NUMBER SHOULD THEN BE MARKED ON THE OUTSIDE OF THE RETURN PACKAGE AND ON ANY CORRESPONDENCE. THE PURCHASER IS RESPONSIBLE FOR SHIPPING CHARGES, FREIGHT, INSURANCE AND PROPER PACKAGING TO PREVENT BREAKAGE IN TRANSIT.

FOR <u>WARRANTY</u> RETURNS, please have the following information available BEFORE contacting OMEGA:

- (1) P.O. Number under which the product was purchased,

- (2) Model and serial number of the product under warranty, and

- (3) Repair instructions and/or specific problems relative to the product.

FOR <u>NON-WARRANTY</u> REPAIRS, consult OMEGA for current repair charges. Have the following information available BEFORE contacting OMEGA:

- (1) P.O. Number to cover the cost of the repair,

- (2) Model and serial number of the product, and

- (3) Repair instructions relative to the product.

OMEGA's policy is to make running changes, not model changes, whenever an improvement is possible. This affords our customers the latest in technology and engineering.

OMEGA is a registered trademark of OMEGA ENGINEERING, INC. © Copyright 1999 OMEGA ENGINEERING, INC. All rights reserved. This document may not be copied, photocopied, reproduced, translated or reduced to any electronic medium or machine readable form, in whole or in part, without prior written consent of OMEGA ENGINEERING, INC.

#### OMEGAnet? On-line Service:

#### Internet e-mail:

DAQP-208/208H/308 Users Manual

http://www.omega.com

info@omega.com

### Servicing North America:

| USA:<br>ISO 9001 Certified | One Omega Drive, Box 4047<br>Stamford, CT 06907-0047<br>Tel: (203) 359-1660                                                                      | E-mail: info@omega.com<br>FAX: (203) 359-7700                    |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Canada:                    | 976 Bergar<br>Laval (Quebec) H7L 5A1<br>Tel: (514) 856-6928                                                                                      | E-mail: info@omega.com<br>FAX: (514) 856-6886                    |

| <u>For imm</u>             | ediate technical or applica                                                                                                                      |                                                                  |

| USA and Canada:            | Sales Service: 1-800-826-6342 / 1-80<br>Customer Service: 1-800-622-2378/<br>Engineering Service: 1-800-872-943<br>TELEX: 996404 EASYLINK: 62968 | 1-800-622-BEST <sup>SM</sup><br>6 / 1-800-USA-WHEN <sup>SM</sup> |

| Mexico and Latin Ameri     | ica: Tel: (001) 800-826-6342<br>En Espanol: (001) 203-359-7803                                                                                   | FAX: (001) 203-359-7807<br>E-mail: espanol@omega.com             |

|                            | Servicing Europe:                                                                                                                                |                                                                  |

| Benelux:                   | Postbus 8034, 1180 LA Amstelveen,<br>Tel: (31) 20 6418405<br>Toll Free in Benelux: 0800 0993344<br>E-mail: nl@omega.com                          | The Netherlands                                                  |

| Czech Republic:            | ul.Rude armady 1868, 733 01 Karvi<br>Tel: 42 (69) 6311899<br>Toll Free: 0800-1-66342                                                             | na-Hraniee<br>FAX: 42 (69) 6311114<br>E-mail: czech@omega.com    |

| France:                    | 9, rue Denis Papin, 78190 Trappes<br>Tel: (33) 130-621-400<br>Toll Free in France: 0800-4-06342<br>E-mail: france@omega.com                      |                                                                  |

| Germany/Austria:           | Daimlerstrasse 26, D-75392 Decken<br>Tel: 49 (07056) 3017<br>Toll Free in Germany: 0130 11 21 66<br>E-mail: germany@omega.com                    |                                                                  |

United Kingdom: ISO 9002 Certified One Omega Drive, River Bend Technology Drive Northbank, Irlam, Manchester M44 5EX, England Tel: 44 (161) 777-6611 FAX: 44 (161) 777-6622 Toll Free in England: 0800-488-488 E-mail: info@omega.co.uk

It is the policy of OMEGA to comply with all worldwide safety and EMC/EMI regulations that apply. OMEGA is constantly pursuing certification of it's products to the European New Approach Directives. OMEGA will add the CE mark to every appropriate device upon certification.

The information contained in this document is believed to be correct but OMEGA Engineering, Inc. accepts no liability for any errors it contains, and reserves the right to alter specifications without notice. WARNING: These products are not designed for use in, and should not be used for, patient connected applications.

## <u>Notice</u>

The information contained in this document cannot be reproduced in any form without the written consent of Omega Engineering Inc. Any software programs accompanying this document can be used only in accordance with any licensing agreement(s) between Omega Engineering Inc. and the purchaser. Omega Engineering Inc. reserves the right to change this documentation or the product to which it refers at any time and without notice.

The authors have taken due care in the preparation of this document and any associated software program(s). Every attempt has been made to ensure accuracy and completeness. Under no circumstances will Omega Engineering Inc. be liable for damages of any kind, incidental or consequential, in regard to or arising from the performance or form of the materials presented herein or in any software program(s) that may accompany this document.

Omega Engineering Inc. encourages and appreciates feedback concerning this document. Please send any written comments to the Technical Support Department at the address listed on the cover of this document.

> Copyright ©2001 by Omega Engineering Inc. All rights reserved. Printed in the U.S.A.

IBM<sup>®</sup>, PC<sup>®</sup> and PC-AT<sup>®</sup> are trademarks of the International Business Machines Corporation. Windows<sup>®</sup>, MS-DOS<sup>®</sup>, Windows 95<sup>®</sup>, Windows 98<sup>®</sup>, Windows NT<sup>®</sup> and Windows 2000<sup>®</sup> are trademarks of the Microsoft Corporation. Other product and company names are registered trademarks or trademarks of their respective holders.

## Table of Contents

| 1. | Introduction                                           | . 8 |

|----|--------------------------------------------------------|-----|

| 2. | Hardware Configuration and Initial Setup               | . 9 |

|    | 2.1 Software Installation: Windows 95/98/2000 ®        |     |

|    | 2.1.1 Windows 2000                                     |     |

|    | 2.1.2 Windows 98                                       |     |

|    | 2.1.3 Windows 95                                       |     |

|    | 2.1.4 Viewing Resources with Device Manager            |     |

|    | 2.2 Software Installation: Windows NT 4.0 ®            |     |

|    | 2.3 Data Acquisition Software and Drivers              |     |

|    | 2.4 Software Installation: Windows 3.x and MS-DOS®     |     |

|    | 2.4.1 Client Driver for MS-DOS2.4.2 Enabler for MS-DOS |     |

|    | 2.4.2 Enabler for MS-DO5                               | 10  |

| 3. | Field Wiring                                           | 21  |

| 0. | 3.1 UIO-37 Screw Terminal Block                        | 21  |

|    | 3.2 CP-DAQPA Cable Assembly                            |     |

|    | 3.2 CI-DAQIA Cable Assembly                            | 23  |

| 4. | Theory of Operation                                    | 25  |

|    | 4.1 DC/DC Power Supply                                 |     |

|    | 4.2 Analog Input Multiplexer                           |     |

|    | 4.3 Programmable Gain Control Amplifier                |     |

|    | 4.4 Scan List Register                                 |     |

|    | 4.5 Trigger Circuit                                    |     |

|    | 4.6 A/D Converter and Data FIFO                        |     |

|    | 4.7 Interrupt and Status                               |     |

|    | 4.8 Digital I/O                                        |     |

|    | 4.9 A/D State Machine                                  |     |

|    | 4.10 D/A Circuit                                       |     |

|    | 4.11 Timer/Counter                                     |     |

|    | HIT TIMET/ Counter                                     | 52  |

| 5. | I/O Registers                                          | 34  |

|    | 5.1 PCMCIA Interface                                   | 34  |

|    | 5.1.1 Configuration and Option Register (COR)          |     |

|    | 5.1.2 Card Configuration and Status Register (CCSR)    |     |

|    | 5.2 Address Map                                 | 36 |

|----|-------------------------------------------------|----|

|    | 5.2.1 Data FIFO Register (base + 0)             |    |

|    | 5.2.2 Scan List Queue Register (base + 1)       | 39 |

|    | 5.2.3 Status Register (base + 2)                | 44 |

|    | 5.2.4 Digital I/O Register                      | 45 |

|    | 5.2.5 Pacer Clock (base + 4, + 5, + 6)          | 46 |

|    | 5.2.6 Command Register (base + 7)               | 47 |

|    | 5.2.7 D/A Data Port (base + 8, base + 9)        | 49 |

|    | 5.2.8 Timer/Counter Port (base + 10, base + 11) | 51 |

|    | 5.2.9 Auxiliary Control Register (base + 15)    | 53 |

|    | 5.2.10 Auxiliary Status Register (base + 15)    | 53 |

|    |                                                 |    |

| 6. | Specifications                                  | 55 |

## List of Figures and Tables

| Figure 3-1. DAQP Series Card Output Connector            | 21 |

|----------------------------------------------------------|----|

| Figure 3-2. CP-DAQPA/UIO-37 D37 Pin Diagram              | 22 |

| Figure 3-3. UIO-37 Terminal Block                        |    |

| Figure 3-4. DAQP Card with Accessories                   | 24 |

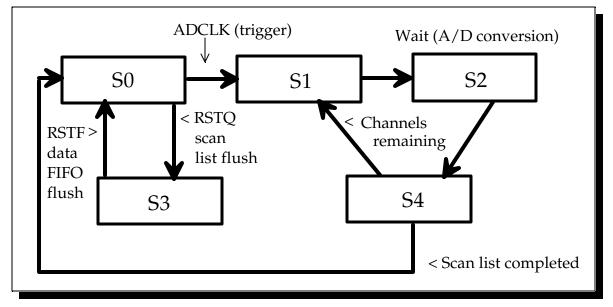

| Figure 4-1. Transition Diagram of A/D Conversion Process | 31 |

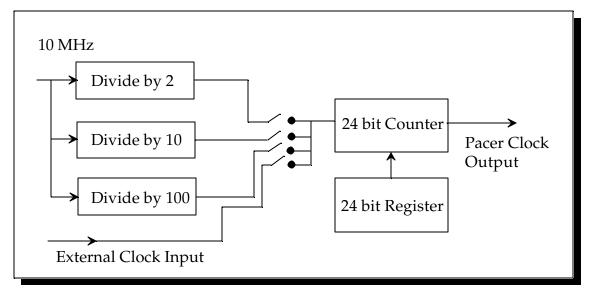

| Figure 5-1. Pacer Clock Block Diagram                    | 46 |

|                                                          |    |

| Table 2-1. Comparison Between Client Driver and Enabler  |    |

| Table 3-1. DAQP Series Card Cable Mapping                |    |

| Table 5-1. PCMCIA Configuration Registers                |    |

| Table 5-2. COR Bit Definition                            |    |

| Table 5-3. CCSR Bit Definition                           |    |

| Table 5-4. DAQP Series Card Address Map                  | 36 |

| Table 5-5. Data FIFO Register Bit Allocation             | 37 |

| Table 5-6. Data FIFO Operation Mode                      | 37 |

| Table 5-7. Data FIFO Threshold Setting                   | 38 |

| Table 5-8. Data FIFO Flag Status                         | 39 |

| Table 5-9. Scan List Queue Entry Bit Definition          | 39 |

| Table 5-10. Scan List Queue Programming Example 1        | 40 |

| Table 5-11. Scan List Queue Programming Example 2        | 40 |

| Table 5-12. Control Register Bit Definition              |    |

| Table 5-13. Status Register Bit Definition               |    |

| Table 5-14. Digital Output Register Bit Definition       |    |

| Table 5-15. Digital Input Register Bit Definition        |    |

| Table 5-16. Command Register Bit Definition              | 47 |

| Table 5-17. Data FIFO Threshold Setting                  |    |

| Table 5-18. D/A Data Port Bit Definition                 |    |

| Table 5-19. D/A Update Modes                             | 50 |

| Table 5-20. Timer/Counter Modes                          |    |

| Table 5-21. Auxiliary Control Register Bit Definition    | 53 |

| Table 5-22. Auxiliary Status Register Bit Definition     |    |

|                                                          |    |

## 1. Introduction

DAQP series cards are PCMCIA type II data acquisition adapters with 4 differential or 8 single-ended analog input channels. The number of input channels can be expanded to 128 when used with input expansion cards. DAQP series products include the DAQP-208, the DAQP-208H and the DAQP-308. Card features include:

- ∠ 4 differential or 8 single-ended analog input channels, expandable to 128 channels

- Z Two 12 bit D/A channels with direct or synchronized update

- Bipolar input range up to ±10 volts with programmable gain of 1, 2, 4 or 8 (DAQP-208/308) or gain of 1, 10, 100 or 1000 (DAQP-208H)

- $\measuredangle$  Programmable scan list with up to 2048 channel and gain entries, plus selectable scan speed of 10, 20 or 40  $\mu s$

- Additional 16 bit timer/counter with auto reload, read-out/overflow latches and internal/external gate control and clock sources

Software, TTL or analog trigger with programmable threshold and pre-trigger capability

Equipped with a 4K data FIFO, the DAQP card can achieve high speed data acquisition under various operating platforms. Also equipped with a 2048 entry scan FIFO, the DAQP supports full speed, random order channel scanning and gain selection for all input channels including expansion channels.

The DAQP card uses a 24-bit pacer clock and a programmable divide-by-2, by-10 or by-100 pre-scaler. The pacer clock can be used with either an internal or external clock source. DAQP series cards are also equipped with two independent 12 bit D/A output channels with a bipolar range of -5 to +5 volts. D/A channels can be updated directly when writing the corresponding D/A port (direct mode) or simultaneously with a synchronization signal.

#### 2.1 Software Installation: Windows 95/98/2000 ®

An "INF" file (daqpcard.inf) is included on the root directory of the DaqSuite CD to allow easy configuration in the Windows environment. Windows uses the "INF" file to determine the system resources required by the DAQP card, searches for available resources to fill the requirements and then updates the Windows hardware registry with entries to allocate the resources. Follow the instructions below to configure your DAQP series card under Windows.

#### Card Information Structure (CIS) Differences

DAQP series cards come with 12 and 16 bit versions. Each version may also have different product names and descriptions depending on the manufacturer or vendor name associated with the card. This results in differences in the CIS for the specific DAQP card version. Windows will configure the DAQP card in the same manner regardless of CIS differences. It is strongly recommended that the DaqSuite CD "INF" file be used to configure the DAQP card and that it should only be used if Windows 95/98/2000 does not recognize the card upon insertion. It is not necessary to install the INF file if Windows recognizes the card when inserted due to the presence of an older INF file in the system. Do not try to modify, merge, rename or delete the system INF files. If difficulties are encountered during installation, contact the technical support department at the number shown on the cover of this manual.

#### 2.1.1 Windows 2000

- 1. Insert the DAQP card into any available PC Card socket. The first time a new PC Card type is installed the "New Hardware Found" window will open. Click Next to continue.

- 2. The New Hardware Found window provides several options to configure the DAQP card. Select the "Search for a suitable driver for my device" radio button. Click Next to continue.

- 3. Insert the DaqSuite CD, select the "CD-ROM drive" check box and click Next to continue. Windows 2000 will browse the CD until it finds the file "x:\daqpcard.inf", where "x" is the CD-ROM drive letter. Click Next to continue.

- 4. When Windows finishes the configuration process, click Finish to exit the New Hardware Found Wizard.

- 5. Hardware Configuration is not complete until the user has run the desired driver support installation from the DaqSuite CD demo. This support installation is required to install Windows 2000 drivers for your DAQP card. Refer to Section 2.3: Data Acquisition Software and Drivers for a list of driver installation options.

#### 2.1.2 Windows 98

- 1. Insert the DAQP card into any available PC Card socket. The first time a new PC Card type is installed the "Add New Hardware Wizard" window will open. Click Next to continue.

- 2. The Add New Hardware Wizard provides several options to configure the DAQP card. Select the recommended option radio button: "Search for the best driver for your device". Click Next to continue.

- 3. An Install from Disk dialog box will open. Insert the DaqSuite CD, either type in or browse for the correct CD-ROM drive letter and then click OK. Windows 98 will browse the CD until it finds the file "x:\daqpcard.inf", where "x" is the CD-ROM drive letter. Click Next to continue.

- 4. When Windows finishes the configuration process, click Finish to exit the New Hardware Found Wizard.

- 5. Hardware configuration is not complete until the user has run the desired driver support installation from the DaqSuite CD demo. This support installation is required to install Windows 98 drivers for your DAQP card. Refer to Section 2.3: Data Acquisition Software and Drivers for a list of driver installation options.

#### 2.1.3 Windows 95

- 1. Insert the DAQP card into any available PC Card socket. The first time a new PC Card type is installed the "New Hardware Found" window will open. Select the "Driver from disk provided by hardware manufacturer" radio button and click OK to continue.

- 2. An Install from Disk dialog box will open. Insert the DaqSuite CD, either type in or browse for the correct CD-ROM drive letter and then click OK. Windows 95 will browse the CD until it finds the file "x:\daqpcard.inf", where "x" is the CD-ROM drive letter and then proceed to configure the hardware.

- 3. Hardware configuration is not complete until the user has run the desired driver support installation from the DaqSuite CD demo. This support installation is required to install Windows 95 drivers for your DAQP card. Refer to Section 2.3: Data Acquisition Software and Drivers for a list of driver installation options.

#### 2.1.4 Viewing Resources with Device Manager

Follow the instructions provided here to view resources used by the DAQP card using the "Device Manager" utility in Windows.

- 1. Double click the My Computer icon located on the Windows desktop and then double click the Control Panel icon. Double click the System icon to open the System Properties window.

- 2. Click the "Device Manager" tab located at the top of the dialog box. (Windows 2000 users must click the "Hardware" tab and then press the "Device Manager" button). The Device Manager lists all hardware devices inside the Windows registry. Additional information is available on any of these devices by clicking on the device name and then selecting the Properties button.

- 3. Double click the device group "Data\_ Acquisition". The DAQP card model name should appear on the list below this category. Double click on the model name to open the Hardware Properties window.

- 4. Click the Resources tab located along the top of the dialog box to view the resources Windows has allocated to the DAQP card.

#### 2.2 Software Installation: Windows NT 4.0 ®

Windows NT 4.0 does not use the "Add New Hardware" wizard to configure new hardware. Once the DAQP card is installed, run the desired driver support installation from the DaqSuite CD demo to install Windows NT 4.0 drivers. During the installation process, NT 4.0 registry entries are created to automatically start and run your hardware. Refer to Section 2.3: Data Acquisition Software and Drivers for a list of driver installation options. After installing the drivers, the base address and IRQ level must be determined and saved in the corresponding configuration file for the resources to be assigned to the device. Determine what I/O Port number and IRQ levels are available from the windows NT diagnostics. Save these to the device's configuration file (see section 2.2 in the daqdrive manual for a description on how to use the configuration utility). You must reboot at this point for these setting to take effect and to determine installation success. To determine if your DAQP card is correctly installed and to view its assigned resources, follow the instructions listed below.

- 1. From within Windows NT 4.0 , Select Start | Programs | Administrative Tools (Common) | Windows NT Diagnostics.

- 2. When the Windows NT Diagnostics window opens, click the "Resources" tab located at the top of the dialog box. Press the Devices button located in the bottom right corner. The DAQP card driver name is "DAQPDRV". This name should be listed under the category "Device".

- 3. To view the resources assigned to the DAQP card, press the IRQ and I/O Port buttons at the bottom of the Windows NT Diagnostics window.

To remove the DAQP card from your Windows NT 4.0 system, run the associated driver support uninstallation program using the Add/Remove Programs icon located in the Control Panel folder. (This will remove all registry entries applicable to your hardware). When the uninstallation is complete, shut down your computer and remove the hardware. To verify these actions, reboot and follow steps 1 and 2 above to ensure the "DAQPDRV" listing no longer appears under the "Device" category.

#### 2.3 Data Acquisition Software and Drivers

Data acquisition software and driver support installations are available from the DaqSuite CD demo main menu.

- 1. Quatech's DaqEZ? This software package was specifically designed to support all Quatech's data acquisition adapter functions and is included free of charge with your hardware. DaqEZ is an easy to use application that requires no programming knowledge and allows the user to graphically acquire and display real time data using customized channel labels, charts and displays. (Includes hardware drivers for Windows 95 or 98).

- 2. DASYTEC's DASYLab DASYLab is designed to solve sophisticated data acquisition and control tasks quickly. Module symbols representing inputs/outputs, display instruments or operations to be performed are inserted into a work sheet and graphically connected. This approach allows complex applications to be constructed without programming knowledge.

The DaqSuite CD includes a fully functional 30 day evaluation version of DASYLab. (Includes hardware drivers for Windows 95, 98, 2000 and NT 4.0).

3. 3rd Party Driver Support - Hardware drivers for Windows 95, 98, 2000 and NT 4.0 are available for the following 3rd party data acquisition software packages:

DASYLab from DASYTEC? - Run this installation if DASYLab software is already installed on the system that will use your Quatech hardware.

LabVIEW? from National Instruments? - Run this installation if LabVIEW software is already installed on the system that will use your Quatech hardware.

TestPoint? from Capital Equipment Corporation - Run this installation if TestPoint software is already installed on the system that will use your Quatech hardware.

4. Drivers/Programming Support - Quatech's Daqdrive? provides hardware drivers, a hardware configuration utility and data acquisition programming examples for Microsoft? and Borland? C/C++, Visual Basic? and Borland Dephi? . (Includes hardware drivers for Windows 95, 98, 2000 and NT 4.0).

#### 2.4 Software Installation: Windows 3.x and MS-DOS®

Two software configuration programs are provided with the DAQP card: a Client Driver named DAQPA\_CL.SYS and a card Enabler named DAQPA\_EN.EXE. Either one of these programs may be used to configure the card <u>but only one may be used at a time</u>. Table 2-1 below highlights the differences between the Client Driver and the Enabler programs. Detailed instructions for installation and usage of the Client Driver and Enabler programs are discussed the following sections.

| Client Driver                     | Enabler                                  |

|-----------------------------------|------------------------------------------|

| DAQPA_CL.SYS                      | DAQPA_EN.EXE                             |

| Interfaces to PCMCIA Card and     | Interfaces directly to Intel 82365SL and |

| Socket Services software (PCMCIA  | other PCIC compatible PCMCIA host        |

| host adapter independent)         | adapters                                 |

| Allows automatic configuration of | Does not support automatic               |

| DAQP card upon insertion (Hot     | configuration of DAQP card upon          |

| Swapping)                         | insertion (Hot Swapping)                 |

| Requires PCMCIA Card and Socket   | Does not require PCMCIA Card and         |

| Services software                 | Socket Services software                 |

Table 2-1. Comparison Between Client Driver and Enabler

On systems with Card and Socket Services installed, the Client Driver is the preferred method of installation. To determine if Card and Socket Services software is installed, install the DAQP series Client Driver. When loaded, the Client Driver will display an error message if Card and Socket Services software is not detected.

#### 2.4.1 Client Driver for MS-DOS

For systems using MS-DOS and PCMCIA Card and Socket Services software, a Client Driver named "DAQPA\_CL.SYS" is provided to configure the DAQP series cards. PCMCIA Card and Socket Services software is not provided with your DAQP card, but is available from your vendor.

Some versions of Card and Socket Services dated before 1993 do not support general purpose I/O cards. After careful installation of the Client Driver, if the DAQP card still does not configure or operate properly, an updated version of Card and Socket Services software may be required. The following procedures are used to install the DAQP series Client Driver:

- 1. Copy the file DAQPA\_CL.SYS located in the PCMCIA\DOS\CLIENTS directory of the DaqSuite CD onto the root directory of the system hard drive.

- 2. Using an ASCII text editor, open the system's CONFIG.SYS file located in the root directory of the boot drive.

- 3. Locate the line in the CONFIG.SYS file where Card and Socket Services software is installed.

- 4. AFTER the line installing the Card and Socket Services software, add the following line to the CONFIG.SYS file:

DEVICE = drive:\DAQPA\_CL.SYS (options)

where (options) are the DAQP series Client Driver command line options discussed on the following pages.

- 5. Save the CONFIG.SYS file and exit the text editor.

- 6. Insert the DAQP card into one of the system PCMCIA slots.

NOTE: Since the DAQP series Client Driver supports "Hot Swapping", it is not necessary to have the DAQP card installed when booting the system. By inserting the card before booting, the Client Driver will report the card configuration during the boot process and thereby verify changes made to CONFIG.SYS.

7. Reboot the system and note the message displayed when the Client Driver is loaded. If the Client Driver reports an "invalid command line option", correct the entry in the CONFIG.SYS file and reboot the system again. If the Client Driver reports "Card and Socket Services not found", then either Card and Socket Services software must be installed on the system or the DAQP series Enabler program must be used to configure the card. If the Client Driver reports the desired card configuration, the installation process is complete and the DAQP card may be removed and inserted from the system as desired. On each insertion into the PCMCIA socket, the DAQP card will automatically be reconfigured to the specified settings.

#### 2.4.1.1 Client Driver Command Line Options

The DAQP series Client Driver accepts up to eight command line arguments from the user to determine the configuration of the DAQP card. If any arguments are provided, the Client Driver will attempt to configure any DAQP card with the options specified in the order they are entered on the command line. Each argument must be enclosed in parenthesis and must be separated from other arguments by a <u>space</u> in the command line. Inside an argument, a <u>comma</u> (no space) should be used to separate the parameters from each other if there are two or more parameters. Within each argument, any or all of the following parameters may be specified:

- b address Specifies the base I/O address of the DAQP card in hexadecimal. "Address" must be in the range 100H 3F8H and must reside on an even 8-byte boundary ("address" must end in 0 or 8). If this option is omitted, a base address will be assigned by Card and Socket Services software.

- i irq Specifies the interrupt level (IRQ) of the DAQP card in hexadecimal. "Irq" must be one of the following values: 3, 4, 5, 7, 9, 10, 11, 12, 14, 15 or 0 if no IRQ if desired. If this option is omitted, an interrupt level will be assigned by Card and Socket Services software.

- s socket Specifies the PCMCIA socket number to configure. "Socket" must be in the range 0 15. If this option is omitted, the configuration argument will be applied to any available DAQP card inserted into any socket in the system.

#### 2.4.1.2 Client Driver Installation Examples

With the Client Driver, the user may specify a list of selections (in the form of command line arguments) for the configuration of the DAQP series cards. The Client Driver scans this list from left to right until it finds a selection that is currently available in the system. If none of the preferred selections are available, the Client Driver requests a configuration from Card and Socket Services software.

Example 1 DEVICE = C:\DAQPA\_CL.SYS

In example 1, no command line arguments are specified. The Client Driver will configure the DAQP card into ANY socket with a base address and IRQ level assigned by Card and Socket Services.

#### Example 2 DEVICE = C:\DAQPA\_CL.SYS (b300)

In this example, a single command line argument is provided. The Client Driver will attempt to configure a DAQP card inserted into ANY socket with a base address of 300H and an IRQ level assigned by Card and Socket Services. If the base address 300H is not available, the DAQP card will NOT be configured.

<u>Example 3</u> DEVICE = C:\DAQPA\_CL.SYS (s0,b300,i5)

Example 3 is also a single command line argument. The client Driver will attempt to configure the DAQP card inserted in socket 0 at base address 300H and IRQ level 5. If either address 300H or IRQ level 5 is unavailable, the card will NOT be configured. In addition, the Client Driver will NOT configure any DAQP card inserted into any socket except socket 0.

<u>Example 4</u> DEVICE = C:\DAQPA\_CL.SYS (b300,i5) (i10) ()

Three command line arguments are provided in this example. The Client Driver will first attempt to configure a DAQP card inserted into any socket with a base address 300H and IRQ level 5. If either address 300H or IRQ level 5 is unavailable, the Client Driver will proceed to the second command line argument and attempt to configure the card with a base address assigned by the Card and Socket Services and IRQ level 10. If IRQ level 10 is also unavailable, the Client Driver will then go to the third command line argument and attempt to configure it with a base address and an IRQ level assigned by Card and Socket Services.

Example 5  $DEVICE = C: DAQPA_CL.SYS (b300,i5) () (i10)$

The difference between example 5 and example 4 is the order of the second and third command line arguments. The Client Driver will first attempt to configure a DAQP card inserted into any socket with a base address 300H and IRQ level 5. If either address 300H or IRQ level 5 is unavailable, the Client Driver will proceed to the second command line argument and attempt to configure the card with a base address and IRQ level assigned by Card and Socket Services. Since the second command line argument includes all available address and IRQ resources, the third command line argument will never be reached by the Client Driver. The user must ensure command line arguments are placed in a logical order.

Example 6  $DEVICE = C: DAQPA_CL.SYS (s0,b300,i5) (s1,b310,i10)$

There are two command line arguments in example 6, which is desirable in systems where two or more DAQP cards are to be installed. The Client Driver will attempt to configure the DAQP card in socket 0 with base address 300H and IRQ 5. If there is a DAQP card in socket 1, it will be configured with base address 310H and IRQ 10. This allows the user to force the card address and IRQ settings to be socket specific as required by software or cable connections. If the requested resources are not available, the DAQP cards will not be configured.

#### 2.4.1.3 Common Problems

#### Generic Client Drivers

Many Card and Socket Services packages include a generic client driver (or SuperClient) which configures standard I/O devices. If one of these generic client drivers is installed, it may configure the DAQP card and cause the DAQP series Client Driver to fail installation. If this is the case, try the following:

Modify the operation of the generic client driver so that it will not configure the DAQP card by placing the DAQP series Client Driver before the generic client driver in the CONFIG.SYS file. Consult the Card and Socket Services documentation for availability and details of this feature.

#### Available Resources

One function of Card and Socket Services software is to track which system resources (memory addresses, I/O addresses, IRQ levels, etc.) are available for assignment to inserted PCMCIA cards. Sometimes, however, the Card and Socket Services assumes or incorrectly determines that a particular resource is unavailable when it actually is available. Most Card and Socket Services generate a resource table, typically in the form of an ".INI" file, which the user can modify to adjust the available system resources. Consult the Card and Socket Services documentation for the availability and details of this feature.

#### Multiple Configuration Attempts

Some Card and Socket Services have a setting which aborts the configuration process after a single configuration failure (such as a configuration request for an unavailable resource). The user should change this setting to allow for multiple configuration attempts. Consult the Card and Socket Services documentation for the availability and details of this feature.

#### Older Versions of Card and Socket Services

Some versions of Card and Socket Services dated before 1993 do not support general purpose I/O cards like the DAQP series PC cards. If after careful installation of the DAQP series Client Driver the DAQP card still can not be configured or operated properly, an updated version of Card and Socket Services may be required.

#### 2.4.2 Enabler for MS-DOS

For systems that are not operating PCMCIA Card and Socket Services software, the DAQP series card includes an Enabler program to enable and configure the DAQP card. This Enabler, DAQPA\_EN.EXE, will operate in any DOS system using an Intel 82365SL or PCIC compatible PCMCIA host adapter.

In order to use the DAQP series Enabler for DOS, the system must NOT be configured with Card and Socket Services software. If Card and Socket Services software is installed, the Enabler may interfere with its operation and the devices it controls. Therefore use either the DAQP series Client Driver or Enabler exclusively.

The DAQP series Enabler does not support automatic configuration of PCMCIA cards upon insertion, more commonly referred to as "Hot Swapping". This means the card must be installed in one of the system's PCMCIA sockets before executing DAQPA\_EN.EXE. If more than one adapter is installed in a system, the Enabler must be executed separately for each card. Furthermore, DAQPA\_EN.EXE should be executed to release the resources used by the card before it is removed from the PCMCIA socket. Since PCMCIA cards do not retain their configuration after removal, any card removed from the system must be reconfigured with the Enabler after being reinserted into it's PCMCIA socket.

The Enabler requires a region of high DOS memory when configuring the DAQP card. This region is 1000H (4096) bytes long and by default begins at address D0000H (it may be changed by the "w" option as described in following sections). If a memory manager such as EMM386, QEMM or 386MAX is installed on the system, this region of DOS memory must be excluded from the memory manager's control (normally by using the "x" switch). Consult the documentation provided with the memory manager software for instructions on how to exclude this memory region. Follow the procedures listed here to install the DAQP Enabler:

- 1. Copy the file DAQPA\_EN.EXE located in the PCMCIA\DOS\Enablers directory of the DaqSuite CD onto the root directory of the system hard drive.

- 2. Using an ASCII text editor, open the system's CONFIG.SYS file located in the root directory of the boot drive.

- 3. Add the following line to the CONFIG.SYS file:

DEVICE = drive:\DAQPA\_EN.EXE (options)

where (options) are the DAQP series Enabler command line options discussed on the following pages. Save the CONFIG.SYS file and exit the text editor.

4. Insert the DAQP card into one of the system PCMCIA slots. NOTE: Since the DAQP series Enabler does not support "Hot Swapping", it is necessary to have the DAQP card installed when booting the system.

6. Reboot the system and note the message displayed when the Enabler is loaded. If the Enabler reports the desired card configuration, the installation process is complete.

#### 2.4.2.1 Enabler Command Line Options

To configure a DAQP series card, the Enabler requires one command line argument from the user to determine the configuration. This argument must be enclosed in parenthesis. Within the argument, a comma (no space) must be used to separate the parameters from each other if there are two or more parameters. The following parameters may be specified in the command line argument:

- s socket Specifies the PCMCIA socket number to configure. "Socket" must be in the range 0 15. This option is always required.

- b address Specifies the base I/O address of the DAQP card in hexadecimal. "Address" must reside on an even 8-byte boundary ("address" must end in 0 or 8). This option is required if the "r" option is not used.

- i irq Specifies the interrupt level (IRQ) of the DAQP card in hexadecimal. "Irq" must be one of the following values: 3, 4, 5, 7, 9, 10, 11, 12, 14, 15, or 0 if no IRQ is desired. This option is required if the "r" option is not used.

- w address Specifies the base address of the memory window required to configure the DAQP card. Set "address" = D0 for a memory window at D0000, D8 for a memory window at D8000, etc. Valid settings for address are C8, CC, D0, D4, D8, and DC. If omitted, "address" = D0 is assumed.

- r Instructs the Enabler to release the resources previously allocated to the DAQP card. When this option is used, B address and I irq options will be ignored. Therefore, do NOT use this option when initially configuring the DAQP card.

- 2.4.2.2 Enabler Examples

Example 1DEVICE = C:\DAQPA\_EN.EXENo command line argument is specified. The Enabler will report an error and display the<br/>proper usage of the Enabler.

Example 2DEVICE = C:\DAQPA\_EN.EXE (s0,b300,i5)In this example, the Enabler will configure the DAQP card in socket 0 with a base address300H and IRQ level 5 using a configuration memory window at D0000H.

<u>Example 3</u> DEVICE = C:\DAQPA\_EN.EXE (i10,b310,s1)

In example 3, the Enabler will configure the DAQP card in socket 1 with a base address at 310H and IRQ level 10 using a configuration memory window at D0000H. Note the parameter order is not significant.

Example 4 DEVICE = C:\DAQPA\_EN.EXE (s0,b300,i5,wCC)

Here the Enabler will configure the DAQP card in socket 0 with a base address at 300H and IRQ level 5 using a configuration memory window at CC000H.

## Example 5DEVICE = C:\DAQPA\_EN.EXE (s0,r)DEVICE = C:\DAQPA\_EN.EXE (s0,r,b300,i5)

These two command line arguments are equivalent because of the "r" option. The Enabler will release the configuration used by the DAQP card in socket 0 using a configuration memory window at D0000H.

Example 6 DEVICE = C:\DAQPA\_EN.EXE (s0,r,wC8) Here the Enabler will release the configuration used by the DAQP card in socket 1, using a configuration memory window at C8000H.

#### 2.4.2.3 Common Problems

#### Memory Range Exclusion

The Enabler requires a region of high DOS memory when configuring a DAQP card. This region is 1000H (4096) bytes long and by default begins at address D0000H (this default address can be changed by using the "w" option).

If a memory manager such as EMM386, QEMM or 386MAX is installed on the system, this region of DOS memory must be excluded from the memory manager's control (normally by using the "x" switch). Consult the documentation provided with the memory manager software for instructions on how to exclude this memory region.

Furthermore, some systems use the high memory area for ROM shadowing to improve overall system performance. For the Enabler to properly operate, any ROM shadowing must be disabled in the address range specified for the configuration window. This can usually be completed by using the system's CMOS setup utility.

#### Socket Numbers

The Enabler requires that the socket number be specified for the DAQP card to be configured. The DAQP card must be inserted into the socket before executing the Enabler.

For the DAQP series Enabler, the lowest socket number is always designated as socket 0 and the highest socket number as N-1, (assuming there are N sockets available). Some vendors number their sockets from 1 to N. In that case, the vendor socket number minus 1 should be used in the "s" option for the DAQP series Enabler.

#### Card and Socket Services Software

In order to use DAQP series Enabler for DOS, the system must NOT be configured with Card and Socket Services software. If Card and Socket Services software is installed, the Enabler may interfere with its operation and the devices it controls.

## 3. Field Wiring

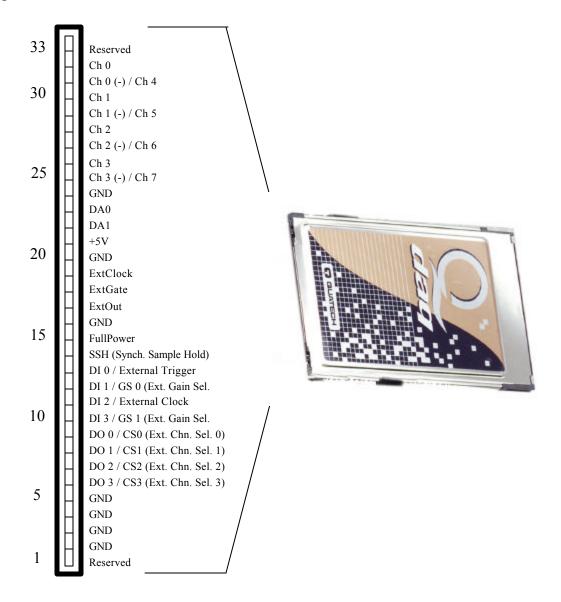

The DAQP card is fitted in with a 32-pin 0.8 mm shielded connector. See Figure 3-1 for pin assignments.

Figure 3-1. DAQP Series Card Output Connector

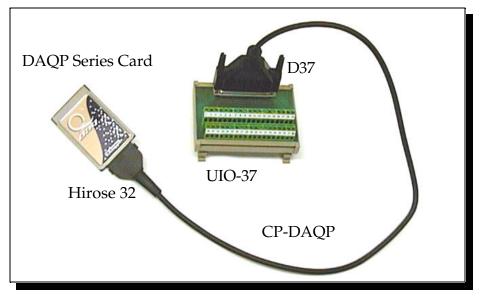

#### 3.1 CP-DAQPA Cable Assembly

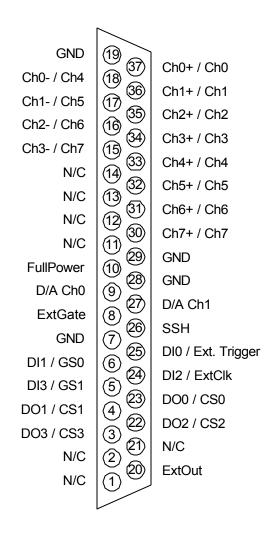

The cable assembly included with your DAQP card, part number CP-DAQPA, converts the card's 32 pin I/O connector to a standard D37 connector. Figure 3-2 illustrates the D37 connector pin assignments for the CP-DAQPA and the optional screw terminal block UIO-37.

Figure 3-2. CP-DAQPA/UIO-37 D37 Pin Diagram

| h <del></del> |       |                                 |           |                                         |

|---------------|-------|---------------------------------|-----------|-----------------------------------------|

| Hirose32      | D37   | Ν                               | ame       | Description                             |

| 32            | 37    | Channel 0                       | Channel 0 | A/D input, differential / single-ended  |

| 31            | 18,33 | Channel 0 (-)                   | Channel 4 | A/D input, differential / single-ended  |

| 30            | 36    | Channel 1                       | Channel 1 | A/D input, differential / single-ended  |

| 29            | 17,32 | Channel 1 (-)                   | Channel 5 | A/D input, differential / single-ended  |

| 28            | 35    | Channel 2                       | Channel 2 | A/D input, differential / single-ended  |

| 27            | 16,31 | Channel 2 (-)                   | Channel 6 | A/D input, differential / single-ended  |

| 26            | 34    | Channel 3                       | Channel 3 | A/D input, differential / single-ended  |

| 25            | 15,30 | Channel 3 (-)                   | Channel 7 | A/D input, differential / single-ended  |

| 24            | 19    | GND                             |           | Signal ground (analog input)            |

| 23            | 9     | DA0                             |           | D/A channel 0 output                    |

| 22            | 27    | DA1                             |           | D/A channel 1 output                    |

| 21            | 1     | +5V                             |           | Power supply output                     |

| 20            | 7     | GND                             |           | Power supply ground return              |

| 19            | 24    | ExtClk (shared with A/D)        |           | Timer/Counter external clock input      |

| 18            | 8     | ExtGate                         |           | Timer/Counter external gate control     |

| 17            | 11    | ExtOut                          |           | Timer/Counter overflow pulse output     |

| 16            | 7     | GND                             |           | Power supply ground return              |

| 15            | 10    | FullPower (org. D/A 0 ref. in)  |           | 1/0 : Full power / Power down           |

| 14            | 26    | SSH (org. D/A 1 ref. in)        |           | Synchronous Sample Hold                 |

| 13            | 25    | Digital in bit 0 (shared)       |           | External trigger (same as in DAS-16)    |

| 12            | 6     | Digital in bit 1 (normal mode)  |           | External gain, LSB (expansion mode)     |

| 11            | 24    | Digital in bit 2 (shared)       |           | External clock (org. DAS-16 Ctr 0 Gate) |

| 10            | 5     | Digital in bit 3 (normal mode)  |           | External gain, MSB (expansion mode)     |

| 9             | 23    | Digital out bit 0 (normal mode) |           | External channel bit 0 (expansion mode) |

| 8             | 4     | Digital out bit 1 (normal mode) |           | External channel bit 1 (expansion mode) |

| 7             | 22    | Digital out bit 2 (normal mode) |           | External channel bit 2 (expansion mode) |

| 6             | 3     | Digital out bit 3 (normal mode) |           | External channel bit 3 (expansion mode) |

| 5             | 28    | GND                             |           | Signal ground (D/A output)              |

| 4             | 28    | GND                             |           | Signal ground (D/A output)              |

| 3             | 29    | GND                             |           | Signal ground (digital)                 |

| 2             | 29    | GND                             |           | Signal ground (digital)                 |

| 1             | N/C   | Reserved                        |           |                                         |

Table 3-1. DAQP Series Card Cable Mapping

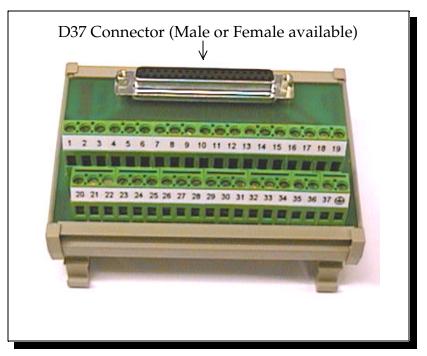

#### 3.2 UIO-37 Screw Terminal Block

For applications requiring discrete wiring connections, the UIO-37 terminal block shown in Figure 3-3 provides a simple way of connecting signals to the DAQP card. The D37 connector is available in either male or female and has two rows of screw terminals. The first row is numbered from pin 1 to pin 19 and the second row from pin 20 to pin 37. Wire gage 16 through 28 is recommended for screw terminal connections. Figure 3-4 illustrates the DAQP card with accessories.

Figure 3-3. UIO-37 Terminal Block

Figure 3-4. DAQP Card with Accessories

## 4. Theory of Operation

The DAQP card consists of 4 differential or 8 single-ended analog input channels each with a bipolar input range of  $\pm 10v$ ,  $\pm 5v$ ,  $\pm 2.5v$  or  $\pm 1.25v$  (programmable gain of 1, 2, 4 or 8). The A/D converter, either 12 -bit or 16-bit, can be operated at a top speed of 100,000 samples per second (10 µs per sample). The A/D converter uses left-justified 2's complement coding. For the 16-bit version, the output ranges from -32768 to 32767. The 12-bit version is structured so that it's contents occupy the most significant 12 bits, padding the least significant 4 bits with all zeros to make a 16-bit output word for each converted input sample.

The DAQP card can be operated as an I/O device, occupying 16 consecutive bytes in the I/O address space. It can also be configured to operate via memory mapped I/O. The DAQP fully complies with PCMCIA standard 2.10 as a type II card. The card has no jumpers or DIP switches. All of the configurable features are software programmable.

Functionally, the DAQP card consists of the following components: the DC/DC power supply, analog input multiplexer, programmable gain control amplifier, A/D converter, data FIFO, scan list FIFO, trigger control circuit, pacer clock, interrupt/status registers, digital I/O register, D/A circuit and associated control circuits.

#### 4.1 DC/DC Power Supply

The DAQP card uses a standard +5 volt digital input power supply from the PCMCIA connector which the DC/DC power supply converts to the ±15v for the analog front end and the +5v power supply for the A/D converter. The DC/DC converter uses 140 mA, 67% of the 210 mA total load current, from the digital input power supply to generate the necessary voltages.

According to the PCMCIA standard, any card that draws more than 100 mA must not be automatically turned on upon insertion until it is intentionally accessed by writing to the card configuration and option register (or its allocated I/O space). The DAQP card supports this specification by providing a unique power down mode control. When the card is first powered up or after a reset, the DC/DC converter is turned off, so that only the digital portion of the DAQP card is up and running. This requires only 40 mA from the digital input +5 volt power supply. The user has the option of reading the card information memory, where the maximum power consumption is listed for reference, and then decide whether or not to "wake up" the card. If required, the card can be set to full power mode immediately when it's PCMCIA configuration and option register (COR) is written by the software.

After the card is set to full power mode for the first time by writing the PCMCIA configuration and option register, it can then be set for power down mode by writing a '1' into bit 2, the power down bit, of the PCMCIA auxiliary control register.

#### 4.2 Analog Input Multiplexer

Differential or single-ended configuration is determined by bit 6 of the high byte in the scan list register. '1' selects differential input, while a '0' selects single-ended input. Expansion cards will only support single-ended channels. It is strongly recommended that single-ended or differential selection be uniform for all internal channels (e.g., all 4 channels as differential or all 8 channels as single-ended). Although it is possible to have some channels configured as single-ended and others as differential, this may cause confusion and unexpected signal errors.

With differential configuration, there are 4 channels. However, if the user specifies channels 4 to 7 in a differential configuration, it will short the inputs to ground for system offset measurement. The readings taken under such a circumstance can be used for offset correction. The input multiplexers have built-in protection against over-voltage when the board is at full power and when it is powered down. The protection mechanism will isolate the input from the rest of the board, as long as the input voltage is within the protection range of  $\pm 30$  volts.

#### 4.3 Programmable Gain Control Amplifier

DAQP series cards have an internal gain of 1, 2, 4 or 8. For the high gain option: DAQP-208 the internal gain choices are 1, 10, 100 and 1000. The gain can be changed "on the fly" when scanning from channel to channel by changing the configuration of the programmable gain instrumentation amplifiers. The internal gain selection is specified by the scan list entry, (bits 4 and 5 of the high byte). The contents of these two bits will determine the gain of the analog front end.

The settling time of the analog front end meets speed requirements, however, if the amplifier is saturated it may need more time to recover. This can cause distortion at the input signal to the A/D converter. It is recommended that amplifier saturation be avoided by using a low gain setting and attenuating the input signal whenever possible.

#### 4.4 Scan List Register

One entry to the scan list register contains a 16-bit word or two 8-bit bytes. It specifies the internal channel and gain selection in the high byte or MSB, and the external channel and gain selection in the low byte or LSB, in addition to other control and configuration settings. The external selections are used for expansion card channels (up to 128), while the internal selections are for channels on board the DAQP card. Expansion cards are not included as part of the DAQP series data acquisition system, however, they can be purchased separately from your vendor.

The number of entries in the scan list ranges from 1 to 2048. There are no dependencies implied among the entries of the scan list. The user may choose any valid gain combination for any channel, internal or external. Channels can be scanned in any order required, repeated or not, with the same or different gain for each entry.

The scan list must be flushed before programming to guarantee the integrity of each entry. There must be an even number of bytes programmed into the scan list, with the low byte sitting at an even offset followed by the high byte, otherwise the channel scan result will be unpredictable.

It is strongly recommended that the differential/single-ended control bit (bit 14, MSB) be programmed the same for all the entries in the scan list. Single-ended configuration should be selected if there are expansion cards connected to the DAQP card. The synchronous sample hold bit (bit 6, LSB) is reserved for expansion cards.

The first channel flag (bit 7, LSB) has to be set for the first (and ONLY the first) entry of the scan list. The DAQP card hardware relies on this bit to tell the end (or the start) of the scan. In normal operations, the DAQP card starts one scan when triggered, (software or TTL trigger in one-shot mode or sampling pulse triggers from the pacer clock in continuous mode). During the scan, each entry in the scan list will be processed until it finds the entry that has the first channel flag set to '1'. The hardware then stops scanning and waits for the next trigger. The scan will continue indefinitely if none of the list entries has the flag set to '1'. On the other hand, if more than one entry has the flag set to '1', the scan list will then be chopped into pieces. Each piece will require a trigger to be scanned. Should the flag be set to '1' on an entry other than the first, a "starting offset" will be introduced to the scan list. Channel scanning will start from the entry with the flag set to '1', run through the list, turn around and end at the one before it. Although this may be useful for diagnosis or special applications, it is the abnormal way of setting the first channel flag and should be avoided unless absolutely necessary.

#### 4.5 Trigger Circuit

The DAQP card can be triggered by software, an external TTL signal, the analog input passing through the preset threshold or the pacer clock. For the TTL or analog trigger, an active trigger edge can be selected for either the low-to-high or high-to-low transition.

In one-shot trigger mode, one trigger (either internal or external), will start one and only one scan of all channels specified in the scan list. (The pacer clock has no effect in this mode although it is good practice to program the pacer clock with a divisor greater than 2). Multiple scans can be initiated by issuing multiple triggers.

In continuous trigger mode (without pre-trigger), the software, TTL or analog trigger initiates a series of scans. The first scan begins immediately on receiving a trigger, while the rest are carried out each time the pacer clock fires. The process will continue until an A/D stop command is received.

If the internal trigger (or the software trigger) is selected, the trig/arm command will serve as a trigger when received by the DAQP card. For the external trigger sources (TTL or analog), the same command will be taken as an arm command, which arms the DAQP card so that the first proper trigger edge following the arm command will serve as the trigger. Unexpected edge transitions during the trigger source configuration are totally ignored if the DAQP card is not armed. The pre-trigger option can be selected in continuous mode (not in one-shot mode) with external trigger sources (not with an internal trigger). If the option is selected, the arm command starts the pacer clock so the input channels specified in the scan list will be scanned each time the pacer clock fires. The results will then be stored in the data FIFO. Once the data FIFO almost full threshold is reached, (it should be programmed as an integer multiple of the scan list length), the least recent scan is automatically discarded and the most recent scan is placed into the data FIFO. This cycle will continue until the external trigger (TTL or analog) is received. From then on, no more scans are discarded and the normal data acquisition process starts with FIFO half full of data samples. In fact, the A/D event bits (bits 3 and 4 in the status register at base + 2) will not be set until the trigger is received. This guarantees that no interrupts will be sent before the trigger is received.

The trigger position in the received data can be determined by subtracting the offset of the programmed data FIFO threshold. The position resolution will be within one pacer clock cycle. However, the trigger position cannot be determined if the trigger comes before the data FIFO is filled to it's programmed threshold. The data lost bit in the status register will be set to indicate this error.

#### 4.6 A/D Converter and Data FIFO

The DAQP card always assumes a bipolar input range of  $\pm 10V$  if the gain is one. The output data format will always be in 2's complement (and left justified for 12-bit versions). The data acquisition time of the A/D converter is 2 µs while it's conversion time is no more than 8 µs. The output of the A/D converter is fed into a data FIFO providing data buffering of up to 512 samples (2048 with 2K option installed).

The A/D converter, once triggered, will complete conversion for every analog input channel specified in the scan list at the specified scan speed and then feed the results into the data FIFO. In between scans, the DAQP card waits until another trigger is received (one-shot mode) or the pacer clock fires (continuous mode).

The data FIFO has two programmable thresholds, one for almost full and the other for almost empty. The DAQP card uses the almost full threshold and ignores the other one.

The data FIFO should always be flushed prior to using the arm/trig command to start data acquisition. When the FIFO is flushed or emptied by the host reading its content, the FIFO empty flag will be set. As long as there are samples left in the data FIFO, the empty flag will be cleared.

When the number of data samples in the FIFO becomes greater than the programmed almost full threshold, the almost full flag is set. When the number becomes less than or equal to the specified almost full threshold, the flag will be cleared. On power up or reset, the threshold is defaulted at 7 bytes to full (3.5 samples). Correct setting of the threshold will help achieve optimal performance of the card.

When the FIFO is full, the full flag will be set, and no more samples can be written into the FIFO. At the end of each scan, the DAQP card will set the data lost flag if the data FIFO is already full. This flag will not be set before or during the scan, but at the end of it. Once the data lost flag is set, it will not be cleared until the status register is read.

The data lost bit in the status register (base + 2) will be set when data continues to enter the A/D data FIFO while it is already full. With the pre-trigger option, the data lost bit is also set when an external trigger is received before the programmed data FIFO threshold is reached.

#### 4.7 Interrupt and Status

The DAQP card has three interrupt sources, the end-of-scan (EOS) interrupt, the FIFO threshold interrupt and the timer interrupt. The control register (base + 2, write only) has two bits to enable or disable the EOS and FIFO interrupts independently. However, it is strongly recommended that the two interrupts be used exclusively. Bit 5 of the auxiliary control register (base + 15, write only) enables or disables the timer interrupt.

When the EOS interrupt is enabled, an interrupt is sent to the host at the end of each scan of the channel list. If there is only one channel in the scan list, the EOS interrupt is reduced to an EOC (end-of-conversion) interrupt.

The FIFO threshold interrupt, when enabled, is sent to the host when the almost full flag is set. The host can then use the "string input" instruction to move a block of samples from the FIFO. The EOS and FIFO threshold event bits in the status register (base + 2, read only) and will be set whenever the corresponding event happens. These bits can be used for indicating the source of the interrupt. Once set, the event bits will not be cleared until the host reads the status register.

When the timer interrupt is enabled, an interrupt is sent to the host whenever the timer overflows. The corresponding event bit is in the auxiliary status register (bit 4 at base +15, read only). Reading the register will not clear this event. It can only be cleared by writing a "0" to bit 5 of the auxiliary control register which disables the timer interrupt.

#### 4.8 Digital I/O

The DAQP card has one digital input port (base + 3, read only) of four bits (bits 0-3), and one digital output port (base + 3, write only) of four bits (bits 0-3). The output port is latched, but the input port is not.

Four input lines are connected to the digital input port, each representing one bit in the port. When reading the digital input port, the CURRENT status of the digital input lines are returned to the host.

All four input lines are shared with other functions. Bit 0 is shared as the external trigger input, while bit 2 is shared as the external clock input. Bits 1 and 3 are taken over as the external gain selection lines if there is an expansion card(s) connected and the expansion bit in the control register is set to '1'. In this case, the digital output lines are driven by the external channel selection bits of the current scan list entry. Otherwise, they will be connected to the latched bits 0-3 of the digital output port. The current status of the digital input lines will always be returned when the host reads the digital input port regardless of whether the lines are shared or not.

#### 4.9 A/D State Machine

The DAQP card has an internal state machine that controls A/D operation, (see Figure 4-1). The state machine defaults to S0 after power up or reset. The normal state flow would be first S0 to S3, initiated by a scan list (queue) flush command (RSTQ). Then the queue must be programmed by writing into the queue (base + 1). With the queue being programmed, the next step is moving the state machine from S3 back to S0. This is done by issuing a flush data FIFO command (RSTF), which sets up the gain and channel selections for the first channel in the scan list and then waits for a trigger to start the scan. When the trigger (ADCLK) comes, the state machine moves from S0 to S1 and then A/D conversion is started. The state machine will wait at S2 until the conversion is completed. It then moves to S4, where the A/D conversion result is written into the data FIFO. The scan rate is determined by the time the state machine moves from S1 to S4, which can be programmed as either 10, 20 or 40 ms. If there are more channels left in the scan list, the state machine will skip to S1 for another conversion loop. Otherwise it will return to S0, waiting for another trigger (or a sampling pulse from the pacer clock if in continuous trigger mode). Any time during data acquisition, an A/D stop command will stop the data acquisition by moving the state machine back to S0.

Figure 4-1. Transition Diagram of A/D Conversion Process

It is important that the sequence of S0-S3-S0 be followed as described above. The user must issue two commands to the DAQP card: the flush scan list command (RSTQ) and the flush data FIFO command (RSTF). This guarantees that the scan list and the data FIFO are flushed properly for the expected data acquisition. Once the flush data FIFO command is issued, the DAQP card will prepare the first channel in the scan list and then return to state S0 waiting for the first trigger. Anytime the data FIFO is flushed, the default threshold setting will be restored (7 bytes to full) by the hardware. The data FIFO threshold should always be programmed after flushing if the required threshold is different from the default threshold.

#### 4.10 D/A Circuit

The DAQP series PC card is equipped with two D/A channels. The 12-bit D/A converter is a serial converter supporting synchronous update and is configured for a bipolar output range from -5V to +5V. The 12-bit output data format is always in 2's complement (right justified), with the upper 4 bits indicating the output channel number (binary '0000' for channel 0 and '0001' for channel 1).

The D/A data port occupies two bytes (write only) in the I/O space, base + 8 being the low byte and base + 9 the high byte. It is recommended that the data port be accessed with a single 16 bit I/O write instruction. If an 8 bit I/O instruction is used, the low byte should be written first, followed by the high byte.

The serial link from the D/A port to the D/A converter contains a 16 bit buffer register and a 16 bit shift register. A data word written into the D/A port is first written into the buffer register, then is loaded to the shift register and finally sent to the input register of the corresponding D/A channel. Bit 5 of the auxiliary status register (base + 15, read) indicates whether the D/A port buffer register is occupied ('1') or empty ('0'). It is recommended that the D/A port be accessed only when this bit is "0" to prevent possible data loss or corruption.

Inside the D/A converter, each channel has a 16 bit shift register, plus a 12 bit input and a 12 bit output register. The data loaded to the output register determines the analog output of the D/A channel.

The DAQP series PC card has 4 D/A operation modes (mode 0 to 3). Mode 0 is the direct update mode. The corresponding D/A channel output register will be updated immediately after the data word is written into the D/A port (if byte I/O is used, after the high byte is written). There is no synchronization between the two channels in this mode.

Modes 1, 2 and 3 all use synchronized update in which the two D/A channels are updated synchronously upon certain event. In mode 1, the event is the independent timer/counter overflow. In mode 2, the event is external gate control moving from low to high. In mode 3, the event is the pacer clock. In synchronous update modes, the data word written to each D/A channel will be buffered in it's input register first and then gets loaded into the output register when the corresponding event (depending on the mode) is received. Synchronous update modes can be used to generate waveforms with accurate phase requirements, such as orthogonal sinusoidal waveforms (sine and cosine).

#### 4.11Timer/Counter

In addition to the 24 bit pacer clock, the DAQP series card is equipped with an independent 16 bit timer/counter. It has an internal clock source of 1 MHz and an external clock input that is shared with the pacer clock external input. The timer circuit contains a 16 bit reload register, a 16 bit up-counter and a 16 bit read-latch register. The reload register holds the initial value for the counter. The initial value is also set each time it overflows. The read-latch register will latch the current count of the counter each time it receives the latch command (writing '1' into

bit 3 of the command register at base + 7). The integrity of the latched count is guaranteed by the logic design.

The timer port is allocated at base + 10 (low byte) and base + 11 (high byte). The 16 bit reload register is accessed when writing to the port, while the read-latch register is accessed when reading the port. The up-counter cannot be accessed directly.

Bit 4 of the auxiliary control register selects the timer clock source. The 1 MHz internal clock source will be selected if the bit is set to "0". The external clock source (or the counter pulse input) is selected if the bit is set to "1". Because of the I/O pin confinement, the timer external clock input is shared with the pacer clock external input (also shared as digital input bit 2).

Bits 3 and 2 in the auxiliary control register (base + 15) control the timer operation. There are four modes (modes 0, 1, 2 and 3 corresponding to 00, 01, 10 and 11 respectively). In mode 0, the counter will stop and reload the initial value when it detects the rising edge of the selected clock source. In mode 1, the counter will pause counting, but not reload as it does in mode 0. Mode 2 is the counting mode in which the counter will count up each time it detects the rising edge of the selected clock source. In mode 3, the counter will be controlled by the external gate signal. Counting proceeds when the gate signal is high and pauses when it is low.

Three I/O pins are associated with the timer: the external clock source input (shared with the pacer clock), external gate control (shared with the D/A) and the timer overflow pulse output (TTL) which goes high when the timer reaches its final count (hexadecimal FFFF).

The reload register can be set up for both counting and timing operations. The value written into the reload register, referred to as X for the sake of discussion, determines the divisor or modulus for timing and counting. Since the final count before reloading is always 65535 (hexadecimal FFFF) for the up-counter, the reload (initial) value determines where the counting will start. Therefore, 65536 - X will be the divisor for timing operations or the modulus for counting operations. For example, a divide-by-2 timer (or modulus 2 counter) can be configured by setting X equal to 65534, while X = 0 implies the divisor is 65536 (or the modulus is 65536). It is recommended that X = 65535 (hexadecimal FFFF) be avoided because the timer will stick at this final count even though the hardware will not reject or indicate such a setting. Changing the reload register "on the fly" is allowed, but the setting will not take effect until the up-counter reaches its final count (65535 or hexadecimal FFFF). The next clock rising edge will load the counter with the new setting.

Bit 5 in the auxiliary control register (base + 15) enables (when set to 1) or disables (when set to 0) the timer interrupt. When enabled, an interrupt will be sent each time the up-counter overflows (passes through its final count). Whether the timer interrupt is enabled or not, setting bit 4 in the auxiliary status register to "1" indicates the overflow event has been detected at least once since the last time the bit was cleared by writing a "1" into bit 5 of the auxiliary control register. Reading the auxiliary status register will not clear this bit.

# 5. I/O Registers

# 5.1 PCMCIA Interface

The information in this section is provided for those who need low level PCMCIA interface details for the DAQP card. The client driver or enabler that comes with the DAQP card will be sufficient for most applications.

The DAQP card performs data acquisition for all host computers equipped with a version 2.10 compliant PCMCIA interface. The DAQP card has a form factor of type II (5 mm thick). The card is highly flexible with respect to addressing and interrupt level use. It can be configured either as a memory only interface or as an I/O interface and can be powered up or down with the help of PCMCIA card and socket services. The DAQP card provides a single interrupt that can be routed to any system interrupt via the PCMCIA socket controller.

There are two sets of registers on the DAQP card: the program registers and the configuration registers.

Program registers fall under program control and belong to the DAQP card. The I/O location of these registers is controlled by the PCMCIA socket configuration and by the contents of the PCMCIA configuration registers.

The configuration registers are as those defined in the PCMCIA 2.10 specification and are located in the DAQP card's configuration space at offset 8000H. The configuration space also contains the Card Information Structure (CIS) which is located at offset 0000H. The CIS memory contains information about the DAQP card as defined by the PCMCIA 2.10 specification. It is recommended that configuration and power up/down control of the DAQP card be carried out through the standard card and socket services although an enabler can be used to complete these tasks.

Two PCMCIA configuration registers are supported by the DAQP card, (see Table 5-1): the Configuration Option Register and the Card Configuration and Status Register.

| Offset | Access | Description                            |

|--------|--------|----------------------------------------|

| 0x8000 | R/W    | Configuration Option Register          |

| 0x8002 | R/W    | Card Configuration and Status Register |

Table 5-1. PCMCIA Configuration Registers

# 5.1.1 Configuration and Option Register (COR)