# ottware Manu

# **RENESAS 32-BIT RISC SINGLE-CHIP MICROCOMPUTER**

Before using this material, please visit our website to confirm that this is the most current document available.

Rev. 1.01 Revision date: Oct 31, 2003 RenesasTechnology www.renesas.com

Download from Www.Somanuals.com. All Manuals Search And Download.

#### Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/ or the country of destination is prohibited.

- Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

## **REVISION HISTORY**

## M32R-FPU Software Manual

| Rev. | Date         |               | Description                                                                                                                                                                   |

|------|--------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |              | Page          | Summary                                                                                                                                                                       |

| 1.00 | Jan 08, 2003 | -             | First edition issued                                                                                                                                                          |

| 1.01 | Oct 31, 2003 | APPENDICES-3  | Hexadecimal Instruction Code Table corrected (BTST instruction)                                                                                                               |

|      |              | APPENDICES-8  | Appendix Figure 3.1.1 corrected<br>Incorrect) *The E1 stage of the FDIV instruction requires 13 cycles.<br>Correct) *The E1 stage of the FDIV instruction requires 14 cycles. |

|      |              | APPENDICES-10 | Appendix Figure 3.2.1 corrected<br>Incorrect) LD1 Correct) LDI                                                                                                                |

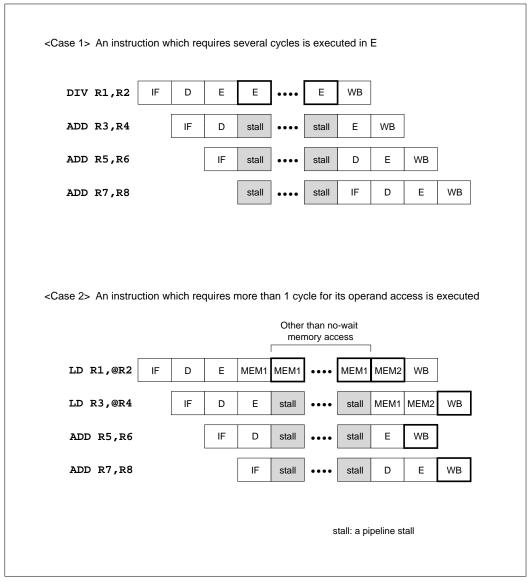

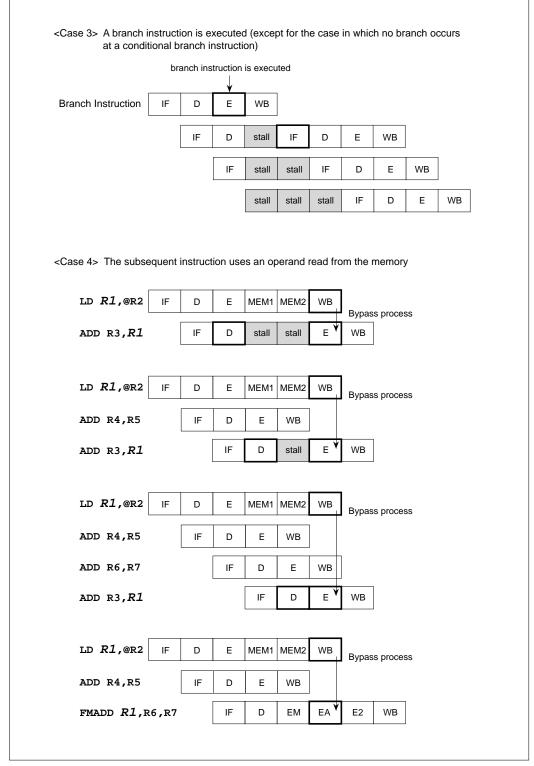

|      |              | APPENDICES-13 | Appendix Figure 3.2.4 corrected<br>Incorrect) ADD <i>R1</i> ,R6,R7 Correct) FMADD <i>R1</i> ,R6,R7                                                                            |

|      |              |               |                                                                                                                                                                               |

# Table of contents

#### CHAPTER 1 CPU PROGRAMMING MODEL

| 1.1 CPU register 1-2                                 |

|------------------------------------------------------|

| 1.2 General-purpose registers 1-2                    |

| 1.3 Control registers 1-3                            |

| 1.3.1 Processor status word register: PSW (CR0) 1-4  |

| 1.3.2 Condition bit register: CBR (CR1) 1-5          |

| 1.3.3 Interrupt stack pointer: SPI (CR2)             |

| User stack pointer: SPU (CR3)1-5                     |

| 1.3.4 Backup PC: BPC (CR6) 1-5                       |

| 1.3.5 Floating-Point Status Register: FPSR (CR7) 1-6 |

| 1.3.6 Floating-Point Exceptions (FPE) 1-8            |

| 1.4 Accumulator 1-11                                 |

| 1.5 Program counter 1-11                             |

| 1.6 Data format 1-12                                 |

| 1.6.1 Data type 1-12                                 |

| 1.6.2 Data format 1-13                               |

| 1.7 Addressing mode 1-15                             |

#### CHAPTER 2 INSTRUCTION SET

| 2.1 Instruction set overview      | 2-2    |

|-----------------------------------|--------|

| 2.1.1 Load/store instructions     | . 2-2  |

| 2.1.2 Transfer instructions       | . 2-4  |

| 2.1.3 Operation instructions      | . 2-4  |

| 2.1.4 Branch instructions         | . 2-6  |

| 2.1.5 EIT-related instructions    | . 2-8  |

| 2.1.6 DSP function instructions   | . 2-8  |

| 2.1.7 Floating-point Instructions | . 2-11 |

| 2.1.8 Bit Operation Instructions  | . 2-11 |

| 2.2 Instruction format            | 2-12   |

(1)

#### CHAPTER 3 INSTRUCTIONS

| 3.1 Conventions for instruction description | 3-2 |

|---------------------------------------------|-----|

| 3.2 Instruction description                 | 3-5 |

#### APPENDIX

| Appendix 1 Hexadecimal Instraction Code Appendix-2                       |

|--------------------------------------------------------------------------|

| Appendix 2 Instruction List Appendix-4                                   |

| Appendix 3 Pipeline Processing Appendix-8                                |

| Appendix 3.1 Instructions and Pipeline Processing Appendix-8             |

| Appendix 3.2 Pipeline Basic Operation Appendix-10                        |

| Appendix 4 Instruction Execution Time Appendix-17                        |

| Appendix 5 IEEE754 Specification Overview Appendix-18                    |

| Appendix 5.1 Floating Point Formats Appendix-18                          |

| Appendix 5.2 Rounding Appendix-20                                        |

| Appendix 5.3 Exceptions Appendix-20                                      |

| Appendix 6 M32R-FPU Specification Supplemental Explanation Appendix-23   |

| Appendix 6.1 Operation Comparision: Using 1 instruction (FMADD or FMSBU) |

| vs. two instructions (FMUL and FADD) Appendix-23                         |

| Appendix 6.1.1 Rounding Mode Appendix-23                                 |

| Appendix 6.1.2 Exception occurring in Step 1 Appendix-23                 |

| Appendix 6.2 Rules concerning Generation of QNaN in M32R-FPU Appendix-28 |

| Appendix 7 Precautions Appendix-29                                       |

| Appendix 7.1 Precautions to be taken when aligning data Appendix-29      |

#### INDEX

This page left blank intentionally.

# CHAPTER 1

# **CPU PROGRAMMIING MODEL**

- 1.1 CPU Register

- 1.2 General-purpose Registers

- 1.3 Control Registers

- 1.4 Accumulator

- 1.5 Program Counter

- 1.6 Data Format

- 1.7 Addressing Mode

# 1.1 CPU Register

The M32R family CPU, with a built-in FPU (herein referred to as M32R-FPU) has 16 general-purpose registers, 6 control registers, an accumulator and a program counter. The accumulator is of 56-bit configuration, and all other registers are a 32-bit configuration.

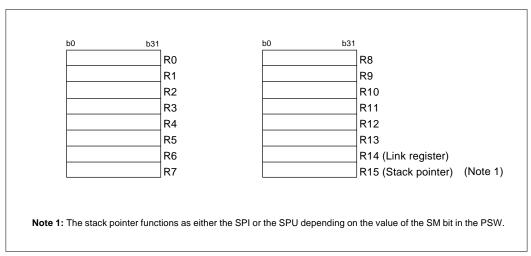

# 1.2 General-purpose Registers

The 16 general-purpose registers (R0 - R15) are of 32-bit width and are used to retain data and base addresses, as well as for integer calculations, floating-point operations, etc. R14 is used as the link register and R15 as the stack pointer. The link register is used to store the return address when executing a subroutine call instruction. The Interrupt Stack Pointer (SPI) and the User Stack Pointer (SPU) are alternately represented by R15 depending on the value of the Stack Mode (SM) bit in the Processor Status Word Register (PSW).

At reset release, the value of the general-purpose registers is undefined.

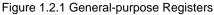

# **1.3 Control Registers**

There are 6 control registers which are the Processor Status Word Register (PSW), the Condition Bit Register (CBR), the Interrupt Stack Pointer (SPI), the User Stack Pointer (SPU), the Backup PC (BPC) and the Floating-point Status Register (FPSR). The dedicated **MVTC** and **MVFC** instructions are used for writing and reading these control registers.

In addition, the SM bit, IE bit and C bit of the PSW can also be set by the SETPSW instruction or the CLRPSW instruction.

Figure 1.3.1 Control Registers

#### 1.3.1 Processor Status Word Register: PSW (CR0)

| b0       | 1        | 2  | 3        | 4        | 5        | 6  | 7       | 8       | 9       | 10  | 11  | 12       | 13  | 14  | b15    |

|----------|----------|----|----------|----------|----------|----|---------|---------|---------|-----|-----|----------|-----|-----|--------|

| 0        | 0        | 0  | 10       | 1 0      | 10       | 10 | 1 0     | 1 0     | Ιο      | I 0 | 1 0 | 1 0      | 1 0 | 1 0 | 1 0    |

| •        | 0        | Ū  | <u> </u> | <u> </u> | <u> </u> |    |         | U V     | 0       | v   | v   | <u> </u> | Ŭ   |     | - U    |

| b16      | 17       | 18 | 19       | 20       | 21       | 22 | 23      | 24      | 25      | 26  | 27  | 28       | 29  | 30  | b31    |

| BSM<br>? | BIE<br>? | 0  | 0        | 0        | 0        | 0  | BC<br>? | SM<br>0 | IE<br>0 | 0   | 0   | 0        | 0   | 0   | C<br>0 |

|          |          |    |          | •        |          |    |         |         |         |     |     |          |     |     |        |

|          |          |    | BPS      | N field  |          |    |         |         |         |     | PS  | W field  |     |     |        |

| < At reset release: "B'0000 0000 0000 0000 ??00 000? 0000 0000 > |

|------------------------------------------------------------------|

|------------------------------------------------------------------|

| b     | Bit Name                            | Function                                              | R | W |

|-------|-------------------------------------|-------------------------------------------------------|---|---|

| D-15  | No function assigned. Fix to "      | 0".                                                   | 0 | 0 |

| 16    | BSM                                 | Saves value of SM bit when EIT occurs                 | R | W |

|       | Backup SM Bit                       |                                                       |   |   |

| 17    | BIE                                 | Saves value of IE bit when EIT occurs                 | R | W |

|       | Backup IE Bit                       |                                                       |   |   |

| 8-22  | No function assigned. Fix to "      | 0".                                                   | 0 | 0 |

| 23    | BC                                  | Saves value of C bit when EIT occurs                  | R | W |

|       | Backup C Bit                        |                                                       |   |   |

| 24    | SM                                  | 0: Uses R15 as the interrupt stack pointer            | R | W |

|       | Stack Mode Bit                      | 1: Uses R15 as the user stack pointer                 |   |   |

| 25    | IE                                  | 0: Does not accept interrupt                          | R | W |

|       | Interrupt Enable Bit                | 1: Accepts interrupt                                  |   |   |

| 26-30 | No function assigned. Fix to "      | 0".                                                   | 0 | 0 |

| 31    | С                                   | Indicates carry, borrow and overflow resulting        | R | W |

|       | Condition Bit                       | from operations (instruction dependent)               |   |   |

|       | No function assigned. Fix to "<br>C | 0".<br>Indicates carry, borrow and overflow resulting |   | - |

The Processor Status Word Register (PSW) indicates the M32R-FPU status. It consists of the current PSW field which is regularly used, and the BPSW field where a copy of the PSW field is saved when EIT occurs.

The PSW field consists of the Stack Mode (SM) bit, the Interrupt Enable (IE) bit and the Condition (C) bit.

The BPSW field consists of the Backup Stack Mode (BSM) bit, the Backup Interrupt Enable (BIE) bit and the Backup Condition (BC) bit.

At reset release, BSM, BIE and BC are undefined. All other bits are "0".

#### 1.3.2 Condition Bit Register: CBR (CR1)

The Condition Bit Register (CBR) is derived from the PSW register by extracting its Condition (C) bit. The value written to the PSW register's C bit is reflected in this register. The register can only be read. (Writing to the register with the **MVTC** instruction is ignored.)

At reset release, the value of CBR is "H'0000 0000".

|     | b0 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | b31 |

|-----|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| CBR | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | С   |

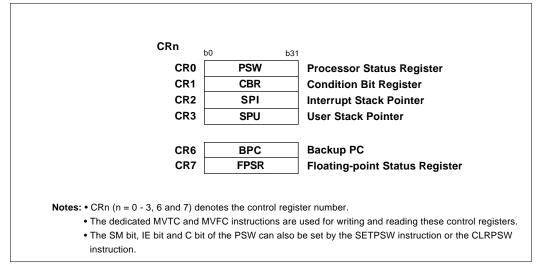

#### 1.3.3 Interrupt Stack Pointer: SPI (CR2)

User Stack Pointer: SPU (CR3)

The Interrupt Stack Pointer (SPI) and the User Stack Pointer (SPU) retain the address of the current stack pointer. These registers can be accessed as the general-purpose register R15. R15 switches between representing the SPI and SPU depending on the value of the Stack Mode (SM) bit in the PSW. At reset release, the value of the SPI and SPU are undefined.

#### 1.3.4 Backup PC: BPC (CR6)

The Backup PC (BPC) is used to save the value of the Program Counter (PC) when an EIT occurs. Bit 31 is fixed to "0".

When an EIT occurs, the register sets either the PC value when the EIT occurred or the PC value for the next instruction depending on the type of EIT. The BPC value is loaded to the PC when the **RTE** instruction is executed. However, the values of the lower 2 bits of the PC are always "00" when returned (PC always returns to the word-aligned address).

At reset release, the value of the BPC is undefined.

|     | b0 | ) |  |  |   |  |  |  |  |  |    |    |  |   |  |      |   |  |  |  | b3 | 31 |

|-----|----|---|--|--|---|--|--|--|--|--|----|----|--|---|--|------|---|--|--|--|----|----|

| BPC |    |   |  |  | 1 |  |  |  |  |  | BF | °C |  | 1 |  | <br> | 1 |  |  |  | 0  | ,  |

#### 1.3.5 Floating-point Status Register: FPSR (CR7)

1

| b0      | 1       | 2       | 3       | 4       | 5       | 6  | 7 | 8 | 9  | 10 | 11  | 12 | 13 | 14  | b15 |

|---------|---------|---------|---------|---------|---------|----|---|---|----|----|-----|----|----|-----|-----|

| FS<br>0 | FX<br>0 | FU<br>0 | FZ<br>0 | FO<br>0 | FV<br>0 | 0  | 0 | 0 | 10 | 0  | I 0 | 10 | 0  | I 0 | 10  |

|         | 17      | 18      | 19      | 20      |         | 22 |   |   | 25 |    | 27  | 28 | 29 | 30  | b31 |

| 0       | EX<br>0 | EU<br>0 | EZ<br>0 | EO<br>0 |         | 0  | - |   |    | -  |     |    |    |     |     |

<At reset release: H0000 0100>

| b    | Bit Name                                | Function                                           | R | W |

|------|-----------------------------------------|----------------------------------------------------|---|---|

| 0    | FS                                      | Reflects the logical sum of FU, FZ, FO and FV.     | R | - |

|      | Floating-point Exception<br>Summary Bit |                                                    |   |   |

| 1    | FX                                      | Set to "1" when an inexact exception occurs        | R | W |

|      | Inexact Exception Flag                  | (if EIT processing is unexecuted (Note 1)).        |   |   |

|      |                                         | Once set, the flag retains the value "1" until     |   |   |

|      |                                         | it is cleared to "0" in software.                  |   |   |

| 2    | FU                                      | Set to "1" when an underflow exception occurs      | R | W |

|      | Underflow Exception Flag                | (if EIT processing is unexecuted (Note 1)).        |   |   |

|      |                                         | Once set, the flag retains the value "1" until     |   |   |

|      |                                         | it is cleared to "0" in software.                  |   |   |

| 3    | FZ                                      | Set to "1" when a zero divide exception occurs     | R | W |

|      | Zero Divide Exception Flag              | (if EIT processing is unexecuted (Note 1)).        |   |   |

|      |                                         | Once set, the flag retains the value "1" until     |   |   |

|      |                                         | it is cleared to "0" in software.                  |   |   |

| 4    | FO                                      | Set to "1" when an overflow exception occurs       | R | W |

|      | Overflow Exception Flag                 | (if EIT processing is unexecuted (Note 1)).        |   |   |

|      |                                         | Once set, the flag retains the value "1" until     |   |   |

|      |                                         | it is cleared to "0" in software.                  |   |   |

| 5    | FV                                      | Set to "1" when an invalid operation exception     | R | W |

|      | Invalid Operation Exception             | occurs (if EIT processing is unexecuted (Note 1)). |   |   |

|      | Flag                                    | Once set, the flag retains the value "1" until     |   |   |

|      |                                         | it is cleared to "0" in software.                  |   |   |

| 6–16 | No function assigned. Fix to "0         | )".                                                | 0 | 0 |

| 17   | EX                                      | 0: Mask EIT processing to be executed when an      | R | W |

|      | Inexact Exception Enable                | inexact exception occurs                           |   |   |

|      | Bit                                     | 1: Execute EIT processing when an inexact          |   |   |

|      |                                         | exception occurs                                   |   |   |

| 18   | EU                                      | 0: Mask EIT processing to be executed when an      | R | W |

|      | Underflow Exception Enable              | underflow exception occurs                         |   |   |

|      | Bit                                     | 1: Execute EIT processing when an underflow        |   |   |

|      |                                         | exception occurs                                   |   |   |

| 19   | EZ                                      | 0: Mask EIT processing to be executed when a       | R | W |

|      | Zero Divide Exception                   | zero divide exception occurs                       |   |   |

|      | Enable Bit                              | 1: Execute EIT processing when a zero divide       |   |   |

|      |                                         | exception occurs                                   |   |   |

| 20   | EO                                      | 0: Mask EIT processing to be executed when an      | R | W |

|      | Overflow Exception                      | overflow exception occurs                          |   |   |

|      | Enable Bit                              | 1: Execute EIT processing when an overflow         |   |   |

|      |                                         | exception occurs                                   |   |   |

Download from Www.Somanuals.com. All Manuals Search And Download.

#### **CPU PROGRAMMING MODEL**

#### **1.3 Control Registers**

| 21     | EV                              | 0: Mask EIT processing to be executed when an      | R    | W       |

|--------|---------------------------------|----------------------------------------------------|------|---------|

| 21     | Invalid Operation Exception     | invalid operation exception occurs                 | ix.  |         |

|        | Enable Bit                      | 1: Execute EIT processing when an invalid          |      |         |

|        |                                 | operation exception occurs                         |      |         |

| 22     | No function assigned. Fix to "0 |                                                    | 0    | 0       |

| 23     | DN                              | 0: Handle the denormalized number as a             | R    | W       |

|        | Denormalized Number Zero        | denormalized number                                |      |         |

|        | Flash Bit (Note 2)              | 1: Handle the denormalized number as zero          |      |         |

| 24     | CE                              | 0: No unimplemented operation exception occurred . | R (I | Note 3  |

|        | Unimplemented Operation         | 1: An unimplemented operation exception occurred.  |      |         |

|        | Exception Cause Bit             | When the bit is set to "1", the execution of an    |      |         |

|        |                                 | FPU operation instruction will clear it to "0".    |      |         |

| 25     | CX                              | 0: No inexact exception occurred.                  | R (I | Note 3) |

|        | Inexact Exception Cause         | 1: An inexact exception occurred.                  |      |         |

|        | Bit                             | When the bit is set to "1", the execution of an    |      |         |

|        |                                 | FPU operation instruction will clear it to "0".    |      |         |

| 26     | CU                              | 0: No underflow exception occurred.                | R (I | Note 3  |

|        | Underflow Exception Cause       | 1: An underflow exception occurred.                |      |         |

|        | Bit                             | When the bit is set to "1", the execution of an    |      |         |

|        |                                 | FPU operation instruction will clear it to "0".    |      |         |

| 27     | CZ                              | 0: No zero divide exception occurred.              | R (I | Note 3  |

|        | Zero Divide Exception           | 1: A zero divide exception occurred.               |      |         |

|        | Cause Bit                       | When the bit is set to "1", the execution of an    |      |         |

|        |                                 | FPU operation instruction will clear it to "0".    |      |         |

| 28     | СО                              | 0: No overflow exception occurred.                 | R (I | Note 3  |

|        | Overflow Exception              | 1: An overflow exception occurred.                 |      |         |

|        | Cause Bit                       | When the bit is set to "1", the execution of an    |      |         |

|        |                                 | FPU operation instruction will clear it to "0".    |      |         |

| 29     | CV                              | 0: No invalid operation exception occurred.        | R (I | Note 3  |

|        | Invalid Operation Exception     | 1: An invalid operation exception occurred.        |      |         |

|        | Cause Bit                       | When the bit is set to "1", the execution of an    |      |         |

|        |                                 | FPU operation instruction will clear it to "0".    |      |         |

| 30, 31 | RM                              | 00: Round to Nearest                               | R    | W       |

|        | Rounding Mode Selection Bit     | 01: Round toward Zero                              |      |         |

|        |                                 | 10: Round toward +Infinity                         |      |         |

|        |                                 | 11: Round toward -Infinity                         |      |         |

Note 1: 'If EIT processing is unexecuted' means whenever one of the exceptions occurs, enable bits 17 to 21 are set to "0" which masks the EIT processing so that it cannot be executed. If two exceptions occur at the same time and their corresponding exception enable bits are set differently (one enabled, and the other masked), EIT processing is executed. In this case, these two flags do not change state regardless of the enable bit settings.

- Note 2: If a denormalized number is given to the operand when DN = "0", an unimplemented exception occurs.

- Note 3: This bit is cleared by writing "0". Writing "1" has no effect (the bit retains the value it had before the write).

#### 1.3.6 Floating-point Exceptions (FPE)

Floating-point Exception (FPE) occurs when Unimplemented Exception (UIPL) or one of the five exceptions specified in the IEEE754 standard (OVF/UDF/IXCT/ DIV0/IVLD) is detected. Each exception processing is outlined below.

(1) Overflow Exception (OVF)

The exception occurs when the absolute value of the operation result exceeds the largest describable precision in the floating-point format. The following table shows the operation results when an OVF occurs.

|               |                    | Operation Result (Content of the Destination Register) |                                                  |

|---------------|--------------------|--------------------------------------------------------|--------------------------------------------------|

| Rounding Mode | Sign of the Result | When the OVF EIT processing is masked (Note 1)         | When the OVF EIT processing is executed (Note 2) |

| -infinity     | +                  | +MAX                                                   |                                                  |

|               | _                  | -infinity                                              |                                                  |

| +infinity     | +                  | +infinity                                              |                                                  |

|               | -                  | -MAX                                                   | No change                                        |

| 0             | +                  | +MAX                                                   |                                                  |

|               | -                  | -MAX                                                   |                                                  |

| Nearest       | +                  | +infinity                                              |                                                  |

|               | _                  | -infinity                                              |                                                  |

Note 1: When the Overflow Exception Enable (EO) bit (FPSR register bit 20) = "0" Note 2: When the Overflow Exception Enable (EO) bit (FPSR register bit 20) = "1" Note: • If an OVF occurs while EIT processing for OVF is masked, an IXCT occurs at the same time.

- +MAX = H'7F7F FFFF, –MAX = H'FF7F FFFF

- (2) Underflow Exception (UDF)

The exception occurs when the absolute value of the operation result is less than the largest describable precision in the floating-point format. The following table shows the operation results when a UDF occurs.

| Operation Result (Content of the Destination Register)                                          |  |  |

|-------------------------------------------------------------------------------------------------|--|--|

| When UDF EIT processing is masked (Note 1)         When UDF EIT processing is executed (Note 2) |  |  |

| No change                                                                                       |  |  |

| DN = 1: 0 is returned                                                                           |  |  |

|                                                                                                 |  |  |

Note 1: When the Underflow Exception Enable (EU) bit (FPSR register bit 18) = "0" Note 2: When the Underflow Exception Enable (EU) bit (FPSR register bit 18) = "1"

#### (3) Inexact Exception (IXCT)

The exception occurs when the operation result differs from a result led out with an infinite range of precision. The following table shows the operation results and the respective conditions in which each IXCT occurs.

|                                         | Operation Result (Content of the Destination Register) |                                                   |  |

|-----------------------------------------|--------------------------------------------------------|---------------------------------------------------|--|

| Occurrence Condition                    | When the IXCT EIT processing is masked (Note 1)        | When the IXCT EIT processing is executed (Note 2) |  |

| Overflow occurs in OVF masked condition | Reference OVF operation results                        | No change                                         |  |

| Rounding occurs                         | Rounded value                                          | No change                                         |  |

Note 1: When the Inexact Exception Enable (EX) bit (FPSR register bit 17) = "0" Note 2: When the Inexact Exception Enable (EX) bit (FPSR register bit 17) = "1"

#### (4) Zero Division Exception (DIV0)

The exception occurs when a finite nonzero value is divided by zero. The following table shows the operation results when a DIV0 occurs.

|                      | Operation Result (Content of                    | the Destination Register)                         |

|----------------------|-------------------------------------------------|---------------------------------------------------|

| Dividend             | When the DIV0 EIT processing is masked (Note 1) | When the DIV0 EIT processing is executed (Note 2) |

| Nonzero finite value | $\pm$ infinity (Sign is derived by exclusive-   | No change                                         |

|                      | ORing the signs of divisor and dividend)        |                                                   |

Note 1: When the Zero Division Exception Enable (EZ) bit (FPSR register bit 19) = "0" Note 2: When the Zero Division Exception Enable (EZ) bit (FPSR register bit 19) = "1"

Please note that the DIV0 EIT processing does not occur in the following conditions.

| Dividend | Behavior                                        |

|----------|-------------------------------------------------|

| 0        | An invalid operation exception occurs           |

| infinity | No exception occur (with the result "infinity") |

#### (5) Invalid Operation Exception (IVLD)

The exception occurs when an invalid operation is executed. The following table shows the operation results and the respective conditions in which each IVLD occurs.

| Occurrence Condition                                  |                                          | Operation Result (Content of the Destination Register)                                       |                                                         |

|-------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------|

|                                                       |                                          | When the IVLD EIT processing is masked (Note 1)                                              | When the IVLD EIT<br>processing is executed<br>(Note 2) |

| Operation for SNaN operand                            |                                          |                                                                                              |                                                         |

| +infinity -(+infinity), -infinity -(-ir               | finity)                                  | QNaN                                                                                         |                                                         |

| 0 X infinity                                          |                                          |                                                                                              |                                                         |

| 0 ÷ 0, infinity ÷ infinity                            | 0 ÷ 0, infinity ÷ infinity               |                                                                                              |                                                         |

| When an integer conversion overflowed                 | When FTOI<br>instruction<br>was executed | Return value when<br>pre-conversion signed bit is:<br>"0" = H'7FFF FFFF<br>"1" = H'8000 0000 | No change                                               |

| When NaN or Infinity was<br>converted into an integer | When FTOS<br>instruction<br>was executed | Return value when<br>pre-conversion signed bit is:<br>"0" = H'0000 7FFF<br>"1" = H'FFF 8000  |                                                         |

| When < or > comparison was<br>performed on NaN        | •                                        | Comparison results<br>(comparison invalid)                                                   |                                                         |

Note 1: When the Invalid Operation Exception Enable (EV) bit (FPSR register bit 21) = "0" Note 2: When the Invalid Operation Exception Enable (EV) bit (FPSR register bit 21) = "1" Notes: • NaN (Not a Number)

SNaN (Signaling NaN): a NaN in which the MSB of the decimal fraction is "0". When SNaN is used as the source operand in an operation, an IVLD occurs. SNaNs are useful in identifying program bugs when used as the initial value in a variable. However, SNaNs cannot be generated by hardware.

QNaN (Quiet NaN): a NaN in which the MSB of the decimal fraction is "1". Even when QNaN is used as the source operand in an operation, an IVLD will not occur (excluding comparison and format conversion). Because a result can be checked by the arithmetic operations, QNaN allows the user to debug without executing an EIT processing. QNaNs are created by hardware.

(6) Unimplemented Exception (UIPL)

The exception occurs when the Denormalized Number Zero Flash (DN) bit (FPSR register bit 23) = "0" and a denormalized number is given as an operation operand (Note 1).

Because the UIPL has no enable bits available, it cannot be masked when they occur. The destination register remains unchanged.

Note: • A UDF occurs when the intermediate result of an operation is a denormalized number, in which case if the DN bit (FPSR register bit 23) = "0", an UIPL occurs.

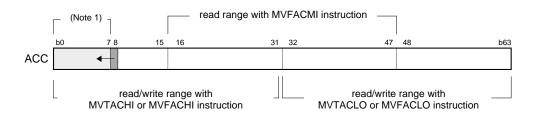

## 1.4 Accumulator

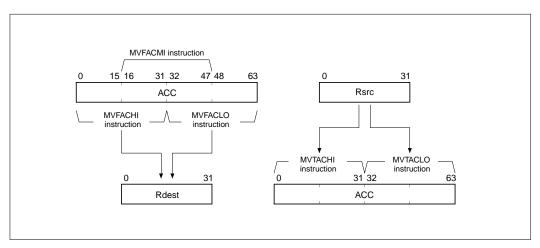

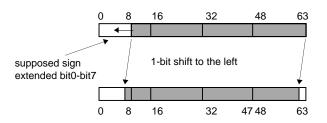

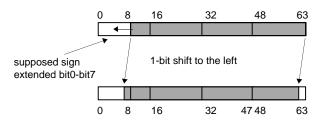

The Accumulator (ACC) is a 56-bit register used for DSP function instructions. The accumulator is handled as a 64-bit register when accessed for read or write. When reading data from the accumulator, the value of bit 8 is sign-extended. When writing data to the accumulator, bits 0 to 7 are ignored. The accumulator is also used for the multiply instruction "MUL", in which case the accumulator value is destroyed by instruction execution.

Use the MVTACHI and MVTACLO instructions for writing to the accumulator. The MVTACHI and MVTACLO instructions write data to the high-order 32 bits (bits 0-31) and the low-order 32 bits (bits 32-63), respectively.

Use the MVFACHI, MVFACLO, and MVFACMI instructions for reading data from the accumulator. The MVFACHI, MVFACLO and MVFACMI instructions read data from the high-order 32 bits (bits 0-31), the low-order 32 bits (bits 32-63) and the middle 32 bits (bits 16-47), respectively.

At reset release, the value of accumulator is undefined.

Note 1: When read, bits 0 to 7 always show the sign-extended value of bit 8. Writing to this bit field is ignored.

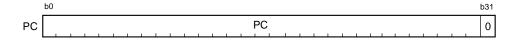

## 1.5 Program Counter

The Program Counter (PC) is a 32-bit counter that retains the address of the instruction being executed. Since the M32R CPU instruction starts with evennumbered addresses, the LSB (bit 31) is always "0".

At reset release, the value of the PC is "H'0000 0000."

## 1.6 Data Format

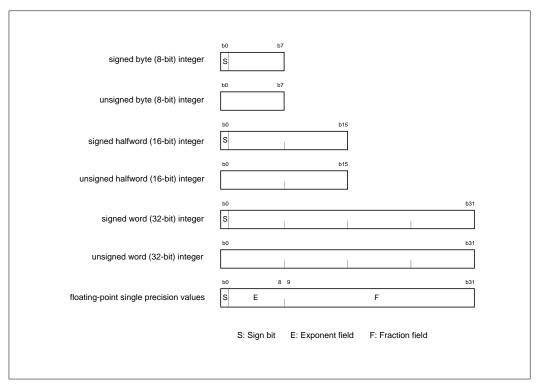

#### 1.6.1 Data Type

The data types that can be handled by the M32R-FPU instruction set are signed or unsigned 8, 16, and 32-bit integers and single-precision floating-point numbers. The signed integers are represented by 2's complements.

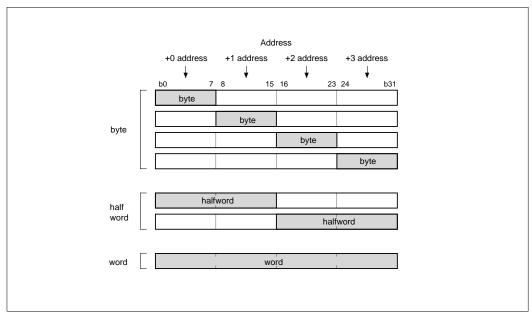

Figure 1.6.1 Data Type

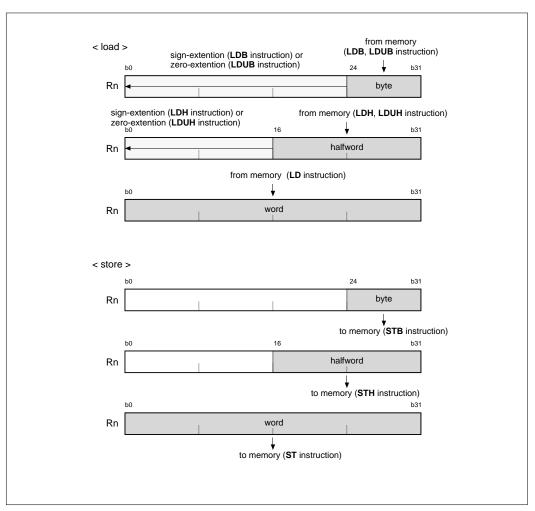

#### 1.6.2 Data Format

(1) Data format in a register

The data sizes in the M32R-FPU registers are always words (32 bits). When loading byte (8-bit) or halfword (16-bit) data from memory into a register, the data is sign-extended (LDB, LDH instructions) or zero-extended (LDUB, LDUH instructions) to a word (32-bit) quantity before being loaded into the register. When storing data from a register into a memory, the 32-bit data, the 16-bit data on the LSB side and the 8-bit data on the LSB side of the register are stored into memory by the **ST**, **STH** and **STB** instructions, respectively.

Figure 1.6.2 Data Format in a Register

#### (2) Data format in memory

The data sizes in memory can be byte (8 bits), halfword (16 bits) or word (32 bits). Although byte data can be located at any address, halfword and word data must be located at the addresses aligned with a halfword boundary (least significant address bit = "0") or a word boundary (two low-order address bits = "00"), respectively. If an attempt is made to access memory data that overlaps the halfword or word boundary, an address exception occurs.

Figure 1.6.3 Data Format in Memory

# 1.7 Addressing Mode

M32R-FPU supports the following addressing modes.

(1) Register direct [R or CR]

The general-purpose register or the control register to be processed is specified.

(2) Register indirect [@R]

The contents of the register specify the address of the memory. This mode can be used by all load/store instructions.

(3) Register relative indirect [@(disp, R)]

(The contents of the register) + (16-bit immediate value which is signextended to 32 bits) specify the address of the memory.

#### (4) Register indirect and register update

- Adds 4 to register contents [@R+] The contents of the register specify the memory address, then 4 is added to the register contents. (Can only be specified with LD instruction).

- Add 2 to register contents [@R+] [M32R-FPU extended addressing mode] The contents of the register specify the memory address, then 2 is added to the register contents. (Can only be specified with STH instruction).

- Add 4 to register contents [@+R] The contents of the register is added by 4, the register contents specify the memory address.

(Can only be specified with ST instruction).

- Subtract 4 to register contents [@-R] The content of the register is decreased by 4, then the register contents specify the memory address. (Can only be specified with ST instruction).

- (5) immediate [#imm]

The 4-, 5-, 8-, 16- or 24-bit immediate value.

(6) PC relative [pcdisp]

(The contents of PC) + (8, 16, or 24-bit displacement which is sign-extended to 32 bits and 2 bits left-shifted) specify the address of memory.

1.7 Addressing Mode

This page left blank intentionally.

# **CHAPTER 2**

# **INSTRUCTION SET**

2.1 Instruction set overview2.2 Instruction format

#### 2.1 Instruction set overview

The M32R-FPU has a total of 100 instructions. The M32R-FPU has a RISC architecture. Memory is accessed by using the load/store instructions and other operations are executed by using register-to-register operation instructions.

M32R CPU supports compound instructions such as " load & address update" and "store & address update" which are useful for high-speed data transfer.

#### 2.1.1 Load/store instructions

The load/store instructions carry out data transfers between a register and a memory.

| LD     | Load                   |

|--------|------------------------|

| LDB    | Load byte              |

| LDUB   | Load unsigned byte     |

| LDH    | Load halfword          |

| LDUH   | Load unsigned halfword |

| LOCK   | Load locked            |

| ST     | Store                  |

| STB    | Store byte             |

| STH    | Store halfword         |

| UNLOCK | Store unlocked         |

Three types of addressing modes can be specified for load/store instructions.

(1) Register indirect

The contents of the register specify the address. This mode can be used by all load/ store instructions.

(2) Register relative indirect

(The contents of the register) + (32-bit sign-extended 16-bit immediate value) specifies the address. This mode can be used by all except **LOCK** and **UNLOCK** instructions.

- (3) Register indirect and register update

- Adds 4 to register contents [@R+] The contents of the register specify the memory address, then 4 is added to the register contents.

(Can only be specified with LD instruction).

- Add 2 to register contents [@R+] [M32R-FPU extended addressing mode] The contents of the register specify the memory address, then 2 is added to the register contents.

(Can only be specified with STH instruction).

- Add 4 to register contents [@+R] The contents of the register is added by 4, the register contents specity the memory address. (Can only be specified with ST instruction).

- Subtract 4 to register contents [@-R] The content of the register is decreased by 4, then the register contents specify the memory address. (Can only be specified with ST instruction).

When accessing halfword and word size data, it is necessary to specify the address on the halfword boundary or the word boundary (Halfword size should be such that the loworder 2 bits of the address are "00" or "10", and word size should be such that the low order 2 bits of the address are "00"). If an unaligned address is specified, an address exception occurs.

When accessing byte data or halfword data with load instructions, the high-order bits are sign-extended or zero-extended to 32 bits, and loaded to a register.

#### 2.1.2 Transfer instructions

The transfer instructions carry out data transfers between registers or a register and an immediate value.

| LD24 | Load 24-bit immediate      |

|------|----------------------------|

| LDI  | Load immediate             |

| MV   | Move register              |

| MVFC | Move from control register |

| MVTC | Move to control register   |

| SETH | Set high-order 16-bit      |

#### 2.1.3 Operation instructions

Compare, arithmetic/logic operation, multiply and divide, and shift are carried out between registers.

• compare instructions

| СМР   | Compare                    |

|-------|----------------------------|

| СМРІ  | Compare immediate          |

| CMPU  | Compare unsigned           |

| CMPUI | Compare unsigned immediate |

#### • arithmetic operation instructions

| Add                                  |

|--------------------------------------|

| Add 3-operand                        |

| Add immediate                        |

| Add with overflow checking           |

| Add 3-operand with overflow checking |

| Add with carry                       |

| Negate                               |

| Subtract                             |

| Subtract with overflow checking      |

| Subtract with borrow                 |

|                                      |

• logic operation instructions

| AND  | AND                    |

|------|------------------------|

| AND3 | AND 3-operand          |

| NOT  | Logical NOT            |

| OR   | OR                     |

| OR3  | OR 3-operand           |

| XOR  | Exclusive OR           |

| XOR3 | Exclusive OR 3-operand |

|      |                        |

• multiply/divide instructions

| DIV  | Divide             |

|------|--------------------|

| DIVU | Divide unsigned    |

| MUL  | Multiply           |

| REM  | Remainder          |

| REMU | Remainder unsigned |

• shift instructions

| Shift left logical               |

|----------------------------------|

| Shift left logical 3-operand     |

| Shift left logical immediate     |

| Shift right arithmetic           |

| Shift right arithmetic 3-operand |

| Shift right arithmetic immediate |

| Shift right logical              |

| Shift right logical 3-operand    |

| Shift right logical immediate    |

|                                  |

#### 2.1.4 Branch instructions

The branch instructions are used to change the program flow.

| вс   | Branch on C-bit                         |

|------|-----------------------------------------|

| BEQ  | Branch on equal to                      |

| BEQZ | Branch on equal to zero                 |

| BGEZ | Branch on greater than or equal to zero |

| BGTZ | Branch on greater than zero             |

| BL   | Branch and link                         |

| BLEZ | Branch on less than or equal to zero    |

| BLTZ | Branch on less than zero                |

| BNC  | Branch on not C-bit                     |

| BNE  | Branch on not equal to                  |

| BNEZ | Branch on not equal to zero             |

| BRA  | Branch                                  |

| JL   | Jump and link                           |

| JMP  | Jump                                    |

| NOP  | No operation                            |

Only a word-aligned (word boundary) address can be specified for the branch address.

The addressing mode of the **BRA**, **BL**, **BC** and **BNC** instructions can specify an 8-bit or 24-bit immediate value. The addressing mode of the **BEQ**, **BNE**, **BEQZ**, **BNEZ**, **BLTZ**, **BGEZ**, **BLEZ**, and **BGTZ** instructions can specify a 16-bit immediate value.

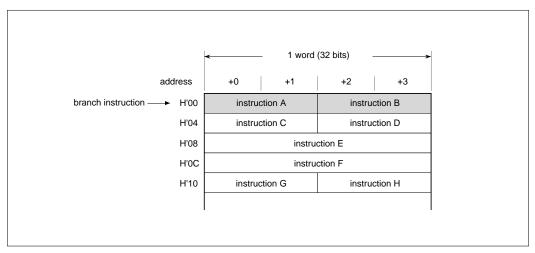

In the **JMP** and **JL** instructions, the register value becomes the branch address. However, the low-order 2-bit value of the register is ignored. In other branch instructions, (PC value of branch instruction) + (sign-extended and 2 bits left-shifted immediate value) becomes the branch address. However, the low order 2-bit value of the address becomes "00" when addition is carried out. For example, refer to **Figure 2.1.1**. When instruction A or B is a branch instruction, branching to instruction G, the immediate value of either instruction A or B becomes 4.

Simultaneous with execution of branching by the **JL** or **BL** instructions for subroutine calls, the PC value of the return address is stored in R14. The low-order 2-bit value of the address stored in R14 (PC value of the branch instruction + 4) is always cleared to "0". For example, refer to **Figure 2.1.1**. If an instruction A or B is a **JL** or **BL** instruction, the return address becomes that of the instruction C.

Fig. 2.1.1 Branch addresses of branch instruction

#### 2.1.5 EIT-related instructions

The EIT-related instructions carry out the EIT events (Exception, Interrupt and Trap). Trap initiation and return from EIT are EIT-related instructions.

TRAPTrapRTEReturn from EIT

#### 2.1.6 DSP function instructions

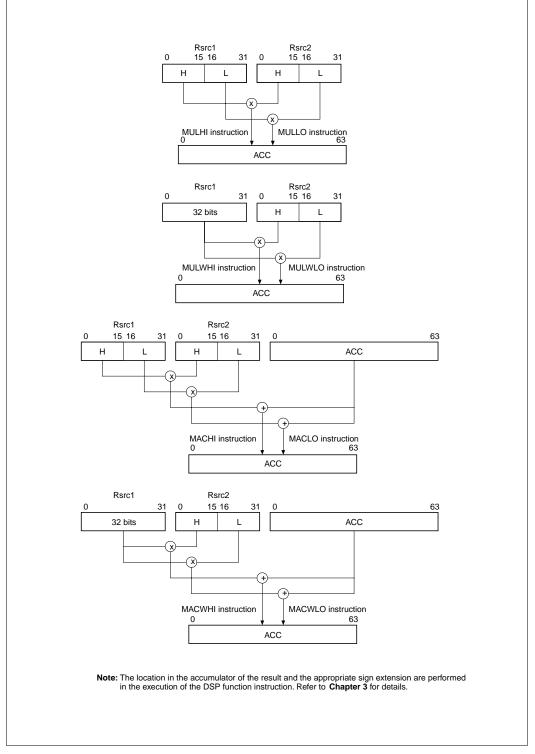

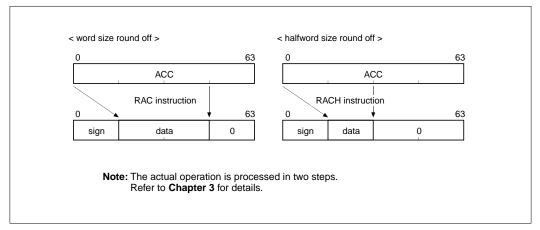

The DSP function instructions carry out multiplication of 32 bits x 16 bits and 16 bits x 16 bits or multiply and add operation; there are also instructions to round off data in the accumulator and carry out transfer of data between the accumulator and a general-purpose register.

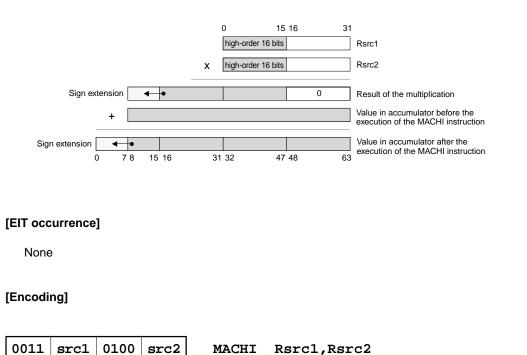

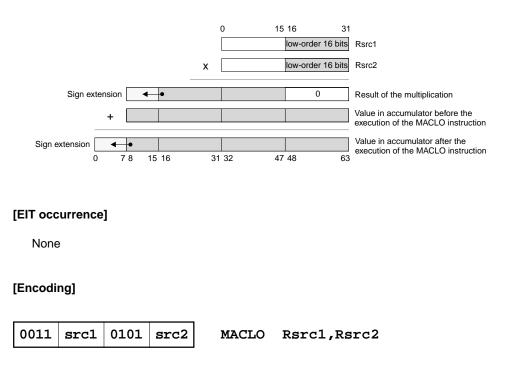

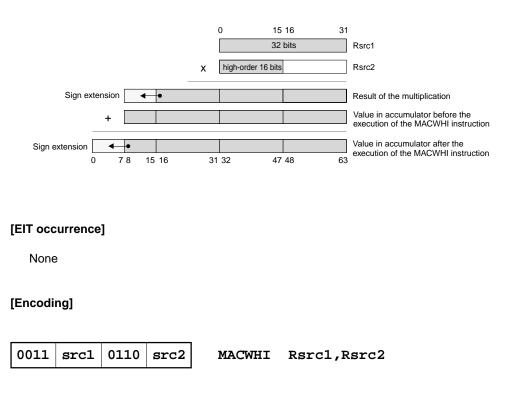

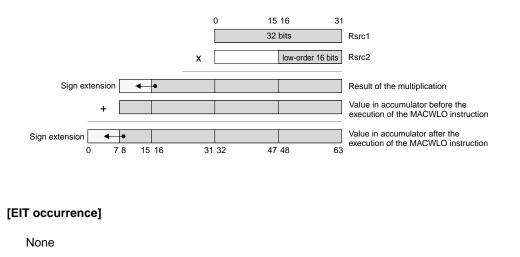

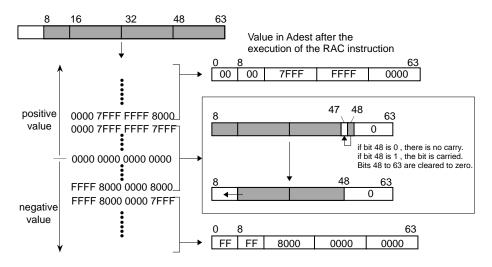

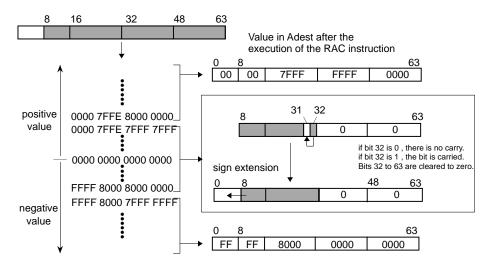

| MACHI<br>MACLO<br>MACWHI<br>MACWLO<br>MULHI<br>MULLO<br>MULWHI<br>MULWLO<br>MVFACHI<br>MVFACLO<br>MVFACMI<br>MVTACHI<br>MVTACLO<br>RAC | Multiply-accumulate high-order halfwords<br>Multiply-accumulate low-order halfwords<br>Multiply-accumulate word and high-order halfword<br>Multiply-accumulate word and low-order halfword<br>Multiply high-order halfwords<br>Multiply low-order halfwords<br>Multiply word and high-order halfword<br>Multiply word and low-order halfword<br>Multiply word and low-order halfword<br>Move high-order word from accumulator<br>Move low-order word from accumulator<br>Move middle-order word from accumulator<br>Move high-order word to accumulator<br>Move low-order word to accumulator<br>Move low-order word to accumulator<br>Round accumulator |

|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAC<br>RACH                                                                                                                            | Round accumulator<br>Round accumulator halfword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

2.1 Instruction set overview

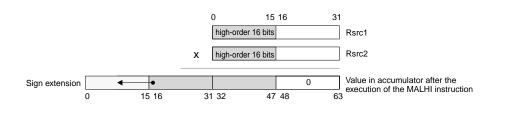

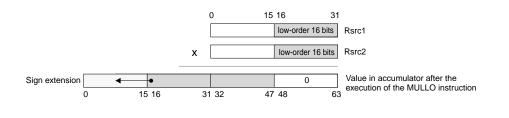

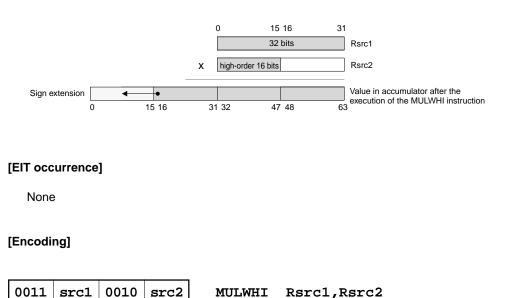

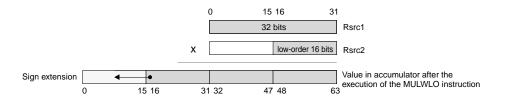

Fig. 2.1.2 DSP function instruction operation 1 (multiply, multiply and accumulate)

2.1 Instruction set overview

Fig. 2.1.3 DSP function instruction operation 2 (round off)

Fig. 2.1.4 DSP function instruction operation 3 (transfer between accumulator and register)

#### 2.1.7 Floating-point Instructions

The following instructions execute floating-point operations.

| FADD  | Floating-point add                                |

|-------|---------------------------------------------------|

| FSUB  | Floating-point subtract                           |

| FMUL  | Floating-point multiply                           |

| FDIV  | Floating-point divede                             |

| FMADD | Floating-point multiply and add                   |

| FMSUB | Floating-point multiply and subtract              |

| ITOF  | Integer to float                                  |

| UTOF  | Unsigned integer to float                         |

| FTOI  | Float to integer                                  |

| FTOS  | Float to short                                    |

| FCMP  | Floating-point compare                            |

| FCMPE | Floating-point compare with exeption if unordered |

#### 2.1.8 Bit Operation Instructions

These instructions determine the operation of the bit specified by the register or memory.

| BSET   | Bit set   |

|--------|-----------|

| BCLR   | Bit clear |

| BTST   | Bit test  |

| SETPSW | Set PSW   |

| CLRPSW | Clear PSW |

## 2.2 Instruction format

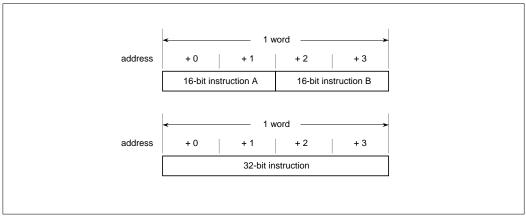

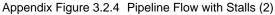

There are two major instruction formats: two 16-bit instructions packed together within a word boundary, and a single 32-bit instruction (see **Figure 2.2.1**). Figure 2.2.2 shows the instruction format of M32R CPU.

Fig. 2.2.1 16-bit instruction and 32-bit instruction

| < 1 | 6-bit in               | structio | 1 >                       |      |        |             |        |      |                                             |

|-----|------------------------|----------|---------------------------|------|--------|-------------|--------|------|---------------------------------------------|

|     | op1                    | R1       | op2                       | R2   | R1 = I | R₁ c        | p R2   |      |                                             |

|     | op1                    | R1       | c R1 = R1 op c            |      |        | op c        |        |      |                                             |

|     | op1                    | cond     | c Branch (Short Displacem |      |        | hort Displa | acem   | ent) |                                             |

| < 3 | < 32-bit instruction > |          |                           |      |        |             |        |      |                                             |

|     | op1                    | R1       | op2                       | R2   | с      |             |        |      | $R_1 = R_2$ op c                            |

|     | op1                    | R1       | op2                       | R2   | с      |             |        |      | Compare and Branch                          |

|     | op1                    | R1       | С                         |      |        |             |        |      | R1 = R1 op c                                |

|     | op1                    | cond     | C                         |      |        |             |        |      | Branch                                      |

|     | op1                    | Rs       | op2                       | 0000 | ор3    | Rd          | op4 00 | 000  | Floating-point 2-operand<br>(Rd=op(Rs))     |

|     | op1                    | Rs1      | op2                       | Rs2  | ор3    | Rd          | op4 00 | 000  | Floating-point 3-operand<br>(Rd=Rs1 op Rs2) |

Fig. 2.2.2 Instruction format of M32R CPU

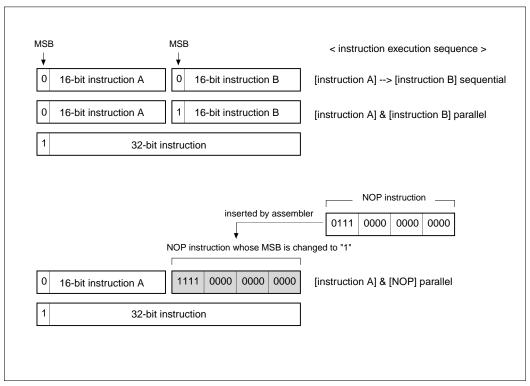

The MSB (Most Significant Bit) of a 32-bit instruction is always "1". The MSB of a 16-bit instruction in the high-order halfword is always "0" (instruction A in Figure 2.2.3), however the processing of the following 16-bit instruction depends on the MSB of the instruction.

In Figure 2.2.3, if the MSB of the instruction B is "0", instructions A and B are executed sequentially; B is executed after A. If the MSB of the instruction B is "1", instructions A and B are executed in parallel.

The current implementation allows only the NOP instruction as instruction B for parallel execution. The MSB of the NOP instruction used for word arraignment adjustment is changed to "1" automatically by a standard Mitsubishi assembler, then the M32R-FPU can execute this instruction without requiring any clock cycles.

Fig. 2.2.3 Processing of 16-bit instructions

This page left blank intentionally.

## **CHAPTER 3**

### INSTRUCTIONS

- 3.1 Conventions for instruction description

- 3.2 Instruction description

### 3.1 Conventions for instruction description

Conventions for instruction description are summarized below.

#### [Mnemonic]

Shows the mnemonic and possible operands (operation target) using assembly language notation.

| symbol(see note) | addressing mode                       | operation target                                                                                                                            |

|------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| R                | register direct                       | general-purpose registers (R0 - R15)                                                                                                        |

| CR               | control register                      | Mcontrol registers (CR0 = PSW, CR1 = CBR, CR2 = SPI,<br>CR3 = SPU, CR6 = BPC, CR7 = FPSR)                                                   |

| @R               | register indirect                     | memory specified by register contents as address                                                                                            |

| @(disp,R)        | register relative indirect            | memory specified by (register contents) + (sign-extended value of 16-bit displacement) as address                                           |

| @R+              | register indirect and register update | Add 4 to register contents. (Register contents specify the memory address, then 4 is added to the contents.)                                |

| @+R              | register indirect and register update | Add 4 to register contents. (4 is added to the register contents, then the register contents specify the memory address.)                   |

| @-R              | register indirect and register update | Subtract 4 to register contents. (4 is subtract to the register contents, hen the register contents specify the memory address.)            |

| #imm             | immediate                             | immediate value (refer to each instruction description)                                                                                     |

| #bitpos          | Bit position                          | Contents of byte data bit position                                                                                                          |

| pcdisp           | PC relative                           | memory specified by (PC contents) + (8, 16, or 24-bit displacement<br>which is sign-extended to 32 bits and 2 bits left-shifted) as address |

Table 3.1.1 Operand list

Note: When expressing Rsrc or Rdest as an operand, a general-purpose register numbers (0 - 15) should be substituted for src or dest. When expressing CRsrc or CRdest, control register numbers (0 - 3, 6, 7) should be substituted for src or dest.

#### [Function]

Indicates the operation performed by one instruction. Notation is in accordance with C language notation.

| meaning                                 |

|-----------------------------------------|

| addition (binomial operator)            |

| subtraction (binomial operator)         |

| multiplication (binomial operator)      |

| division (binomial operator)            |

| remainder operation (binomial operator) |

| increment (monomial operator)           |

| decrement (monomial operator)           |

|                                         |

Table 3.1.2 Operation expression (operator)

3-2 Download from Www.Somanuals.com. All Manuals Search And Download.

3

| operator | meaning                                                                                        |

|----------|------------------------------------------------------------------------------------------------|

| -        | sign invert (monomial operator)                                                                |

| =        | substitute right side into left side (substitute operator)                                     |

| +=       | adds right and left variables and substitute into left side (substitute operator)              |

| -=       | subtract right variable from left variable and substitute into left side (substitute operator) |

| >        | greater than (relational operator)                                                             |

| <        | less than (relational operator)                                                                |

| >=       | greater than or equal to (relational operator)                                                 |

| <=       | less than or equal to (relational operator)                                                    |

| ==       | equal (relational operator)                                                                    |

| !=       | not equal (relational operator)                                                                |

| &&       | AND (logical operator)                                                                         |

|          | OR (logical operator)                                                                          |

| !        | NOT (logical operator)                                                                         |

| ?:       | execute a conditional expression (conditional operator)                                        |

#### Table 3.1.3 Operation expression (operator) (cont.)

#### Table 3.1.4 Operation expression (bit operator)

| operator | meaning                 |  |

|----------|-------------------------|--|

| <<       | bits are left-shifted   |  |

| >>       | bits are right-shifted  |  |

| &        | bit product (AND)       |  |

|          | bit sum (OR)            |  |

| *        | bit exclusive or (EXOR) |  |

| ~        | bit invert              |  |

#### Table 3.1.5 Data type

| expression     | sign | bit length | range                                    |

|----------------|------|------------|------------------------------------------|

| signed char    | yes  | 8          | -128 to +127                             |

| signed short   | yes  | 16         | -32,768 to +32,767                       |

| signed int     | yes  | 32         | -2,147,483,648 to +2,147,483,647         |

| unsigned char  | no   | 8          | 0 to 255                                 |

| unsigned short | no   | 16         | 0 to 655,535                             |

| unsigned int   | no   | 32         | 0 to 4,294,967,295                       |

| signed64bit    | yes  | 64         | signed 64-bit integer (with accumulator) |

#### Table 3.1.6 Data type (floating-point)

| expression | floating-point format          |  |

|------------|--------------------------------|--|

| float      | single precision values format |  |

#### [Description]

Describes the operation performed by the instruction and any condition bit change.

#### [EIT occurrence]

Shows possible EIT events (Exception, Interrupt, Trap) which may occur as the result of the instruction's execution. Only address exception (AE), floating-point exception (FPE) and trap (TRAP) may result from an instruction execution.

#### [Instruction format]

Shows the bit level instruction pattern (16 bits or 32 bits). Source and/or destination register numbers are put in the src and dest fields as appropriate. Any immediate or displacement value is put in the imm or disp field, its maximum size being determined by the width of the field provided for the particular instruction. Refer to **2.2 Instruction format** for detail.

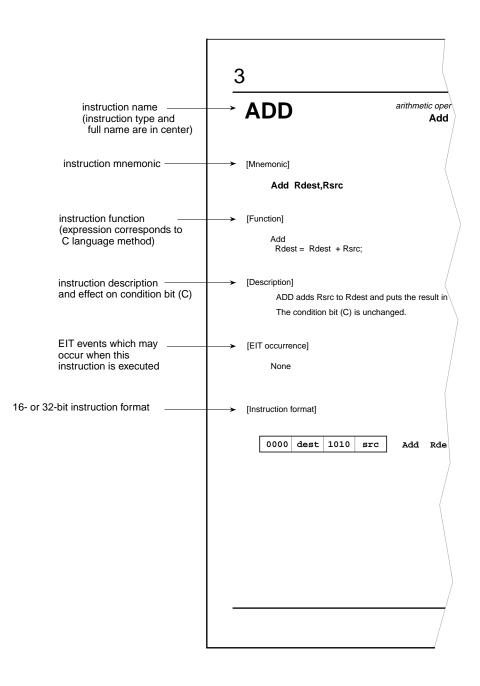

### 3.2 Instruction description

This section lists M32R-FPU instructions in alphabetical order. Each page is laid out as shown below.

ADD

3

arithmetic/logic operation

#### [Mnemonic]

ADD Rdest,Rsrc

#### [Function]

Add Rdest = Rdest + Rsrc;

#### [Description]

ADD adds Rsrc to Rdest and puts the result in Rdest. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0000 dest 1010 src

ADD Rdest,Rsrc

### INSTRUCTIONS 3.2 Instruction description

ADD3

arithmetic operation instruction Add 3-operand

#### [Mnemonic]

ADD3 Rdest,Rsrc,#imm16

#### [Function]

Add

Rdest = Rsrc + ( signed short ) imm16;

#### [Description]

ADD3 adds the 16-bit immediate value to Rsrc and puts the result in Rdest. The immediate value is sign-extended to 32 bits before the operation.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

| 1000 dest | 1010 | src | imm16 |

|-----------|------|-----|-------|

|-----------|------|-----|-------|

ADD3 Rdest,Rsrc,#imm16

arithmetic operation instruction Add immediate

#### [Mnemonic]

ADDI Rdest,#imm8

#### [Function]

Add Rdest = Rdest + ( signed char ) imm8;

#### [Description]

ADDI adds the 8-bit immediate value to Rdest and puts the result in Rdest. The immediate value is sign-extended to 32 bits before the operation. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

| 0100 | dest | imm8 |

|------|------|------|

|------|------|------|

ADDI Rdest,#imm8

3

## ADDV

arithmetic operation instruction Add with overflow checking

#### [Mnemonic]

ADDV Rdest,Rsrc

#### [Function]

Add

Rdest = ( signed ) Rdest + ( signed ) Rsrc; C = overflow ? 1 : 0;

#### [Description]

ADDV adds Rsrc to Rdest and puts the result in Rdest. The condition bit (C) is set when the addition results in overflow; otherwise it is cleared.

#### [EIT occurrence]

None

#### [Encoding]

| 0000 | dest | 1000 | src |

|------|------|------|-----|

|------|------|------|-----|

ADDV Rdest,Rsrc

# ADDV3 arithmetic operation instruction Add 3-operand with overflow checking ADDV3

#### [Mnemonic]

ADDV3 Rdest,Rsrc,#imm16

#### [Function]

Add

```

\label{eq:Rdest} \begin{aligned} &\mathsf{Rdest} = ( \ \text{signed} \ ) \ \mathsf{Rsrc} + ( \ \text{signed} \ ) \ ( \ ( \ \text{signed short} \ ) \ \text{imm16} \ ); \\ &\mathsf{C} = \text{overflow} \ \ ? \ \ 1 : 0; \end{aligned}

```

#### [Description]

ADDV3 adds the 16-bit immediate value to Rsrc and puts the result in Rdest. The immediate value is sign-extended to 32 bits before it is added to Rsrc.

The condition bit (C) is set when the addition results in overflow; otherwise it is cleared.

#### [EIT occurrence]

None

#### [Encoding]

| 1000 | dest | 1000 | src | imm16 |

|------|------|------|-----|-------|

|      |      |      |     |       |

#### ADDV3 Rdest,Rsrc,#imm16

### INSTRUCTIONS 3.2 Instruction description

**ADDX**

arithmetic operation instruction Add with carry

[Mnemonic]

ADDX Rdest,Rsrc

#### [Function]

#### Add

Rdest = ( unsigned ) Rdest + ( unsigned ) Rsrc + C; C = carry\_out ? 1:0;

#### [Description]

ADDX adds Rsrc and C to Rdest, and puts the result in Rdest.

The condition bit (C) is set when the addition result cannot be represented by a 32-bit unsigned integer; otherwise it is cleared.

#### [EIT occurrence]

None

#### [Encoding]

| 0000 | dest | 1001 | src |

|------|------|------|-----|

|------|------|------|-----|

ADDX Rdest,Rsrc

AND

3

logic operation instruction **AND**

#### [Mnemonic]

AND Rdest,Rsrc

#### [Function]

Logical AND Rdest = Rdest & Rsrc;

#### [Description]

AND computes the logical AND of the corresponding bits of Rdest and Rsrc and puts the result in Rdest.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

0000 dest 1100 src

AND Rdest,Rsrc

AND3

logic operation instruction

AND 3-operand

#### [Mnemonic]

AND3 Rdest,Rsrc,#imm16

#### [Function]

Logical AND Rdest = Rsrc & ( unsigned short ) imm16;

#### [Description]

AND3 computes the logical AND of the corresponding bits of Rsrc and the 16-bit immediate value, which is zero-extended to 32 bits, and puts the result in Rdest. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

| 1000 dest | 1100 | src | imm16 |

|-----------|------|-----|-------|

|-----------|------|-----|-------|

AND3 Rdest,Rsrc,#imm16

## BC

branch instruction

### BC

### Bit clear M32R-FPU Extended Instruction

#### [Mnemonic]

(1) BC pcdisp8

(2) BC pcdisp24

#### [Function]

#### Branch

```

(1) if (C==1) PC = (PC & 0xffffffc) + (((signed char) pcdisp8) << 2);</li>

(2) if (C==1) PC = (PC & 0xfffffffc) + (sign_extend (pcdisp24) << 2); where</li>

#define sign_extend(x) (((signed)((x)<<8)) >>8)

```

#### [Description]

BC causes a branch to the specified label when the condition bit (C) is 1.

There are two instruction formats; which allows software, such as an assembler, to decide on the better format.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

| 0111 | 1100 | pcdisp8 | BC pcdisp8 |    |          |

|------|------|---------|------------|----|----------|

| 1111 | 1100 |         | pcdisp24   | вс | pcdisp24 |

**BCLR**

bit operation

### Bit clear

### BCLR

### [M32R-FPU Extended Instruction]

[Mnemonic]

BCLR #bitpos,@(disp16,Rsrc)

#### [Function]

Bit operation for memory contents Set 0 to specified bit. \* ( signed char\* ) ( Rsrc + ( signed short ) disp16 ) & = ~ ( 1<< ( 7-bitpos ) ) ;

#### [Description]

BCLR reads the byte data in the memory at the address specified by the Rsrc combined with the 16-bit displacement, and then stores the value of the bit that was specified by bitpos to be set to "0". The displacement is sign-extended before the address calculation. bitpos becomes 0 to 7; MSB becomes 0 and LSB becomes 7. The memory is accessed in bytes. The LOCK bit is on while the BCLR instruction is executed, and is cleared when the execution is completed. The LOCK bit is internal to the CPU and cannot be directly read or written to by the user.

Condition bit C remains unchanged.

The LOCK bit is internal to the CPU and is the control bit for receiving all bus right requests from circuits other than the CPU.

Refer to the Users Manual for non-CPU bus right requests, as the handling differs according to the type of MCU.

#### [EIT occurrence]

None

#### [Encoding]

| 1010 | 0 | bitpos | 0111 | src | disp16 |

|------|---|--------|------|-----|--------|

|------|---|--------|------|-----|--------|

BCLR #bitpos,@(disp16,Rsrc)

## BEQ

### branch instruction Branch on equal to

#### [Mnemonic]

BEQ Rsrc1,Rsrc2,pcdisp16

#### [Function]

Branch

```

if ( Rsrc1 == Rsrc2 ) PC = ( PC & 0xffffffc ) + ( ( ( signed short ) pcdisp16 ) << 2);

```

#### [Description]

BEQ causes a branch to the specified label when Rsrc1 is equal to Rsrc2. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

| 1011 | src1 | 0000 | src2 | pcdisp16 |

|------|------|------|------|----------|

|------|------|------|------|----------|

BEQ Rsrc1,Rsrc2,pcdisp16

**BEQZ**

*branch instruction* Branch on equal to zero

#### [Mnemonic]

BEQZ Rsrc,pcdisp16

#### [Function]

Branch

if ( Rsrc == 0 ) PC = ( PC & 0xffffffc ) + ( ( ( signed short ) pcdisp16 ) << 2);

#### [Description]

BEQZ causes a branch to the specified label when Rsrc is equal to zero. The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

| 1011 | 0000 | 1000 | src | pcdisp16 |

|------|------|------|-----|----------|

|------|------|------|-----|----------|

BEQZ Rsrc,pcdisp16

## BGEZ

branch instruction

### Branch on greater than or equal to zero

#### [Mnemonic]

BGEZ Rsrc,pcdisp16

#### [Function]

Branch

```

if ( (signed) Rsrc >= 0 ) PC = (PC \& 0xffffffc) + ( ( ( signed short ) pcdisp16 ) << 2);

```

#### [Description]

BGEZ causes a branch to the specified label when Rsrc treated as a signed 32-bit value is greater than or equal to zero.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

| 1011 0000 1011 src | pcdisp16 |

|--------------------|----------|

|--------------------|----------|

BGEZ Rsrc,pcdisp16

**BGTZ**

branch instruction Branch on greater than zero

#### [Mnemonic]

BGTZ Rsrc,pcdisp16

#### [Function]

#### Branch

if ((signed) Rsrc > 0) PC = (PC & 0xffffffc) + ( ( (signed short) pcdisp16 ) << 2);

#### [Description]

BGTZ causes a branch to the specified label when Rsrc treated as a signed 32-bit value is greater than zero.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

| 1011 | 0000 | 1101 | src | pcdisp16 |

|------|------|------|-----|----------|

|------|------|------|-----|----------|

BGTZ Rsrc,pcdisp16

## BL

branch instruction Branch and link

#### [Mnemonic]

(1) BL pcdisp8

(2) BL pcdisp24

#### [Function]

Subroutine call (PC relative)

(1) R14 = ( PC & 0xffffffc ) + 4; PC = ( PC & 0xffffffc ) + ( ( ( signed char ) pcdisp8 ) << 2 );</li>

(2) R14 = ( PC & 0xffffffc ) + 4;

PC = ( PC & 0xffffffc ) + ( sign\_extend ( pcdisp24 ) << 2 );

where

#define sign\_extend(x) ( ( ( signed ) ( (x) << 8 ) ) >>8 )

#### [Description]

BL causes an unconditional branch to the address specified by the label and puts the return address in R14.

There are two instruction formats; this allows software, such as an assembler, to decide on the better format.

The condition bit (C) is unchanged.

#### [EIT occurrence]

None

#### [Encoding]

| 0111 | 1110 | pcdisp8 | BL       | pcdisp8 |    |          |

|------|------|---------|----------|---------|----|----------|

| 1111 | 1110 |         | pcdisp24 |         | BL | pcdisp24 |

## BLEZ

*branch instruction* Branch on less than or equal to zero

#### [Mnemonic]

BLEZ Rsrc,pcdisp16

#### [Function]

#### Branch

if ((signed) Rsrc <= 0) PC = (PC & 0xffffffc) + (((signed short) pcdisp16) << 2);