## **Product Manual**

3.5" Hard Disk Drives

# **SPINPOINT V40**

**JULY 7, 2001 (Rev 1.0)**

## TABLE OF CONTENTS

| 1.1   USER DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CHAPTER 1 | SCOPE                                 | 1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|----|

| 1.2   MANUAL ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.1 USER  | DEFINITION                            |    |

| 1.3       TERMINOLOGY AND CONVENTIONS       2         1.4       REPERENCE.       3         CHAPTER 2       DESCRIPTION       4         2.1       INTRODUCTION       4         2.2       KEY FEATURES.       4         2.3       STANDARDS AND REGULATIONS.       5         2.4       HARDWARE REQUIREMENTS       5         CHAPTER 3       SPECIFICATION SUMMARY       6         3.1       SPECIFICATION SUMMARY       6         3.2       PHYSICAL SPECIFICATIONS       7         3.3       LOIGOLAL CONFIGURATIONS       7         3.4       PERFORMANCE SPECIFICATIONS       8         3.5       POWER REQUIREMENTS       9         3.6       ENVIRONMENTAL SPECIFICATIONS       10         3.7       RELIABILITY SPECIFICATIONS       11         CHAPTER 4       INSTALLATION       12         4.1       SPACE REQUIREMENTS       12         4.2       UNPACKING INSTRUCTIONS       13         4.3       MOUNTING       13         4.3       4.3.1       Orientation       13         4.3.2       Clearance       15         4.4.3       Ventilation       16         4.4.                                                                                                                                                         |           |                                       |    |

| 1.4   REFERENCE   33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                       |    |

| CHAPTER 2   DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                       |    |

| 2.1       INTRODUCTION       4         2.2       KEY FEATURES       4         2.3       STANDARDS AND REGULATIONS       5         2.4       HARDWARE REQUIREMENTS       5         CHAPTER 3       SPECIFICATIONS       6         3.1       SPECIFICATION SUMMARY       6         3.2       PHYSICAL SPECIFICATIONS       7         3.3       LOGICAL CONFIGURATIONS       7         3.4       PERFORMANCE SPECIFICATIONS       8         3.5       POWER REQUIREMENTS       9         3.6       ENVIRONMENTAL SPECIFICATIONS       10         3.7       RELABILITY SPECIFICATIONS       11         CHAPTER 4       INSTALLATION       12         4.1       SPACE REQUIREMENTS       12         4.2       UNPACKING INSTRUCTIONS       13         4.3       MOUNTING       13         4.3.1       Orientation       13         4.3.2       Ventiation       16         4.4       CABLE CONNECTORS       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6 <td></td> <td></td> <td></td>                                                                                                                     |           |                                       |    |

| 2.2       KEY FEATURES.       4         2.3       STANDARDS AND REGULATIONS.       5         2.4       HARDWARE REQUIREMENTS       5         CHAPTER 3       SPECIFICATIONS       6         3.1       SPECIFICATION SUMMARY       6         3.2       PHYSICAL SPECIFICATIONS.       7         3.3       LOIGICAL CONFIGURATIONS.       7         3.4       PERFORMANCE SPECIFICATIONS.       8         3.5       POWER REQUIREMENTS.       9         3.6       ENVIRONMENTAL SPECIFICATIONS.       10         3.7       RELIABILITY SPECIFICATIONS.       11         CHAPTER 4 INSTALLATION.       12         4.1       SPACE REQUIREMENTS.       12         4.2       UNPACKING INSTRUCTIONS.       13         4.3       MOUNTING.       13         4.3.1       Orientation       13         4.3.2       Ventilation       13         4.3.3       Ventilation       16         4.4       CABLE CONNECTORS.       16         4.4.1       DC POWER Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS.       18                                                                                                                                                  | CHAPTER 2 | DESCRIPTION                           | 4  |

| 2.2       KEY FEATURES.       4         2.3       STANDARDS AND REGULATIONS.       5         2.4       HARDWARE REQUIREMENTS       5         CHAPTER 3       SPECIFICATIONS       6         3.1       SPECIFICATION SUMMARY       6         3.2       PHYSICAL SPECIFICATIONS.       7         3.3       LOIGICAL CONFIGURATIONS.       7         3.4       PERFORMANCE SPECIFICATIONS.       8         3.5       POWER REQUIREMENTS.       9         3.6       ENVIRONMENTAL SPECIFICATIONS.       10         3.7       RELIABILITY SPECIFICATIONS.       11         CHAPTER 4 INSTALLATION.       12         4.1       SPACE REQUIREMENTS.       12         4.2       UNPACKING INSTRUCTIONS.       13         4.3       MOUNTING.       13         4.3.1       Orientation       13         4.3.2       Ventilation       13         4.3.3       Ventilation       16         4.4       CABLE CONNECTORS.       16         4.4.1       DC POWER Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS.       18                                                                                                                                                  | 2.1 INTRO | DUCTION                               | 4  |

| 2.4       HARDWARE REQUIREMENTS       5         CHAPTER 3       SPECIFICATIONS       6         3.1       SPECIFICATION SUMMARY       6         3.2       PHYSICAL SPECIFICATIONS       7         3.3       LOGICAL CONFIGURATIONS       7         3.4       PERFORMANCE SPECIFICATIONS       8         3.5       POWER REQUIREMENTS       9         3.6       ENVIRONMENTAL SPECIFICATIONS       10         3.7       RELIABILITY SPECIFICATIONS       11         CHAPTER 4       INSTALLATION       12         4.1       SPACE REQUIREMENTS       12         4.2       UNPACKING INSTRUCTIONS       13         4.3       MOUNTING       13         4.3.1       Orientation       13         4.3.2       Clearance       15         4.3.3       Ventilation       16         4.4       CABLE CONNECTORS       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DENYE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21                                                                                                                                                      | 2.2 KEY F | EATURES                               | 4  |

| 2.4       HARDWARE REQUIREMENTS       5         CHAPTER 3       SPECIFICATIONS       6         3.1       SPECIFICATION SUMMARY       6         3.2       PHYSICAL SPECIFICATIONS       7         3.3       LOGICAL CONFIGURATIONS       7         3.4       PERFORMANCE SPECIFICATIONS       8         3.5       POWER REQUIREMENTS       9         3.6       ENVIRONMENTAL SPECIFICATIONS       10         3.7       RELIABILITY SPECIFICATIONS       11         CHAPTER 4       INSTALLATION       12         4.1       SPACE REQUIREMENTS       12         4.2       UNPACKING INSTRUCTIONS       13         4.3       MOUNTING       13         4.3.1       Orientation       13         4.3.2       Clearance       15         4.3.3       Ventilation       16         4.4       CABLE CONNECTORS       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DENYE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21                                                                                                                                                      | 2.3 Stani | DARDS AND REGULATIONS                 | 5  |

| 3.1       SPECIFICATION SUMMARY.       6         3.2       PHYSICAL SPECIFICATIONS.       7         3.3       LOGICAL CONFIGURATIONS.       7         3.4       PERFORMANCE SPECIFICATIONS.       8         3.5       POWER REQUIREMENTS.       9         3.6       ENVIRONMENTAL SPECIFICATIONS.       10         3.7       RELIABILITY SPECIFICATIONS.       11         CHAPTER 4       INSTALLATION.       12         4.1       SPACE REQUIREMENTS.       12         4.2       UNPACKING INSTRUCTIONS.       13         4.3       MOUNTING.       13         4.3.1       Orientation       13         4.3.2       Clearance.       15         4.4.3       Ventilation       16         4.4.4       CABLE CONNECTORS.       16         4.4.1       DC Power Connector.       16         4.4.2       AT-Bus Interface Connector.       16         4.5       JUMPER BLOCK CONFIGURATIONS.       18         4.6       DRIVE INSTALLATION.       20         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip.       22         CHAPTER 5       DISK DRIVE OPERATION       23         5                                                                                                                         | 2.4 Hard  | WARE REQUIREMENTS                     | 5  |

| 3.2       PHYSICAL SPECIFICATIONS       7         3.3       LOGICAL CONFIGURATIONS       7         3.4       PERFORMANCE SPECIFICATIONS       8         3.5       POWER REQUIREMENTS       9         3.6       ENVIRONMENTAL SPECIFICATIONS       10         3.7       RELIABILITY SPECIFICATIONS       11         CHAPTER 4       INSTALLATION       12         4.1       SPACE REQUIREMENTS       12         4.2       UNPACKING INSTRUCTIONS       13         4.3       MOUNTING       13         4.3.1       Orientation       13         4.3.2       Clearance       15         4.4.3       Ventilation       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5       DISK DRIVE OPERATION       23         5.1.1       Base                                                                                                              | CHAPTER 3 | SPECIFICATIONS                        | 6  |

| 3.2       PHYSICAL SPECIFICATIONS       7         3.3       LOGICAL CONFIGURATIONS       7         3.4       PERFORMANCE SPECIFICATIONS       8         3.5       POWER REQUIREMENTS       9         3.6       ENVIRONMENTAL SPECIFICATIONS       10         3.7       RELIABILITY SPECIFICATIONS       11         CHAPTER 4       INSTALLATION       12         4.1       SPACE REQUIREMENTS       12         4.2       UNPACKING INSTRUCTIONS       13         4.3       MOUNTING       13         4.3.1       Orientation       13         4.3.2       Clearance       15         4.4.3       Ventilation       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5       DISK DRIVE OPERATION       23         5.1.1       Base                                                                                                              | 3.1 Speci | FICATION SUMMARY                      | 6  |

| 3.3       LOGICAL CONFIGURATIONS       7         3.4       PERFORMANCE SPECIFICATIONS       8         3.5       POWER REQUIREMENTS       9         3.6       ENVIRONMENTAL SPECIFICATIONS       10         3.7       RELIABILITY SPECIFICATIONS       11         CHAPTER 4 INSTALLATION       12         4.1       SPACE REQUIREMENTS       12         4.2       UNPACKING INSTRUCTIONS       13         4.3       MOUNTING       13         4.3.1       Orientation       13         4.3.2       Clearance       15         4.3.3       Ventilation       16         4.4       CABLE CONNECTORS       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5 DISK DRIVE OPERATION       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assem                                                                                                                   |           |                                       |    |

| 3.4       PERFORMANCE SPECIFICATIONS       8         3.5       POWER REQUIREMENTS       9         3.6       ENVIRONMENTAL SPECIFICATIONS       10         3.7       RELIABILITY SPECIFICATIONS       11         CHAPTER 4 INSTALLATION       12         4.1       SPACE REQUIREMENTS       12         4.2       UNPACKING INSTRUCTIONS       13         4.3       MOUNTING       13         4.3.1       Orientation       13         4.3.2       Clearance       15         4.3.3       Ventilation       16         4.4       CABLE CONNECTORS       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5 DISK DRIVE OPERATION       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.5       Voice Coil Motor                                                                                                                   |           |                                       |    |

| 3.5       POWER REQUIREMENTS       .9         3.6       ENVIRONMENTAL SPECIFICATIONS       .10         3.7       RELIABILITY SPECIFICATIONS       .11         CHAPTER 4       INSTALLATION       .12         4.1       SPACE REQUIREMENTS       .12         4.2       UNPACKING INSTRUCTIONS       .13         4.3       MOUNTING       .13         4.3.1       Orientation       .13         4.3.2       Clearance       .15         4.4.3       Ventilation       .16         4.4       CABLE CONNECTORS       .16         4.4.1       DC Power Connector       .16         4.4.2       AT-Bus Interface Connector       .16         4.5       JUMPER BLOCK CONFIGURATIONS       .18         4.6       DRIVE INSTALLATION       .20         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       .22         CHAPTER 5       DISK DRIVE OPERATION       .23         5.1.1       Base Casting Assembly       .23         5.1.2       DC Spindle Motor Assembly       .23         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       .25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       .                                                                          |           |                                       |    |

| 3.6       ENVIRONMENTAL SPECIFICATIONS       10         3.7       RELABILITY SPECIFICATIONS       11         CHAPTER 4       INSTALLATION       12         4.1       SPACE REQUIREMENTS       12         4.2       UNPACKING INSTRUCTIONS       13         4.3       MOUNTING       13         4.3.1       Orientation       13         4.3.2       Clearance       15         4.3.3       Ventilation       16         4.4       CABLE CONNECTORS       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5       DISK DRIVE OPERATION       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil                                                                                                              |           |                                       |    |

| 3.7       RELIABILITY SPECIFICATIONS       11         CHAPTER 4       INSTALLATION       12         4.1       SPACE REQUIREMENTS       12         4.2       UNPACKING INSTRUCTIONS       13         4.3       MOUNTING       13         4.3.1       Orientation       13         4.3.2       Clearance       15         4.3.3       Ventilation       16         4.4       CABLE CONNECTORS       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       PSYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5       DISK DRIVE OPERATION       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.2       DC Spindle Motor Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.2.                                                                                                    |           |                                       |    |

| CHAPTER 4         INSTALLATION         12           4.1         SPACE REQUIREMENTS         12           4.2         UNPACKING INSTRUCTIONS         13           4.3         MOUNTING         13           4.3.1         Orientation         13           4.3.2         Clearance         15           4.3.3         Ventilation         16           4.4         CABLE CONNECTORS         16           4.4.1         DC Power Connector         16           4.4.2         AT-Bus Interface Connector         16           4.5         JUMPER BLOCK CONFIGURATIONS         18           4.6         DRIVE INSTALLATION         20           4.7         SYSTEM STARTUP PROCEDURE         21           4.7.1         Drive Installation to Access the Full Capacity Using 32GB Clip         22           CHAPTER 5 DISK DRIVE OPERATION           5.1         Bease Casting Assembly         23           5.1.1         Base Casting Assembly         23           5.1.2         DC Spindle Motor Assembly         23           5.1.3         Disk Stack Assembly         25           5.1.4         Head Stack Assembly         25           5.1.5         Voice Coil Motor and Actu                                                   |           |                                       |    |

| 4.1       SPACE REQUIREMENTS       12         4.2       UNPACKING INSTRUCTIONS       13         4.3       MOUNTING       13         4.3.1       Orientation       13         4.3.2       Clearance       15         4.3.3       Ventilation       16         4.4       CABLE CONNECTORS       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5 DISK DRIVE OPERATION       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       23         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.2.1       Digital Signal Process and Interface Controller <t< td=""><td></td><td></td><td></td></t<>                                       |           |                                       |    |

| 4.2       UNPACKING INSTRUCTIONS       13         4.3       MOUNTING       13         4.3.1       Orientation       13         4.3.2       Clearance       15         4.3.3       Ventilation       16         4.4       CABLE CONNECTORS       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5       DISK DRIVE OPERATION       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.1.2       Drive Electronoics       26         5.2.2       AT Disk Controller       26         5.2.2                                                                                                         | CHAPTER 4 | INSTALLATION                          | 12 |

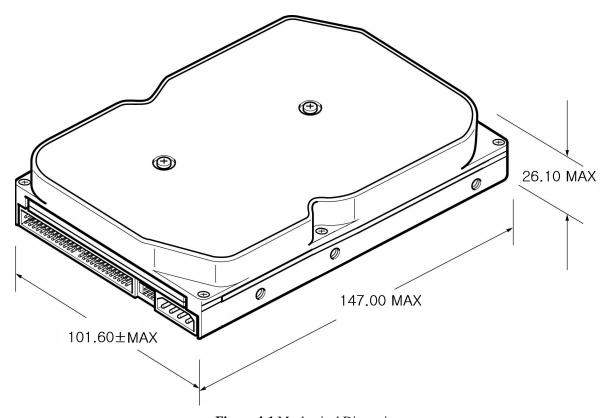

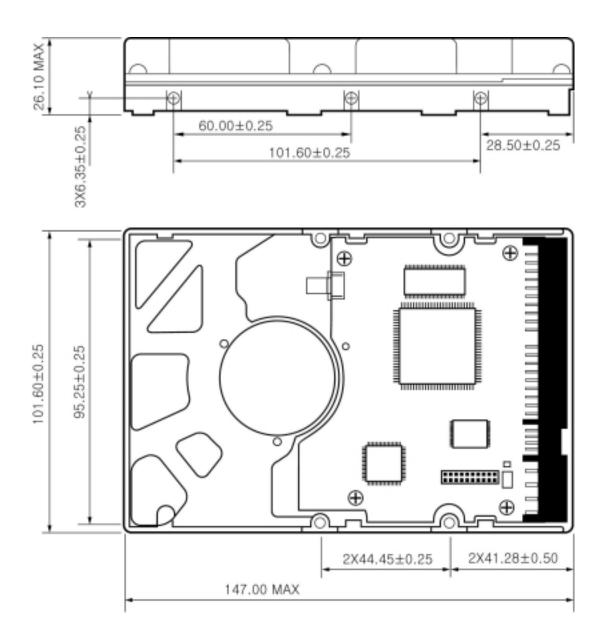

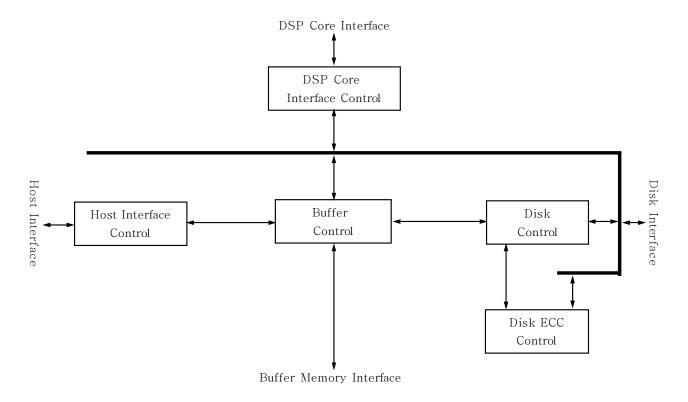

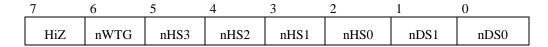

| 4.3 MOUNTING       13         4.3.1 Orientation       13         4.3.2 Clearance       15         4.3.3 Ventilation       16         4.4 CABLE CONNECTORS       16         4.4.1 DC Power Connector       16         4.4.2 AT-Bus Interface Connector       16         4.5 JUMPER BLOCK CONFIGURATIONS       18         4.6 DRIVE INSTALLATION       20         4.7 SYSTEM STARTUP PROCEDURE       21         4.7.1 Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5 DISK DRIVE OPERATION       23         5.1.1 Base Casting Assembly       23         5.1.2 DC Spindle Motor Assembly       23         5.1.3 Disk Stack Assembly       23         5.1.5 Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6 Air Filtration System       25         5.2 DRIVE ELECTRONICS       26         5.2.1 Digital Signal Process and Interface Controller       26         5.2.2 AT Disk Controller       26         5.2.2.1 The Host Interface Control Block       29         5.2.2.3 The Disk Control Block       29         5.2.2.4 The Disk ECC Control Block       31         5.2.2.5 Frequency Synthesizer       31         5.2.2.6 Power Management                          | 4.1 SPACE | REQUIREMENTS                          | 12 |

| 4.3.1       Orientation       13         4.3.2       Clearance       15         4.3.3       Ventilation       16         4.4       CABLE CONNECTORS       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5 DISK DRIVE OPERATION         5.1       HEAD/ DISK ASSEMBLY (HDA)       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.2       DRIVE ELECTRONICS       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2.1       The Buffer Control Block       29                                                                                     | 4.2 Unpa  | CKING INSTRUCTIONS                    | 13 |

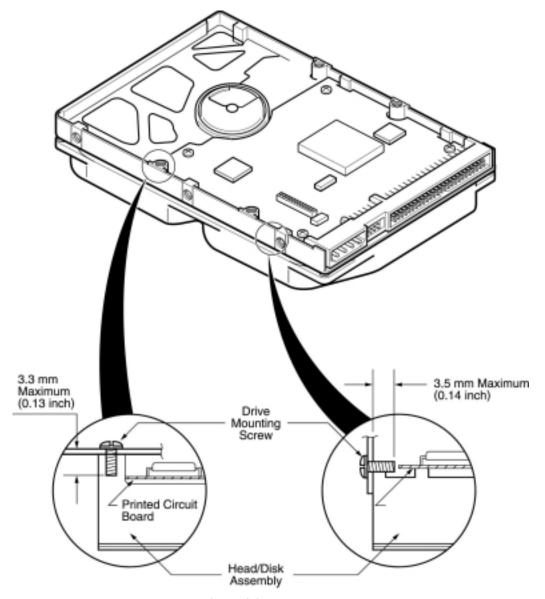

| 4.3.2       Clearance       15         4.3.3       Ventilation       16         4.4       CABLE CONNECTORS.       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5 DISK DRIVE OPERATION       23         5.1       HEAD / DISK ASSEMBLY (HDA)       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.2       DRIVE ELECTRONICS       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Disk Control                                                                    | 4.3 Moun  | VTING                                 | 13 |

| 4.3.3       Ventilation       16         4.4       CABLE CONNECTORS       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5 DISK DRIVE OPERATION       23         5.1       HEAD / DISK ASSEMBLY (HDA)       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.2       DRIVE ELECTRONICS       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       29         5.2.2.4                                                                           |           |                                       |    |

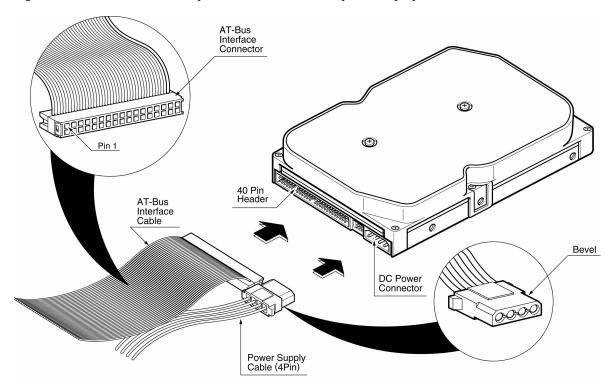

| 4.4       CABLE CONNECTORS       16         4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5 DISK DRIVE OPERATION       23         5.1       HEAD / DISK ASSEMBLY (HDA)       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk COctrol Block       29         5.2.2.4       The Disk ECC Control Block       31                                        |           |                                       |    |

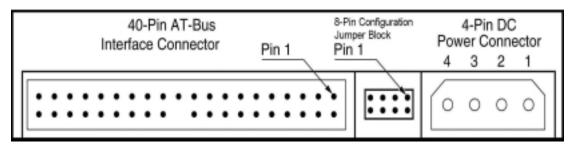

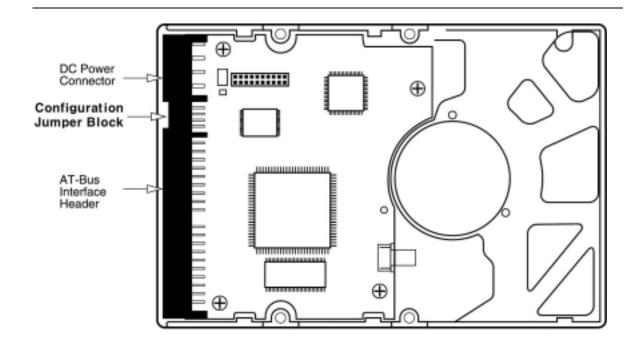

| 4.4.1       DC Power Connector       16         4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5 DISK DRIVE OPERATION       23         5.1       HEAD / DISK ASSEMBLY (HDA)       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.2       Drive Electronics       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31 <td< td=""><td>4.3.3 V</td><td>Ventilation</td><td> 16</td></td<> | 4.3.3 V   | Ventilation                           | 16 |

| 4.4.2       AT-Bus Interface Connector       16         4.5       JUMPER BLOCK CONFIGURATIONS       18         4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5 DISK DRIVE OPERATION       23         5.1       HEAD / DISK ASSEMBLY (HDA)       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.2       DRIVE ELECTRONICS       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       28         5.2.2.3       The Disk ECC Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31 <t< td=""><td></td><td></td><td></td></t<>            |           |                                       |    |

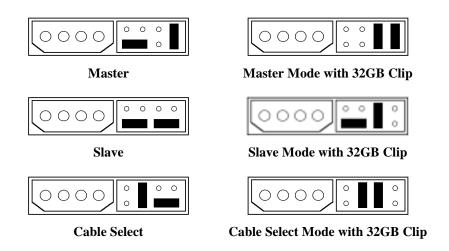

| 4.5       JUMPER BLOCK CONFIGURATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                                       |    |

| 4.6       DRIVE INSTALLATION       20         4.7       SYSTEM STARTUP PROCEDURE       21         4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5 DISK DRIVE OPERATION       23         5.1       HEAD / DISK ASSEMBLY (HDA)       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.2       DRIVE ELECTRONICS       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2       AT Disk Controller       26         5.2.2.1       The Host Interface Control Block       29         5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                    |           |                                       |    |

| 4.7       SYSTEM STARTUP PROCEDURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                                       |    |

| 4.7.1       Drive Installation to Access the Full Capacity Using 32GB Clip       22         CHAPTER 5 DISK DRIVE OPERATION       23         5.1       HEAD / DISK ASSEMBLY (HDA)       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.2       DRIVE ELECTRONICS       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                                                                                                            |           |                                       |    |

| CHAPTER 5 DISK DRIVE OPERATION         23           5.1 HEAD / DISK ASSEMBLY (HDA)         23           5.1.1 Base Casting Assembly         23           5.1.2 DC Spindle Motor Assembly         23           5.1.3 Disk Stack Assembly         25           5.1.4 Head Stack Assembly         25           5.1.5 Voice Coil Motor and Actuator Latch Assemblies         25           5.1.6 Air Filtration System         25           5.2 DRIVE ELECTRONICS         26           5.2.1 Digital Signal Process and Interface Controller         26           5.2.2 AT Disk Controller         26           5.2.2.1 The Host Interface Control Block         28           5.2.2.2 The Buffer Control Block         29           5.2.2.3 The Disk Control Block         29           5.2.2.4 The Disk ECC Control Block         31           5.2.2.5 Frequency Synthesizer         31           5.2.2.6 Power Management         31                                                                                                                                                                                                                                                                                                      |           |                                       |    |

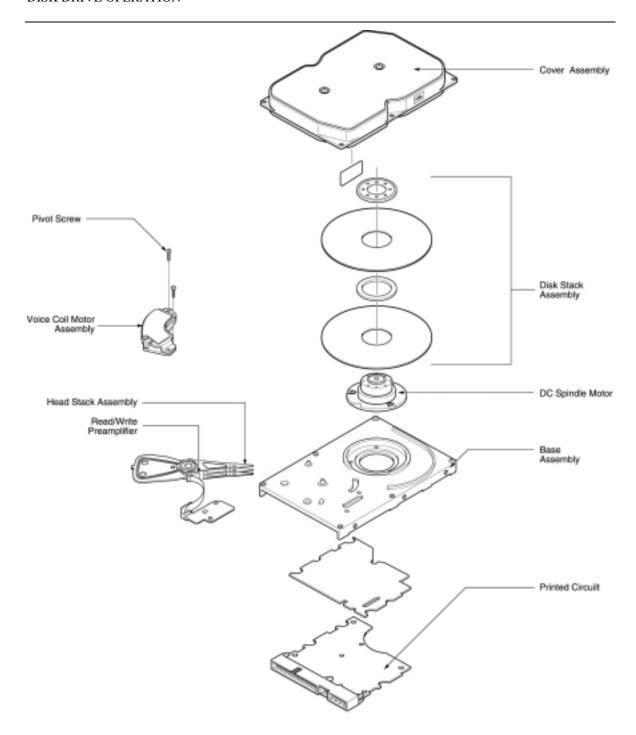

| 5.1       HEAD / DISK ASSEMBLY (HDA)       23         5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.2       DRIVE ELECTRONICS       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2       AT Disk Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                                                                                                                                                                                                        | 4./.1 1   |                                       |    |

| 5.1.1       Base Casting Assembly       23         5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.2       DRIVE ELECTRONICS       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2       AT Disk Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                                                                                                                                                                                                                                                              |           |                                       |    |

| 5.1.2       DC Spindle Motor Assembly       23         5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.2       DRIVE ELECTRONICS       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2       AT Disk Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                                       |    |

| 5.1.3       Disk Stack Assembly       25         5.1.4       Head Stack Assembly       25         5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.2       DRIVE ELECTRONICS       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2       AT Disk Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                       |    |

| 5.1.4 Head Stack Assembly       25         5.1.5 Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6 Air Filtration System       25         5.2 DRIVE ELECTRONICS       26         5.2.1 Digital Signal Process and Interface Controller       26         5.2.2 AT Disk Controller       26         5.2.2.1 The Host Interface Control Block       28         5.2.2.2 The Buffer Control Block       29         5.2.2.3 The Disk Control Block       29         5.2.2.4 The Disk ECC Control Block       31         5.2.2.5 Frequency Synthesizer       31         5.2.2.6 Power Management       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           | •                                     |    |

| 5.1.5       Voice Coil Motor and Actuator Latch Assemblies       25         5.1.6       Air Filtration System       25         5.2       DRIVE ELECTRONICS       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2       AT Disk Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                                       |    |

| 5.1.6       Air Filtration System       25         5.2       DRIVE ELECTRONICS       26         5.2.1       Digital Signal Process and Interface Controller       26         5.2.2       AT Disk Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                                       |    |

| 5.2 DRIVE ELECTRONICS       26         5.2.1 Digital Signal Process and Interface Controller       26         5.2.2 AT Disk Controller       26         5.2.2.1 The Host Interface Control Block       28         5.2.2.2 The Buffer Control Block       29         5.2.2.3 The Disk Control Block       29         5.2.2.4 The Disk ECC Control Block       31         5.2.2.5 Frequency Synthesizer       31         5.2.2.6 Power Management       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                                       |    |

| 5.2.1       Digital Signal Process and Interface Controller       26         5.2.2       AT Disk Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | · · · · · · · · · · · · · · · · · · · |    |

| 5.2.2       AT Disk Controller       26         5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                       |    |

| 5.2.2.1       The Host Interface Control Block       28         5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                       |    |

| 5.2.2.2       The Buffer Control Block       29         5.2.2.3       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                       |    |

| 5.2.2.3       The Disk Control Block       29         5.2.2.4       The Disk ECC Control Block       31         5.2.2.5       Frequency Synthesizer       31         5.2.2.6       Power Management       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                                       |    |

| 5.2.2.4       The Disk ECC Control Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                                       |    |

| 5.2.2.6 Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                                       |    |

| $\mathcal{C}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.2.2.5   | Frequency Synthesizer                 | 31 |

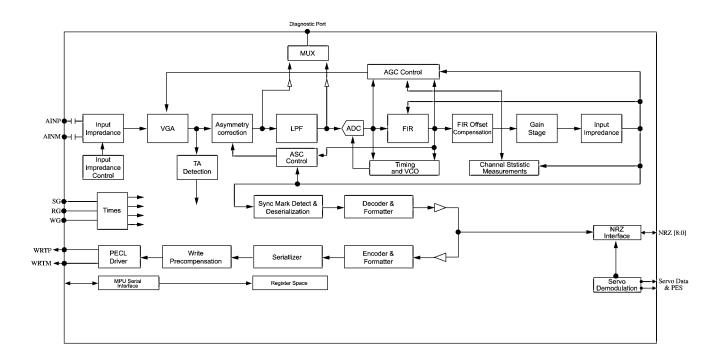

| 5.2.3 Read/Write IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                                       |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.2.3 F   | Read/Write IC                         | 31 |

| 5.2.3.           | 1 Time Base Generator                   | 32 |

|------------------|-----------------------------------------|----|

| 5.2.3.           |                                         |    |

| 5.2.3.3          |                                         |    |

| 5.2.3.4          |                                         |    |

| 5.2.3.           |                                         |    |

|                  | RVO SYSTEM                              |    |

|                  | AD AND WRITE OPERATIONS                 |    |

| 5.4.1            | The Read Channel                        |    |

| 5.4.1            |                                         |    |

|                  | The Write Channel                       |    |

|                  | RMWARE FEATURES                         |    |

| 5.5.1            | Read Caching                            |    |

| 5.5.2            | Write Caching                           |    |

| 5.5.3            | Defect Management                       |    |

| 5.5.4            | Automatic Defect Allocation             | 37 |

| 5.5.5            | Multi-burst ECC Correction              | 37 |

| 5.5.6            | SMART                                   |    |

| 5.5.7            | AAM                                     |    |

|                  |                                         |    |

| CHAPTER          | 6 AT INTERFACE AND ATA COMMANDS         | 39 |

| 6.1 INT          | TRODUCTION                              | 20 |

|                  |                                         |    |

|                  | YSICAL INTERFACE                        |    |

| 6.2.1            | Signal Conventions                      |    |

| 6.2.2            | Signal Summary                          |    |

| 6.2.3            | Signal Descriptions                     |    |

| 6.2.3.           | <b>I J</b>                              |    |

| 6.2.3.2          | (                                       |    |

| 6.2.3.           | - ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' |    |

| 6.2.3.4          | . , , , , , , , , , , , , , , , , , , , |    |

| 6.2.3.           |                                         |    |

| 6.2.3.0          | ,                                       |    |

| 6.2.3.7          |                                         |    |

| 6.2.3.8          | ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` `   |    |

| 6.2.3.9          |                                         |    |

| 6.2.3.           |                                         |    |

| 6.2.3.           | (                                       |    |

| 6.2.3.           | - (· · · · · · · · · · · · · · · · ·    |    |

| 6.2.3.<br>6.2.3. | ` & /                                   |    |

|                  | GICAL INTERFACE                         |    |

|                  |                                         |    |

| 6.3.1            | General                                 |    |

|                  | 1 Bit Conventions                       |    |

| 6.3.1.2          |                                         |    |

| 6.3.2            | I/O Register - Address                  |    |

| 6.3.3            | Control Block Register Descriptions     |    |

| 6.3.3.           |                                         |    |

| 6.3.3.2          | β ,                                     |    |

| 6.3.3.3          | $\mathcal{E}$                           |    |

| 6.3.4            | Command Block Register Descriptions     |    |

| 6.3.4.           | $\varepsilon$ ,                         |    |

| 6.3.4.2          |                                         |    |

| 6.3.4.3          | 8 ( )                                   |    |

| 6.3.4.4          | 6 \ '                                   |    |

| 6.3.4.5          |                                         |    |

| 6.3.4.0          | , , ,                                   |    |

| 6.3.4.           | , , ,                                   |    |

| 6.3.4.8          | 2 ( )                                   |    |

| 6.3.4.9          | E , ,                                   |    |

| 6.3.4.           |                                         |    |

|                  | COMMAND REGISTER DESCRIPTIONS           |    |

| 6.4.1            | Check Power Mode (98h, E5h)             |    |

| 6.4.2            | Download Micro Code (92h)               |    |

| 6.4.3            | Execute Device Diagnostics (90h)        | 56 |

|                  |                                         |    |

| 6.4.4                | Flush Cache (E7h)                                         | 57 |

|----------------------|-----------------------------------------------------------|----|

| 6.4.5                | Format Track (50h)                                        |    |

| 6.4.6                | Identify Device (ECh)                                     |    |

| 6.4.7                | Idle (97h,E3h)                                            |    |

| 6.4.8                | Idle Immediate (95h,E1h)                                  |    |

| 6.4.9                | Initialize Device Parameters (91h)                        |    |

| 6.4.10               | Read Buffer (E4h)                                         |    |

| 6.4.11               | Read DMA (C8h:with retry, C9h:without retry)              |    |

| 6.4.12               | Read Long (22h:with retry, 23h: without retry)            |    |

| 6.4.13               | Read Multiple Command (C4h)                               |    |

| 6.4.14               | Read Native Max Address (F8h)                             |    |

| 6.4.15               | Read Sector(s) (20h:with retry, 21h:without retry)        |    |

| 6.4.16               | Read Verify Sector(s) (40h:with retry, 41h:without retry) |    |

| 6.4.17               | Recalibrate (1xh)                                         |    |

| 6.4.17               | Seek (7xh)                                                |    |

| 6.4.19               | Set Features (EFh)                                        |    |

| 6.4.19               | Set Max Address (F9h)                                     |    |

| 6.4.21               | Set Multiple Mode (C6h)                                   |    |

| 6.4.22               | 1 ' '                                                     |    |

| 6.4.23               | Sleep (99h, E6h)                                          |    |

|                      | Standby (96h,E2h)                                         |    |

| 6.4.24               | SMART (B0h)                                               |    |

| 6.4.24.1<br>6.4.24.2 | · · · · · · · · · · · · · · · · · · ·                     |    |

| 6.4.24.3             |                                                           |    |

| 6.4.24.4             |                                                           |    |

| 6.4.24.5             |                                                           |    |

| 6.4.24.6             |                                                           |    |

| 6.4.24.7             |                                                           |    |

| 6.4.24.8             |                                                           |    |

| 6.4.24.9             |                                                           |    |

| 6.4.25               | Standby (96h, E2h)                                        |    |

| 6.4.26               | Standby Immediate (94h, E0h)                              | 76 |

| 6.4.27               | Write Buffer (E8h)                                        |    |

| 6.4.28               | Write Long (32h:with retry, 33h:without retry)            |    |

| 6.4.29               | Write DMA (CAh)                                           |    |

| 6.4.30               | Write Multiple Command (C5h)                              |    |

| 6.4.31               | Write Sector(s) (30h:with retry, 31h:without retry)       | 77 |

| 6.5 Pro              | GRAMMING REQUIREMENTS                                     | 79 |

| 6.5.1                | Reset Response                                            |    |

| 6.5.2                | Error Posting                                             | 79 |

| 6.5.3                | Power Conditions                                          |    |

| 6.5.3.1              | Sleep mode                                                | 81 |

| 6.5.3.2              | Standby mode                                              |    |

| 6.5.3.3              | Idle mode                                                 |    |

| 6.5.3.4              | Normal mode                                               |    |

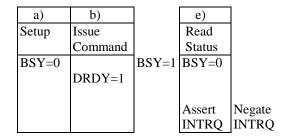

|                      | TOCOL OVERVIEW                                            |    |

| 6.6.1                | PIO Data in Commands                                      |    |

| 6.6.1.1<br>6.6.1.2   | PIO Read Command PIO Read Aborted Command                 |    |

| 6.6.2                | PIO Data Out Commands                                     |    |

| 6.6.2.1              | PIO Write Command                                         |    |

| 6.6.2.2              | PIO Write Aborted Command.                                |    |

| 6.6.3                | Non-Data Commands                                         |    |

| 6.6.4                | DMA Data Transfer Commands                                |    |

| 6.6.4.1              | Normal DMA transfer                                       |    |

| 6.6.4.2              | Aborted DMA transfer                                      |    |

| 6.6.4.3              | Aborted DMA Command                                       |    |

| 6.7 TIM              | NG                                                        |    |

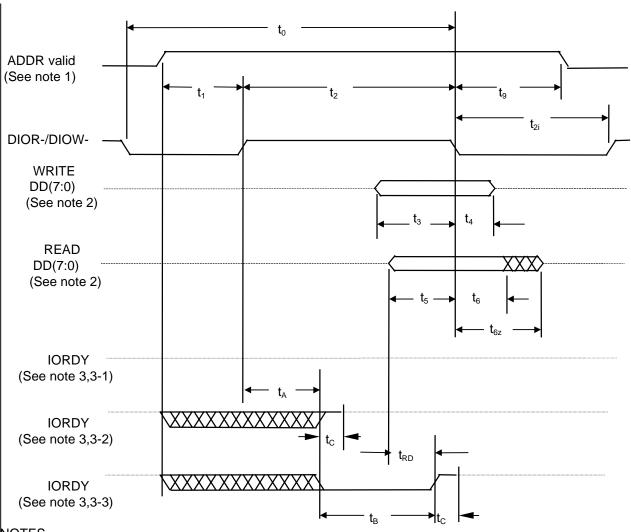

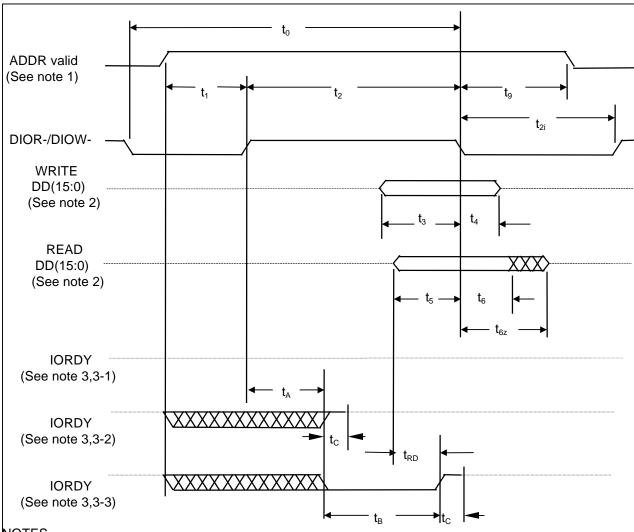

| 6.7.1                | Register transfers                                        |    |

| 6.7.2                | PIO data transfers                                        |    |

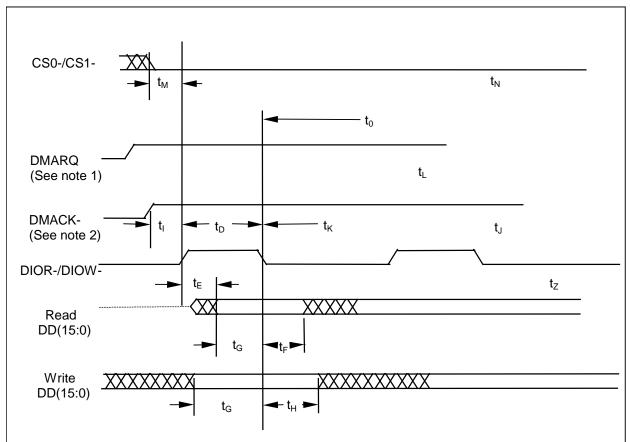

| 6.7.3                | Multiword DMA data transfer                               |    |

| SninPoint W          | 40 Product Manual                                         | V  |

| շխու սու չ           | TV I I VUUCI MAIIUAI                                      | v  |

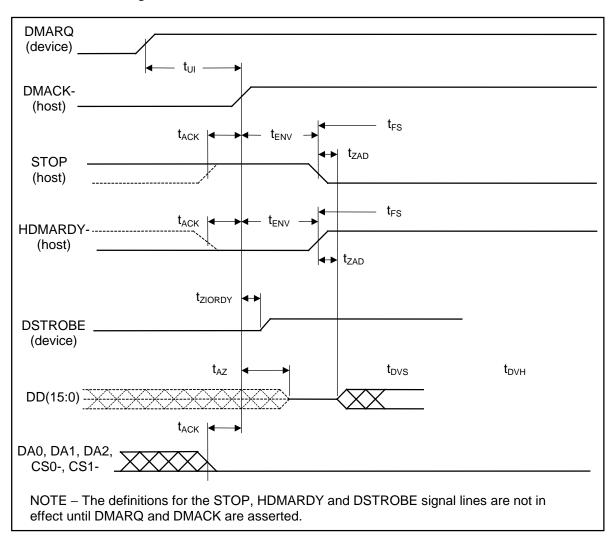

| 6.7.4              | Ultra DMA data transfer                       |     |

|--------------------|-----------------------------------------------|-----|

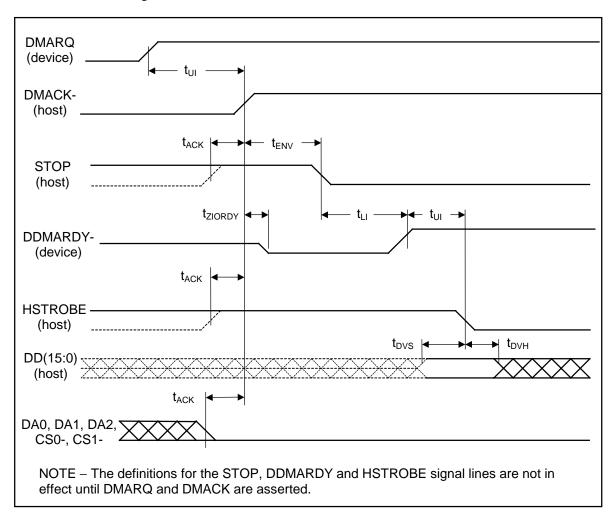

| 6.7.4.1            | Initiating an Ultra DMA data in burst         |     |

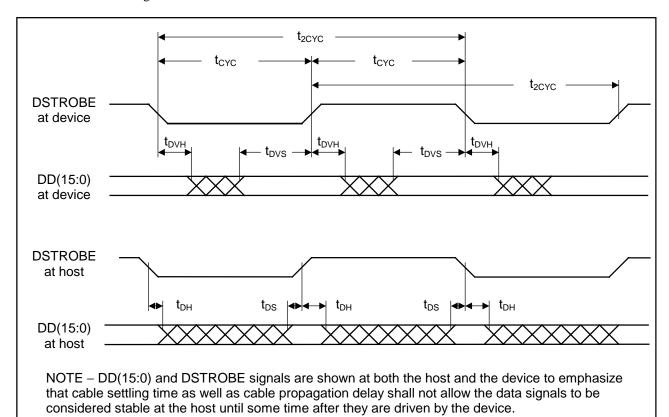

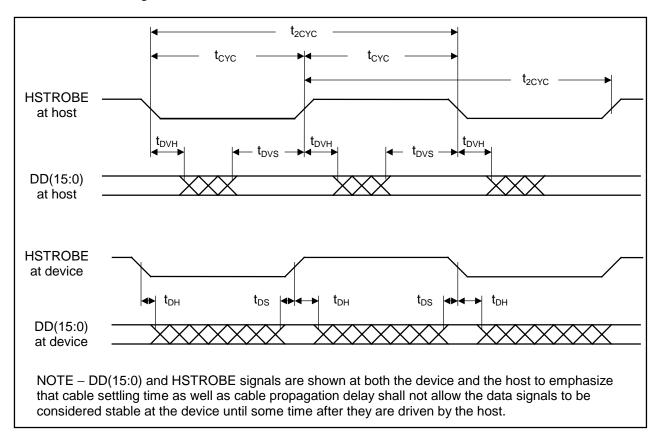

| 6.7.4.2            | Ultra DMA data burst timing requirements      |     |

| 6.7.4.3            | Sustained Ultra DMA data in burst             |     |

| 6.7.4.4            | Host pausing an Ultra DMA data in burst       |     |

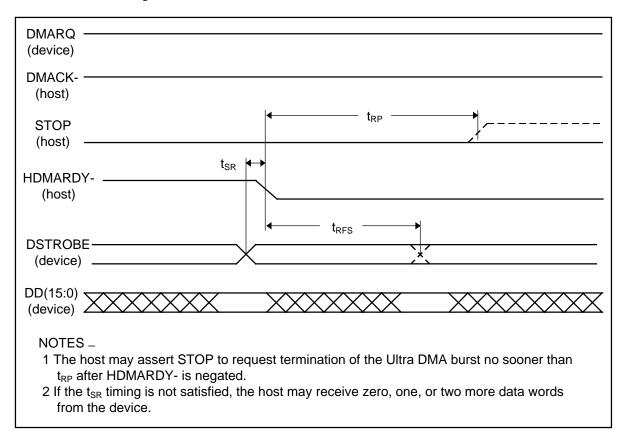

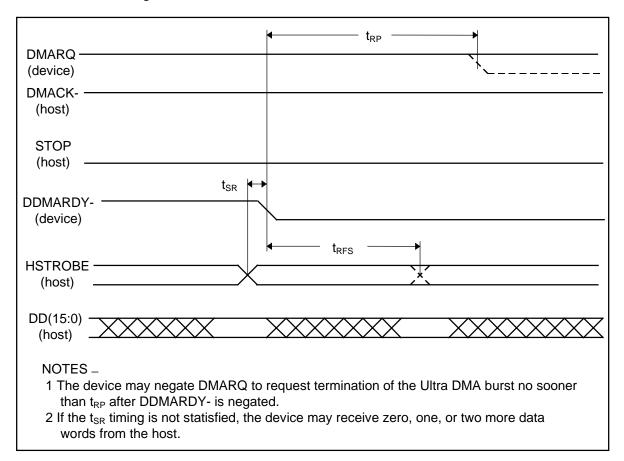

| 6.7.4.5            | Device terminating an Ultra DMA data in burst |     |

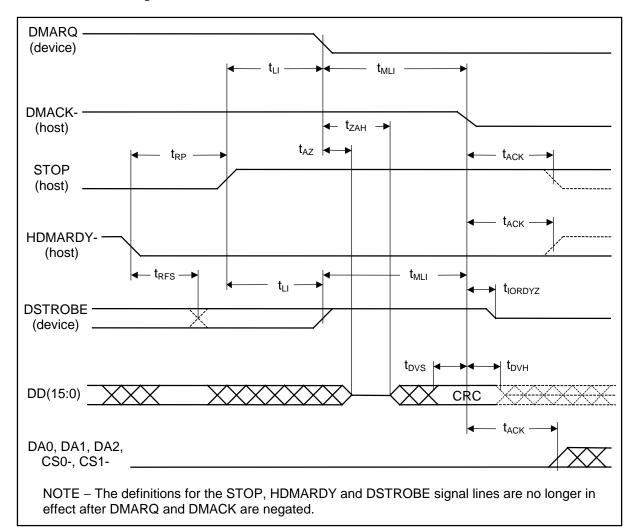

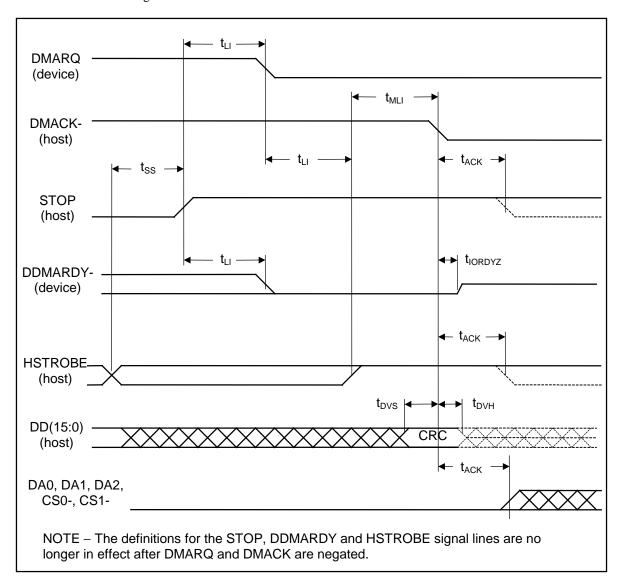

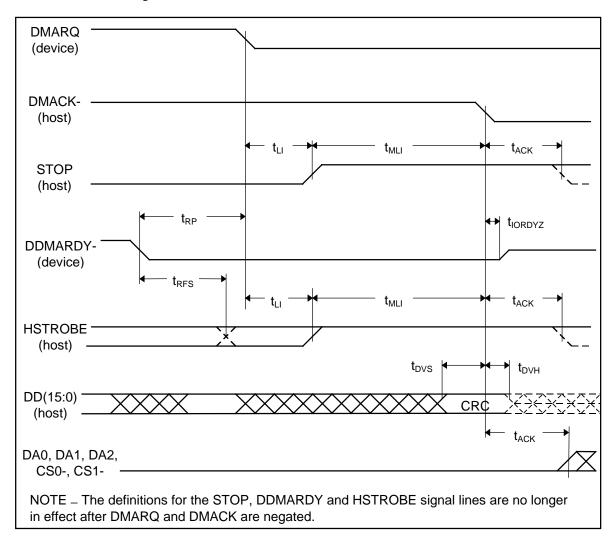

| 6.7.4.6            | Host terminating an Ultra DMA data in burst   |     |

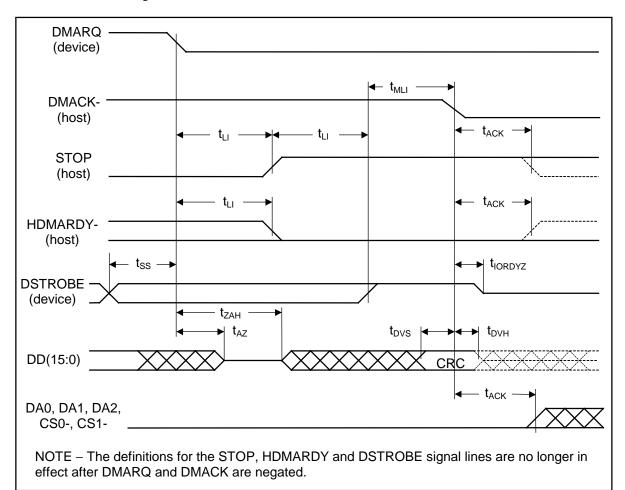

| 6.7.4.7<br>6.7.4.8 | Initiating an Ultra DMA data out burst        |     |

| 6.7.4.9            | Device pausing an Ultra DMA data out burst    |     |

| 6.7.4.10           |                                               |     |

| 6.7.4.11           |                                               |     |

| CHAPTER 7          | MAINTENANCE                                   |     |

|                    | eral Information                              |     |

|                    | VTENANCE PRECAUTIONS                          |     |

|                    | VICE AND REPAIR                               |     |

| 7.5 SERV           | TICE AND REPAIR                               | 107 |

| Table 3-1          | TABLE OF TABLES  Specifications               | 6   |

|                    | Physical Specifications                       |     |

|                    | Logical Configurations                        |     |

|                    | Performance Specifications                    |     |

|                    | Power Requirements                            |     |

|                    | Environmental Specifications                  |     |

|                    | Environmental Specifications (continued)      |     |

|                    | Reliability Specifications                    |     |

|                    | Power Connector Pin Assignment                |     |

|                    | Logical Drive Parameters                      |     |

|                    | AT-Bus Interface Signals                      |     |

|                    | Interface Signals Description                 |     |

|                    | I/O Port Function/Selection Address           |     |

| Table 6-4          | Command Codes and Parameters                  | 54  |

| Table 6-5          | Diagnostic Codes                              | 57  |

| Table 6-6          | IDENTIFY DEVICE information                   | 58  |

| Table 6-7          | Automatic Standby Timer Periods               | 62  |

| Table 6-8          | Set Feature Register Definitions              | 67  |

| Table 6-9          | Transfer mode values                          | 67  |

|                    | 0 SMART Feature register values               |     |

|                    | 1 Device SMART data structure                 |     |

| Table 6-1          | 2 Off-line data collection status values      | 74  |

| Table 6-1          | 3 Command Errors                              | 80  |

| Table 6-1          | 4 Power Saving Mode                           | 81  |

|                    | 5 Power Conditions                            |     |

|                    | 6 Register transfer to/from device            |     |