# VXI-MXI User Manual

October 1993 Edition

Part Number 320222-01

© Copyright 1989, 1993 National Instruments Corporation. All Rights Reserved.

#### **National Instruments Corporate Headquarters**

6504 Bridge Point Parkway Austin, TX 78730-5039 (512) 794-0100 (800) 433-3488 (toll-free U.S. and Canada) Technical support fax: (512) 794-5678

#### **Branch Offices:**

Australia 03 879 9422, Austria 0662 435986, Belgium 02 757 00 20, Canada (Ontario) 519 622 9310, Canada (Québec) 514 694 8521, Denmark 45 76 26 00, Finland 90 527 2321, France 1 48 65 33 70, Germany 089 714 50 93, Italy 02 48301892, Japan 03 3788 1921, Netherlands 01720 45761, Norway 03 846866, Spain 91 640 0085, Sweden 08 730 49 70, Switzerland 056 27 00 20, U.K. 0635 523545

#### **Limited Warranty**

The National Instruments MXIbus boards and accessories are warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this manual is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### **Trademarks**

Product and company names listed are trademarks or trade names of their respective companies.

## Warning Regarding Medical and Clinical Use of National Instruments Products

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

#### FCC/DOC Radio Frequency Interference Compliance

This equipment generates and uses radio frequency energy and, if not installed and used in strict accordance with the instructions in this manual, may cause interference to radio and television reception. This equipment has been tested and found to comply with the following two regulatory agencies:

#### **Federal Communications Commission**

This device complies with Part 15 of the Federal Communications Commission (FCC) Rules for a Class A digital device. Operation is subject to the following two conditions:

- 1. This device may not cause harmful interference in commercial environments.

- 2. This device must accept any interference received, including interference that may cause undesired operation.

#### **Canadian Department of Communications**

This device complies with the limits for radio noise emissions from digital apparatus set out in the Radio Interference Regulations of the Canadian Department of Communications (DOC).

Le présent appareil numérique n'émiet pas de bruits radioélectriques dépassant les limites applicables aux appareils numériques de classe A prescrites dans le réglement sur le brouillage radioélectrique édicté par le ministére des communications du Canada.

#### **Instructions to Users**

These regulations are designed to provide reasonable protection against harmful interference from the equipment to radio reception in commercial areas. Operation of this equipment in a residential area is likely to cause harmful interference, in which case the user will be required to correct the interference at his own expense.

There is no guarantee that interference will not occur in a particular installation. However, the chances of interference are much less if the equipment is installed and used according to this instruction manual.

If the equipment does cause interference to radio or television reception, which can be determined by turning the equipment on and off, one or more of the following suggestions may reduce or eliminate the problem.

- Operate the equipment and the receiver on different branches of your AC electrical system.

- Move the equipment away from the receiver with which it is interfering.

- Reorient or relocate the receiver's antenna.

- Be sure that the equipment is plugged into a grounded outlet and that the grounding has not been defeated with a cheater plug.

**Notice to user:** Changes or modifications not expressly approved by National Instruments could void the user's authority to operate the equipment under the FCC Rules.

If necessary, consult National Instruments or an experienced radio/television technician for additional suggestions. The following booklet prepared by the FCC may also be helpful: *How to Identify and Resolve Radio-TV Interference Problems*. This booklet is available from the U.S. Government Printing Office, Washington, DC 20402, Stock Number 004-000-00345-4.

## **Contents**

| About This Manual                            | χi   |

|----------------------------------------------|------|

| Organization of This Manual                  | vi   |

| How to Use This Manual                       |      |

|                                              |      |

| Related Documentation                        |      |

| Customer Communication                       | X11  |

| Chapter 1                                    |      |

| General Information                          | 1 1  |

| Overview                                     |      |

|                                              |      |

| Front Panel Features                         |      |

| What Your Kit Should Contain                 |      |

| Optional Equipment                           |      |

| Unpacking                                    | 1-/  |

| Chanter 2                                    |      |

| Chapter 2                                    | 0.1  |

| General Description                          | 2-1  |

| Electrical Characteristics                   |      |

| VMEbus Modules                               |      |

| VXI-MXI Functional Description               | 2-5  |

| Chapter 2                                    |      |

| Chapter 3                                    |      |

| Configuration and Installation               | 3-1  |

| Configuring the VXI-MXI                      | 3-1  |

| The Metal Enclosure                          |      |

| VXIbus Slot 0                                |      |

| VXIbus Logical Address                       |      |

| VMEbus Request Level                         |      |

| VMEbus Timeout Value                         |      |

| VMEbus Timeout Chain Position                | 3-10 |

| Interlocked Arbitration Mode                 | 3-13 |

| MXIbus System Controller                     | 3-14 |

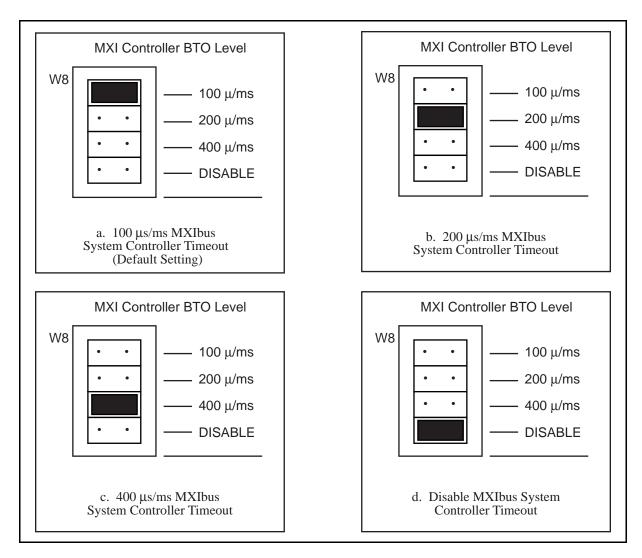

| MXIbus System Controller Timeout             |      |

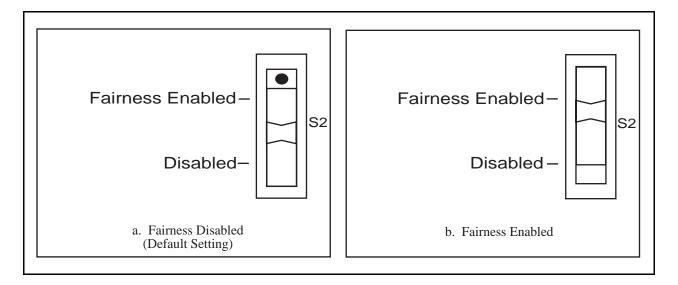

| MXIbus Fairness Option                       |      |

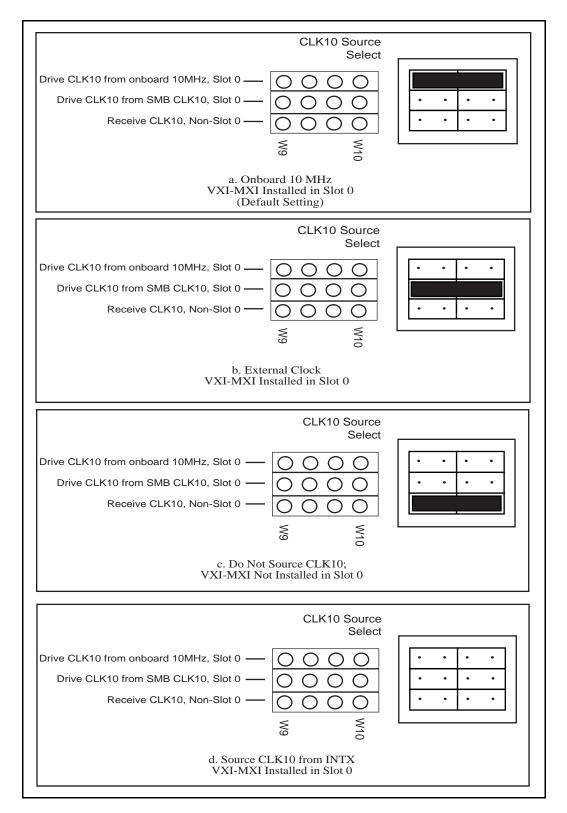

| CLK10 Source                                 |      |

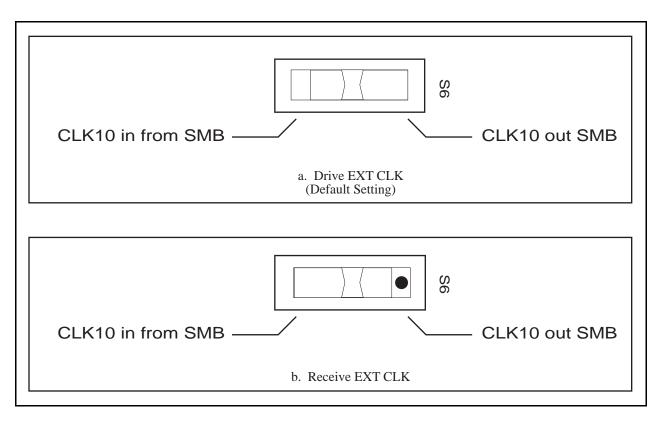

| EXT CLK SMB Input/Output                     |      |

| INTX CLK10 Mapping                           |      |

| Trigger Input Termination                    |      |

| Reset Signal Select                          | 3-23 |

| Installing the VXI-MXI Hardware              | 3-23 |

| MXIbus Termination                           |      |

| INTX Termination                             |      |

| Installation Instructions                    |      |

| Connecting the INTX Cable                    |      |

| Connecting the MXIbus Cable                  |      |

| System Power Cycling Requirements            |      |

| VMEbus Devices in VXIbus/MXIbus Systems      |      |

| VIVILUUS DEVICES III VAIUUS/MAIUUS DYSICIIIS |      |

| Chapter 4                                                       |                 |

|-----------------------------------------------------------------|-----------------|

| Register Descriptions                                           | 4-1             |

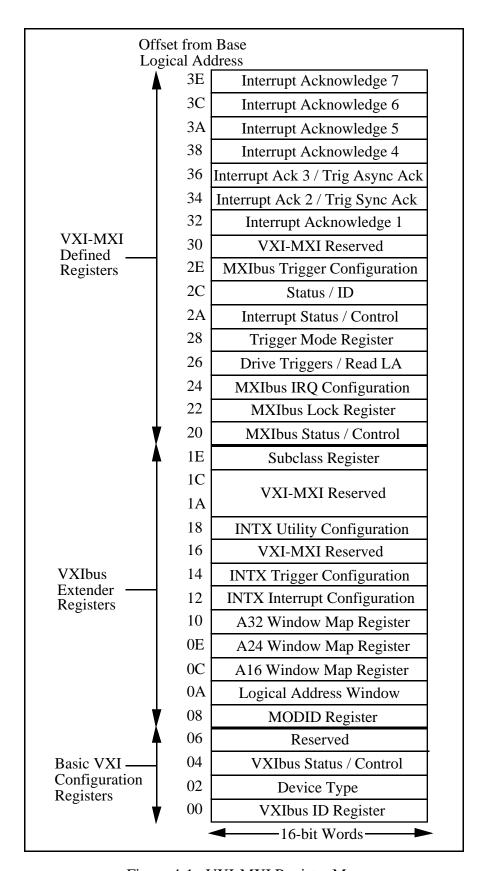

| Register Maps                                                   | 4-1             |

| Register Sizes                                                  | 4-1             |

| Register Description Format                                     | 4-1             |

| Hard and Soft Reset                                             | 4-1             |

| VXIbus Configuration Registers                                  |                 |

| VXIbus ID Register                                              | 4-4             |

| Device Type Register                                            | 4-6             |

| VXIbus Štatus/Control Register                                  | 4-7             |

| VXIbus Extender Registers                                       | 4-9             |

| MODID Register                                                  | 4-9             |

| Logical Address Window Register                                 | 4-10            |

| A16 Window Map Register                                         | 4-14            |

| A24 Window Map Register                                         | 4-18            |

| A32 Window Map Register                                         | 4-22            |

| INTX Interrupt Configuration Register                           | 4-26            |

| INTX Trigger Configuration Register                             | 4-27            |

| INTX Utility Configuration Register                             | 4-28            |

| Subclass Register                                               | 4-30            |

| MXIbus Defined Registers                                        | 4-31            |

| MXIbus Status/Control Register                                  | 4-31            |

| MXIbus Lock Register                                            | 4-36            |

| MXIbus IRQ Configuration Register                               | 4-37            |

| Drive Triggers/Read LA Register                                 | 4-39            |

| Trigger Mode Selection Register                                 | 4-41            |

| Interrupt Status/Control Register                               | 4-45            |

| Status/ID Register                                              | 4-48            |

| MXIbus Trigger Configuration Register                           | 4-49            |

| Trigger Synchronous Acknowledge Register                        | 4-50            |

| Trigger Asynchronous Acknowledge Register                       | 4-5(            |

| IRQ Acknowledge Registers                                       | 4-51            |

|                                                                 |                 |

| Chapter 5                                                       |                 |

| Programming Considerations                                      | 5_1             |

| System Configuration                                            | 5_1             |

| Planning a VXIbus/MXIbus System Logical Address Map             | 5 <sub>-1</sub> |

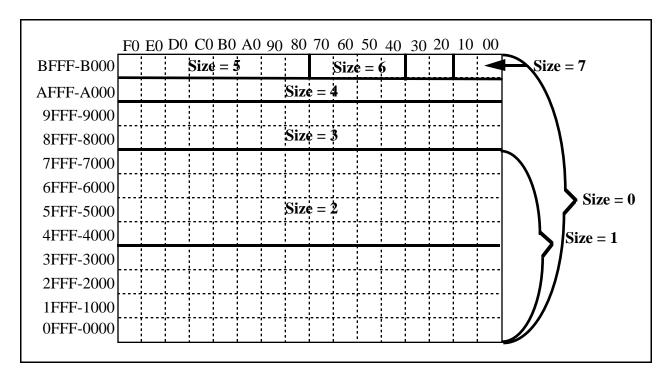

| Base/Size Configuration Format                                  | 5_3             |

| High/Low Configuration Format                                   | 5-5             |

| Steps to Follow When Planning a System Logical Address Map      | 5-5             |

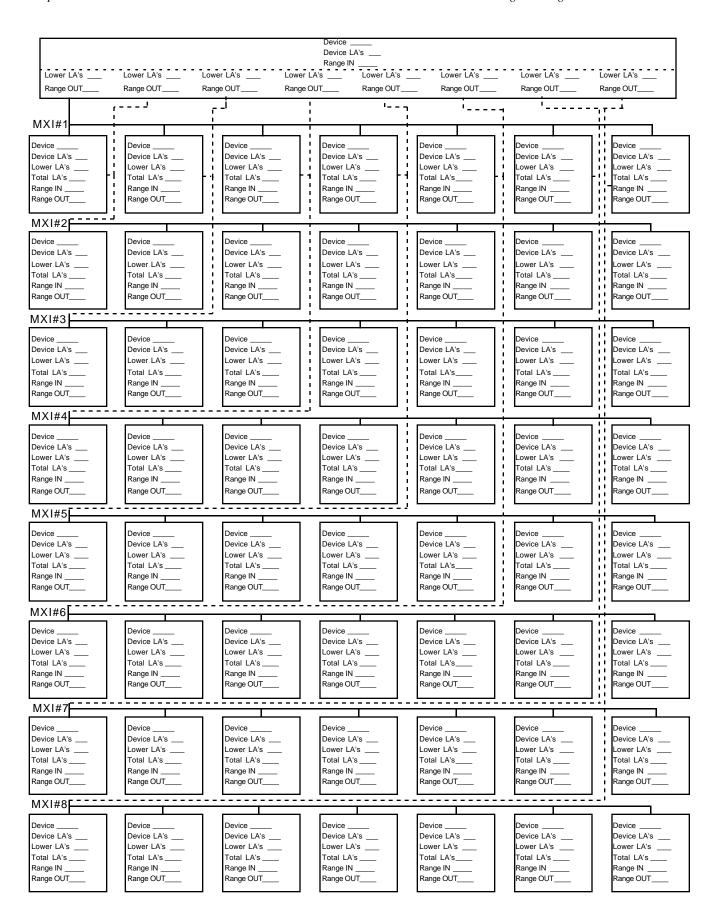

| Worksheets for Planning Your VXIbus/MXIbus Logical Address Map. | 5-19            |

| Alternative Worksheets for Planning Your VXIbus/MXIbus Logical  |                 |

| Address Map                                                     | 5-18            |

| Planning a VXIbus/MXIbus System A16 Address Map                 | 5-21            |

| Worksheets for Planning Your VXIbus/MXIbus A16 Address Map      | 5-29            |

| Multiframe RM Operation                                         | 5-35            |

| Configuring the Logical Address Window                          | 5-34            |

| Configuring the Logical Address Window Example                  | 5-36            |

| Configuring the A24 and A32 Addressing Windows                  |                 |

| System Administration and Initiation                            | 5_30            |

| Chapter 6                                                                                                                                                                                |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Theory of Operation  VMEbus Address and Address Modifier Transceivers                                                                                                                    | 6-1        |

| VMEbus Address and Address Modifier Transceivers                                                                                                                                         | 6-1        |

| VXIbus System Controller Functions                                                                                                                                                       | 6-1        |

| VMEbus Data Transceivers                                                                                                                                                                 | 6-1        |

| VMEbus Control Signals Transceivers                                                                                                                                                      | 6-2        |

| VMEbus Requester and Arbiter Circuitry                                                                                                                                                   | 6-2        |

| TTL and ECL Trigger Lines and CLK10 Circuitry                                                                                                                                            | 6-2        |

| SYSFAIL, ACFAIL, and SYSRESET                                                                                                                                                            | 6-3        |

| Interrupt Circuitry                                                                                                                                                                      | 6-3        |

| Parity Check and Generation                                                                                                                                                              | 6-6        |

| A32, A24, A16, and LA Windows                                                                                                                                                            | 6-6        |

| VXI-MXI Configuration Registers                                                                                                                                                          | 6-6        |

| MXIbus Master Mode State Machine                                                                                                                                                         |            |

| MXIbus Slave Mode State Machine                                                                                                                                                          | 0-10       |

| MXIbus Address/Data and Address Modifier Transceivers                                                                                                                                    |            |

| MXIbus System Controller Functions                                                                                                                                                       | 0-12       |

| MXIbus Control Signals Transceivers                                                                                                                                                      |            |

| MXIbus Requester and Arbiter Circuitry                                                                                                                                                   | 0-12       |

| Annondix A                                                                                                                                                                               |            |

| Appendix A                                                                                                                                                                               |            |

| Specifications                                                                                                                                                                           | A-1        |

| A I'm D                                                                                                                                                                                  |            |

| Appendix B                                                                                                                                                                               |            |

| Mnemonics Key                                                                                                                                                                            | B-1        |

| Appendix C VXI-MXI Component Placement Removing the Metal Enclosure from the VXI-MXI Removing the INTX Daughter Card from the VXI-MXI Installing the INTX Daughter Card onto the VXI-MXI |            |

| Annondin D                                                                                                                                                                               |            |

| Appendix D                                                                                                                                                                               |            |

| Connector Descriptions                                                                                                                                                                   |            |

| MXIbus Connector                                                                                                                                                                         |            |

| INTX Connector                                                                                                                                                                           | D-3        |

| Appendix E                                                                                                                                                                               |            |

|                                                                                                                                                                                          | E 1        |

| Configuring a Two-Frame System                                                                                                                                                           | E-1        |

| Configuring VXI-MXIs for a Two-Frame System                                                                                                                                              | E-1        |

| Configuration Requirements for Two-Frame SystemBTO Unit                                                                                                                                  | E-0        |

| Logical Addresses                                                                                                                                                                        |            |

| CLK10 Mapping                                                                                                                                                                            |            |

| CLK10 Mapping                                                                                                                                                                            | L-0        |

| Appendix F                                                                                                                                                                               |            |

| Customer Communication                                                                                                                                                                   | T7 1       |

| Cusionici Communication                                                                                                                                                                  | Г-1        |

| Glossary                                                                                                                                                                                 | Glossory 1 |

| U105541 y                                                                                                                                                                                | O1058a1y-1 |

| Index                                                                                                                                                                                    | Index-1    |

#### **Figures**

| Figure 1-1. Figure 1-2. | VXI-MXI Interface Module                                      | 1-2  |

|-------------------------|---------------------------------------------------------------|------|

| · ·                     | VAI-WAI Interface Woulde with INTA Option                     | 1-3  |

| Figure 2-1.             | VXI-MXI Block Diagram                                         |      |

| Figure 2-2.             | VXI-MXI INTX Daughter Card Option Block Diagram               | 2-8  |

| Figure 3-1.             | VXI-MXI Parts Locator Diagram                                 |      |

| Figure 3-2.             | VXI-MXI with INTX Parts Locator Diagram                       |      |

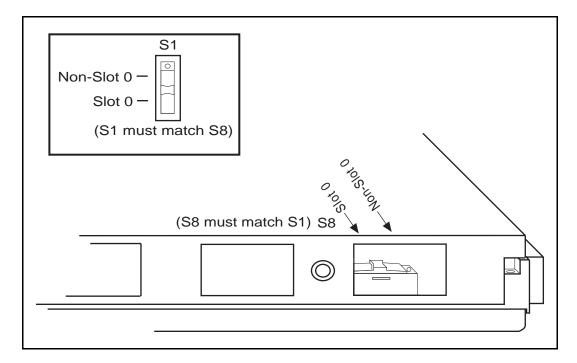

| Figure 3-3.             | VXIbus Slot 0 Selection                                       |      |

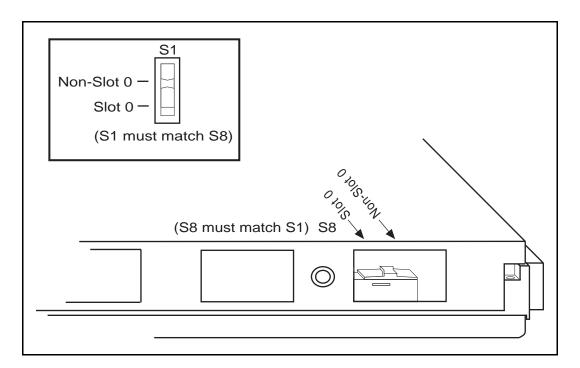

| Figure 3-4.             | VXIbus Non-Slot 0 Selection                                   |      |

| Figure 3-5.             | Logical Address Selection                                     |      |

| Figure 3-6.             | VMEbus Requester Jumper Settings                              |      |

| Figure 3-7.             | VMEbus Timeout Value Selection                                |      |

| Figure 3-8.             | VMEbus Timeout; One VXI-MXI in Mainframe                      |      |

| Figure 3-9.             | VMEbus Timeout; Multiple VXI-MXIs in Mainframe                |      |

| Figure 3-10.            | No VMEbus Timeout; Multiple VXI-MXIs in Mainframe             |      |

| Figure 3-11.            | Interlocked Arbitration Mode Selection                        |      |

| Figure 3-12.            | MXIbus System Controller Selection                            | 3-15 |

| Figure 3-13.            | MXIbus System Controller Timeout Value Selection              | 3-16 |

| Figure 3-14.            | MXIbus Fair Requester Selection                               |      |

| Figure 3-15.            | CLK10 Source Signal Options                                   |      |

| Figure 3-16.            | EXT CLK SMB Input/Output Setting                              |      |

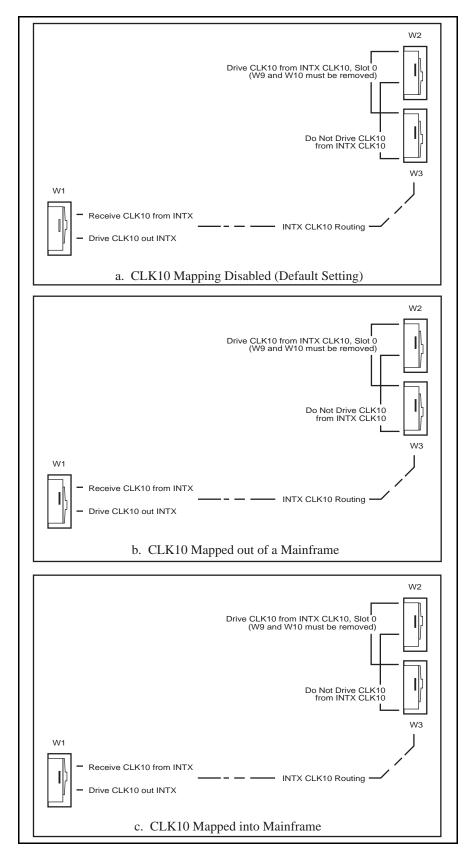

| Figure 3-17.            | INTX CLK10 Mapping Switches                                   |      |

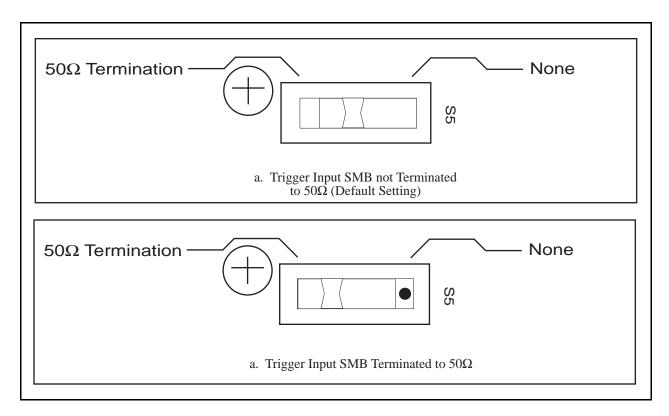

| Figure 3-18.            | Trigger Input Termination Option Settings                     | 3-22 |

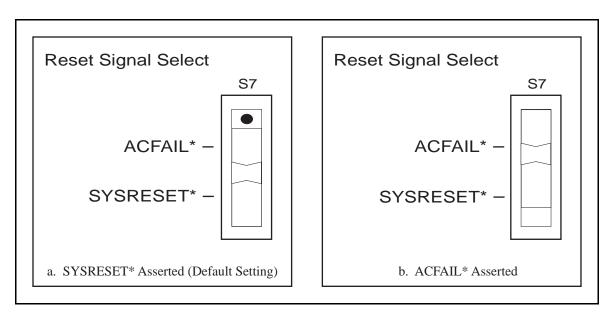

| Figure 3-19.            | Reset Signal Selection Settings                               | 3-23 |

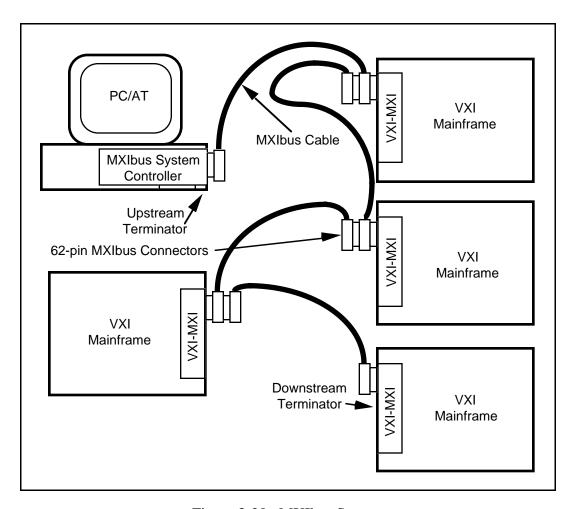

| Figure 3-20.            | MXIbus System                                                 |      |

| Figure 3-21.            | MXIbus Terminating Networks                                   |      |

| Figure 3-22.            | INTX Terminator Example                                       | 3-26 |

| Figure 3-23.            | MXIbus Single-Ended Cable Configuration                       | 3-28 |

| Figure 3-24.            | MXIbus Dual-Ended Cable Configuration                         | 3-29 |

| Figure 4-1.             | VXI-MXI Register Map                                          | 4-3  |

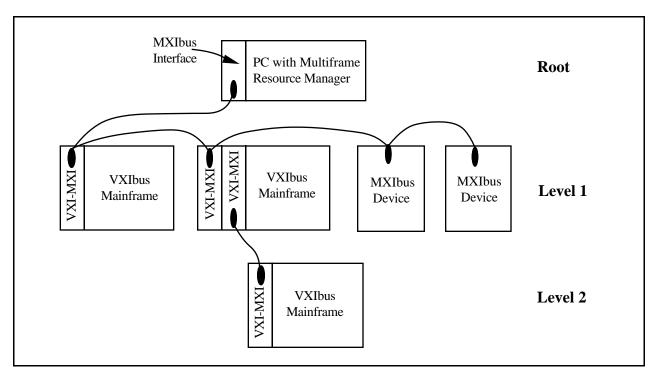

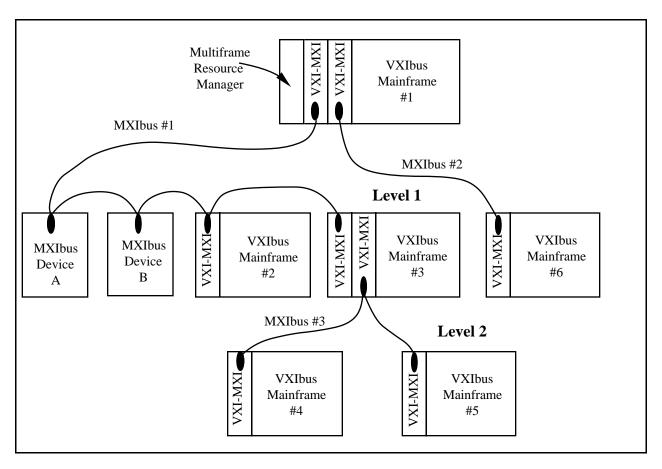

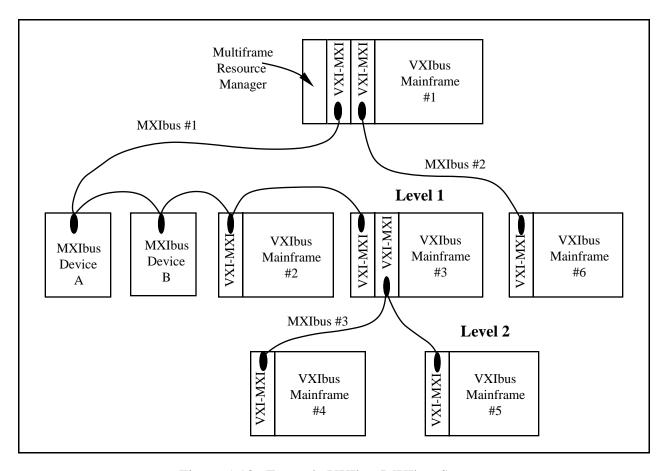

| Figure 5-1.             | VXIbus/MXIbus System with Multiframe RM on a PC               |      |

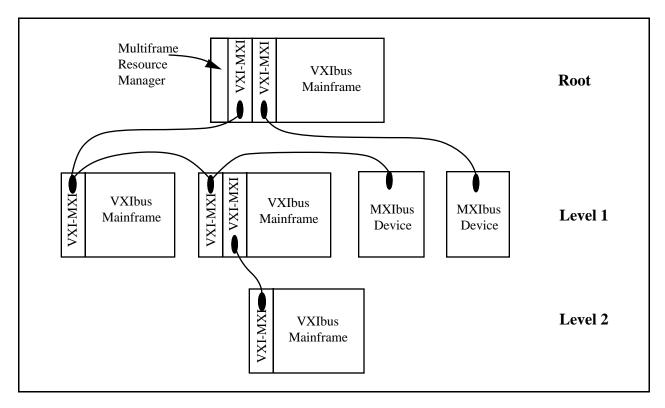

| Figure 5-2.             | VXIbus/MXIbus System with Multiframe RM in a VXIbus Mainframe | 5-2  |

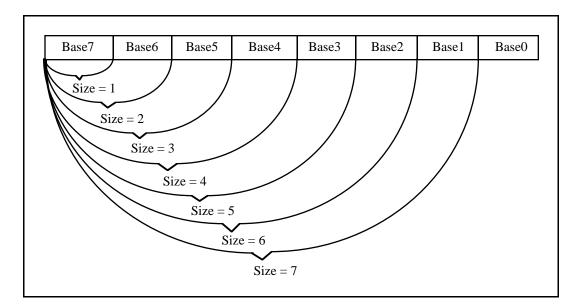

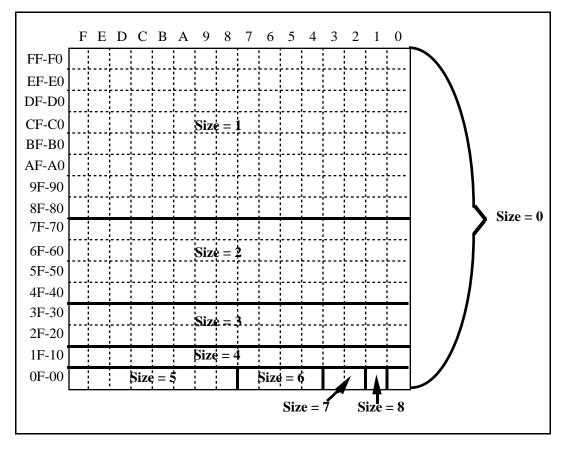

| Figure 5-3.             | Base and Size Combinations                                    |      |

| Figure 5-4.             | Address Range Allocation for Different Size Values            | 5-4  |

| Figure 5-5.             | Example VXIbus/MXIbus System                                  | 5-8  |

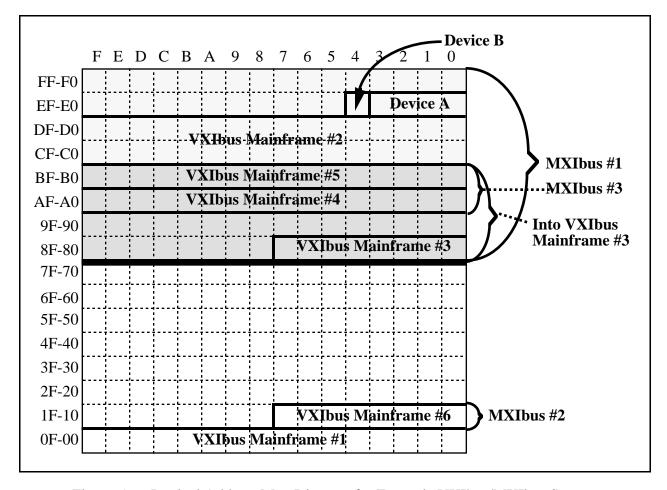

| Figure 5-6.             | Logical Address Map Diagram for Example VXIbus/MXIbus System  | 5-9  |

| Figure 5-7.             | Worksheet 1 for Example VXIbus/MXIbus System                  | 5-10 |

| Figure 5-8.             | Worksheet 2 for Example VXIbus/MXIbus System                  | 5-11 |

| Figure 5-9.             | Worksheet 3 for Example VXIbus/MXIbus System                  | 5-12 |

| Figure 5-10.            | Worksheet 4 for Example VXIbus/MXIbus System                  | 5-12 |

| Figure 5-11.            | Logical Address Map Example with Alternative Worksheet        | 5-20 |

| Figure 5-12.            | A16 Space Allocations for all Size Values                     | 5-22 |

| Figure 5-13.            | Example VXIbus/MXIbus System                                  |      |

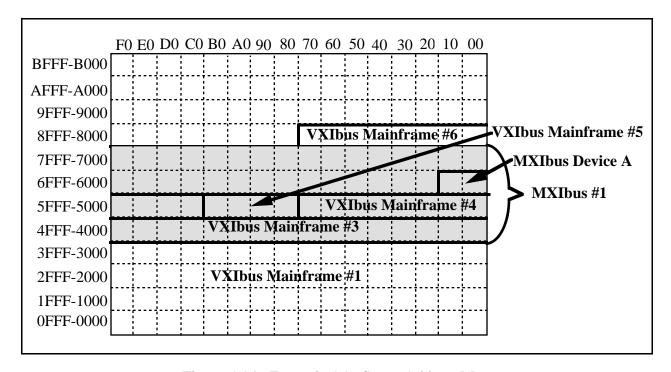

| Figure 5-14.            | Example A16 Space Address Map                                 | 5-25 |

| Figure 5-15.            | Worksheet 1 for A16 Address Map Example                       | 5-26 |

| Figure 5-16.            | Worksheet 2 for A16 Map Example                               | 5-27 |

| Figure 5-17.            | Worksheet 3 for A16 Map Example                               | 5-28 |

| Figure 6-1. Figure 6-2.                                                 | Master to Slave VMEbus/MXIbus Transfers  Deadlock Situation                                                                                                                                                                                           |                     |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Figure C-1.<br>Figure C-2.<br>Figure C-3.                               | VXI-MXI Parts Locator Diagram                                                                                                                                                                                                                         | C-3                 |

| Figure D-1. Figure D-2.                                                 | MXIbus Connector                                                                                                                                                                                                                                      |                     |

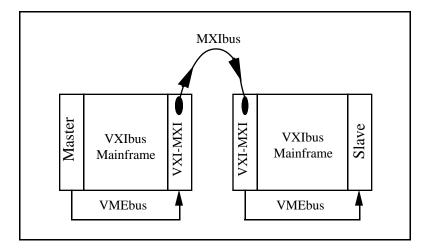

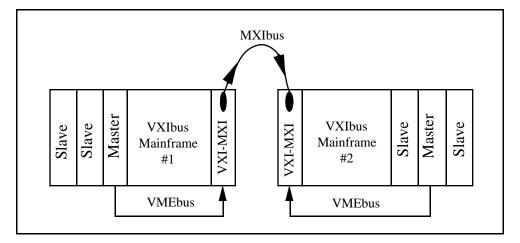

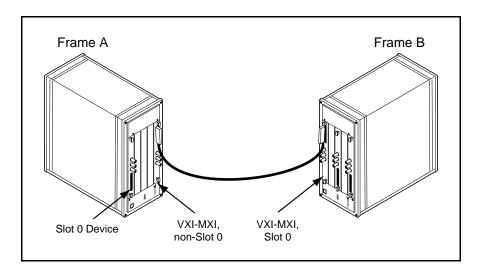

| Figure E-1.<br>Figure E-2.<br>Figure E-3.<br>Figure E-4.<br>Figure E-5. | A Two-Frame VXI System  VXI-MXI in Frame A without INTX  VXI-MXI in Frame B without INTX  VXI-MXI in Frame A with INTX  VXI-MXI in Frame B with INTX                                                                                                  | E-2<br>E-3<br>E-4   |

|                                                                         | Tables                                                                                                                                                                                                                                                |                     |

| Table 2-1.<br>Table 2-2.<br>Table 2-3.                                  | VXI-MXI VMEbus Signals                                                                                                                                                                                                                                | 2-2                 |

| Table 3-1.                                                              | MXIbus System Power Cycling Requirements                                                                                                                                                                                                              | 3-30                |

| Table 4-1.                                                              | VXI-MXI Register Map                                                                                                                                                                                                                                  | 4-2                 |

| Table 5-1. Table 5-2. Table 5-3. Table 5-4. Table 5-5.                  | Base and Size Combinations  Example VXIbus/MXIbus System Required Logical Addresses  Amount of A16 Space Allocated for all Size Values  Example VXIbus/MXIbus System Required A16 Space  Logical Address Assignments for Example VXIbus/MXIbus System | 5-8<br>5-21<br>5-25 |

| Table 6-1.<br>Table 6-2.<br>Table 6-3.<br>Table 6-4.                    | VXI-MXI Addresses for VMEbus Interrupt Levels VMEbus to MXIbus Address Modifier Line Map Transfer Responses for VMEbus Address Modifiers VMEbus/MXIbus Transfer Size Comparison                                                                       | 6-7<br>6-8          |

| Table D-1. Table D-2. Table D-3. Table D-4.                             | MXIbus Connector Signal Assignments  MXIbus Signal Groupings  INTX Connector Signal Assignments  INTX Signal Groupings                                                                                                                                | D-2<br>D-3          |

#### **About This Manual**

The *VXI-MXI User Manual* describes the functional, physical, and electrical aspects of the VXI-MXI and contains information concerning its operation and programming.

#### **Organization of This Manual**

The VXI-MXI User Manual is organized as follows:

- Chapter 1, *General Information*, describes the VXI-MXI features, lists the contents of your VXI-MXI kit, and explains how to unpack the VXI-MXI kit.

- Chapter 2, *General Description*, contains the physical and electrical specifications for the VXI-MXI and describes the characteristics of key components.

- Chapter 3, *Configuration and Installation*, describes the configuration and installation of the VXI-MXI hardware.

- Chapter 4, *Register Descriptions*, contains detailed descriptions of the VXI-MXI registers, which are used to configure and control the module's operation.

- Chapter 5, *Programming Considerations*, explains important considerations for programming the VXI-MXI and configuring a system using VXI-MXIs.

- Chapter 6, *Theory of Operation*, contains a functional overview of the VXI-MXI board and explains the operation of each functional block making up the VXI-MXI.

- Appendix A, Specifications, lists the specifications of the VXI-MXI.

- Appendix B, *Mnemonics Key*, contains an alphabetical listing of all mnemonics used in this manual.

- Appendix C, *VXI-MXI Component Placement*, contains information on the component placement and describes how to remove the metal enclosure and INTX daughter card.

- Appendix D, *Connector Descriptions*, describes the connector pin assignments for the MXIbus connector.

- Appendix E, *Configuring a Two-Frame System*, describes how to configure a system containing two mainframes linked by VXI-MXI modules.

- Appendix F, *Customer Communication*, contains forms you can use to request help from National Instruments or to comment on our products and manuals.

- The *Glossary* contains an alphabetical list and description of terms used in this manual, including abbreviations, acronyms, metric prefixes, and symbols.

- The *Index* contains an alphabetical list of key terms and topics in this manual, including the page where you can find each one.

#### **How to Use This Manual**

If you will be installing your VXI-MXI into a system with a VXIbus Resource Manager, you only need to read Chapters 1 through 3 of this manual. If you have more than two VXI-MXIs extending your system, you will find useful system configuration information in Chapter 5. Appendix E is a quick reference for users who have a system containing two mainframes linked by VXI-MXI modules. If you are writing your own VXIbus Resource Manager routines, you can find programming information and descriptions of the VXI-MXI hardware in Chapters 4 through 6.

#### **Related Documentation**

The following manuals contain information that you may find helpful as you read this manual:

- IEEE Standard for a Versatile Backplane Bus: VMEbus, ANSI/IEEE Standard 1014-1987

- Multisystem Extension Interface Bus Specification, Version 1.2 (part number 340007-01)

- *VXIbus System Specification*, Revision 1.4, VXIbus Consortium (available from National Instruments, part number 350083-01)

#### **Customer Communication**

National Instruments wants to receive your comments on our products and manuals. We are interested in the applications you develop with our products, and we want to help if you have problems with them. To make it easy for you to contact us, this manual contains comment and configuration forms for you to complete. These forms are in Appendix F, *Customer Communication*, at the end of this manual.

### Chapter 1 General Information

This chapter describes the VXI-MXI features, lists the contents of your VXI-MXI kit, and explains how to unpack the VXI-MXI kit.

The VXI-MXI interface is a C-size extended class mainframe extender for the VXIbus (VMEbus Extensions for Instrumentation). It extends the VXIbus architecture outside a VXIbus mainframe via the MXIbus (Multisystem Extension Interface bus). A VXIbus mainframe equipped with a VXI-MXI can be transparently connected to other MXIbus devices such as other VXIbus mainframes, MXIbus instruments, or MXIbus-equipped personal computers. The VXI-MXI interface module uses address mapping to transparently translate bus cycles on the VXIbus system bus (VMEbus) to the MXIbus and vice versa.

The VXI-MXI is housed in a metal enclosure to improve EMI performance and to provide easy handling. Because the enclosure includes cut-outs to facilitate changes to switch and jumper settings, it should not be necessary to remove it under most circumstances.

The VXI-MXI is available with an Interrupt and Timing Extension (INTX) daughter card option. If you ordered this option, the INTX card is already installed on your VXI-MXI. The INTX daughter card is a full-length daughter card that plugs into the two daughter card connectors on the VXI-MXI. Because this manual describes the VXI-MXI with and without this option, you can find information on the INTX card throughout this manual. Refer also to Appendix C, *VXI-MXI Component Placement*, for information on removing and reinstalling the INTX daughter card. This appendix also contains silkscreens of the VXI-MXI and the INTX card.

Figure 1-1 shows the enclosed VXI-MXI interface module without the INTX option. Figure 1-2 shows the enclosed VXI-MXI interface module with the INTX option.

Figure 1-1. VXI-MXI Interface Module

Figure 1-2. VXI-MXI Interface Module with INTX Option

General Information Chapter 1

#### **Overview**

The VXI-MXI is an extended class Register-Based VXIbus device with optional Slot 0 capability so that it can reside in any slot in a C-size or D-size VXIbus chassis. The VXI-MXI converts A32, A24, A16, D32, D16, and D08(EO) VXIbus bus cycles into MXIbus bus cycles and vice versa. The VXI-MXI has four address windows that map into and out of the VXIbus mainframe. These four windows represent the three VMEbus address spaces (A32, A24, and A16) plus a dedicated window for mapping the VXIbus configuration space (the upper 16 kilobytes of A16 space).

The MXIbus is a multidrop system bus that connects multiple devices at the hardware bus level in a software-transparent manner. Multiple VXIbus mainframes with VXI-MXI interfaces can be connected to form a single multiframe VXIbus system. An external PC with a MXIbus interface can also be connected to a VXIbus mainframe with a VXI-MXI. This configuration makes the PC appear to be embedded on a VXIbus module that is plugged into the VXIbus mainframe.

Multiple MXIbus devices are tightly coupled by mapping together portions of each device's address space and locking the internal hardware bus cycles to the MXIbus. The window address circuitry on each MXIbus device monitors internal local bus cycles to detect bus cycles that map across the MXIbus. Similarly, external MXIbus cycles are monitored to detect MXIbus cycles that map into the VXIbus system. MXIbus devices can operate in parallel at full speed over their local system bus and need to synchronize operation with another device only when addressing or being addressed by a resource located on another MXIbus device. The MXIbus device originating the transaction must gain ownership of both the MXIbus and the local bus in the target MXIbus device. All hardware bus cycles are then coupled across the MXIbus and local buses before the transfer completes.

#### The VXI-MXI has the following features:

- Interfaces the VXIbus to the MXIbus (32-bit Multisystem eXtension Interface bus)

- Extends VXIbus to multiple mainframes, external MXIbus-equipped instruments, and external MXIbus-equipped personal computers (PCs)

- Allows multiple VXIbus mainframes to appear as a single VXIbus system

- Provides integrated block mode for high-performance data transfers

- Supports dynamic configuration of VXIbus devices

- Provides optional interlocked bus operation for prevention of deadlock conditions

- Includes daughter card connector scheme giving additional functionality for optional daughter cards

- Is fully compatible with VXIbus and MXIbus specifications

- Has no restrictions on Commander/Servant hierarchy or physical location of devices

The VXI-MXI generates all the support signals required by the VMEbus:

- VMEbus System Controller functions:

- 16 MHz system clock driver

- VME bus timeout (BTO)

Chapter 1 General Information

- Data transfer bus arbiter (PRI ARBITER)

- Interrupt acknowledge daisy-chain driver

- Pushbutton system reset switch

- VMEbus master capabilities:

- Access to A16, A24, and A32 address space

- D08(EO), D16, and D32 accesses

- Release-on-Request bus requester (jumper-selectable arbitration level)

- VMEbus slave accesses:

- A16, A24, and A32 address space

- D08(EO), D16, and D32 accesses

- VXIbus Slot 0 functions:

- 10 MHz clock

- MODID register

- TTL and ECL Trigger line support

All integrated circuit drivers and receivers used on the VXI-MXI meet the requirements of both the VMEbus specification and the MXIbus specification.

#### **Front Panel Features**

The VXI-MXI has the following front panel features:

- Three front panel LEDs

- FAILED LED indicates that the VMEbus SYSFAIL line is asserted.

- VXI ACCESS LED indicates when the VXI-MXI is accessed from the VXIbus.

- MXI ACCESS LED indicates when the VXI-MXI is accessed from the MXIbus.

- MXIbus connector

- Three SMB connectors

- Trigger input

- Trigger output

- External clock input or output (configurable)

- System reset pushbutton

- INTX connector (if your VXI-MXI includes the INTX daughter card option)

General Information Chapter 1

#### What Your Kit Should Contain

Your VXI-MXI kit should contain the following components:

| Component                                          | Part Number |

|----------------------------------------------------|-------------|

| Standard VXI-MXI Interface Module                  | 181045-01   |

| or                                                 |             |

| Enhanced VXI-MXI Interface Module with INTX option | 181045-02   |

| VXI-MXI User Manual                                | 320222-01   |

### **Optional Equipment**

| Equipment                                                                               | Part Number                                                   |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Type M1 MXIbus Cables Straight-point connector to straight-point connector:             |                                                               |

| - 1 m<br>- 2 m<br>- 4 m<br>- 8 m<br>- 20 m                                              | 180758-01<br>180758-02<br>180758-04<br>180758-08<br>180758-20 |

| Type M2 MXIbus Cables Straight-point connector to right-angle daisy-chain connector:    |                                                               |

| - 1 m<br>- 2 m<br>- 4 m<br>- 8 m<br>- 20 m                                              | 180760-01<br>180760-02<br>180760-04<br>180760-08<br>180760-20 |

| Type M3 MXIbus Cables Right-angle point connector to right-angle daisy-chain connector: |                                                               |

| - 1 m<br>- 2 m<br>- 4 m<br>- 8 m<br>- 20 m                                              | 180761-01<br>180761-02<br>180761-04<br>180761-08<br>180761-20 |

| MXIbus Terminating Pac (External)                                                       | 180780-01                                                     |

Chapter 1 General Information

The following optional equipment is also available and may be necessary if your VXI-MXI includes the INTX daughter card.

| Equipment                                                                                                           | Part Number                                                   |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Type INTX1 Cables Straight-point connector to straight-point connector:                                             |                                                               |

| - 1 m<br>- 2 m<br>- 4 m<br>- 8 m<br>- 20 m                                                                          | 180980-01<br>180980-02<br>180980-04<br>180980-08<br>180980-20 |

| Type INTX2 Cables Right-angle point connector to right-angle daisy-chain connector:  - 1 m - 2 m - 4 m - 8 m - 20 m | 180982-01<br>180982-02<br>180982-04<br>180982-08<br>180982-20 |

#### **Unpacking**

Follow these steps when unpacking your VXI-MXI:

- 1. Before attempting to configure or install the VXI-MXI, inspect the shipping container and its contents for damage. If damage appears to have been caused in shipment, file a claim with the carrier. Retain the packing material for possible inspection and/or for reshipment.

- 2. Verify that the pieces contained in the package you received match the kit parts list. *Do not* remove the board from its bag at this point.

- 3. Your VXI-MXI module is shipped packaged in an antistatic plastic bag to prevent electrostatic damage to the module. Several components on the module can be damaged by electrostatic discharge. To avoid such damage while handling the module, touch the plastic bag to a metal part of your grounded VXIbus mainframe chassis before removing the module from the bag.

- 4. As you remove the VXI-MXI module from its bag, be sure to handle it only by its edges. Avoid touching any of the IC components or connectors. Inspect the module for loose components or any other sign of damage. Notify National Instruments if the module appears damaged in any way. *Do not* install a damaged module into your VXIbus mainframe.

## Chapter 2 General Description

This chapter contains the physical and electrical specifications for the VXI-MXI and describes the characteristics of key interface board components.

#### **Electrical Characteristics**

All integrated circuit drivers and receivers used on the VXI-MXI meet the requirements of the VMEbus specification. Table 2-1 contains a list of the VMEbus signals used by the VXI-MXI and the electrical loading presented by the circuitry on the interface board (in terms of device types and their part numbers).

Note: Throughout this manual, an asterisk (\*) following a bus signal mnemonic indicates that the signal is active low.

Table 2-1. VXI-MXI VMEbus Signals

| Bus Signals              | Driver Device<br>Part Number | Receiver Device<br>Part Number |

|--------------------------|------------------------------|--------------------------------|

| D[31–0], A[31–1],        | ALS645-1                     | ALS645-1                       |

| AM[5–0], LWORD           | ALS646-1                     | ALS646-1                       |

| DS0*, DS1*, WRITE*       | F125                         | ALS244                         |

| AS*                      | F125                         | ALS240                         |

| SYSCLK                   | F125                         | _                              |

| BG[3-0]IN*               | -                            | HCT273,<br>GAL16V8             |

| BG[3-0]OUT*              | LS32                         | _                              |

| BBSY*, SYSFAIL*, ACFAIL* | F38                          | ALS240                         |

| BR[3-0]*, DTACK*, BERR*  | F38                          | ALS244                         |

| SYSRESET*                | AS760                        | ALS244                         |

| IACK*                    | F38                          | _                              |

(continues)

General Description Chapter 2

Table 2-1. VXI-MXI VMEbus Signals (Continued)

| Bus Signals | Driver Device<br>Part Number | Receiver Device<br>Part Number |

|-------------|------------------------------|--------------------------------|

| IACKIN*     | _                            | LS540                          |

| IACKOUT*    | GAL20V8                      | _                              |

| IRQ[7-1]*   | AS760,<br>LS145              | LS540                          |

All MXIbus transceivers meet the requirements of the MXIbus specification. Table 2-2 lists the components used.

Table 2-2. MXIbus Transceiver Requirements

| Transceivers         | Component Designation |

|----------------------|-----------------------|

| Data Transceivers    | DS3862                |

| Control Transceivers | DS3662                |

#### **VMEbus Modules**

The VXI-MXI has the following VMEbus modules:

- VMEbus Requester

- VMEbus Master

- VMEbus Slave

- Interrupter

- IACK Daisy-Chain Driver

When the VXI-MXI is configured as a VXIbus Slot 0 device, it also has the following VMEbus modules:

- VMEbus Timer

- Arbiter

- System Clock Driver

Chapter 2 General Description

The VXI-MXI does not support the following VMEbus modules:

- Serial Clock Driver

- Power Monitor

Table 2-3 indicates the VXI-MXI VMEbus compliance levels.

Table 2-3. VXI-MXI VMEbus Compliance Levels

| <b>Compliance Notation</b>     | Description                                                                         |

|--------------------------------|-------------------------------------------------------------------------------------|

| Bus Slave Compliance Levels    |                                                                                     |

| D08(O)                         | 8-bit data path to configuration registers and MXIbus                               |

| D16 & D08(EO)                  | 8-bit or 16-bit data path to configuration registers or MXIbus                      |

| D32                            | 32-bit data path to MXIbus                                                          |

| A16                            | Responds to 16-bit short I/O addresses when specified on the address modifier lines |

| A24                            | Responds to 24-bit memory addresses when specified on the address modifier lines    |

| A32                            | Responds to 32-bit memory addresses when specified on the address modifier lines    |

| ADO                            | Accommodates address-only cycles                                                    |

| BLT                            | Responds to block mode transfers                                                    |

| RMW                            | Can accept Read-Modify-Write cycles                                                 |

| DTB Arbiter Compliance Level   |                                                                                     |

| PRI                            | Monitors BR3* through BR0* and drives BG3OUT* through BG0OUT* and BCLR*             |

| DTB Requester Compliance Level |                                                                                     |

| ROR                            | Release-on-Request                                                                  |

(continues)

General Description Chapter 2

Table 2-3. VXI-MXI VMEbus Compliance Levels (Continued)

| Compliance Notation                 | Description                                                                                                        |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|

| Bus Master Compliance Levels        |                                                                                                                    |  |

| D08(EO)                             | 8-bit data path from MXIbus                                                                                        |  |

| D16 & D08(EO)                       | 8-bit or 16-bit data path from MXIbus                                                                              |  |

| D32                                 | 32-bit data path from MXIbus                                                                                       |  |

| A16                                 | Generates 16-bit short I/O addresses when specified by the MXIbus address modifier lines                           |  |

| A24                                 | Generates 24-bit memory addresses when specified by the MXIbus address modifier lines                              |  |

| A32                                 | Generates 32-bit memory addresses when specified by the MXIbus address modifier lines                              |  |

| BLT                                 | Generates block mode transfers when specified by the MXIbus address modifier lines                                 |  |

| RMW                                 | Can generate Read-Modify-Write cycles                                                                              |  |

| Interrupter Compliance Levels       |                                                                                                                    |  |

| I(7-1)                              | Can generate an interrupt request on interrupt lines IRQ7 through IRQ1                                             |  |

| D16 & D32                           | Responds to 16-bit and 32-bit interrupt acknowledge cycles by providing a 16-bit Status/ID byte on D00 through D15 |  |

| ROAK                                | Releases its interrupt request line when its Status/ID is read during an interrupt acknowledge cycle               |  |

| Interrupt Handler Compliance Levels | mpliance Levels                                                                                                    |  |

| IH(7-1)                             | Can generate interrupt acknowledge cycles in response to interrupt requests on IRQ7 through IRQ1                   |  |

| D16                                 | Generates a 16-bit interrupt acknowledge cycle in response to a VMEbus interrupt request                           |  |

Chapter 2 General Description

#### **VXI-MXI Functional Description**

In simplest terms, the VXI-MXI can be thought of as a bus translator that converts VXIbus signals into appropriate MXIbus signals. From the perspective of the MXIbus, the VXI-MXI implements a MXIbus interface to communicate with other MXIbus devices. From the perspective of the VMEbus, the VXI-MXI is an interface to the outside world.

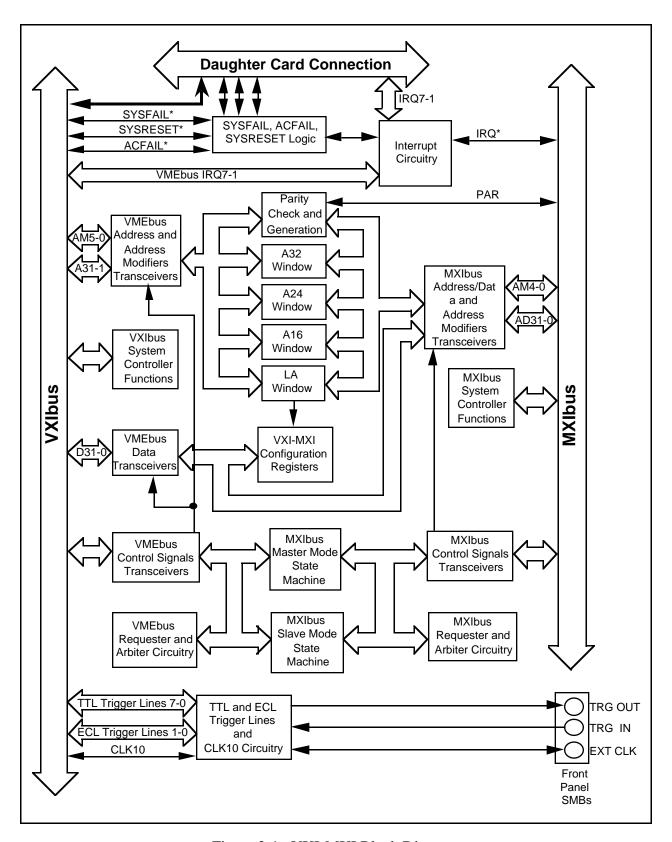

Figure 2-1 is a functional block diagram of the VXI-MXI. Refer to Chapter 6, *Theory of Operation* for more details about the major components of the VXI-MXI.

| • | VMEbus Address and Address Modifiers | These transc |

|---|--------------------------------------|--------------|

|   | Transceivers                         | VMEbus ad    |

These transceivers control the direction of the VMEbus address lines and latch the status of the address lines on the falling edge of the VMEbus address strobe.

• VXIbus System Controller Functions

If the VXI-MXI is selected as the VMEbus System Controller, this circuitry generates the 16 MHz system clock, provides the VMEbus arbiter and the VMEbus Bus Timer Unit, and drives the VXIbus CLK10 signal.

VMEbus Data Transceivers

These transceivers control the direction of the VMEbus data lines and meet VMEbus specifications for timing and signal loading.

VMEbus Control Signals Transceivers

These transceivers control the direction of the VMEbus control signals and meet VMEbus specifications for timing and signal loading.

VMEbus Requester and Arbiter Circuitry

This circuitry is used to request the VMEbus and to provide the VMEbus arbiter function if the VXI-MXI is the VMEbus System Controller.

TTL and ECL Trigger Lines and CLK10 Circuitry This circuitry controls the sending and receiving of the TTL and ECL Trigger lines to and from the SMB connectors on the front panel and from onboard registers. This logic also controls whether the VXI-MXI receives the CLK10 signal from another VXIbus device, or drives the signal from an onboard 10 MHz oscillator or from an external signal connected to the EXT CLK SMB connector on the front panel.

SYSFAIL, ACFAIL, and SYSRESET

Through this circuitry, the VMEbus signals SYSFAIL, ACFAIL and SYSRESET connect to the corresponding signals on the daughter card connections. These three signals can also be individually enabled to generate a VMEbus interrupt. With control bits in onboard registers, SYSFAIL and SYSRESET can also be driven on the VMEbus backplane.

General Description Chapter 2

Figure 2-1. VXI-MXI Block Diagram

Chapter 2 General Description

**Interrupt Circuitry** This circuitry generates and receives interrupt requests on the VMEbus, the MXIbus, and on boards plugged into the daughter card connectors. Interrupt requests routed between VXIbus mainframes can be transparently serviced by interrupt handlers in VXIbus mainframes other than the requester's own mainframe. Parity Check and Generation This circuitry checks and generates MXIbus parity. A32, A24, A16 and LA Windows These address windows assign portions of the MXIbus address space to the VXIbus mainframe and vice versa. VXI-MXI Configuration Registers These registers provide all the configuration information required by the VXI-MXI and are accessible from both the VXIbus and the MXIbus. MXIbus Master Mode State Machine This state machine converts VXIbus cycles mapped out of a MXIbus window to the MXIbus into MXIbus cycles. MXIbus Slave Mode State Machine This state machine converts MXIbus cycles mapped through a MXIbus window into the VXIbus mainframe into VXIbus cycles. MXIbus Address/Data and Address These transceivers and associated circuitry control **Modifiers Transceivers** the direction of the MXIbus address and data lines. When a VXIbus transfer is mapped out to the MXIbus, the VXIbus address/data lines are multiplexed into the MXIbus address/data lines. When a MXIbus transfer is mapped into the VXIbus, the MXIbus address/data lines are demultiplexed into separate VXIbus address and data lines. MXIbus System Controller Functions If the VXI-MXI is the MXIbus System Controller, this circuitry provides the MXIbus arbiter, interrupt daisy-chain generation, and the MXIbus System Controller timeout logic. MXIbus Control Signals Transceivers These transceivers control the direction of the MXIbus control signals. This circuitry is used to request the MXIbus when MXIbus Requester and Arbiter Circuitry a VXIbus transfer is mapped into a MXIbus window. **Daughter Card Connection** The two daughter card connectors can be used to add additional functionality to the VXI-MXI in the form of plug-in daughter cards.

General Description Chapter 2

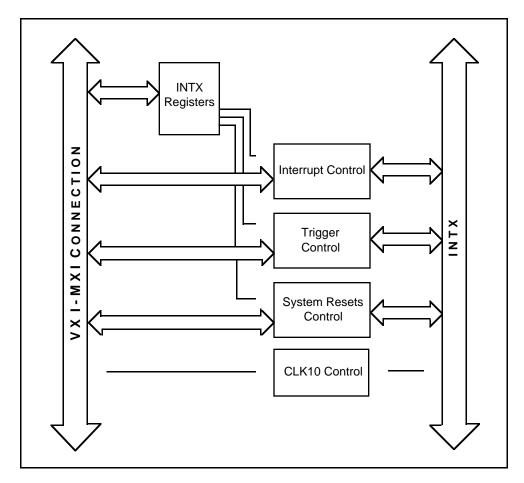

The following information applies only to VXI-MXI kits that include the INTX daughter card option. Figure 2-2 is a block diagram of the circuitry of the INTX daughter card.

Figure 2-2. VXI-MXI INTX Daughter Card Option Block Diagram

INTX Registers

The INTX card has three onboard registers that reside in the VXI-MXI configuration space: the INTX Interrupt Configuration Register, the INTX Trigger Configuration Register, and the INTX Utility Configuration Register. These registers configure the mapping of the VMEbus interrupt lines, the VXIbus trigger lines and the SYSRESET, SYSFAIL, and ACFAIL lines to and from the INTX connector. The INTX card also drives the Extended Device Type Class field in the VXIbus Status/Control Register when that register is accessed on the VXI-MXI.

Chapter 2 General Description

• Interrupt Control

The interrupt control logic maps the VMEbus interrupt lines to and from the corresponding INTX interrupt lines. In conjunction with the VXI-MXI circuitry, the interrupt requests routed between VXIbus mainframes through the INTX connector can be transparently serviced by interrupt handlers in VXIbus mainframes other than the mainframe from which the request was generated. This process takes advantage of transparent MXIbus interrupt acknowledge cycles.

When an interrupt request received from across the INTX is driven on the corresponding VMEbus interrupt line, an interrupt handler in the receiving VXIbus mainframe generates an interrupt acknowledge cycle for that interrupt request. This interrupt acknowledge cycle is transparently converted into a MXIbus interrupt acknowledge cycle for that interrupt request level. Similarly, when a VMEbus interrupt line is driven out of the VXIbus mainframe across the INTX connection, an interrupt handler in another VXIbus mainframe can generate an interrupt acknowledge cycle to handle that interrupt. The VXI-MXI in the requesting mainframe recognizes that the MXIbus interrupt acknowledge cycle is for the request it is driving and converts the cycle into a VMEbus interrupt acknowledge cycle that can service the VMEbus interrupt requester.

The trigger control logic maps the VXIbus TTL trigger lines to and from the corresponding INTX trigger lines.

The system resets control circuitry maps the VMEbus signals SYSRESET, SYSFAIL, and ACFAIL to the corresponding signals on the INTX connection.

The CLK10 control circuitry routes the VMEbus 10 MHz signal to and from the INTX connection. The configuration of the CLK10 mapping is controlled by three switches on the INTX daughter card. Refer to the *INTX CLK10 Mapping* section of Chapter 3, *Configuration and Installation*, for instructions on configuring these switches.

- Trigger Control

- System Resets Control

- CLK10 Control

## **Chapter 3 Configuration and Installation**

This chapter describes the configuration and installation of the VXI-MXI.

#### **Configuring the VXI-MXI**

Before installing the VXI-MXI in the VXIbus mainframe, configure the VXI-MXI to suit the needs for your VXIbus system. The VXI-MXI module contains jumpers, switches, and slide switches that you can use to configure the following options:

- VXIbus Slot 0

- VXIbus Logical Address

- VMEbus Request Level

- VMEbus Timeout Value

- VMEbus Timeout Chain Position

- Interlocked Arbitration Mode

- MXIbus System Controller

- MXIbus System Controller Timeout

- MXIbus Fairness Option

- CLK10 Source

- EXT CLK SMB Input/Output

- Trigger Input Termination

- Reset Signal Select

If your VXI-MXI module includes the INTX daughter card option, you can also configure the following option:

CLK10 Mapping

Figure 3-1. VXI-MXI Parts Locator Diagram

Figure 3-2. VXI-MXI with INTX Parts Locator Diagram

#### The Metal Enclosure

The VXI-MXI is housed in a metal enclosure to improve EMC performance and to provide easy handling. Because the enclosure includes cut-outs to facilitate changes to switch and jumper settings, it should not be necessary to remove it under normal circumstances.

Should you find it necessary to open the enclosure, remove the three screws on the top, the three screws on the bottom, and the three screws on the right side panel of the enclosure.

#### **VXIbus Slot 0**

The VXI-MXI is shipped from the factory configured to be installed in Slot 0 of the VXIbus mainframe. If another device is already in Slot 0, you must decide which device will be the Slot 0 device and reconfigure the other device for Non-Slot 0 use.

Warning: Do not install a device configured for Slot 0 into another slot without first reconfiguring it for Non-Slot 0 use. Doing so could result in damage to the Non-Slot 0 device, the VXIbus backplane, or both.

Figure 3-3 shows the default configuration settings for the VXI-MXI installed as the Slot 0 device. The position of slide switches S1 and S8 must match. For Slot 0 configuration, they must both be in the ON position. In addition to S1 and S8, jumper block W7 and jumper blocks W9 and W10 must be set for Slot 0 configuration. Refer to the *VMEbus Timeout Chain Position* section and the *CLK10 Source* section later in this chapter to examine the options for these jumper blocks.

Figure 3-3. VXIbus Slot 0 Selection

When the VXI-MXI is installed in Slot 0, it becomes the VMEbus System Controller, meaning that it has VMEbus Data Transfer Bus Arbiter capability (PRI ARBITER) and that it drives the 16 MHz VMEbus system clock. The VMEbus Data Transfer Bus Arbiter circuitry accepts bus requests on all four VMEbus request levels, prioritizes the requests, and grants the bus to the highest priority requester. The VMEbus system clock is driven by an onboard 16 MHz oscillator with a 50% ±5% duty cycle.

The VXIbus specification defines several additional functions for devices installed in the Slot 0 position. A Slot 0 device must implement a 16-bit MODID register to control and monitor the VXIbus MODID lines. Slot 0 cards must also have 16.9 k pull-up resistors on each VXIbus MODID line. If the card is not in Slot 0, the MODID0 line on that card must be pulled down to ground with an 825 resistor.

The VXIbus Resource Manager (RM) identifies whether the VXI-MXI is configured as a Slot 0 device by reading the VXIbus Model Code in the Device Type Register. If the VXIbus Model Code for the VXI-MXI is hex 00FE, the module is configured as a Slot 0 device; if the code is hex 08FE, the module is configured as a Non-Slot 0 device.

To configure the VXI-MXI as a Non-Slot 0 device, change slide switches S1 and S8 to the OFF positions as depicted in Figure 3-4. Remember to also change the settings of jumper block W7 and jumper blocks W9 and W10 as described later in this chapter.

Figure 3-4. VXIbus Non-Slot 0 Selection

#### **VXIbus Logical Address**

Each device in a VXIbus/MXIbus system is assigned a unique number between 0 and 254. This 8-bit number, called the *logical address*, defines the base address for the configuration registers located on the device. With unique logical addresses, each VXIbus device in the system is assigned 64 bytes of configuration space in the upper 16 KB of A16 space.

Some VXIbus devices have dynamically configurable logical addresses. These devices have an initial logical address of hex FF, which indicates that they can be dynamically configured. While the VXI-MXI does support dynamic configuration of VXIbus devices within its mainframe, it cannot itself be dynamically configured. Therefore, do not set the logical address for the VXI-MXI to hex FF.

The VXIbus RM has Logical Address 0 by definition. The VXI-MXI does not have VXIbus RM capability, so do not set the logical address for the VXI-MXI to 0. If you are configuring a multiple-mainframe VXIbus/MXIbus system, refer to Chapter 5, *Programming Considerations*, for instructions on planning a VXIbus/MXIbus system logical address map. If you are connecting only a PC with a MXIbus interface to the VXI-MXI, you should leave the logical address at the default setting of 1. Using this setting, you can install devices with all other possible logical addresses in the VXIbus mainframe.

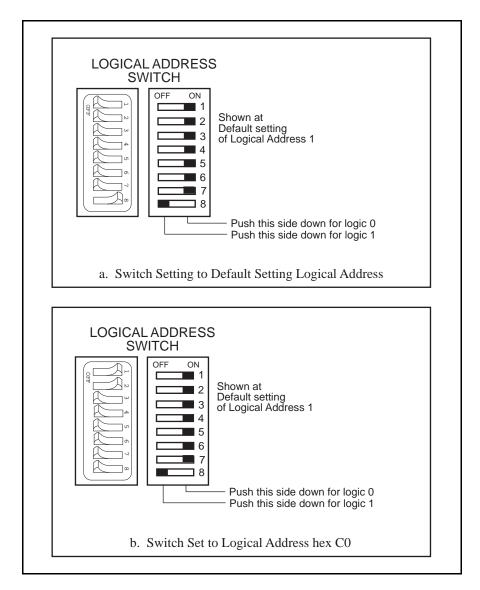

An 8-bit DIP switch selects the logical address for the VXI-MXI. As shown in Figure 3-1, this switch is labeled *LOGICAL ADDRESS SWITCH* on the front panel. The ON position on the DIP switch corresponds to a logic value of 0, and the OFF position corresponds to a logic value of 1. This switch is set at the factory to a default logical address of 1. Verify that the logical address assigned to the VXI-MXI is not used by any other statically configured VXIbus device in your system. Remember that logical addresses hex 0 and FF are not allowed for the VXI-MXI.

Figure 3-5 shows switch settings for logical address hex 1 and C0.

Figure 3-5. Logical Address Selection

#### **VMEbus Request Level**

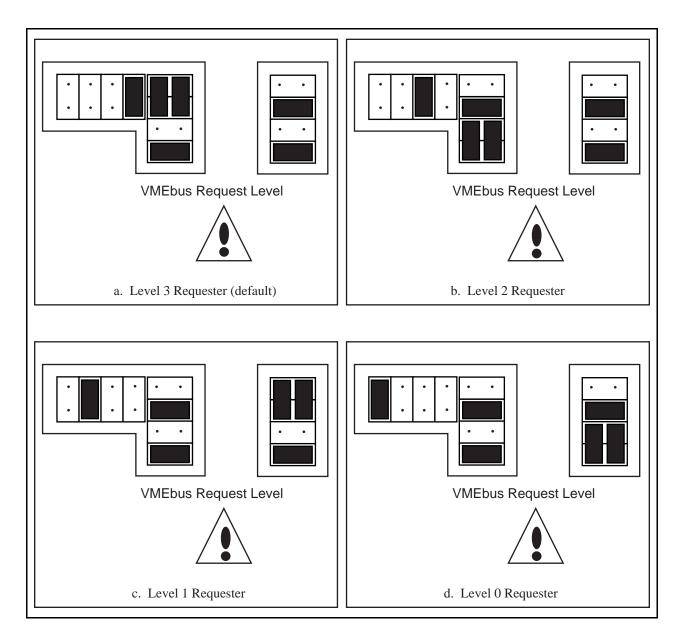

The VXI-MXI uses one of the four VMEbus request levels to request use of the VMEbus Data Transfer Bus (DTB). The VXI-MXI requests use of the DTB whenever an external MXIbus device attempts a transfer that maps into the VXIbus mainframe.

The VXI-MXI is shipped from the factory configured to use VMEbus request level 3, as required in the VXIbus specification. Request level 3 is the highest priority request level and request level 0 is the lowest. You can change the VXI-MXI to use any of the other three request levels by changing the jumper configuration on the jumper blocks labeled *VMEbus Request Level* on the front panel. You may want to change request levels to change the priority of the VXI-MXI request signal. For more information, refer to the VMEbus specification.

To change the VMEbus request level of the VXI-MXI, rearrange the jumpers on the pin arrays as shown in Figure 3-6.

Figure 3-6. VMEbus Requester Jumper Settings

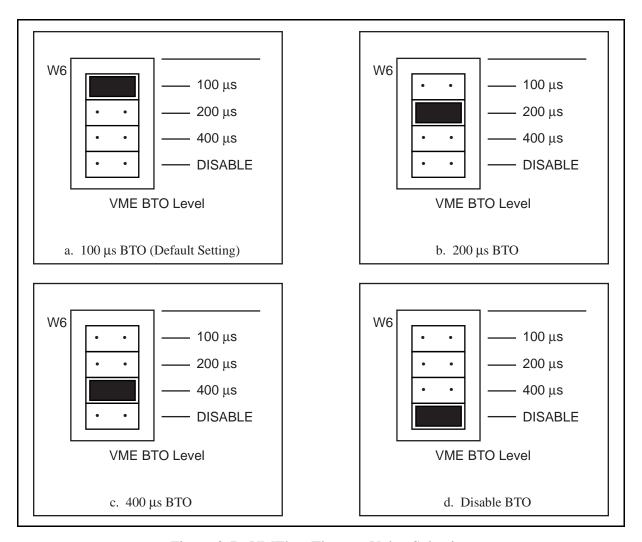

#### **VMEbus Timeout Value**

When a VXI-MXI is installed in a VXIbus mainframe, the VME Bus Timeout Unit (BTO) circuitry for the VXIbus mainframe must be on the VXI-MXI. If there are multiple VXI-MXI interfaces in a mainframe, the BTO must be enabled on one of them and they must be in adjacent slots. In the case of multiple VXI-MXIs, it is recommended that the BTO be enabled on the VXI-MXI that is installed in Slot 0. The BTO monitors the current bus cycle and asserts the bus error (BERR) signal if a data transfer acknowledge (DTACK) or BERR is not received from the selected slave within the given amount of time after data strobe (DS1 or DS0) becomes active. Whenever a MXIbus transfer into or out of the VXI-MXI occurs, the VMEbus timeout on the VXI-MXI is disabled and the MXIbus System Controller BTO monitors the transfer. This

configuration allows VXIbus transfers to have short bus timeout values and MXIbus transfers to have much longer timeout values.

You can either disable the VMEbus timeout value or set it to 100, 200, or 400 µs by moving the *VME BTO Level* jumper, as shown in Figure 3-7. The VMEbus timeout is disabled when a VMEbus cycle maps out of the mainframe, initiating a MXIbus cycle. The configuration of the *VME BTO Chain Position* jumper block selects how the VXIbus local bus is used to disable the VMEbus timeout when outward MXIbus transfers occur. If another device has a BTO module, remember to enable the BTO on the VXI-MXI and to disable the VMEbus BTO on the other device.

Figure 3-7. VMEbus Timeout Value Selection

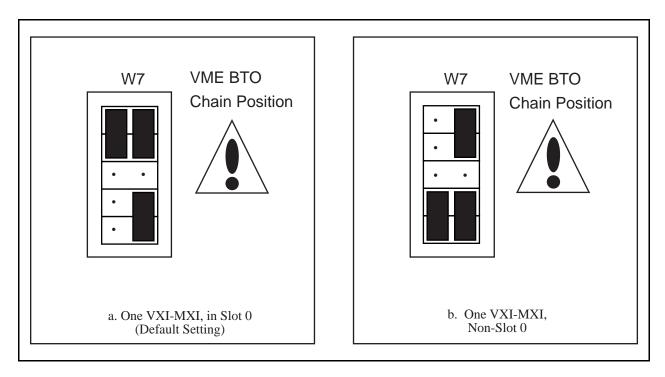

### **VMEbus Timeout Chain Position**

The VME BTO Chain Position jumper block indicates the location of the VXI-MXI interface in relation to other VXI-MXIs installed in the mainframe. If only one VXI-MXI is in the system, set the jumper block to one of the configurations shown in Figure 3-8.

Figure 3-8. VMEbus Timeout; One VXI-MXI in Mainframe

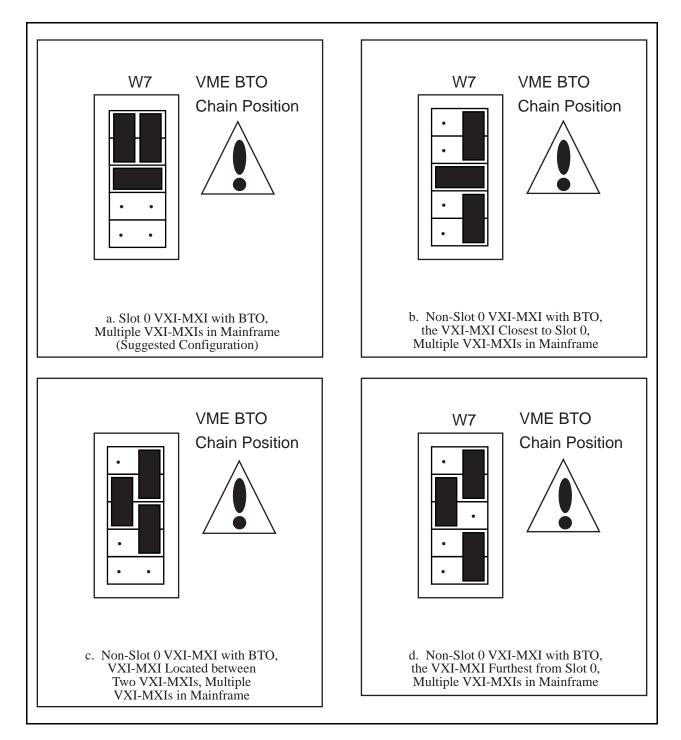

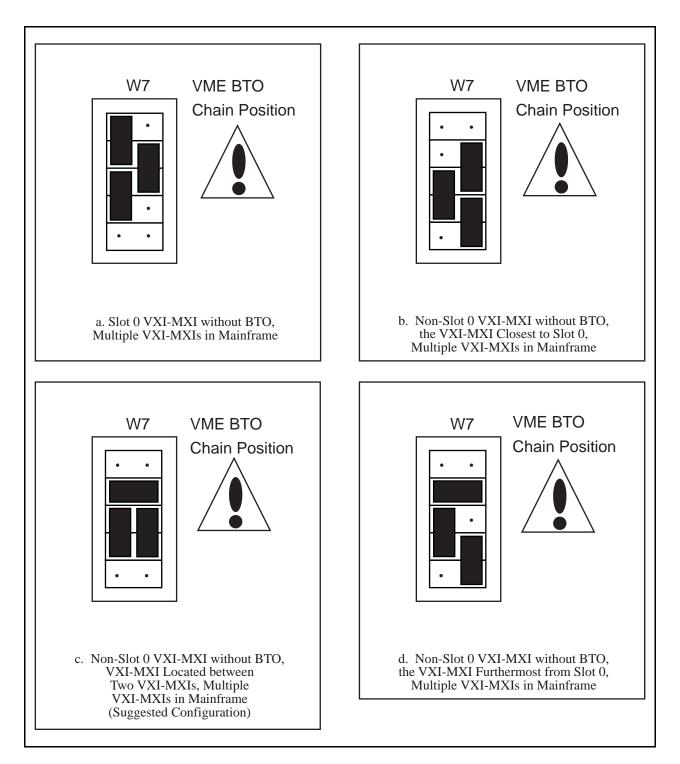

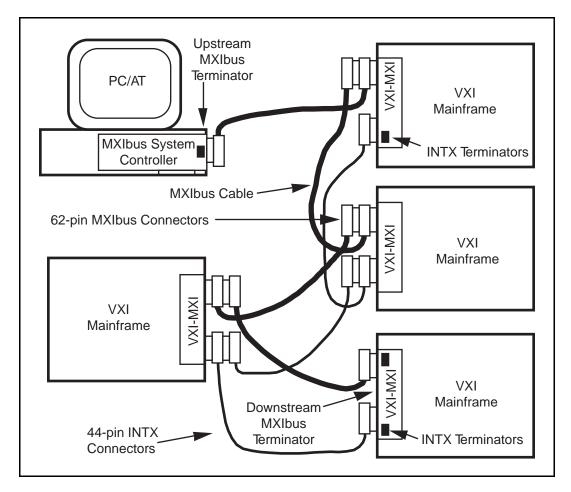

When you have multiple VXI-MXI modules installed in adjacent slots, the VXIbus local bus is used to send a signal to the VXI-MXI with the VMEbus BTO to indicate that an outward MXIbus transfer is in progress. The following figures show how to configure the *VME BTO Chain Position* jumper block to select how the VXIbus local bus is used to disable the VMEbus timeout during outward MXIbus transfers.

If the system contains more than one VXI-MXI, select which card will supply the VMEbus timeout, and set the jumper block according to the VXI-MXI's position in relation to the adjacent VXI-MXIs. Figure 3-9 shows four possible settings.

Figure 3-9. VMEbus Timeout; Multiple VXI-MXIs in Mainframe

For the VXI-MXIs that do not supply the VMEbus timeout, set the *VME BTO Chain Position* jumper block to reflect each VXI-MXI's position in relation to the adjacent VXI-MXIs. See Figure 3-10.

Figure 3-10. No VMEbus Timeout; Multiple VXI-MXIs in Mainframe

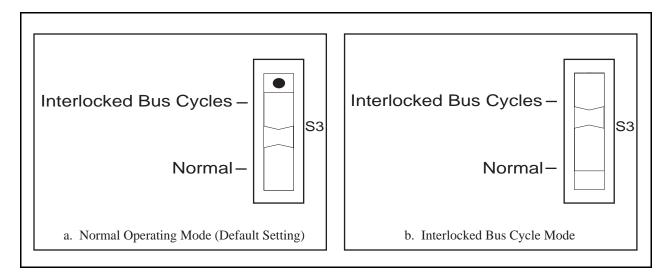

### **Interlocked Arbitration Mode**

Interlocked arbitration mode is an optional mode of operation in which the system performs as one large VXIbus mainframe with only one master of the entire system (VXIbus and MXIbus) at any given moment. This mode of operation prevents deadlocks by interlocking all arbitration in the VXIbus/MXIbus system. Refer to Chapter 6 for a thorough discussion of interlocked arbitration mode.

In the normal operating mode, there can be multiple masters operating simultaneously in the VXIbus/MXIbus system. A deadlock occurs when a MXIbus master requests use of a VXIbus resource in another VXIbus mainframe while a VXIbus master in that mainframe is in the process of requesting a resource across the MXIbus. When this situation occurs, the VXIbus master must give up its bus ownership to resolve the conflict. The BERR signal is used to terminate the transfer on the VMEbus; however, devices in the VXIbus mainframe must be able to detect a BERR caused by a deadlock condition so that they can retry the operation.

The VXI-MXI is shipped from the factory configured for normal operating mode. If MXIbus transfers will be occurring both into and out of the mainframe and the VXIbus modules in your system do not have the capability for handling BERR exceptions caused by deadlock conditions, you may want to configure the VXI-MXI for interlocked arbitration mode. In this mode, no changes will need to be made to software. However, parallel processing in separate VXIbus mainframes is no longer possible, and system performance may be lower than in normal operating mode.

VMEbus requesters are awarded the bus when they receive an active signal on the daisy-chained bus grant line. Requesters closest to the Slot 0 device have higher priority, therefore, than devices installed in slots farther from Slot 0. In addition, four bus request levels further prioritize modules. For proper operation in interlocked arbitration mode, all VXI-MXIs should be configured to request at bus request level 3, the factory default setting. In addition, only one mainframe can have a requester at a higher priority than the VXI-MXIs in that mainframe. This requester may be a Slot 0 device other than a VXI-MXI, such as a multiframe Resource Manager. In all the other mainframes, the VXI-MXIs must be the highest priority requesters. This means that a VXI-MXI should be installed in Slot 0 of its respective mainframe. In the case of multiple VXI-MXIs in a single mainframe, the additional VXI-MXIs should be installed in the slots adjacent to the Slot 0 VXI-MXI.

Note: Interlocked arbitration mode has a potential for long access times. Therefore, you should configure bus timeouts for adequate times.

In a VXIbus/MXIbus system, you can configure some VXI-MXIs for normal operating mode and others for interlocked arbitration mode. The VXIbus mainframes configured in interlocked arbitration mode will be interlocked with each other and the mainframes configured for normal operating mode can perform transfers in parallel. This type of system configuration is recommended if you have one of the following situations:

- A VXIbus mainframe with only slave devices and no masters. Without bus masters, there is no chance for deadlock. The VXI-MXIs in this mainframe can be configured for normal operating mode.

- A VXIbus mainframe with both masters and slaves, but the masters communicate only with the slaves in their mainframe. The masters never attempt transfers across the MXIbus so there is no chance for deadlock when a MXIbus master attempts a transfer into the VXI mainframe. The VXI-MXIs in this mainframe can be configured for normal operating mode.

Select interlocked arbitration mode by changing the default setting of the slide switch from *Normal* to *Interlocked Bus Cycles* as shown in Figure 3-11.

Figure 3-11. Interlocked Arbitration Mode Selection

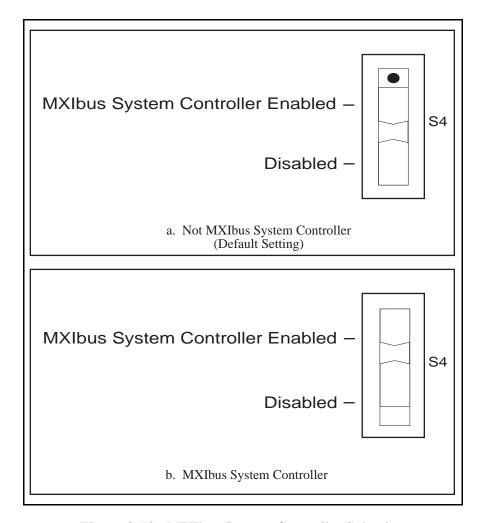

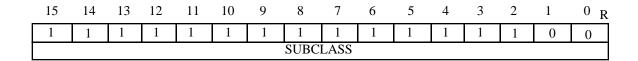

## **MXIbus System Controller**