TMS320C6201 Digital Signal Processor Silicon Errata

> SPRZ153 November 2000

Copyright © 2000, Texas Instruments Incorporated

Download from Www.Somanuals.com. All Manuals Search And Download.

# Contents

| 1 | Introduction    |                                                                            | 4   |

|---|-----------------|----------------------------------------------------------------------------|-----|

| • |                 | Reliability Conditions                                                     |     |

|   | •               |                                                                            |     |

|   |                 | ition                                                                      |     |

|   | TMS Defin       | ition                                                                      | 4   |

|   | 1.2 Revision lo | lentification                                                              | 5   |

| 2 | Changes to the  | TMS320C6201 Data Sheet (literature number SPRS051)                         | 6   |

| 3 | Silicon Revisio | n 3.1 Known Design Exceptions to Functional Specifications                 | . 8 |

|   | Advisory 3.1.1  | Issues When Pausing at a Block Boundary                                    | . 8 |

|   | Advisory 3.1.2  | DMA: Transfer Incomplete When Pausing a Synchronized Transfer in Mid-frame | . 8 |

|   | Advisory 3.1.3  | DMA Multiframe Split-mode Transfers Source Address Indexing Not Functional | 9   |

|   | Advisory 3.1.4  | DMA: Stopped Transfer Reprogrammed Does Not Wait for Sync                  | 9   |

|   | Advisory 3.1.5  | DMA Freezes if Postincrement/Decrement Across Port Boundary                | 9   |

|   | Advisory 3.1.6  | DMA Paused During Emulation Halt                                           | 10  |

|   | Advisory 3.1.7  | DMA: RSYNC = 10000b (DSPINT) Does Not Wait for Sync                        | 10  |

|   | Advisory 3.1.8  | EMIF: Invalid SDRAM Access to Last 1K Byte of CE3                          | 10  |

|   | Advisory 3.1.9  | Cache During Emulation With Extremely Slow External Memory                 | 11  |

| 4 | Silicon Revisio | n 3.0 Known Design Exceptions to Functional Specifications                 | 12  |

|   | Advisory 3.0.8  | EMIF: Inverted SDCLK and SSCLK at Speeds Above 175 MHz                     | 12  |

|   | Advisory 3.0.9  | CPU: L2-unit Long Instructions Corrupted During Interrupt                  | 14  |

| 5 | Silicon Revisio | n 2.1 Known Design Exceptions to Functional Specifications                 | 15  |

|   | Advisory 2.1.1  | EMIF: CE Space Crossing on Continuous Request Not Allowed                  | 15  |

|   | Advisory 2.1.2  | EMIF: SDRAM Invalid Access                                                 | 15  |

|   | Advisory 2.1.4  | DMA: RSYNC Cleared Late for Frame-synchronized Transfer                    | 16  |

|   | Advisory 2.1.5  | McBSP: DXR to XSR Copy Not Generated                                       | 16  |

|   | Advisory 2.1.6  | DMA Split-mode End-of-frame Indexing                                       | 18  |

|   | Advisory 2.1.7  | DMA Channel 0 Multiframe Split-Mode Incompletion                           | 19  |

|   | Advisory 2.1.8  | Timer Clock Output Not Driven for External Clock                           | 19  |

|   | Advisory 2.1.9  | Power-Down Pin PD Not Set High for Power-Down 2 Mode                       | 19  |

|   | Advisory 2.1.10 | EMIF: RBTR8 Bit Not Functional                                             | 19  |

|   | Advisory 2.1.11 | McBSP: Incorrect mLaw Companding Value                                     | 20  |

|   | Advisory 2.1.12 | False Cache Hit – Extremely Rare                                           | 20  |

|   | Advisory 2.1.13 | EMIF: HOLD Feature Improvement on Revision 3                               | 20  |

|   | Advisory 2.1.14 | EMIF: HOLD Request Causes Problems With SDRAM Refresh                      | 21  |

|   | Advisory 2.1.15 | DMA Priority Ignored by PBUS                                               | 21  |

|   | Advisory 2.1.16 | DMA Split-mode Receive Transfer Incomplete After Pause                     | 22  |

|   | Advisory 2.1.17 | DMA Multiframe Transfer Data Lost During Stop                              | 22  |

|   | Advisory 2.1.18 | Bootload: HPI Feature Improvement on Revision 3                            | 22  |

|   |                 |                                                                            |     |

|   | Advisory 2.1.19 | PMEMC: Branch from External to Internal                                                         | 23 |

|---|-----------------|-------------------------------------------------------------------------------------------------|----|

|   | •               | DMA: DMA Data Block Corrupted After Start Zero Transfer Count                                   |    |

|   | -               |                                                                                                 |    |

| 6 | Silicon Revisio | n 2.0 Known Design Exceptions to Functional Specifications                                      |    |

|   | Advisory 2.0.1  | Program Fetch: Cache Modes Not Functional                                                       | 24 |

|   | Advisory 2.0.2  | Bootload: Boot from 16-Bit and 32-Bit Asynchronous ROMs Not Functional                          | 24 |

|   | Advisory 2.0.3  | DMA Channel 0 Split Mode Combined With autoinitialization Performs Improper<br>Reinitialization | 24 |

|   | Advisory 2.0.4  | DMA/Program Fetch: Cannot DMA into Program Memory From External                                 | 24 |

|   | Advisory 2.0.5  | Data Access: Parallel Accesses to EMIF or Internal Peripheral Bus Location                      |    |

|   |                 | Sequenced Wrong                                                                                 | 25 |

|   | Advisory 2.0.7  | EMIF: Reserved Fields Have Incorrect Values                                                     | 25 |

|   | Advisory 2.0.8  | EMIF: SDRAM Refresh/DCAB Not Performed Prior to HOLD Request Being Granted                      | 25 |

|   | Advisory 2.0.9  | McBSP New Block Interrupt Does Not Occur for Start of Block 0                                   | 26 |

|   | Advisory 2.0.11 | DMA/Internal Data Memory: First Load Data Corrupted When DMA in High Priority                   | 26 |

|   | Advisory 2.0.12 | McBSP: FRST Improved in 2.1 over 2.0                                                            | 26 |

|   | Advisory 2.0.13 | McBSP: XEMPTY Stays Low When DXR Written Late                                                   | 27 |

|   | Advisory 2.0.14 | EMIF: Multiple SDRAM CE Spaces: Invalid Access After Refresh                                    | 27 |

|   | Advisory 2.0.18 | DMA/Internal Data Memory: Conflict Data Corruption                                              | 27 |

|   | Advisory 2.0.19 | EMIF: Data Setup Times                                                                          | 28 |

|   | Advisory 2.0.24 | EMIF Extremely Rare Cases Cause an Improper Refresh Cycle to Occur                              | 28 |

| 7 | Documentation   | Support                                                                                         | 28 |

## 1 Introduction

This document describes the silicon updates to the functional specifications for the TMS320C6201 silicon releases 3.1, 3.0, 2.1, and 2.0.

## 1.1 Quality and Reliability Conditions

## **TMX** Definition

Texas Instruments (TI) does not warranty either (1) electrical performance to specification, or (2) product reliability for products classified as "TMX." By definition, the product has not completed data sheet verification or reliability performance qualification according to TI Quality Systems Specifications.

The mere fact that a "TMX" device was tested over a particular temperature and voltage ranges should not, in any way, be construed as a warranty of performance.

## **TMP Definition**

TI does not warranty product reliability for products classified as "TMP." By definition, the product has not completed reliability performance qualification according to TI Quality Systems Specifications; however, products are tested to a published electrical and mechanical specification.

## **TMS** Definition

Fully-qualified production device.

## 1.2 Revision Identification

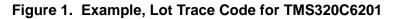

The device revision can be determined by the lot trace code marked on the top of the package. The location for the lot trace codes for the GJL package is shown in Figure 1 and the revision numbers are listed in Table 1.

NOTE: Qualified devices are marked with the letters "TMS" at the beginning of the device name, while nonqualified devices are marked with the letters "TMX" at the beginning of the device name.

|  | Table 1. | Lot Trace Nu | mber Names |

|--|----------|--------------|------------|

|--|----------|--------------|------------|

| Lot Trace Code | Silicon Revision | Comments |

|----------------|------------------|----------|

| 20             | 2.0              |          |

| 21             | 2.1              |          |

| 30             | 3.0              |          |

| 31             | 3.1              |          |

ED [31:0] ,

SSADS -

SSOE -

## 2 Changes to the TMS320C6201 Data Sheet (literature number SPRS051)

## Table 2. Timing Requirements for Interrupt Response Cycles

| NO. |                             |                                          | C62 | 01B |      |

|-----|-----------------------------|------------------------------------------|-----|-----|------|

| NO. |                             |                                          |     |     | UNIT |

| 4   | td(CKO2L-IACKV)             | Delay time, CLKOUT2 low to IACK valid    | -4  | 6   | ns   |

| 5   | <sup>t</sup> d(CKO2L-INUMV) | Delay time, CLKOUT2 low to INUMx valid   |     | 6   | ns   |

| 6   | td(CKO2L-INUMIV)            | Delay time, CLKOUT2 low to INUMx invalid | -4  |     | ns   |

## Table 3. JTAG Test-Port Timing

| NO. |                     |                                              | C62<br>C62 | ,   | UNIT |

|-----|---------------------|----------------------------------------------|------------|-----|------|

|     |                     |                                              | MIN        | MAX |      |

| 1   | T <sub>c(TCK)</sub> | Cycle time, TCK                              | 50         |     | ns   |

| 4   | Th(TCKH-TDIV)       | Hold time, TDI/TMS/TRST valid after TCK high | 9          |     | ns   |

7

03

$\Omega^2$

▶ 10

$\Omega_4$

▶ 12

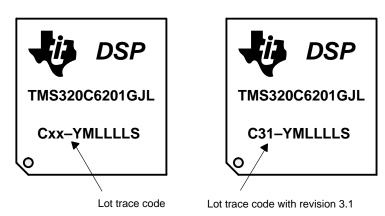

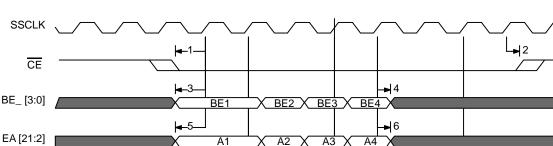

## Figure 2. SBSRAM Read Timing (1/2 Rate SSCLK) (See Note)

NOTE: The CEx output setup and hold times are specified to be accurate relative to the clock cycle to which they are referenced, since these timings are specified as minimums. However, the CE output setup and hold time may be greater than that shown in the data sheet in multiples of P ns. In other words, for output setup time, the CEx transition from high to low may happen P, 2P, ..., or nP ns before the time specified by the data sheet. Similarly, for output hold time, the CEx low-to-high transition may happen P, 2P, ..., or nP ns after the time specified by the data sheet. This is indicated by the period of uncertainty for specs 1 and 2 in Figure 2, and Figure 3.

**4**\_9

**I4**-11-

NOTE: The CEx output setup and hold times are specified to be accurate relative to the clock cycle to which they are referenced, since these timings are specified as minimums. However, the CE output setup and hold time may be greater than that shown in the data sheet in multiples of P ns. In other words, for output setup time, the CEx transition from high to low may happen P, 2P, ..., or nP ns before the time specified by the data sheet. Similarly, for output hold time, the CEx low-to-high transition may happen P, 2P, ..., or nP ns after the time specified by the data sheet. This is indicated by the period of uncertainty for specs 1 and 2 in Figure 2, and Figure 3.

## 3 Silicon Revision 3.1 Known Design Exceptions to Functional Specifications

| Advisory 3.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                      | Issues When Pausing at a Block Boundary                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.1, 3.0, 2.1, and 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Details:                                                                                                                                                                                                                                                                                                                                                                                                                                            | The following problems exist when a DMA channel is paused at a block boundary:                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • DMA does not flush internal FIFO when a channel is paused across block boundary.<br>As a result, data from old and new blocks of that channel are in FIFO simultaneously.<br>This prevents other channels from using the FIFO for high performance until that<br>channel is restarted. Data is not lost when that channel is started again. (Internal<br>reference number C601299)                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • For DMA transfers with autoinitialization, if a channel is paused just as the last transfer in a block completes (just as the transfer counter reaches zero), none of the register reloads take place (count, source address, and destination address). When the same channel is restarted, the channel will not transfer anything due to the zero transfer count. This problem only occurs at block boundaries. (Internal reference number C601258) |

| Workaround:                                                                                                                                                                                                                                                                                                                                                                                                                                         | Do not pause across block boundary if the internal FIFO is to be used by other channels for high performance. For DMA transfers with autoinitialization, if a channel is paused with a zero transfer count, manually reload all registers before restarting the channel.                                                                                                                                                                               |

| Advisory 3.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                      | DMA: Transfer Incomplete When Pausing a Synchronized Transfer in Mid-frame                                                                                                                                                                                                                                                                                                                                                                             |

| Revision(s) Affected:                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.1, 3.0, 2.1, and 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>Details</b> : If a frame-synchronized transfer is paused in mid-frame and then restarted again, a channel does not continue the transfer. Instead, the channel waits for synchronizat channel is manually synchronized, it will properly complete the frame, but will imme the transfer of the next frame. This behavior occurs for both a software pause (set 10b) and for an emulation halt (with EMOD = 1). (Internal reference number C6012) |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Workaround:                                                                                                                                                                                                                                                                                                                                                                                                                                         | If pausing the DMA channel in software, do the following to restart:                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1. Set the RSYNC bit in the Secondary Control Register.                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ol> <li>Read the Transfer Count Register and then write back to Transfer Count Register. This<br/>enables the present frame to transfer but will wait for the next sync event to trigger the<br/>next frame transfer.</li> </ol>                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3. Set START to 01b or 11b.                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | If pausing the DMA channel with an emulation halt, do the following to restart:                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1. Double-click on the Transfer Count Register and hit enter (rewrite current transfer count).                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ol> <li>Set the RSYNC STAT bit in the Secondary Control Register (change 0xXXXX4XXX to<br/>0xXXX1XXX).</li> </ol>                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>3</b> . Run.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NOTE: The sequence of 1 and 2 is critical for an emulator halt (EMOD = 1), but not for the software pause.                                                                                                                                                                                                                                                                                                                                             |

| Advisory 3.1.3                                                                                                                                                                                                                                                                                                                                                                                                            | DMA Multiframe Split-mode Transfers Source Address Indexing Not Functional                                                                                                                                                                                                                                                                                                                                                          |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s) Affected:                                                                                                                                                                                                                                                                                                                                                                                                     | 3.1, 3.0, 2.1, and 2.0                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| <b>Details</b> : If a DMA channel is configured to do a multiframe split-mode transfer with SRC_DIR (11b), the source address is always modified using the Element Index, even during the element transfer of a frame. The transfer of the last element in a frame should index source address using the Frame Index instead of the Element Index. DST_DIR = 11th functions properly. (Internal reference number C601256) |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Workaround:                                                                                                                                                                                                                                                                                                                                                                                                               | For multiframe transfers, use two DMA channels instead of using the split mode. Source Index works properly for non-split-mode transfers.                                                                                                                                                                                                                                                                                           |  |

| Advisory 3.1.4                                                                                                                                                                                                                                                                                                                                                                                                            | DMA: Stopped Transfer Reprogrammed Does Not Wait for Sync                                                                                                                                                                                                                                                                                                                                                                           |  |

| Revision(s) Affected:                                                                                                                                                                                                                                                                                                                                                                                                     | 3.1, 3.0, 2.1, and 2.0                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Details:                                                                                                                                                                                                                                                                                                                                                                                                                  | If any non-synchronized transfer (e.g., auto-init transfer) is stopped, and then the same channel is programmed to do a write-synchronized transfer (e.g., split-mode transfer), the write transfer does not wait for the sync event. (Internal reference number C601261)                                                                                                                                                           |  |

| Workaround:                                                                                                                                                                                                                                                                                                                                                                                                               | Perform a nonsynchronized dummy transfer of one element to/from the same location before starting the synchronized transfer.                                                                                                                                                                                                                                                                                                        |  |

| Advisory 3.1.5                                                                                                                                                                                                                                                                                                                                                                                                            | DMA Freezes if Postincrement/Decrement Across Port Boundary                                                                                                                                                                                                                                                                                                                                                                         |  |

| Revision(s) Affected:                                                                                                                                                                                                                                                                                                                                                                                                     | 3.1, 3.0, 2.1, and 2.0                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Details:                                                                                                                                                                                                                                                                                                                                                                                                                  | For any DMA transfers with source/destination address postincrement/decrement, if the last<br>element to be transferred is aligned on a port boundary, then the DMA may freeze before<br>transferring this element. A port boundary is the address boundary between external memory<br>and program memory, between external memory and the peripheral address space, or<br>between program memory and the peripheral address space. |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                           | The following conditions cause DMA to freeze:                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                           | • For non-sync and frame-sync transfers: if a channel is paused after the second-to-last element is read, the DMA will freeze when the channel is then restarted with a request to the address at a port boundary.                                                                                                                                                                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                           | • For split-mode transfers or read/write-sync transfers: the DMA will freeze while transferring the element aligned on the port boundary. A continuous burst transfer with post-increment/decrement source/destination address does not exhibit this problem. (Internal reference number C601300)                                                                                                                                   |  |

| Workaround:                                                                                                                                                                                                                                                                                                                                                                                                               | Do not transfer to boundary addresses if the DMA source/destination address is<br>post-incremented/<br>decremented.                                                                                                                                                                                                                                                                                                                 |  |

| Advisory 3.1.6        | DMA Paused During Emulation Halt                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 3.1, 3.0, 2.1, and 2.0                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Details:              | When running an autoinitialized transfer, the DMA write state machine is halted during an emulation halt regardless of the value of EMOD in the DMA Channel Primary Control Register. The read state machine functions properly in this case. The problem exists only at block boundaries. If EMOD = 1, this problem is irrelevant since the DMA channel is expected to pause during an emulation halt. (Internal reference number C601301) |

| Workaround:           | There is no workaround for EMOD = 0. Expect DMA transfers to pause when the emulator stops the processor.                                                                                                                                                                                                                                                                                                                                   |

| Advisory 3.1.7        | DMA: RSYNC = 10000b (DSPINT) Does Not Wait for Sync                                                                                                                                                                                                                                                                                                                                                                                         |

| Revision(s) Affected: | 3.1, 3.0, 2.1, and 2.0                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Details:              | If RSYNC in the DMA Channel Primary Control Register is set to host-port host-to-DSP interrupt (DSPINT – 10000b), the DMA channel would do the read transfer without waiting for the sync event. There is not a problem if WSYNC is set to DSPINT. (Internal reference number C601302)                                                                                                                                                      |

| Workaround:           | Do not use synchronized DMA reads to DSPINT. If a DMA read is desired during a host-port host-to-DSP interrupt, set RSYNC in the Primary Control Register to one of the EXT_INT events instead (EXT_INT4 – EXT_INT7) and have the host trigger an interrupt on that pin rather than by writing to HPIC.                                                                                                                                     |

| Advisory 3.1.8        | EMIF: Invalid SDRAM Access to Last 1K Byte of CE3                                                                                                                                  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision(s) Affected: | 3.1, 3.0, 2.1, and 2.0                                                                                                                                                             |  |  |

| Details:              | If 16M bytes of SDRAM (two 64M bits in a 1M X 16x4 organization) is used in CE3, you can have invalid accesses to the last 1K byte of CE3 (0x03FFFC00).                            |  |  |

|                       | This occurs when the following is true:                                                                                                                                            |  |  |

|                       | <ul> <li>After a DCAB (deactivate all pages) to all SDRAM CE spaces (forced by Refresh or<br/>MRS command)</li> </ul>                                                              |  |  |

|                       | • The first access to CE3 is to the last page of CE3 (0x03FFFC00).                                                                                                                 |  |  |

|                       | • Then a page activate will not be issued to CE3. Since the SDRAM in CE3 is in a deactivated state at that point, invalid accesses will occur. (Internal reference number C630280) |  |  |

| Workaround:           | Best Case: Avoid designing a board with a 64M-bit (1M X 16x4) SDRAM mapped into CE3.                                                                                               |  |  |

Alternative: If a 64M-bit SDRAM is located in CE3, avoid using the last 1K byte in the CE3 memory map (0x03FFFC00).

| Advisory 3.1.9        | Cache During Emulation With Extremely Slow External Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision(s) Affected: | 3.1, 3.0, 2.1, and 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Details:              | If a program requests fetch packet "A" followed immediately by fetch packet "B", and all of the following four conditions are true:                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                       | <ol> <li>A and B are separated by a multiple of 64K in memory (i.e., they will occupy the same<br/>cache frame)</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                       | 2. B is currently located in cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                       | 3. You are using the emulator to single-step through the branch from A to B                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                       | <ol> <li>The code is running off of an extremely slow external memory that transfers one 32-bit<br/>word every 8000 or more CPU clock cycles (CPU running at 200 MHz)</li> </ol>                                                                                                                                                                                                                                                                                                                                       |  |  |

|                       | Then A will be registered as a "miss" and B will be registered as a "hit". B will not be reloaded into cache, and A will be executed twice. This condition is extremely rare because B has to be in cache memory, and must be the next fetch packet requested after A (which is not in cache memory). In addition, this problem only occurs if you single-step through the branch from A to B using the emulator, and if the code is located in an extremely slow external memory. (Internal reference number C630283) |  |  |

| Workaround:           | • Do not single-step through the branch from A to B if the above conditions are true.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                       | Do not use an extremely slow external memory (transfers and 22 bit word every 8000                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

• Do not use an extremely slow external memory (transfers one 32-bit word every 8000 or more CPU clock cycles) if conditions 1, 2, and 3 are true.

#### Silicon Revision 3.0 Known Design Exceptions to Functional Specifications 4

| Advisory 3.0.8        | EMIF: Inverted SDCLK and SSCLK at Speeds Above 175 MHz                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 3.0, 2.1, and 2.0                                                                                                                                                                                                                                                                                                                                                                                                |

| Details:              | A speedpath in the device causes SDCLK and SSCLK to start up 180 degrees out-of-phase (effectively inverted) from the desired waveform. Normally, EMIF outputs are delayed 1/2 CPU clock from the rising edge of SDCLK/SSCLK to give it adequate hold time while maintaining more than adequate setup times.                                                                                                     |

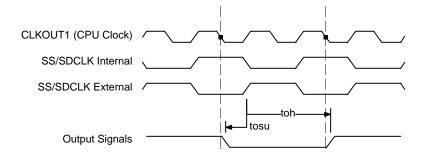

|                       | The desired relationship is described in the TMS320C6201B data sheet (SPRS051) and is illustrated in Figure 4 and Figure 6. However, in the case where SDCLK/SSCLK becomes inverted (Figure 5 and Figure 7), control signals only have 1/2 CPU clock of setup to the next SDCLK/SSCLK rising rather than 3/2 CPU clock of setup. This has two negative effects to interface timing to external synchronous RAMs. |

|                       | 1 On writes setup time to RAMs for control signals and write data is reduced by 1 CPU cycle                                                                                                                                                                                                                                                                                                                      |

On writes, setup time to RAMs for control signals and write data is reduced by 1 CPU cycle.

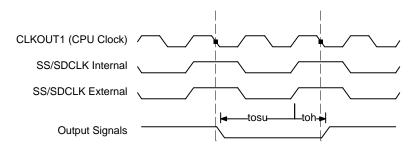

## Figure 4. Write Example – Desired Behavior

EMIF: Inverted SDCLK and SSCLK at Speeds Above 175 MHz (Continued)

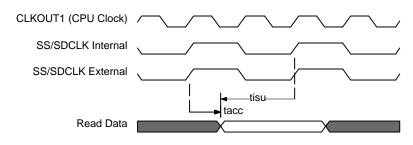

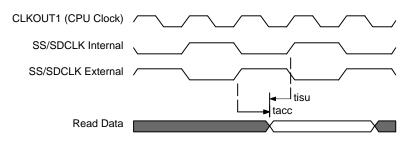

2. On SBSRAM/SDRAM reads, data will be sampled on the falling edge before the rising edge that would be expected. In this case, the input setup time for data at the C62x<sup>™</sup> is reduced by 1 CPU cycle. Note that this case can be compounded with Case 1. The control signals could be latched one SSCLK/SDCLK cycle (2 CPU cycles) late by the memories. Thus, the setup could be reduced by up to 3 CPU cycles and be more than an entire SSCLK/SDCLK late.

#### Figure 6. Read Example – Desired Behavior

CLKOUT2 is also affected by this speedpath bug and is 180 degrees out-of-phase. It behaves in the same way as SDCLK. (Internal reference number C601307)

Workaround:

- For prototypes, raising the core supply to 1.9 2.1 V corrects this problem. This is not recommended in boards shipped to customers, since the manufacturing process is not designed to be reliable outside the normal operating range. This option allows the user to verify current board designs at all valid frequency ranges.

- Reduce the operating frequency of the TMS320C6201B until SSCLK/SDCLK has the desired relationship. Typically, this occurs at 175 MHz across the range of recommended operating conditions.

- Since SSCLK and SDCLK are inverted externally relative to each other by design, these signals can be swapped on external memory interfaces to correct the problem (SSCLK to SDRAM and SDCLK to SBSRAM). This will cause invalid operation at frequencies below 175 MHz and will not work with future silicon revisions.

- If CLKOUT2 is used as an SDRAM clock, follow all the workarounds for SDCLK.

C62x is a trademark of Texas Instruments Incorporated.

|                       | EMIF: Inverted SDCLK and SSCLK at Speeds Above 175 MHz (Continued)                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Alternate Workaround: | The following alternate workarounds can help for certain board and layout configurations.                                                                                                                                                                                                                                                                                                                      |

|                       | <ul> <li>Using faster (125 MHz or PC100) SDRAMs and/or SBSRAMs will reduce the chances<br/>of data corruption and/or increase the frequency at which reliable memory operation<br/>can be observed. Operation is not specified to be reliable across operating conditions<br/>and different samples of memory and C6201B devices due to lot-to-lot variation on<br/>both the memory and the C6201B.</li> </ul> |

|                       | <ul> <li>SDCLK/SSCLK can be delayed externally. This can be accomplished either via<br/>inverter(s), precision delay device, or longer board route on the clock line. The idea is<br/>to force the external clock to resemble the desired clock waveform as closely as<br/>possible, providing more setup for both reads and writes.</li> </ul>                                                                |

|                       | • You may start the device at a frequency where the skew does not occur and raise the operating frequency to the desired rate. This must be done at each processor reset. This solution works since the speedpath exists in the reset (non-run time) operation of the SDCLK/SSCLK circuit. Whatever operations starts at reset is observable until the next reset.                                             |

| Resolution            | • Revision 3.1 of silicon will correct this problem.                                                                                                                                                                                                                                                                                                                                                           |

| Advisory 3.0.9        | CPU: L2-unit Long Instructions Corrupted During Interrupt                                                                                                                                                                                                                                                                            |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 3.0, 2.1, and 2.0                                                                                                                                                                                                                                                                                                                    |

| Details:              | If an interrupt occurs causing a B-side L-unit (.L2 unit) instruction that writes a long value to be annulled, the top 8 bits of the result will be written rather than being annulled. This bug only applies to the B-side L-unit (.L2 unit). The A-side L-unit (.L1 unit) functions correctly. (Internal reference number C620774) |

|                       | This bug will not affect:                                                                                                                                                                                                                                                                                                            |

|                       | Customers programming in C with no long data types.                                                                                                                                                                                                                                                                                  |

|                       | Customers not using code with long instructions on the .L2-unit.                                                                                                                                                                                                                                                                     |

|                       | <ul> <li>Customers only using long instructions on the .L2-unit inside loops 5 or less than<br/>5 cycles long. (Interrupts are disabled in the five delay slots of a branch.)</li> </ul>                                                                                                                                             |

| Workaround:           | <ul> <li>Disable interrupts using the appropriate compiler switches or register modifications<br/>in the affected C code.</li> </ul>                                                                                                                                                                                                 |

|                       | • Disable interrupts seven execute packets before any long instructions on the .L2-unit that are <i>not</i> in the delay slots of a branch.                                                                                                                                                                                          |

|                       | • Use the .L1-unit for long instructions if interrupts are anticipated.                                                                                                                                                                                                                                                              |

| Resolution            | • Revision 3.1 of silicon will correct this problem.                                                                                                                                                                                                                                                                                 |

|                       |                                                                                                                                                                                                                                                                                                                                      |

## 5 Silicon Revision 2.1 Known Design Exceptions to Functional Specifications

| Advisory 2.1.1        | EMIF: CE Space Crossing on Continuous Request Not Allowed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 2.1 and 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Details:              | Any continuous request of the EMIF cannot cross CE address space boundaries. This condition can result in bad data read, or writing to the wrong CE. (Internal Reference Numbers 2600 and 3421)                                                                                                                                                                                                                                                                                                                                                   |

| Workaround:           | CPU Program Fetch: The simplest fix is for all external program to reside within a single CE space. Alternatively, program fetch flow should not occur across CE spaces. This can be accomplished by branching on-chip between executing from one CE to another CE.                                                                                                                                                                                                                                                                               |

|                       | DMA: All DMA block transfers without read or write synchronization should have all EMIF addresses within a frame to belong to one CE space. In other words, all read (src) addresses should belong to one CE space and should not cross CE boundaries. The same applies to write (dst) addresses within a frame. Note that the source can be in the same CE space or different CE space as the destination. DMA transfers with read and/or write synchronization together with CE boundaries crossed between frames are not affected by this bug. |

|                       | CPU Data Access: External CPU data accesses cannot perform continuous requests and thus are not affected by this bug.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Advisory 2.1.2        | EMIF: SDRAM Invalid Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Revision(s) Affected: | 2.1 and 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Details:              | An invalid SDRAM access occurs when all of the following are true:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | <ul> <li>Two or more SDRAM devices in different CE spaces</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | Each SDRAM device has a page activate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                       | One active page is in bank 0 and the other in bank 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | <ul> <li>Each CE space with SDRAM is accessed (alternating) without a page miss or refresh<br/>occurring (no Deactivate command).</li> <li>OR</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |

|                       | <ul> <li>Two or more SDRAM devices in different CE spaces</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | A trickle refresh deactivates both devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

- Before refresh occurs, a request to access one CE space comes in. The refresh will wait until the first requester has completed.

- If request to second CE space occurs before refresh occurs, then an invalid access takes place, since the controller neglects the fact that this space was deactivated. (Internal Reference Numbers 4139, 0335, and 0871)

EMIF: SDRAM Invalid Access (Continued)

Workaround:

Avoid use of multiple CE spaces of SDRAM within a single refresh period.

| Advisory 2.1.4        | DMA: RSYNC Cleared Late for Frame-synchronized Transfer                                                                                                                                                                    |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 2.1 and 2.0                                                                                                                                                                                                                |

|                       | In a frame-synchronized transfer, RSYNC is only cleared after the beginning of last write transfer. It should occur after the start of the first read transfer in the synchronized frame. (Internal reference number 0267) |

| Workaround:           | Wait until end-of-frame (perhaps using DMAC pins for external status) to issue next frame synchronization.                                                                                                                 |

|                       |                                                                                                                                                                                                                            |

| Advisory 2.1.5 McBSP: DXR to XSR Copy Not Generated |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Revision(s) Affected: | 2.1 and 2.0 |

|-----------------------|-------------|

|-----------------------|-------------|

Details:If any element size other than 32 bits is written to the DXR of either serial port, then the<br/>register is not copied to the XSR. (Internal reference number 0511)