# TMS320DM643x DMP VLYNQ Port

# **User's Guide**

Literature Number: SPRU938B September 2007

Download from Www.Somanuals.com. All Manuals Search And Download.

| _   |        |                                                          |   |

|-----|--------|----------------------------------------------------------|---|

| 1   |        | iction                                                   |   |

|     | 1.1    | Purpose of the Peripheral                                |   |

|     | 1.2    | Features                                                 |   |

|     | 1.3    | Functional Block Diagram                                 |   |

|     | 1.4    | Industry Standard(s) Compliance Statement                |   |

| 2   | •      | eral Architecture                                        |   |

|     | 2.1    | Clock Control                                            |   |

|     | 2.2    | Signal Descriptions                                      |   |

|     | 2.3    | Pin Multiplexing                                         |   |

|     | 2.4    | Protocol Description                                     |   |

|     | 2.5    | VLYNQ Functional Description                             |   |

|     | 2.6    | Initialization                                           |   |

|     | 2.7    | Auto-Negotiation                                         |   |

|     | 2.8    | Address Translation                                      |   |

|     | 2.9    | Flow Control                                             |   |

|     | 2.10   | Reset Considerations                                     |   |

|     | 2.11   | Interrupt Support                                        |   |

|     | 2.12   | EDMA Event Support                                       |   |

|     | 2.13   | Power Management                                         |   |

|     | 2.14   | Endianness Considerations                                |   |

|     | 2.15   | Emulation Considerations                                 |   |

| 3   | VLYNG  | Port Registers                                           | 1 |

|     | 3.1    | Revision Register (REVID)                                |   |

|     | 3.2    | Control Register (CTRL)                                  |   |

|     | 3.3    | Status Register (STAT)                                   |   |

|     | 3.4    | Interrupt Priority Vector Status/Clear Register (INTPRI) |   |

|     | 3.5    | Interrupt Status/Clear Register (INTSTATCLR)             |   |

|     | 3.6    | Interrupt Pending/Set Register (INTPENDSET)              |   |

|     | 3.7    | Interrupt Pointer Register (INTPTR)                      |   |

|     | 3.8    | Transmit Address Map Register (XAM)                      |   |

|     | 3.9    | Receive Address Map Size 1 Register (RAMS1)              |   |

|     | 3.10   | Receive Address Map Offset 1 Register (RAMO1)            |   |

|     | 3.11   | Receive Address Map Size 2 Register (RAMS2)              |   |

|     | 3.12   | Receive Address Map Offset 2 Register (RAMO2)            |   |

|     | 3.13   | Receive Address Map Size 3 Register (RAMS3)              |   |

|     | 3.14   | Receive Address Map Offset 3 Register (RAMO3)            |   |

|     | 3.15   | Receive Address Map Size 4 Register (RAMS4)              |   |

|     | 3.16   | Receive Address Map Offset 4 Register (RAMO4)            |   |

|     | 3.17   | Chip Version Register (CHIPVER)                          |   |

|     | 3.18   | Auto Negotiation Register (AUTNGO)                       |   |

| 4   | Remote | e Configuration Registers                                |   |

| Anr |        | VLYNQ Protocol Specifications                            |   |

|     | A.1    | Introduction                                             |   |

|     | ,      |                                                          |   |

| Special 8b/10b Code Groups | 39                                                                                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supported Ordered Sets     | 39                                                                                                                                                        |

| VLYNQ 2.0 Packet Format    | 40                                                                                                                                                        |

| VLYNQ 2.X Packets          | 42                                                                                                                                                        |

| Write/Read Performance     | 44                                                                                                                                                        |

| Introduction               | 44                                                                                                                                                        |

| Write Performance          | 44                                                                                                                                                        |

| Read Performance           | 46                                                                                                                                                        |

| Revision History           | 47                                                                                                                                                        |

|                            | Supported Ordered Sets<br>VLYNQ 2.0 Packet Format<br>VLYNQ 2.X Packets<br>Write/Read Performance<br>Introduction<br>Write Performance<br>Read Performance |

# List of Figures

| 1   | VLYNQ Port Functional Block Diagram                      | . 9 |

|-----|----------------------------------------------------------|-----|

| 2   | External Clock Block Diagram                             | 10  |

| 3   | Internal Clock Block Diagram                             | 10  |

| 4   | VLYNQ Module Structure                                   | 12  |

| 5   | Write Operations                                         | 13  |

| 6   | Read Operations                                          | 14  |

| 7   | Example Address Memory Map                               | 17  |

| 8   | Interrupt Generation Mechanism Block Diagram             | 21  |

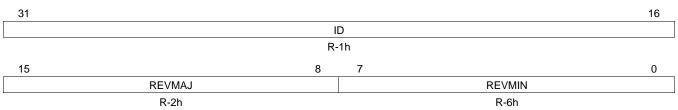

| 9   | Revision Register (REVID)                                | 25  |

| 10  | Control Register (CTRL)                                  | 26  |

| 11  | Status Register (STAT)                                   | 28  |

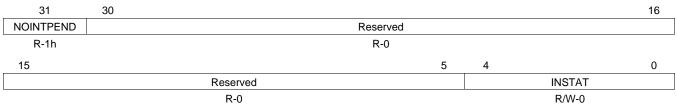

| 12  | Interrupt Priority Vector Status/Clear Register (INTPRI) | 30  |

| 13  | Interrupt Status/Clear Register (INTSTATCLR)             | 30  |

| 14  | Interrupt Pending/Set Register (INTPENDSET)              | 31  |

| 15  | Interrupt Pointer Register (INTPTR)                      | 31  |

| 16  | Transmit Address Map Register (XAM)                      | 32  |

| 17  | Receive Address Map Size 1 Register (RAMS1)              | 33  |

| 18  | Receive Address Map Offset 1 Register (RAMO1)            | 33  |

| 19  | Receive Address Map Size 2 Register (RAMS2)              | 34  |

| 20  | Receive Address Map Offset 2 Register (RAMO2)            | 34  |

| 21  | Receive Address Map Size 3 Register (RAMS3)              | 35  |

| 22  | Receive Address Map Offset 3 Register (RAMO3)            | 35  |

| 23  | Receive Address Map Size 4 Register (RAMS4)              | 36  |

| 24  | Receive Address Map Offset 4 Register (RAMO4)            | 36  |

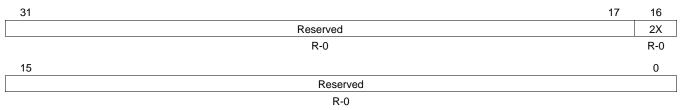

| 25  | Chip Version Register (CHIPVER)                          | 37  |

| 26  | Auto Negotiation Register (AUTNGO)                       | 37  |

| A-1 | Packet Format (10-bit Symbol Representation)             | 40  |

# List of Tables

| 1   | VLYNQ Signal Descriptions                                                   | 11 |

|-----|-----------------------------------------------------------------------------|----|

| 2   | Address Translation Example (Single Mapped Region)                          | 17 |

| 3   | Address Translation Example (Single Mapped Region)                          | 18 |

| 4   | VLYNQ Register Address Space                                                | 24 |

| 5   | VLYNQ Port Controller Registers                                             | 24 |

| 6   | Revision Register (REVID) Field Descriptions                                | 25 |

| 7   | Control Register (CTRL) Field Descriptions                                  | 26 |

| 8   | Status Register (STAT) Field Descriptions                                   | 28 |

| 9   | Interrupt Priority Vector Status/Clear Register (INTPRI) Field Descriptions | 30 |

| 10  | Interrupt Status/Clear Register (INTSTATCLR) Field Descriptions             | 30 |

| 11  | Interrupt Pending/Set Register (INTPENDSET) Field Descriptions              | 31 |

| 12  | Interrupt Pointer Register (INTPTR) Field Descriptions                      | 31 |

| 13  | Address Map Register (XAM) Field Descriptions                               | 32 |

| 14  | Receive Address Map Size 1 Register (RAMS1) Field Descriptions              | 33 |

| 15  | Receive Address Map Offset 1 Register (RAMO1) Field Descriptions            | 33 |

| 16  | Receive Address Map Size 2 Register (RAMS2) Field Descriptions              | 34 |

| 17  | Receive Address Map Offset 2 Register (RAMO2) Field Descriptions            | 34 |

| 18  | Receive Address Map Size 3 Register (RAMS3) Field Descriptions              | 35 |

| 19  | Receive Address Map Offset 3 Register (RAMO3) Field Descriptions            | 35 |

| 20  | Receive Address Map Size 4 Register (RAMS4) Field Descriptions              | 36 |

| 21  | Receive Address Map Offset 4 Register (RAMO4) Field Descriptions            | 36 |

| 22  | Chip Version Register (CHIPVER) Field Descriptions                          | 37 |

| 23  | Auto Negotiation Register (AUTNGO) Field Descriptions                       | 37 |

| 24  | VLYNQ Port Remote Controller Registers                                      | 38 |

| A-1 | Special 8b/10b Code Groups                                                  | 39 |

| A-2 | Supported Ordered Sets                                                      | 39 |

| A-3 | Packet Format (10-bit Symbol Representation) Description                    | 41 |

| B-1 | Scaling Factors                                                             | 45 |

| B-2 | Expected Throughput (VLYNQ Interface Running at 76.5 MHZ and 99 MHZ)        | 45 |

| B-3 | Relative Performance with Various Latencies                                 | 46 |

| C-1 | Document Revision History                                                   | 47 |

# About This Manual

This document describes the VLYNQ port in the TMS320DM643x Digital Media Processor (DMP).

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the TMS320DM643x Digital Media Processor (DMP). Copies of these documents are available on the Internet at <u>www.ti.com</u>. *Tip:* Enter the literature number in the search box provided at www.ti.com.

The current documentation that describes the DM643x DMP, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: <u>www.ti.com/c6000</u>.

<u>SPRU978</u> — *TMS320DM643x DMP DSP Subsystem Reference Guide.* Describes the digital signal processor (DSP) subsystem in the TMS320DM643x Digital Media Processor (DMP).

<u>SPRU983</u> — *TMS320DM643x DMP Peripherals Overview Reference Guide.* Provides an overview and briefly describes the peripherals available on the TMS320DM643x Digital Media Processor (DMP).

<u>SPRAA84</u> — TMS320C64x to TMS320C64x+ CPU Migration Guide. Describes migrating from the Texas Instruments TMS320C64x digital signal processor (DSP) to the TMS320C64x+ DSP. The objective of this document is to indicate differences between the two cores. Functionality in the devices that is identical is not included.

SPRU732 — TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of the C64x DSP with added functionality and an expanded instruction set.

SPRU871 — TMS320C64x+ DSP Megamodule Reference Guide. Describes the TMS320C64x+ digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

#### Trademarks

VLYNQ is a trademark of Texas Instruments.

7

# **VLYNQ** Port

#### 1 Introduction

#### 1.1 Purpose of the Peripheral

The VLYNQ<sup>™</sup> communications interface port is a low pin count, high-speed, point-to-point serial interface in the TMS320DM643x Digital Media Processor (DMP) used for connecting to host processors and other VLYNQ compatible devices. The VLYNQ port is a full-duplex serial bus where transmit and receive operations occur separately and simultaneously without interference.

VLYNQ enables the extension of an internal bus segment to one or more external physical devices. The external devices are mapped to local physical address space and appear as if they are on the internal bus of the DM643x DMP. The external devices must also have a VLYNQ interface.

VLYNQ uses a simple block code (8b/10b) packet format and supports in-band flow control so that no extra terminals are needed to indicate that overflow conditions might occur.

The VLYNQ module on the DM643x DMP serializes a write transaction to the remote/external device and transfers the write via the VLYNQ port (TX pins). The remote VLYNQ module deserializes the transaction on the other side.

The read transactions to the remote/external device follow the same process, but the remote device's VLYNQ module serializes the read return data and transfers it to the VLYNQ port (RX pins). The read return data is finally deserialized and released to the device internal bus.

The external device can also initiate read and write transactions.

#### 1.2 Features

The general features of the VLYNQ port are:

- Low pin count (10 pin interface, scalable to as low as 3 pins)

- No tri-state signals

- All signals are dedicated and driven by only one device

- Necessary to allow support for high-speed PHYs

- Simple packet-based transfer protocol for memory-mapped access

- Write request/data packet

- Read request packet

- Read response data packet

- Interrupt request packet

- Auto width negotiation

- Symmetric Operations

- Transmit (TX) pins on the first device connect to the receive (RX) pins on the second device and vice-versa.

- Data pin widths are automatically detected after reset

- Re-request packets, response packets, and flow control information are all multiplexed and sent across the same physical pins.

- Supports both host/peripheral and peer-to-peer communication models

- Simple block code packet formatting (8b/10b)

- Supports in-band and flow control

- No extra pins are needed

- Allows the receiver to momentarily throttle the transmitter back when overflow is about to occur

- Uses the special built-in block code capability to interleave flow control information seamlessly with user data

- Automatic packet formatting optimizations

- Internal loopback modes are provided

- Connects to legacy VLYNQ devices

### 1.3 Functional Block Diagram

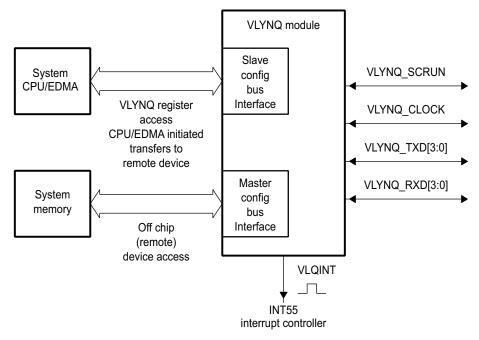

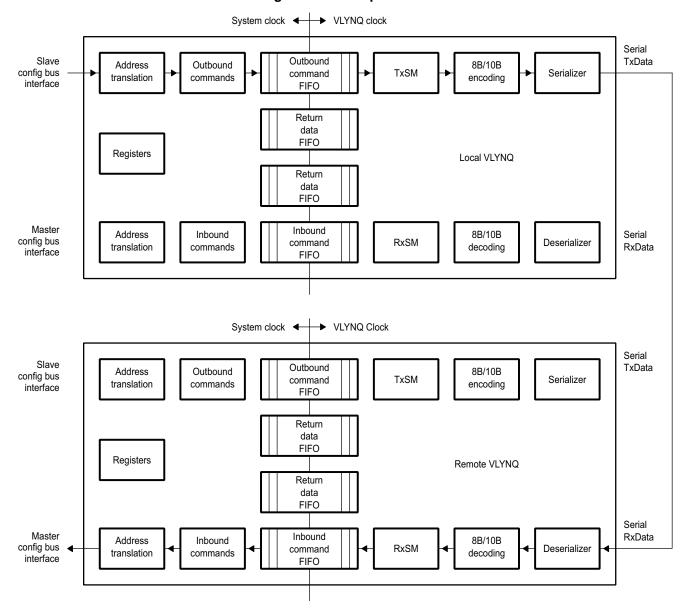

Figure 1 shows a functional block diagram of the VLYNQ port.

Figure 1. VLYNQ Port Functional Block Diagram

# 1.4 Industry Standard(s) Compliance Statement

VLYNQ is an interface defined by Texas Instruments and does not conform to any other industry standard.

# 2 Peripheral Architecture

This section discusses the architecture and basic functions of the VLYNQ peripheral.

### 2.1 Clock Control

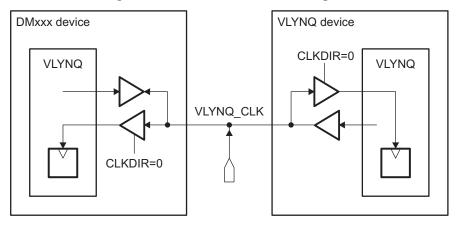

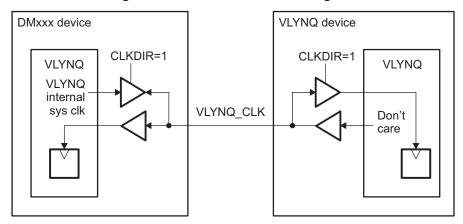

The module's serial clock direction and frequency are software configurable through the CLKDIR and CLKDIV bits in the VLYNQ control register (CTRL). The VLYNQ serial clock can be sourced from the internal system clock (CLKDIR = 1) or by an external clock source (CLKDIR = 0) for its serial operations.

The CLKDIV bit can divide the serial clock (1/1 - 1/8) down when the internal clock is selected as the source. The serial clock is not affected by the CLKDIV bit values, if the serial clock is externally sourced.

The reset value of the CLKDIR bit is 0 (external clock source).

The external clock source is shown in Figure 2. The internal clock source is shown in Figure 3.

Figure 2. External Clock Block Diagram

#### Figure 3. Internal Clock Block Diagram

# 2.2 Signal Descriptions

The VLYNQ module on the DM643x device supports 1 to 4 bit-wide RX/TX configurations. Chip-level pin multiplexing registers control the configuration. See the pin multiplexing information in the device-specific data manual.

If the VLYNQ data width does not match the number of transmit/receive lines that are available on the remote device, negotiation between the two VLYNQ devices automatically configures the width (see Section 2.7).

The VLYNQ interface signals are shown in Table 1.

| Pin Name       | Signal Name                                    | Signal Type  | Function                                                                                                                                                                                                                                                                                  |

|----------------|------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VLYNQ_CLOCK    | VLYNQ serial clock                             | Input/Output | The VLYNQ reference clock supports the internally or<br>externally generated clock.                                                                                                                                                                                                       |

| VLYNQ_SCRUN    | VLYNQ serial clock run<br>request (Active low) | Input/Output | The VLYNQ serial clock run request allows remote requests<br>for the VLYNQ serial clock to be turned off for system power<br>management.<br>Low: The request VLYNQ serial clock is active.<br>High: The VLYNQ serial clock is requested to be high when<br>all transactions are complete. |

| VLYNQ_RXD[0:3] | VLYNQ receive data                             | Input        | VLYNQ receive data is synchronous with the VLYNQ serial clock.                                                                                                                                                                                                                            |

| VLYNQ_TXD[0:3] | VLYNQ transmit data                            | Output       | VLYNQ transmit data is synchronous with the VLYNQ serial<br>clock.                                                                                                                                                                                                                        |

#### Table 1. VLYNQ Signal Descriptions

#### 2.3 Pin Multiplexing

Extensive use of pin multiplexing is used to accommodate the largest number of peripheral functions in the smallest possible package. Pin multiplexing is controlled using a combination of hardware configurations at device reset and software programmable register settings. The VLYNQ module pins are not enabled at reset. In order to change the default function of device pins at reset, the pin multiplexing registers (PINMUX*n*) must be configured appropriately. Refer to the pin multiplexing information in the device-specific data manual for more detailed information on the processor pin multiplexing and configuration registers.

# 2.4 Protocol Description

VLYNQ relies on 8b/10b block coding to minimize the number of serial pins and allows for in-band packet delineation and control.

Appendix A provides general information on 8b/10b coding definitions and their implementation within the VLYNQ module in the DM643x device.

#### 2.5 VLYNQ Functional Description

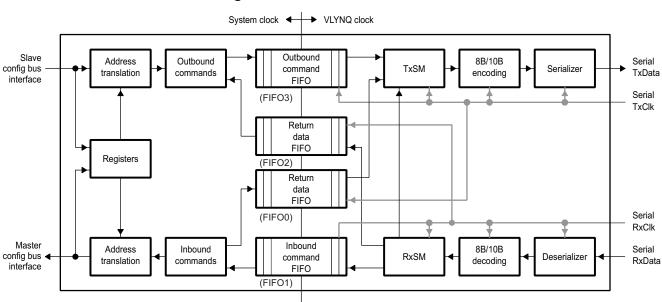

The VLYNQ core supports both host-to-peripheral and peer-to-peer communication models and is symmetrical. The VLYNQ module structure is shown in Figure 4.

#### Figure 4. VLYNQ Module Structure

The VLYNQ core module implements two 32-bit configuration bus interfaces. Transmit operations and control register access require the slave configuration bus interface. The master configuration bus interface is required for receive operations. Converting to and from the 32-bit bus to the external serial interface requires serializer and deserializer blocks.

8b/10b block coding encodes data on the serial interface. Frame delineation, initialization, and flow control use special overhead code groups.

FIFOs buffer the entire burst on the bus for maximum performance, thus minimizing bus latency. Using write operations of each VLYNQ module interfaced is typically recommended to ensure the best performance on both directions of the link.

#### 2.5.1 Write Operations

Write requests that initiate from the slave configuration bus interface of the local device write to the outbound command (CMD) FIFO. Data is subsequently read from the FIFO and encapsulated in a write request packet. The address is translated, and the packet is encoded and serialized before being transmitted to remote device. The remote device subsequently deserializes and decodes the receive data and writes it into the inbound CMD FIFO. A write operation initiates on the remote device's master configuration bus interface after reading the address and data from the FIFO.

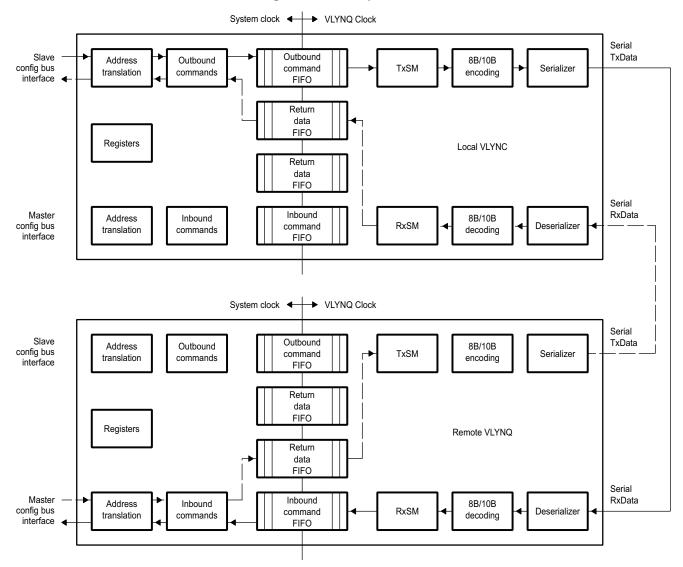

The data flow between two VLYNQs that are connected is shown in Figure 5. In the example shown in Figure 5, the write originates from the DM643x device.

Figure 5. Write Operations

#### 2.5.2 Read Operations

Read requests from the slave configuration bus interface are written to the outbound CMD FIFO (similar to the write requests). Data is subsequently read from the FIFO and encapsulated into a read request packet. The packet is encoded and serialized before it is transmitted to the remote device. Next, the remote device deserializes, decodes the receive data, and writes the receive data to the inbound CMD FIFO. After reading the address from the FIFO, a master configuration bus interface read operation initiates in the remote device. When the remote master configuration bus interface receives the read data, the data is written to the return data FIFO before it is encoded and serialized. When the receive data reaches the local VLYNQ module, it is deserialized, decoded, and written to the return data FIFO (local device). Finally, the read data is transferred on the local device's slave configuration interface.

The data flow between two connected VLYNQ devices with read requests that originate from the DM643x device is shown in Figure 6. The remote VLYNQ device returns the read data. Read data is shown with dotted arrows.

Figure 6. Read Operations

**Note:** Not servicing read operations results in deadlock. The only way to recover from a deadlock situation is to perform a hard reset. Read operations are typically not serviced due to read requests that are issued to a non-existent remote VLYNQ device or they are not serviced due to trying to perform reads on the VLYNQ memory map prior to establishing the link.

Generally, you should not use read operations to transfer data packets since the serial nature of the interface could potentially result in longer latencies. See Appendix B for more information.

#### 2.6 Initialization

Since VLYNQ devices can be controlled solely over the serial interface (that is, no local CPU exists), an automatic reliable initialization sequence (without user configuration) establishes a connection between two VLYNQ devices, just after a VLYNQ module is enabled and auto-negotiation occurs. Auto-negotiation is defined in Section 2.7. The same sequence is used to recover from error conditions. However, it is important to ensure that the appropriate bits are configured in the pin mux registers to ensure that the VLYNQ peripheral is active.

Bit 0 in the VLYNQ status register (LINK bit) is set to 1 when a link is established.

A link pulse timer generates a periodic link code every 2048 serial clock cycles. The link is lost when time expires and no link code has been detected during a period of 4096 serial clock cycles.

#### 2.7 Auto-Negotiation

Auto-negotiation occurs after reset. It involves placing a negotiation protocol in the outbound data and processing the inbound data to establish connection information. The width of the data pins on the serial interface is automatically determined at reset as a part of the initialization sequence. For a connection between two VLYNQ devices of version 2.0 and later (VLYNQ on DM643x device is version 2.6), the negotiation protocol using the available serial pins is used to convey the maximum width capability of each device. The TXD data pins are not required to have the same width as the RXD data pins.

The auto width negotiation does not occur until after completion of the VLYNQ 1.x legacy width configuration, which involves a period of 2000 VLYNQ 1.x system clock cycles for connection to VLYNQ 1.x devices. After the VLYNQ 1.x has determined its width, it receives the VLYNQ2.x auto width negotiation protocol. The VLYNQ 1.x device does not recognize this protocol and transmits error codes over the serial interface. The received error codes allow the VLYNQ 2.x devices to determine how many serial pins are valid on the connected VLYNQ 1.x device.

Once the width is established, VLYNQ further identifies the version (version 1.x or version 2.x) of the remote VLYNQ. This better determines the capabilities of the connected VLYNQ device. This is software readable via the VLYNQ auto-negotiation register (AUTNGO), bit 16 (0 = Ver 1.x, 1 = Ver 2.x), after the link has been established.

#### 2.8 Address Translation

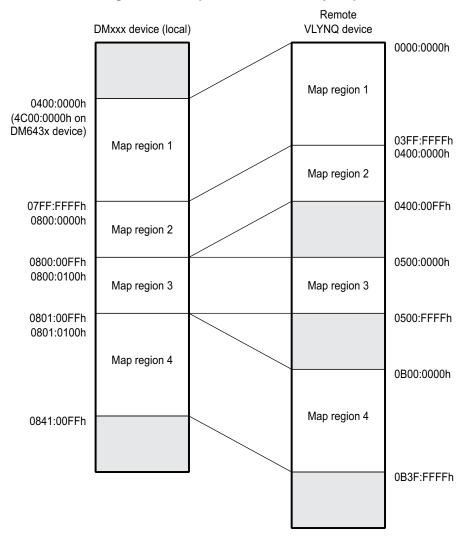

Remote VLYNQ device(s) are memory mapped to the local (host) device's address space when a link is established (this is similar to any other on-chip peripherals). Enumerating the VLYNQ devices (single or multiple) into a coherent memory map for accessing each device is part of the initialization sequence.

After the enumeration, the host (local) device can access the remote device address map using local device addresses. The VLYNQ module in the host device manages the address translation of the local address to the remote address. A remote VLYNQ device is mapped to the local device's address via the address map registers (TX address map, RX address map size *n*, RX address map offset *n*, where n = 1 to 4). The transmit side has a contiguous map; the size of the map is the same as the remote device map. Figure 7 illustrates this mapping.

In the local device, the address of the VLYNQ remote memory map in the local configuration space is the transmit address accessing remote devices over the serial interface. The address of the VLYNQ remote memory map is programmed in the TX address map register (XAM). When the local device transmits, first it strips off the transmit address offset in the local device memory map. Then, the local device sends the data with an address offset from the transmit address.

VLYNQ allows each receive packet address to be translated into one of the four mapped regions. The size and offset of each memory region must be aligned to 32-bit words. No restriction is placed on programming the size or on the offset of each mapped region, as long as the total memory that is mapped into these one to four regions is not more then 64 MBytes.

**Note:** Care should be taken while programming the receive address map size register (RAMS*n*) and the receive address map offset register (RAMO*n*) values. These registers should be programmed with valid address locations and memory size to match the device specifications. See the Memory Map Summary and the System Interconnect sections in your device-specific data manual to identify the valid memory regions that can be accessed by an off-chip peer device through the VLYNQ interface.

The transmitted address is used to determine which remote mapped region is being accessed at the remote device. This is achieved by summing each memory size sequentially until the memory size is larger than the transmitted address. The last memory size that is added is the targeted region. A memory size and an offset specify the remote map. The remote map is programmed in the RX address map size register (RAMS*n*) and in the RX address map offset (RAMO*n*) in the remote device.

#### Figure 7. Example Address Memory Map

The following shows an example illustrating the address translation used in each VLYNQ module.

Address bits [31:26] are not used for address translation to remote devices on the DM643x device.

Table 2 shows the address map register configuration when the DM643x device is transmitting data to the remote device.

Table 2. Address Translation Example (Single Mapped Region)

| Register                | DM643x VLYNQ Module | Remote VLYNQ Module |

|-------------------------|---------------------|---------------------|

| TX Address Map          | 0000 : 0000h        | Do not care         |

| RX Address Map Size 1   | Do not care         | 0000 : 0100h        |

| RX Address Map Offset 1 | Do not care         | 0800 : 0000h        |

#### DM643x VLYNQ Module:

|          | 4C00 : 0054h | Initial address at the slave configuration bus                                                              |

|----------|--------------|-------------------------------------------------------------------------------------------------------------|

|          | 0000 : 0054h | Initial address [25:0] at the slave configuration bus interface                                             |

| subtract | 0000 : 0000h | TX address map register (there is no need to change the reset value of the DM643x device for this register) |

|          | 0000 : 0054h |                                                                                                             |

#### **Remote VLYNQ Module:**

|         | 0000 : 0054h | Initial address from the RX serial interface |

|---------|--------------|----------------------------------------------|

| compare | 0000 : 0100h | RX address map size 1 register               |

|         | 0000 : 0054h |                                              |

| add     | 0800 : 0000h | RX address map offset 1 register             |

|         | 0800 : 0054h | Translated address to remote device          |

The local address 4C00:0054h (or 0000 0054h) was translated to 0800:0054h on the remote VLYNQ device in Table 3.

Table 3 shows the address map register configuration when the DM643x device is receiving data from the remote device.

| Register                | DM643x VLYNQ Module | Remote VLYNQ Module |

|-------------------------|---------------------|---------------------|

| TX Address Map          | Do not care         | 0400 : 0000h        |

| RX Address Map Size 1   | 0000 : 0100h        | Do not care         |

| RX Address Map Offset 1 | 0200 : 0000h        | Do not care         |

| RX Address Map Size 2   | 0000 : 0100h        | Do not care         |

| RX Address Map Offset 2 | 8200 : 0000h        | Do not care         |

|                         |                     |                     |

#### Table 3. Address Translation Example (Single Mapped Region)

#### Remote VLYNQ Module:

|          | 0400 : 0154h | Initial address at the slave configuration bus for the remote device |

|----------|--------------|----------------------------------------------------------------------|

| subtract | 0400 : 0000h | TX address map register                                              |

|          | 0000 : 0154h | Translated address to remote device via serial interface             |

#### DM643x VLYNQ Module:

|          | 0000 : 0154h | Initial address from the RX serial interface                                                      |

|----------|--------------|---------------------------------------------------------------------------------------------------|

| compare  | 0000 : 0100h | RX address map size 1 register                                                                    |

|          | 0000 : 0154h | The RX packet address is greater than the value in the RX address map size 1 register             |

| compare  | 0000 : 0200h | RX address map size 1 register + RX address map size 2                                            |

|          |              | Since the RX packet address < the RX address map size 1 register + RX address map size 2 register |

| add      | 8200 : 0000h | RX address map offset 2 register                                                                  |

| subtract | 0000 : 0100h | RX address map size 1 register                                                                    |

|          | 8200 : 0054h | Translated address to DM643x device                                                               |

#### **Example 1. Address Translation Example**

Translated Address = RX Packet Address + RX Address Map Offset 4 Register -

```

The remote address 0400:0154h (or 0000 0054h) was translated to 8200:0054h on the DM643x (local)

device in this example.

The translated address for packets received on the serial interface is determined as follows:

If (RX Packet Address < RX Address Map Size 1 Register) {

Translated Address = RX Packet Address +

RX Address Map Offset 1 Register

} else if (RX Packet Address < (RX Address Map Size 1 Register +

RX Address Map Size 2 Register)) {

Translated Address = RX Packet Address +

RX Address Map Offset 2 Register -

RX Address Map Size 1 Register

} else if (RX Packet Address < (RX Address Map Size 1 Register +

RX Address Map Size 2 Register +

RX Address Map Size 3 Register)) {

Translated Address = RX Packet Address +

RX Address Map Offset 3 Register -

RX Address Map Size 1 Register -

RX Address Map Size 2 Register

} else if (RX Packet Address < (RX Address Map Size 1 Register +

RX Address Map Size 2 Register +

RX Address Map Size 3 Register +

```

RX Address Map Size 4 Register)) {

RX Address Map Size 1 Register -RX Address Map Size 2 Register -RX Address Map Size 3 Register

#### 2.9 Flow Control

} else {

Translated Address = 0x0

The VLYNQ module includes flow control features. The VLYNQ module automatically generates flow control enable requests, /P/, when the RX/inbound FIFOs (FIFO1 and FIFO2) resources are consumed. The FIFOs can take up to 16 32-bit words.

The remote device will begin transmitting idles, /l/, starting on the first byte boundary following reception of the request. When sufficient RX FIFO resources have been made available, a flow control disable request, /C/, is transmitted to the remote device. In response, the remote device will resume transmission of data. See Appendix A.

#### 2.10 Reset Considerations

#### 2.10.1 Software Reset Considerations

Peripheral clock and reset control is done through the power and sleep controller (PSC) module that is included with the device. For more information, see Section 2.13. Additionally, there is a software reset (the reset bit in the VLYNQ control register, CTRL) within the peripheral itself. Writing a 1 to the reset bit resets all of the internal state machines of the VLYNQ module, the serial interface is disabled, and the link is lost. The VLYNQ module remains in reset until the software clears the bit.

**Note:** When setting the reset bit, the VLYNQ status register (STAT) value is the only value that is set to the default value. All of the other VLYNQ memory-mapped registers retain their values prior to the software reset.

#### 2.10.2 Hardware Reset Considerations

When a hardware reset occurs, the VLYNQ peripheral resets its register values to the default values and the serial interface is disabled. After a hardware reset, the VLYNQ memory mapped registers and any chip-level registers that are associated with VLYNQ (for example, pin multiplexing registers) must be configured appropriately before data transmission can resume.

#### CAUTION

Be cautious when only resetting one of the VLYNQ devices after two or more VLYNQ devices have established a link. If only one of the VLYNQ devices is in reset, then no data activity can occur across the serial interface during the time of reset.

#### 2.11 Interrupt Support

#### 2.11.1 Interrupt Events and Requests

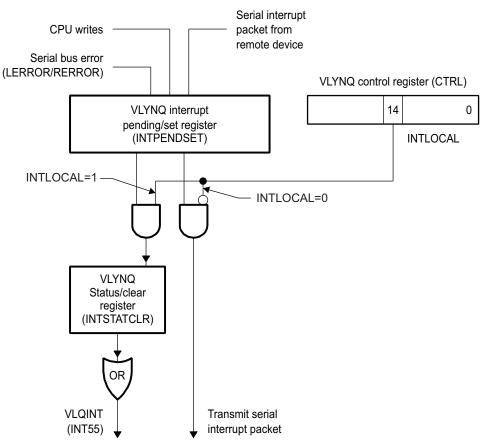

The VLYNQ module interrupt VLQINT is mapped to the interrupt controller (INT55). For more information on the interrupt controller, see the device-specific data manual.

Interrupts generate when bits are set in the VLYNQ interrupt pending/set register (INTPENDSET). Bits are set in the INTPENDSET register when any of the following occur:

- Writing directly to the INTPENDSET

- Remote interrupt (via the serial interrupt packet)

- Serial bus error

When INTPENDSET is a non-zero value, the method of forwarding the interrupt status depends on the state of the INTLOCAL bit in the VLYNQ control register (CTRL):

- When INTLOCAL = 0, the contents of INTPENDSET are inserted into an interrupt packet and sent over the serial interface. When packet transmission completes, the associated bits clear in INTPENDSET.

- When INTLOCAL = 1, bits in INTPENDSET transfer to the VLYNQ interrupt status/clear register (INTSTATCLR). The logical-OR of all of the bits in INTSTATCLR is driven onto the interrupt line, causing the VLYNQINT to pulse. If the system writes to INTSTATCLR while interrupts are still pending, a new VLQINT interrupt is generated.

For additional flexibility of interrupt handling, the INSTAT bit in the interrupt priority vector status/clear register (INTPRI) reports the highest priority interrupt asserted in INTPENDSET when INTLOCAL = 1 in CTRL. The VLYNQ interprets bit 0 of the INSTAT bits as the highest priority and interprets bit 31 as the lowest priority. The value that is returned when read is the vector of the highest priority interrupt. Software can clear that interrupt by writing back the vector value. Additionally, INTRPRI provides a read-only status bit (NOINTPEND) to indicate whether or not there are any pending interrupts in INTSTATCLR.

The VLYNQ interrupt generation mechanism is shown in Figure 8.

#### Figure 8. Interrupt Generation Mechanism Block Diagram

#### 2.11.2 Writes to Interrupt Pending/Set Register

As previously discussed, if the CPU writes to the VLYNQ interrupt pending/set register (INTPENDSET), then depending on the value of the INTLOCAL bit in the VLYNQ control register (CTRL), this will result in a local interrupt (to the device interrupt controller) or an interrupt packet transmitted over the serial interface to the remote device.

#### 2.11.3 Remote Interrupts

Remote interrupts occur when an interrupt packet is received over the serial interface from a remote device. The interrupt status is extracted from the packet and written to a location pointed to by the interrupt pointer register (INTPTR).

The INTPTR should contain the address of the interrupt pending/set register (INTPENDSET). To get INTPTR to contain the address of INTPENDSET, program INTPTR with a value of 14h (the offset for INTPENDSET). Additionally, the INT2CFG bit in the VLYNQ control register (CTRL) must be set to 1, dictating that the VLYNQ writes to a local register space (in this case, INTPENDSET).

Once an interrupt packet is received over the serial interface, the interrupt status is extracted and written to INTPENDSET. After the interrupt status is extracted and written to INTPENDSET, the interrupt generation occurs as previously described in Section 2.11.2.

The following summarizes the steps that are required to ensure that the device receives the remote interrupts:

- Program the VLYNQ interrupt pointer register (INTRPTR) with a value of 14h, which is the offset address of the VLYNQ interrupt/pending set register (INTPENDSET).

- Set the INT2CFG bit to 1 in the VLYNQ control register (CTRL).

#### 2.11.4 Serial Bus Error Interrupts

Due to erroneous transmit packets that are detected by remote devices (remote error) or errors in the inbound packets (local error), the serial bus errors result in the setting of the RERROR or LERROR bits in the VLYNQ status register (STAT).

Additionally, if the INTENABLE bit is set in the VLYNQ control register (CTRL), setting the RERROR or LERROR bits cause these status interrupts to post to the interrupt pending/set register (INTPENDSET), causing the VLYNQINT to be asserted to the CPU.

To ensure that serial bus errors result in interrupts to notify the application software, you must perform the following steps:

- 1. Set the INTENABLE bit to 1 in the VLYNQ control register (CTRL).

- Set the INTVEC bits in CTRL to point to a free bit in the VLYNQ interrupt pending/set register (INTPENDSET). The serial bus error should result in setting the bits in INTPENDSET that are not used by the application software for other interrupts (bit locations written directly in INTPENDSET or via remote interrupts).

- 3. During VLYNQ initialization, the RERROR bit is set after the VLYNQ module achieves a link. When the link bit is set in the VLYNQ status register (STAT), write a 1 to the RERROR bit. Writing a 1 to the RERROR bit clears the RERROR bit and prevents the software interrupt handler from seeing the first RERROR as a legitimate serial bus error interrupt.

#### 2.12 EDMA Event Support

The VLYNQ module on the DM643x device is classified as a master peripheral. Classification as a master peripheral normally implies that the peripheral is able to sustain its own transfers without relying on any external peripherals (for example, the system DMA, etc). However, the VLYNQ module does not have an internal DMA (as some other master peripherals).

Therefore, it is likely that the VLYNQ module can rely on the on-chip enhanced DMA (EDMA3) controller for performing burst transfer. The EDMA3 can still be used to perform burst transfers out to remote VLYNQ memory map (writes). This use model provides better throughput with less overhead.

**Note:** There is no VLYNQ event that allows hardware synchronization to occur with the EDMA3 controller on the DM643x device.

The VLYNQ module uses a 16-word deep FIFO to buffer the burst writes. Since the EDMA3 controller is much faster compared to the serial VLYNQ interface, a data back-up can occur. Therefore, configuring EDMA3 for optimal transfer size, etc. is essential.

#### 2.13 Power Management

The VLYNQ module can be placed in reduced-power modes to conserve power during periods of low activity. The power management of the VLYNQ module is controlled by the processor Power and Sleep Controller (PSC). The PSC acts as a master controller for power management for all of the peripherals on the device. For detailed information on power management procedures using the PSC, see the *TMS320DM643x DMP DSP Subsystem Reference Guide* (SPRU978).

The power conservation modes that are available via the PSC are:

- Idle/Disabled state : Idle/disabled state stops the clocks from going to the peripheral and prevents all of the register accesses. After re-enabling the peripheral from its idle state, all registers prior to setting in the disabled state are restored and data transmission proceeds. Re-initialization is not required.

- Synchronized reset : The synchronized reset state is similar to the power-on reset (POR) state. When

the processor is turned on, reset to the peripheral is asserted, then clocks to the peripheral are gated.

Registers reset to their default values. When powering-up after a synchronized reset, all of the VLYNQ

module registers must be reconfigured and the link must be re-established before data transmission.

If the serial clock is internally sourced, you can use the CLKDIV bit in the VLYNQ control register (CTRL) to divide the serial clock down. This saves normal mode operation power consumption (at the expense of reduced performance).

Additionally, the module provides the capability of auto-idling the serial clock domain (disable the VLYNQ CLK) when the serial clock is sourced from the DM643x device and the VLYNQ SCRUN pin is connected to the remote device. This allows power savings when there is no activity on the serial interface.

**Note:** There is no support for external wake-up for the VLYNQ module on the DM643x device. If the VLYNQ module on the DM643x device has been disabled via the PSC, then even though serial activity requests can be indicated from the remote VLYNQ device via the VLYNQ SCRUN pin, it does not allow the serial clock (VLYNQ CLK) to be sourced until the VLYNQ module is re-enabled via the PSC.

This can be configured by enabling the power management enable (PMEN) bit in the VLYNQ control registers (CTRL, 0 = disable, 1 = enable). This bit should only be set if the SCRUN pin is connected to the remote VLYNQ device.

The SCRUN pin is a bi-directional pin which is driven low whenever there is serial activity on the local or remote VLYNQ interface.

#### 2.14 Endianness Considerations

There are no endianness considerations for the VLYNQ peripheral.

#### 2.15 Emulation Considerations

During debug, the CPU may be halted for single stepping, bench marking, profiling, or other debug uses using the emulator. VLYNQ does not support emulation halts/suspend operation. VLYNQ operations continue during emulation halt/suspend.

#### 3 VLYNQ Port Registers

Table 4 describes the address space for the VLYNQ registers and memory.

| Block Name              | Start Address | End Address | Size      |  |

|-------------------------|---------------|-------------|-----------|--|

| VLYNQ Control Registers | 01E0 1000h    | 01E0 11FFh  | 512 bytes |  |

| Reserved                | 01E0 1200h    | 01E0 1FFFh  | -         |  |

| VLYNQ Remote Memory Map | 4C00 0000h    | 4FFF FFFFh  | 64 Mbytes |  |

#### Table 4. VLYNQ Register Address Space

Table 5 lists the memory-mapped registers for the VLYNQ port controller. See the device-specific data manual for the memory address of these registers.

The first 128 bytes map to the VLYNQ configuration registers that are maintained by the local (device) VLYNQ register control module while the second 128 bytes map to the remote configuration registers that are physically located in the remote device linked by the VLYNQ serial interface. Any access to the second set of registers causes VLYNQ to issue a read or write VLYNQ packet to be transmitted and only completes if a link is established between the two devices.

| Offset | Acronym    | Register Description                            | Section      |

|--------|------------|-------------------------------------------------|--------------|

| 0h     | REVID      | Revision Register                               | Section 3.1  |

| 4h     | CTRL       | Control Register                                | Section 3.2  |

| 8h     | STAT       | Status Register                                 | Section 3.3  |

| Ch     | INTPRI     | Interrupt Priority Vector Status/Clear Register | Section 3.4  |

| 10h    | INTSTATCLR | Interrupt Status/Clear Register                 | Section 3.5  |

| 14h    | INTPENDSET | Interrupt Pending/Set Register                  | Section 3.6  |

| 18h    | INTPTR     | Interrupt Pointer Register                      | Section 3.7  |

| 1Ch    | XAM        | Transmit Address Map Register                   | Section 3.8  |

| 20h    | RAMS1      | Receive Address Map Size 1 Register             | Section 3.9  |

| 24h    | RAMO1      | Receive Address Map Offset 1 Register           | Section 3.10 |

| 28h    | RAMS2      | Receive Address Map Size 2 Register             | Section 3.11 |

| 2Ch    | RAMO2      | Receive Address Map Offset 2 Register           | Section 3.12 |

| 30h    | RAMS3      | Receive Address Map Size 3 Register             | Section 3.13 |

| 34h    | RAMO3      | Receive Address Map Offset 3 Register           | Section 3.14 |

| 38h    | RAMS4      | Receive Address Map Size 4 Register             | Section 3.15 |

| 3Ch    | RAMO4      | Receive Address Map Offset 4 Register           | Section 3.16 |

| 40h    | CHIPVER    | Chip Version Register                           | Section 3.17 |

| 44h    | AUTNGO     | Auto Negotiation Register                       | Section 3.18 |

#### Table 5. VLYNQ Port Controller Registers

24

# 3.1 Revision Register (REVID)

The revision register (REVID) contains the major and minor revisions for the VLYNQ module. The REVID is shown in Figure 9 and described in Table 6.

#### Figure 9. Revision Register (REVID)

LEGEND: R = Read only; -n = value after reset

| Bit   | Field  | Value | Description             |

|-------|--------|-------|-------------------------|

| 31-16 | ID     | 01h   | Unique module ID.       |

| 15-8  | REVMAJ | 0-FFh | Major revision.         |

|       |        | 2h    | Current major revision. |

| 7-0   | REVMIN | 0-FFh | Minor revision.         |

|       |        | 6h    | Current minor revision. |

#### Table 6. Revision Register (REVID) Field Descriptions

# 3.2 Control Register (CTRL)

The control register (CTRL) determines operation of the VLYNQ module. The CTRL is shown in Figure 10 and described in Table 7.

### Figure 10. Control Register (CTRL)

| 31     | 30                                                      | 29 27     | 26 24       | 23    | 3     |     | 22      |      | 21     | 20    | 19     | 18    | 16     |

|--------|---------------------------------------------------------|-----------|-------------|-------|-------|-----|---------|------|--------|-------|--------|-------|--------|

| PMEN   | SCLKPUDIS                                               | Reserved  | RXSAMPELVAL | RTMVA | LIDWR | RTM | IENABLE | TXFA | STPATH | Rese  | erved  | CL    | KDIV   |

| R/W- 0 | R/W- 0                                                  | R-0       | R/W- 3h     | R/W   | /- 0  | R   | 2/W- 0  | R    | /W- 0  | R     | -0     | R     | /W- 0  |

| 15     | 14                                                      | 13        | 12          | 8     | 7     |     | 6       | 3    | 2      |       |        | 1     | 0      |

| CLKDIR | INTLOCAL                                                | INTENABLE | E INTVEC    |       | INT2C | FG  | Reserv  | ed   | AOPTDI | SABLE | E   IL | OOP   | RESET  |

| R/W- 0 | R/W- 0                                                  | R/W- 0    | R/W-0       |       | R/W-  | -0  | R-0     |      | R/W    | - 0   | R      | /W- 0 | R/W- 0 |

|        | I = C = ND, $P = N = A = A = A = A = A = A = A = A = A$ |           |             |       |       |     |         |      |        |       |        |       |        |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 7. Control Register (CTRL) Field Descriptions

| Bit   | Field       | Value | Description                                                                                                                                                                                                                                                                                                        |

|-------|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | PMEN        |       | Power management enable.                                                                                                                                                                                                                                                                                           |

|       |             | 0     | VLYNQ CLK is always active if it is set as an output (assuming that VLYNQ module is enabled).                                                                                                                                                                                                                      |

|       |             |       | If set as an output, VLYNQ CLK becomes inactive when there is no traffic over the serial bus.                                                                                                                                                                                                                      |

|       |             | 1     | The PMEN bit should only be set to 1 when the SCRUN is connected to the remote/external VLYNQ device.                                                                                                                                                                                                              |

| 30    | SCLKPUDIS   | 0     | Serial clock pull-up disable. Always write 0.                                                                                                                                                                                                                                                                      |

| 29-27 | Reserved    | 0     | Reserved. Always read as 0. Writes have no effect.                                                                                                                                                                                                                                                                 |

| 26-24 | RXSAMPELVAL | 0-7h  | RTM sample value. If the RTMENABLE bit is 0, the receive timing manager forces the value in the RXSAMPELVAL bit as the clock sample value. If the RTMENABLE bit is 1, then the value set by the RXSAMPELVAL bit is ignored. In order to modify the value, you must simultaneously write a 1 to the RTMVALIDWR bit. |

| 23    | RTMVALIDWR  |       | RTM valid write bit.                                                                                                                                                                                                                                                                                               |

|       |             | 0     | Will not allow writes to RXSAMPLEVAL bits.                                                                                                                                                                                                                                                                         |

|       |             | 1     | Will allow writes to RXSAMPLEVAL bits.                                                                                                                                                                                                                                                                             |

| 22    | RTMENABLE   |       | RTM enable bit.                                                                                                                                                                                                                                                                                                    |

|       |             | 0     | The receive timing manager uses the value set in the RXSAMPLEVAL bit as the clock sample value.                                                                                                                                                                                                                    |

|       |             | 1     | The receive timing manager is enabled. It automatically selects the receive clock.                                                                                                                                                                                                                                 |

| 21    | TXFASTPATH  | 0-1   | Transmit fast path. When set, the fastest path is chosen for the serial data.                                                                                                                                                                                                                                      |

| 20-19 | Reserved    | 0     | Reserved. Always read as 0. Writes have no effect.                                                                                                                                                                                                                                                                 |

| 18-16 | CLKDIV      | 0-7h  | Serial clock output divider.                                                                                                                                                                                                                                                                                       |

| 15    | CLKDIR      |       | Serial CLK direction. Determines whether the VLYNQ CLK is an input or an output.                                                                                                                                                                                                                                   |

|       |             | 0     | The VLYNQ CLK is externally sourced.                                                                                                                                                                                                                                                                               |

|       |             | 1     | The VLYNQ CLK is internally sourced and equal to the VLYNQ module system clock divided by the divider value set in the CLKDIV bit.                                                                                                                                                                                 |

| 14    | INTLOCAL    |       | Interrupt local.                                                                                                                                                                                                                                                                                                   |

|       |             | 0     | The interrupt is forwarded to the remote VLYNQ device over the serial interface as an interrupt packet.                                                                                                                                                                                                            |

|       |             | 1     | Interrupt is posted in the interrupt status/clear register and results in the assertion of the VLQINT to the device interrupt controllers.                                                                                                                                                                         |

| 13    | INTENABLE   |       | Interrupt enable.                                                                                                                                                                                                                                                                                                  |

|       |             | 0     | VLYNQ module status interrupts are ignored.                                                                                                                                                                                                                                                                        |

|       |             | 1     | VLYNQ module status interrupts (if RERROR or LERROR bits are set) are posted to the interrupt pending/set register.                                                                                                                                                                                                |

| 12-8  | INTVEC      | 0-1Fh | Interrupt vector. This bit indicates which bit in the interrupt pending/set register is set for VLYNQ module status (RERROR/LERROR) interrupts.                                                                                                                                                                    |

| Bit | Field       | Value | Description                                                                                                                                                                                                                                                                                   |

|-----|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | INT2CFG     |       | Interrupt to configuration register. Determines which register is written with the status contained in interrupt packets that are received over the serial interface. Always write 1 to this bit and configure the interrupt pointer register to point to the interrupt pending/set register. |

|     |             | 0     | Bits[31:2] of the interrupt pointer register are used to point to a system interrupt register.                                                                                                                                                                                                |

|     |             | 1     | The least significant 8 bits of the interrupt pointer register are used to point to a VLYNQ module local register (typically the interrupt pending/set register).                                                                                                                             |

| 6-3 | Reserved    | 0     | Reserved. Always read as 0. Writes have no effect.                                                                                                                                                                                                                                            |

| 2   | AOPTDISABLE |       | Address optimization disable.                                                                                                                                                                                                                                                                 |

|     |             | 0     | Address optimization is enabled, eliminating unnecessary address bytes.                                                                                                                                                                                                                       |

|     |             | 1     | Address optimization is disabled.                                                                                                                                                                                                                                                             |

| 1   | ILOOP       |       | Internal loop back.                                                                                                                                                                                                                                                                           |

|     |             | 0     | Normal operation.                                                                                                                                                                                                                                                                             |

|     |             | 1     | Serial transmit data is wrapped back to the serial receive data.                                                                                                                                                                                                                              |

| 0   | RESET       |       | Software reset. It does not reset the VLYNQ memory-mapped registers (except for the VLYNQ status register). You have to reprogram the VLYNQ registers if they must have a different value after a software reset.                                                                             |

|     |             | 0     | Normal operation.                                                                                                                                                                                                                                                                             |

|     |             | 1     | All internal state machines are reset, the serial interface is disabled, and the link is lost.                                                                                                                                                                                                |

# Table 7. Control Register (CTRL) Field Descriptions (continued)

# 3.3 Status Register (STAT)

The status register (STAT) is used to detect conditions that may be of interest to the system designer. The STAT is shown in Figure 11 and described in Table 8.

| 31     | 28       | 27       | 24       | 23       | 20    | 19    | 15     |

|--------|----------|----------|----------|----------|-------|-------|--------|

| Rese   | erved    | SWID     | THIN     | SWIDT    | HOUT  | Rese  | erved  |

| R      | -0       | R        | -0       | R        | -0    | R     | -0     |

| 14     |          |          | 12       | 11       | 10    | 9     | 8      |

|        | RXCURRE  | NTSAMPLE |          | RTM      | IFLOW | OFLOW | RERROR |

|        | R        | -0       |          | R-1      | R-0   | R-0   | W1C-0  |

| 7      | 6        | 5        | 4        | 3        | 2     | 1     | 0      |

| LERROR | NFEMPTY3 | NFEMPTY2 | NFEMPTY1 | NFEMPTY0 | SPEND | MPEND | LINK   |

| W1C-0  | R-0      | R-0      | R-0      | R-0      | R-0   | R-0   | R-0    |

#### Figure 11. Status Register (STAT)

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear bit; -n = value after reset; x= reset value is indeterminate

| Bit   | Field           | Value | Description                                                                                                                                                        |

|-------|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-28 | Reserved        | 0     | Reserved. Always read as 0. Writes have no effect.                                                                                                                 |

| 27-24 | SWIDTHIN        | 0-Fh  | Size of the inbound serial data. Indicates the number of receive pins that are being used to establish the serial interface.                                       |

|       |                 | 0     | No pins used                                                                                                                                                       |

|       |                 | 1h    | 1 RX pin used                                                                                                                                                      |

|       |                 | 2h    | 2 RX pins used                                                                                                                                                     |

|       |                 | 3h    | 3 RX pins used                                                                                                                                                     |

|       |                 | 4h    | 4 RX pins used                                                                                                                                                     |

|       |                 | 5h-Fh | Reserved                                                                                                                                                           |

| 23-20 | SWIDTHOUT       | 0-Fh  | Size of the outbound serial data. Indicates the number of transmit pins that are being used to establish the serial interface.                                     |

|       |                 | 0     | No pins used                                                                                                                                                       |

|       |                 | 1h    | 1 TX pin used                                                                                                                                                      |

|       |                 | 2h    | 2 TX pins used                                                                                                                                                     |

|       |                 | 3h    | 3 TX pins used                                                                                                                                                     |

|       |                 | 4h    | 4 TX pins used                                                                                                                                                     |

|       |                 | 5h-Fh | Reserved                                                                                                                                                           |

| 19-15 | Reserved        | 0     | Reserved. Always read as 0. Writes have no effect.                                                                                                                 |

| 14-12 | RXCURRENTSAMPLE | 0-Fh  | Current RTM sample. Indicates the current clock sample value used by RTM.                                                                                          |

| 11    | RTM             | 1     | RTM enable. Always read as 1. Indicates that the VLYNQ module on the DM643x DMSoC has the receive timing manager (RTM).                                            |

| 10    | IFLOW           |       | Inbound flow control.                                                                                                                                              |

|       |                 | 0     | Free to transmit.                                                                                                                                                  |

|       |                 | 1     | Indicates that a flow control enable request has been received and has stalled transmit until a flow control disable request is received.                          |

| 9     | OFLOW           |       | Outbound flow control. Indicates the status of the two inbound FIFOs (FIFO1 or FIFO2).                                                                             |

|       |                 | 0     | Indicates that the internal flow control threshold is not yet reached.                                                                                             |

|       |                 | 1     | Indicates that the internal flow control threshold has been reached (FIFO1 or FIFO2 is full) and a flow control enable request has been sent to the remote device. |

#### Table 8. Status Register (STAT) Field Descriptions

| Table 8. Status Register | (STAT) Field | Descriptions | (continued) |

|--------------------------|--------------|--------------|-------------|

|--------------------------|--------------|--------------|-------------|

| Bit | Field    | Value | Description                                                                                                                                                                          |

|-----|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | RERROR   |       | Remote Error. Write a 1 to this bit to clear it.                                                                                                                                     |

|     |          | 0     | No error                                                                                                                                                                             |

|     |          | 1     | This bit indicates that a downstream VLYNQ module has detected a packet error. This bit is set when an error indication, /E/, is received from the serial interface. See Appendix A. |

|     |          |       | If this bit is set, and the INTENABLE (bit 13 in VLYNQ control register) is also set, it asserts the VLYNQ interrupt (VLQINT).                                                       |

| 7   | LERROR   |       | Local error. Write a 1 to this bit to clear it.                                                                                                                                      |

|     |          | 0     | No error.                                                                                                                                                                            |

|     |          | 1     | This bit indicates that an inbound packet contains an error that is detected by the local VLYNQ module.                                                                              |

|     |          |       | If this bit is set, and the INTENABLE (bit 13 in VLYNQ control register) is also set, it asserts the VLYNQ interrupt (VLQINT).                                                       |

| 6   | NFEMPTY3 |       | FIFO 3 is not empty.                                                                                                                                                                 |

|     |          | 0     | Indicates that the slave command FIFO is empty.                                                                                                                                      |

|     |          | 1     | Indicates that the slave command FIFO is not empty.                                                                                                                                  |

| 5   | NFEMPTY2 |       | FIFO 2 is not empty.                                                                                                                                                                 |

|     |          | 0     | Indicates that the slave data FIFO is empty.                                                                                                                                         |

|     |          | 1     | Indicates that the slave data FIFO is not empty.                                                                                                                                     |

| 4   | NFEMPTY1 |       | FIFO 1 is not empty.                                                                                                                                                                 |

|     |          | 0     | Indicates that the master command FIFO is empty.                                                                                                                                     |