# SM320F2812-HT Digital Signal Processor

# **Data Manual**

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Literature Number: SGUS062A June 2009-Revised April 2010

# **Contents**

| 1 | Featu      | ıres    |                                                  | <u>11</u> |

|---|------------|---------|--------------------------------------------------|-----------|

|   | 1.1        | SUPPO   | ORTS EXTREME TEMPERATURE APPLICATIONS            | 12        |

| 2 | Intro      | duction |                                                  | <u>13</u> |

|   | 2.1        | Descrip | tion                                             | <u>13</u> |

|   | 2.2        | Device  | Summary                                          | <u>14</u> |

|   | 2.3        | Die Lay | out                                              | <u>15</u> |

|   | 2.4        | Pin Ass | ignments                                         | <u>16</u> |

|   | 2.5        | •       | Descriptions                                     |           |

| 3 | Func       |         | Overview                                         |           |

|   | 3.1        | -       | y Map                                            | _         |

|   | 3.2        |         | escriptions                                      |           |

|   |            | 3.2.1   | C28x CPU                                         |           |

|   |            | 3.2.2   | Memory Bus (Harvard Bus Architecture)            |           |

|   |            | 3.2.3   | Peripheral Bus                                   |           |

|   |            | 3.2.4   | Real-Time JTAG and Analysis                      |           |

|   |            | 3.2.5   | External Interface (XINTF)                       |           |

|   |            | 3.2.6   | Flash                                            |           |

|   |            | 3.2.7   | L0, L1, H0 SARAMs                                |           |

|   |            | 3.2.8   | Boot ROM                                         |           |

|   |            | 3.2.9   | Security                                         |           |

|   |            | 3.2.10  | Peripheral Interrupt Expansion (PIE) Block       |           |

|   |            | 3.2.11  | External Interrupts (XINT1, XINT2, XINT13, XNMI) |           |

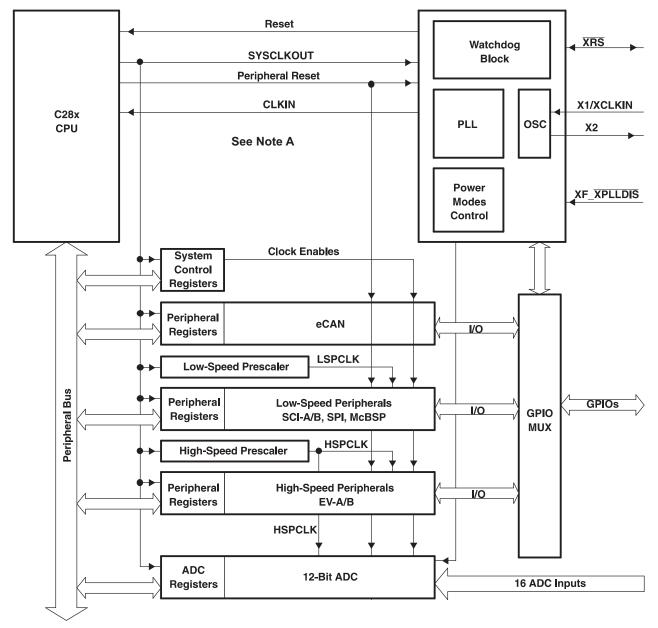

|   |            | 3.2.12  | Oscillator and PLL                               |           |

|   |            | 3.2.13  | Watchdog                                         |           |

|   |            | 3.2.14  | Peripheral Clocking                              | _         |

|   |            | 3.2.15  | Low-Power Modes                                  |           |

|   |            | 3.2.16  | Peripheral Frames 0, 1, 2 (PFn)                  |           |

|   |            | 3.2.17  | General-Purpose Input/Output (GPIO) Multiplexer  |           |

|   |            | 3.2.18  | 32-Bit CPU Timers (0, 1, 2)                      |           |

|   |            | 3.2.19  | Control Peripherals                              |           |

|   |            | 3.2.20  | Serial Port Peripherals                          |           |

|   | 3.3        | Registe | - T                                              | <u>36</u> |

|   | 3.4        |         | Emulation Registers                              |           |

|   | 3.5        |         | Il Interface, XINTF                              |           |

|   |            | 3.5.1   | Timing Registers                                 |           |

|   | 0.0        | 3.5.2   | XREVISION Register                               |           |

|   | 3.6        |         | ots                                              |           |

|   | 0.7        | 3.6.1   | External Interrupts                              |           |

|   | 3.7<br>3.8 | •       | Control                                          |           |

|   | 5.0        | 3.8.1   | Loss of Input Clock                              |           |

|   | 3.9        |         | sed Clock Module                                 |           |

|   |            |         | Reference Oscillator Clock Option                |           |

|   | 3.10       |         |                                                  |           |

|   | 3.11       |         | log Blockwer Modes Block                         |           |

|   | 3.12       | LOW-PO  | WEI IVIUUES DIUCK                                | 51        |

#### www.ti.com

| 4 | Perip | pherals                                                                                                                     | <u>52</u> |

|---|-------|-----------------------------------------------------------------------------------------------------------------------------|-----------|

|   | 4.1   | 32-Bit CPU-Timers 0/1/2                                                                                                     | <u>52</u> |

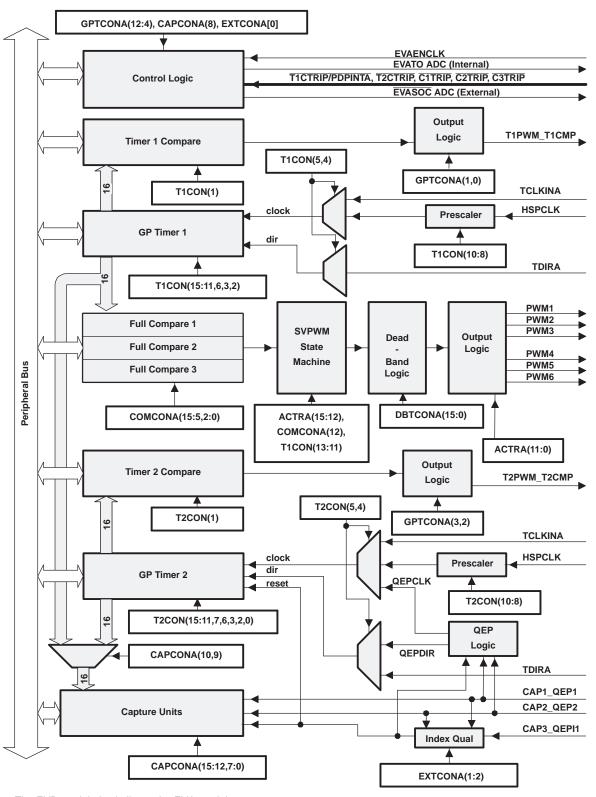

|   | 4.2   | Event Manager Modules (EVA, EVB)                                                                                            | <u>55</u> |

|   |       | 4.2.1 General-Purpose (GP) Timers                                                                                           | <u>58</u> |

|   |       | 4.2.2 Full-Compare Units                                                                                                    | <u>58</u> |

|   |       | 4.2.3 Programmable Deadband Generator                                                                                       | <u>58</u> |

|   |       | 4.2.4 PWM Waveform Generation                                                                                               | <u>58</u> |

|   |       | 4.2.5 Double Update PWM Mode                                                                                                | <u>58</u> |

|   |       | 4.2.6 PWM Characteristics                                                                                                   | <u>59</u> |

|   |       | 4.2.7 Capture Unit                                                                                                          | <u>59</u> |

|   |       | 4.2.8 Quadrature-Encoder Pulse (QEP) Circuit                                                                                | <u>59</u> |

|   |       | 4.2.9 External ADC Start-of-Conversion                                                                                      | <u>59</u> |

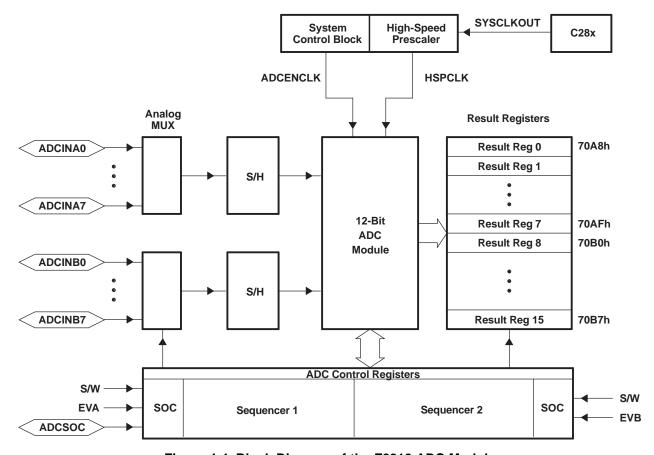

|   | 4.3   | Enhanced Analog-to-Digital Converter (ADC) Module                                                                           | <u>60</u> |

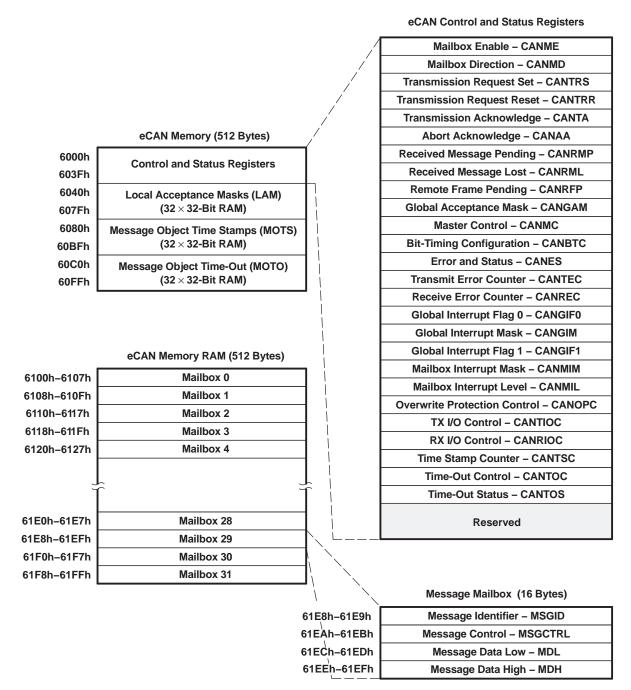

|   | 4.4   | Enhanced Controller Area Network (eCAN) Module                                                                              | <u>65</u> |

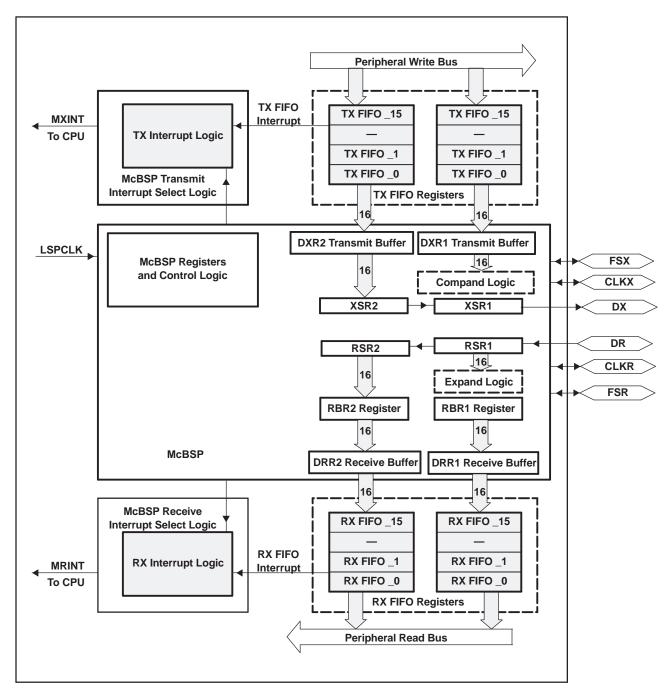

|   | 4.5   | Multichannel Buffered Serial Port (McBSP) Module                                                                            | <u>69</u> |

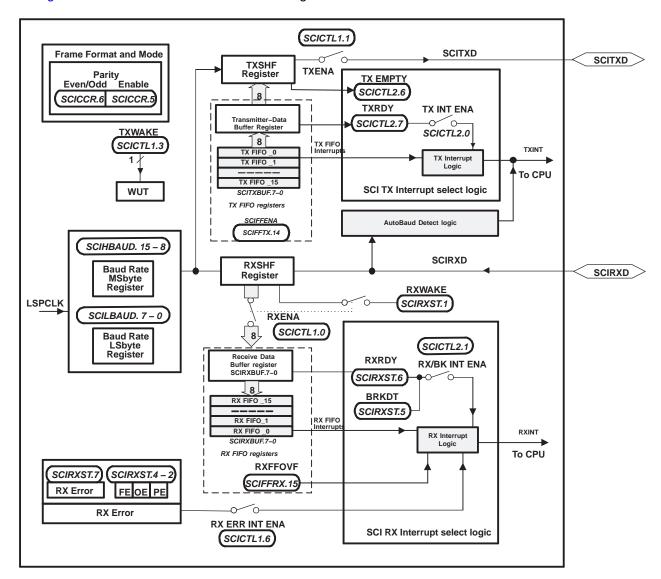

|   | 4.6   | Serial Communications Interface (SCI) Module                                                                                | 73        |

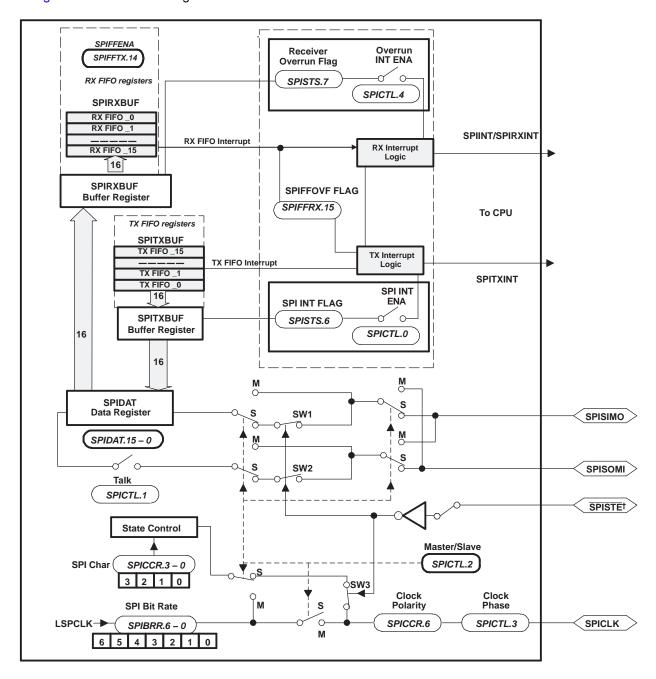

|   | 4.7   | Serial Peripheral Interface (SPI) Module                                                                                    | 76        |

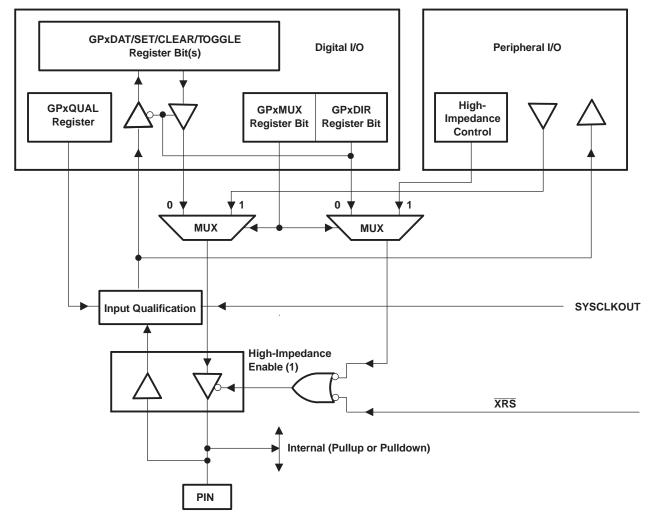

|   | 4.8   | GPIO MUX                                                                                                                    | 79        |

| 5 | Deve  | elopment Support                                                                                                            | 82        |

|   | 5.1   | Device and Development Support Tool Nomenclature                                                                            | <u>82</u> |

|   | 5.2   | Documentation Support                                                                                                       |           |

| 6 | Elect | trical Specifications                                                                                                       |           |

|   | 6.1   | Absolute Maximum Ratings                                                                                                    |           |

|   | 6.2   | Recommended Operating Conditions                                                                                            |           |

|   | 6.3   | Electrical Characteristics                                                                                                  | <u>86</u> |

|   | 6.4   | Current Consumption by Power-Supply Pins Over Recommended Operating Conditions During  Low-Power Modes at 150-MHz SYSCLKOUT | 88        |

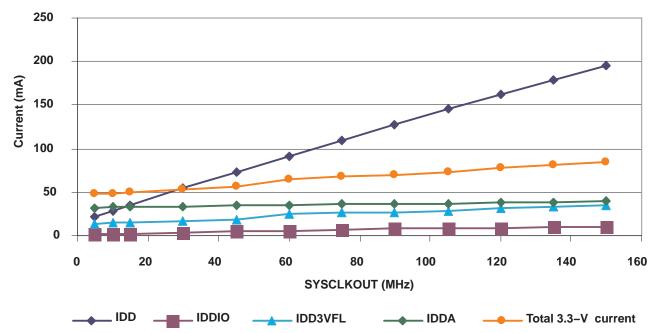

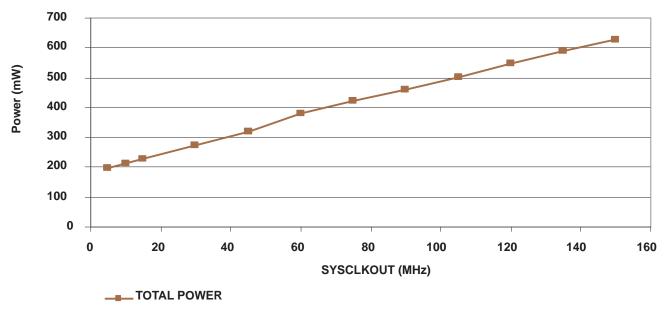

|   | 6.5   | Current Consumption Graphs                                                                                                  |           |

|   | 6.6   | Reducing Current Consumption                                                                                                |           |

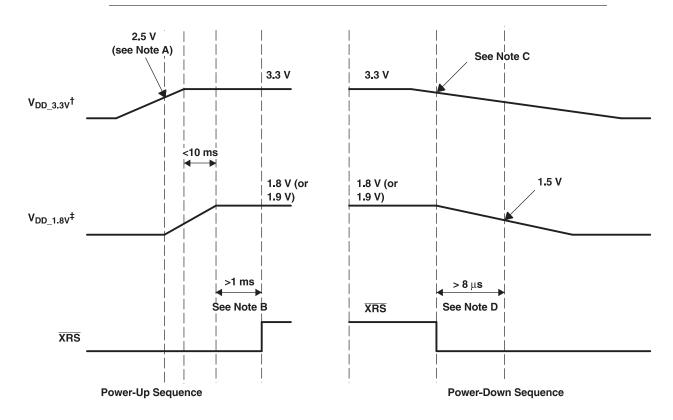

|   | 6.7   | Power Sequencing Requirements                                                                                               |           |

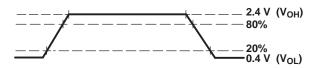

|   | 6.8   | Signal Transition Levels                                                                                                    |           |

|   | 6.9   | Timing Parameter Symbology                                                                                                  |           |

|   | 6.10  | General Notes on Timing Parameters                                                                                          |           |

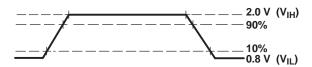

|   | 6.11  | Test Load Circuit                                                                                                           |           |

|   | 6.12  | Device Clock Table                                                                                                          |           |

|   | 6.13  | Clock Requirements and Characteristics                                                                                      | _         |

|   |       | 6.13.1 Input Clock Requirements                                                                                             |           |

|   |       | 6.13.2 Output Clock Characteristics                                                                                         |           |

|   | 6.14  | Reset Timing                                                                                                                |           |

|   | 6.15  | Low-Power Mode Wakeup Timing                                                                                                |           |

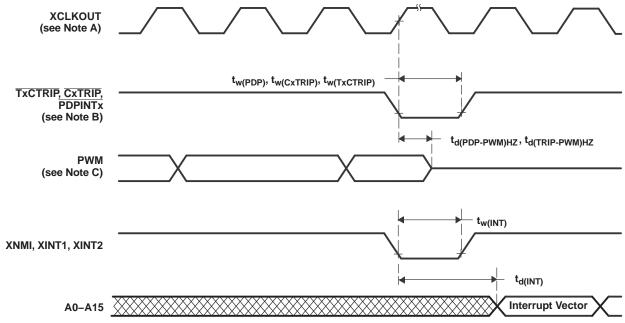

|   | 6.16  | Event Manager Interface                                                                                                     |           |

|   |       | 6.16.1 PWM Timing                                                                                                           | 104       |

|   |       | 6.16.2 Interrupt Timing                                                                                                     |           |

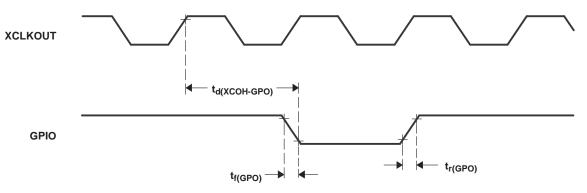

|   | 6.17  | General-Purpose Input/Output (GPIO) – Output Timing                                                                         |           |

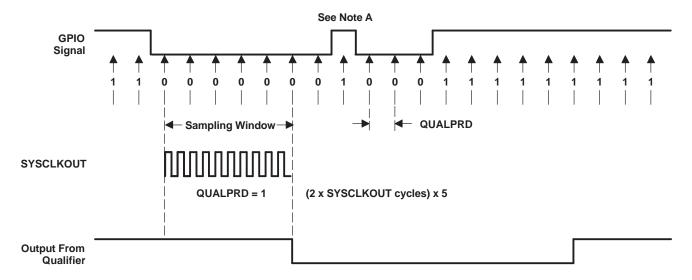

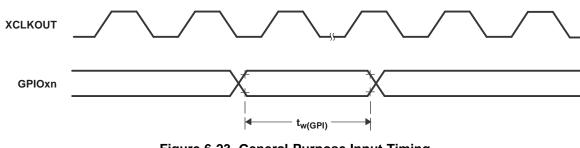

|   | 6.18  | General-Purpose Input/Output (GPIO) – Input Timing                                                                          |           |

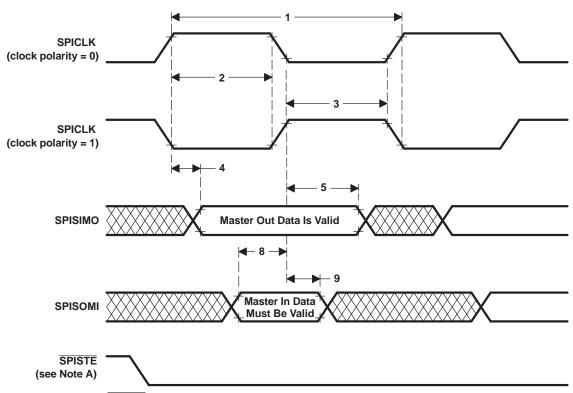

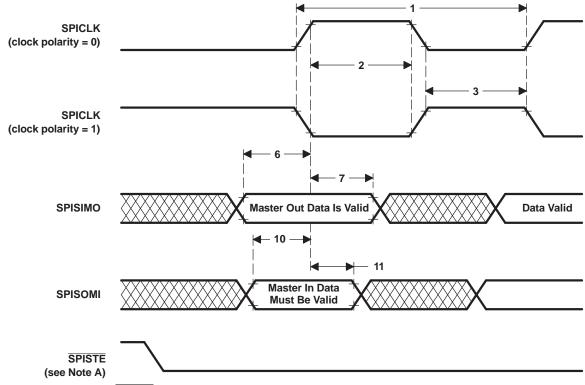

|   | 6.19  | SPI Master Mode Timing                                                                                                      |           |

|   |       |                                                                                                                             |           |

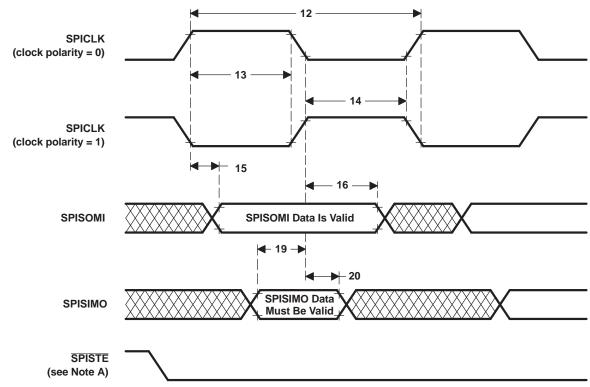

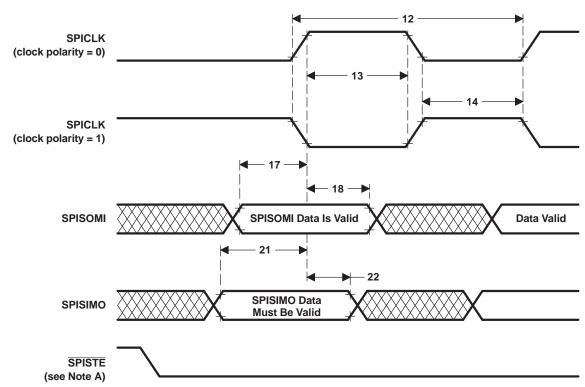

| 6.20  | SPI Slav | ve Mode T    | iming                                                           | <u>113</u> |

|-------|----------|--------------|-----------------------------------------------------------------|------------|

| 6.21  | Externa  | I Interface  | (XINTF) Timing                                                  | <u>117</u> |

| 6.22  | XINTF S  | Signal Aligr | nment to XCLKOUT                                                | 121        |

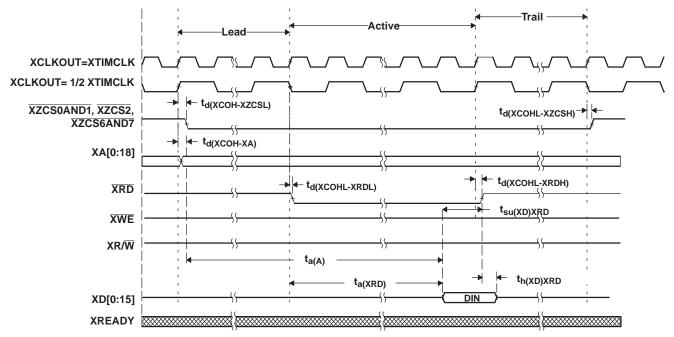

| 6.23  | Externa  | I Interface  | Read Timing                                                     | 122        |

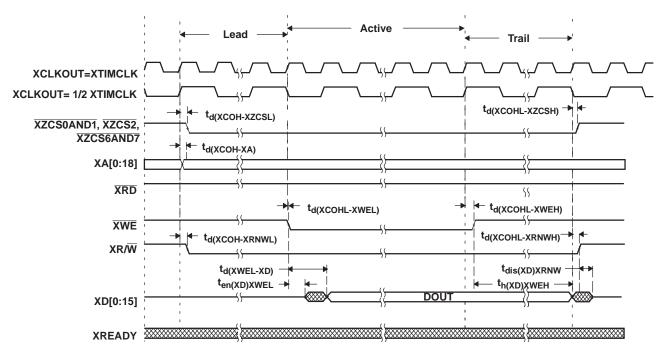

| 6.24  | Externa  | I Interface  | Write Timing                                                    | 123        |

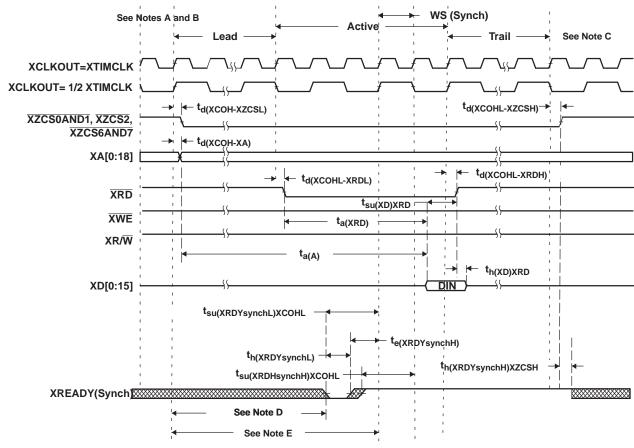

| 6.25  | Externa  | I Interface  | Ready-on-Read Timing With One External Wait State               | 125        |

| 6.26  | Externa  | I Interface  | Ready-on-Write Timing With One External Wait State              | 128        |

| 6.27  | XHOLD    | and XHOL     | _DA                                                             | 131        |

| 6.28  | XHOLD    | /XHOLDA      | Timing                                                          | 132        |

| 6.29  | On-Chip  | Analog-to    | -Digital Converter                                              | <u>134</u> |

|       | 6.29.1   | ADC Abs      | olute Maximum Ratings                                           | <u>134</u> |

|       | 6.29.2   | ADC Elec     | ctrical Characteristics Over Recommended Operating Conditions   | 135        |

|       | 6.29.3   | Current C    | Consumption for Different ADC Configurations (at 25-MHz ADCCLK) | <u>136</u> |

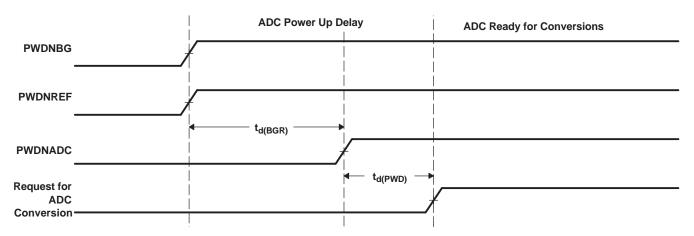

|       | 6.29.4   | ADC Pow      | ver-Up Control Bit Timing                                       | 137        |

|       | 6.29.5   | Detailed I   | Description                                                     |            |

|       |          | 6.29.5.1     | Reference Voltage                                               |            |

|       |          | 6.29.5.2     | Analog Inputs                                                   | <u>138</u> |

|       |          | 6.29.5.3     | Converter                                                       | 138        |

|       |          | 6.29.5.4     | Conversion Modes                                                | <u>138</u> |

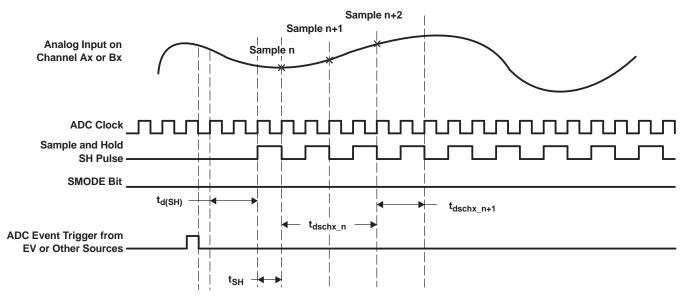

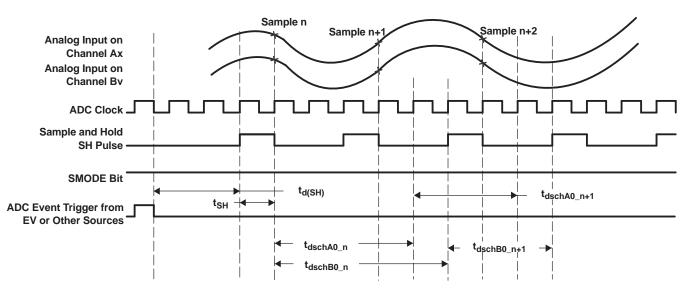

|       | 6.29.6   | Sequentia    | al Sampling Mode (Single Channel) (SMODE = 0)                   | 138        |

|       | 6.29.7   |              | eous Sampling Mode (Dual-Channel) (SMODE = 1)                   |            |

|       | 6.29.8   | Definition   | s of Specifications and Terminology                             |            |

|       |          | 6.29.8.1     | Integral Nonlinearity                                           |            |

|       |          | 6.29.8.2     | Differential Nonlinearity                                       |            |

|       |          | 6.29.8.3     | Zero Offset                                                     |            |

|       |          | 6.29.8.4     | Gain Error                                                      | <u>141</u> |

|       |          | 6.29.8.5     | Signal-to-Noise Ratio + Distortion (SINAD)                      | <u>141</u> |

|       |          | 6.29.8.6     | Effective Number of Bits (ENOB)                                 |            |

|       |          | 6.29.8.7     | Total Harmonic Distortion (THD)                                 | <u>141</u> |

|       |          | 6.29.8.8     | Spurious Free Dynamic Range (SFDR)                              |            |

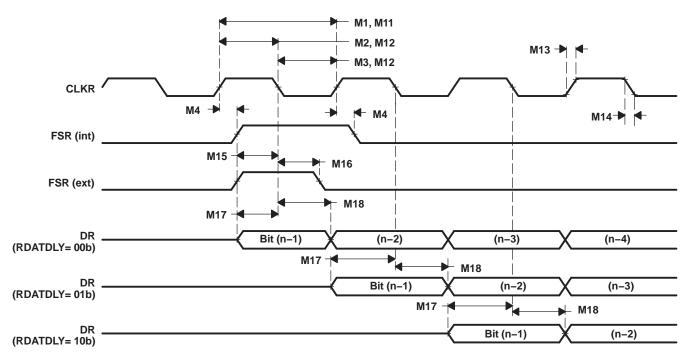

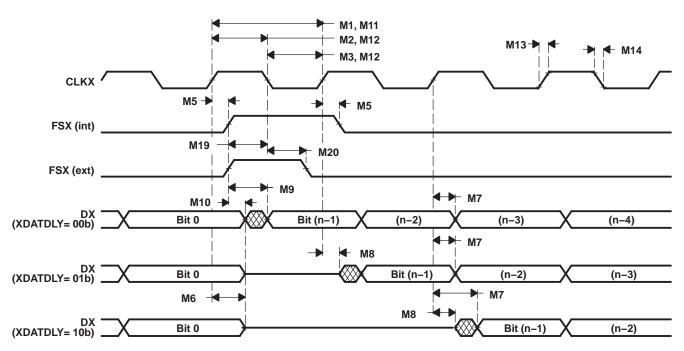

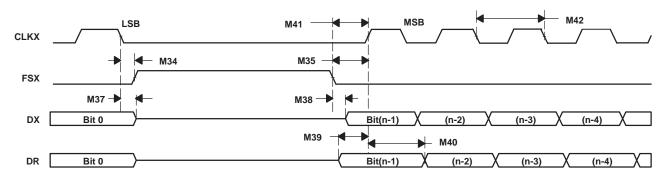

| 6.30  | Multicha |              | red Serial Port (McBSP) Timing                                  |            |

|       | 6.30.1   |              | ransmit and Receive Timing                                      |            |

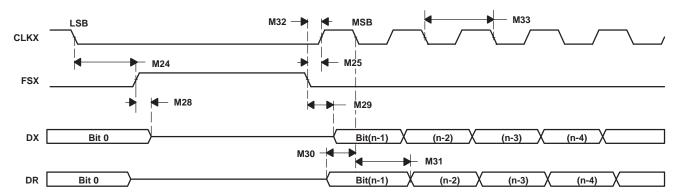

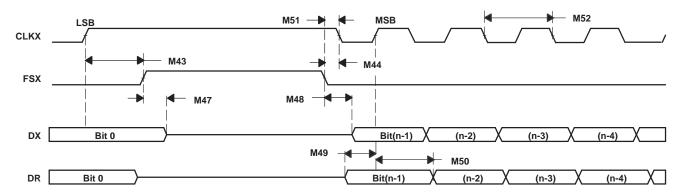

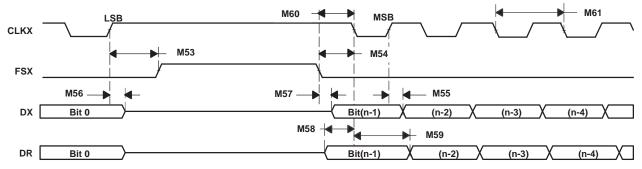

|       | 6.30.2   |              | s SPI Master or Slave Timing                                    |            |

| 6.31  |          | •            |                                                                 |            |

| Maala | 6.31.1   |              | ended Operating Conditions                                      |            |

|       |          |              |                                                                 |            |

7

# **List of Figures**

| 2-1  | SM320F2812 Die Layout                                                | <u>15</u>  |

|------|----------------------------------------------------------------------|------------|

| 2-2  | SM320F2812 172-Pin HFG CQFP (Top View)                               | <u>16</u>  |

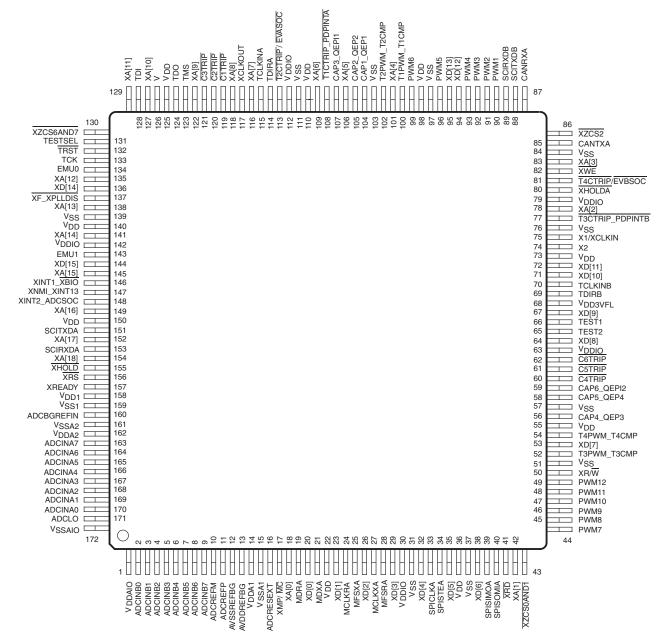

| 3-1  | Functional Block Diagram                                             | 28         |

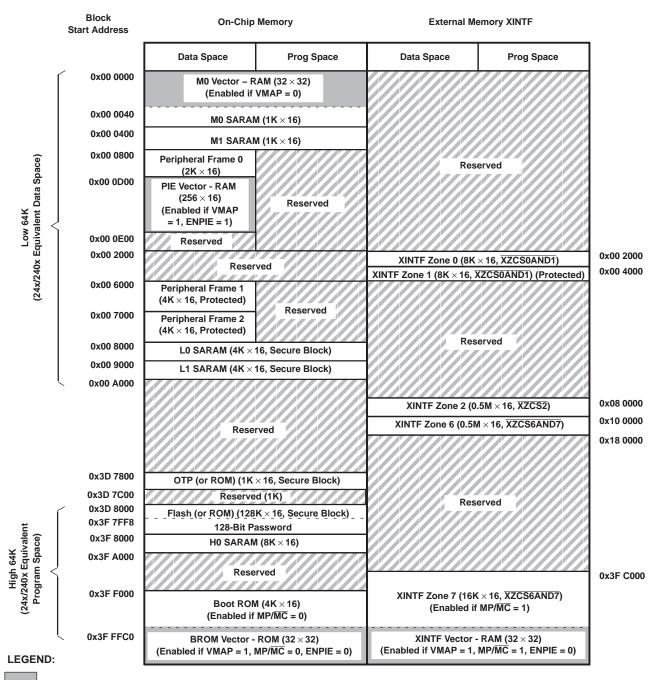

| 3-2  | F2812 Memory Map (See Notes A. Through G.)                           | 28         |

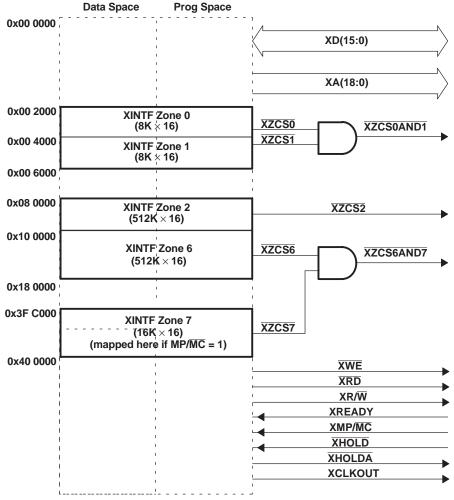

| 3-3  | External Interface Block Diagram                                     | <u>40</u>  |

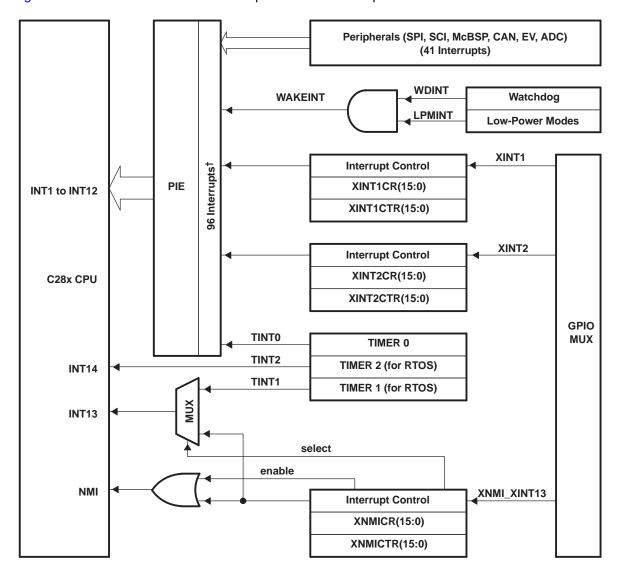

| 3-4  | Interrupt Sources                                                    | <u>42</u>  |

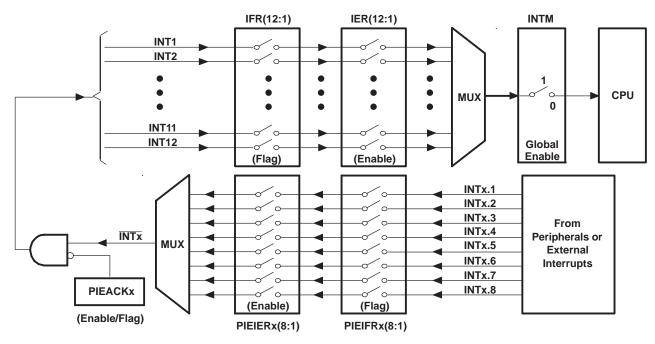

| 3-5  | Multiplexing of Interrupts Using the PIE Block                       | <u>43</u>  |

| 3-6  | Clock and Reset Domains                                              | <u>46</u>  |

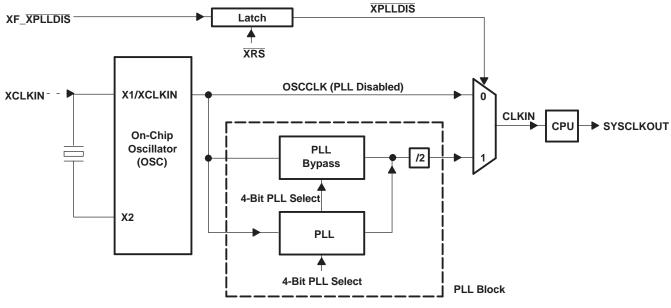

| 3-7  | OSC and PLL Block                                                    | <u>48</u>  |

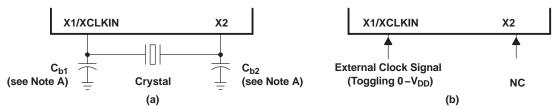

| 3-8  | Recommended Crystal/Clock Connection                                 | <u>49</u>  |

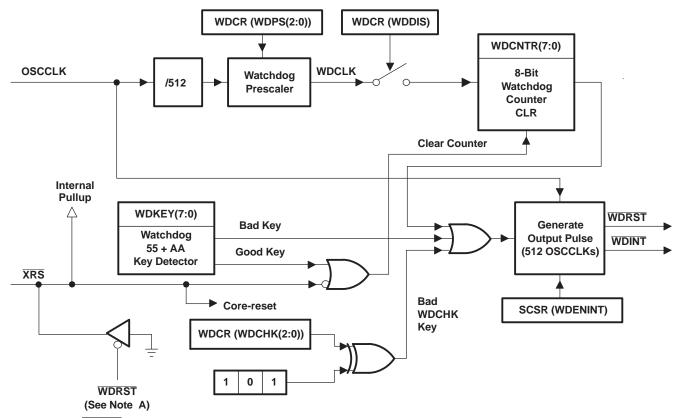

| 3-9  | Watchdog Module                                                      | <u>50</u>  |

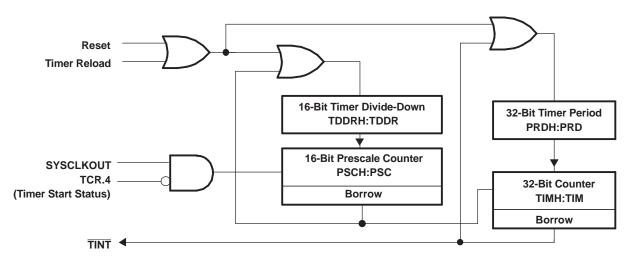

| 4-1  | CPU-Timers                                                           | <u>52</u>  |

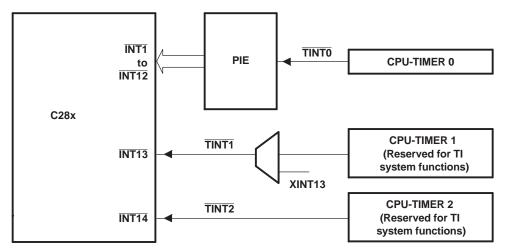

| 4-2  | CPU-Timer Interrupts Signals and Output Signal (See Notes A. and B.) | <u>53</u>  |

| 4-3  | Event Manager A Functional Block Diagram (See Note A.)               | <u>58</u>  |

| 4-4  | Block Diagram of the F2812 ADC Module                                | <u>61</u>  |

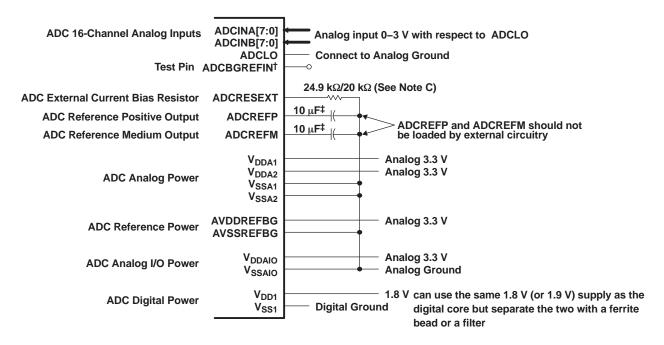

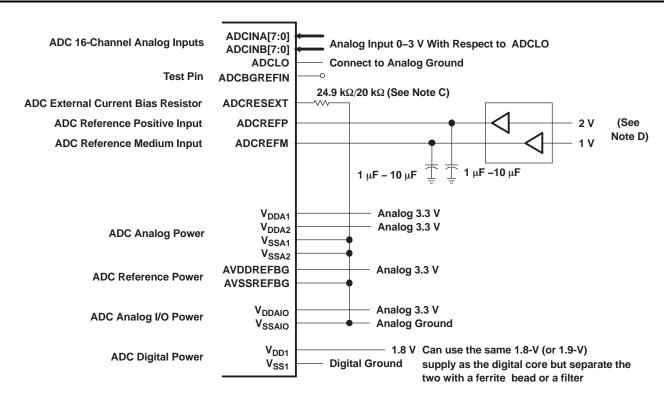

| 4-5  | ADC Pin Connections With Internal Reference (See Notes A and B)      | <u>62</u>  |

| 4-6  | ADC Pin Connections With External Reference                          | <u>63</u>  |

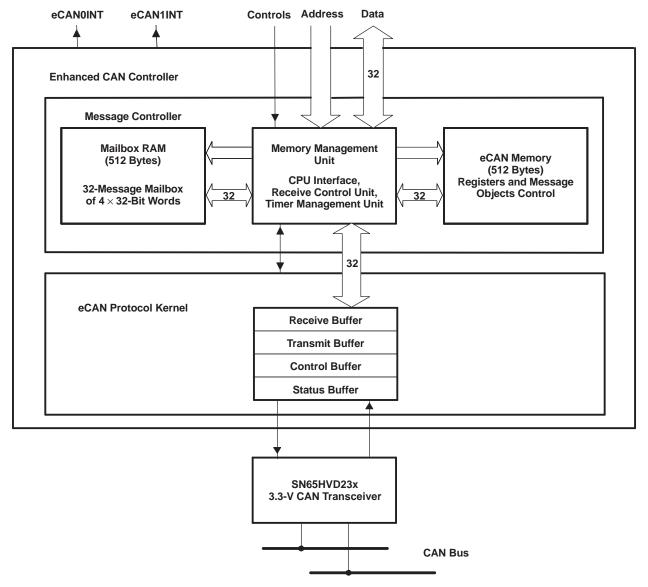

| 4-7  | eCAN Block Diagram and Interface Circuit                             | <u>66</u>  |

| 4-8  | eCAN Memory Map                                                      | <u>67</u>  |

| 4-9  | McBSP Module With FIFO                                               | <u>70</u>  |

| 4-10 | Serial Communications Interface (SCI) Module Block Diagram           | <u>75</u>  |

| 4-11 | Serial Peripheral Interface Module Block Diagram (Slave Mode)        | <u>78</u>  |

| 4-12 | GPIO/Peripheral Pin Multiplexing                                     | <u>81</u>  |

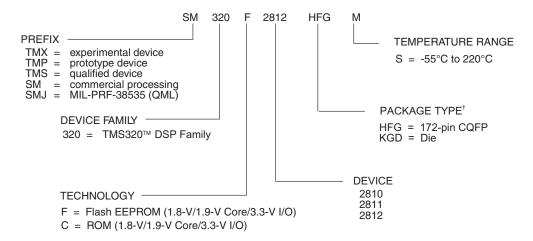

| 5-1  | 28x Device Nomenclature                                              | 83         |

| 6-1  | SM320F2812-HT Life Expectancy Curve                                  | 87         |

| 6-2  | Typical Current Consumption Over Frequency                           | <u>89</u>  |

| 6-3  | Typical Power Consumption Over Frequency                             | 90         |

| 6-4  | F2812 Typical Power-Up and Power-Down Sequence – Option 2            | 91         |

| 6-5  | Output Levels                                                        | 92         |

| 6-6  | Input Levels                                                         | 92         |

| 6-7  | 3.3-V Test Load Circuit                                              | 93         |

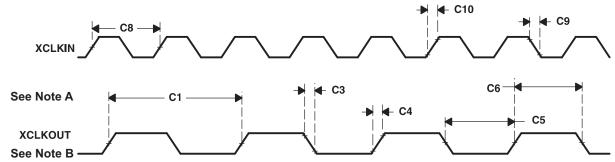

| 6-8  | Clock Timing                                                         | 96         |

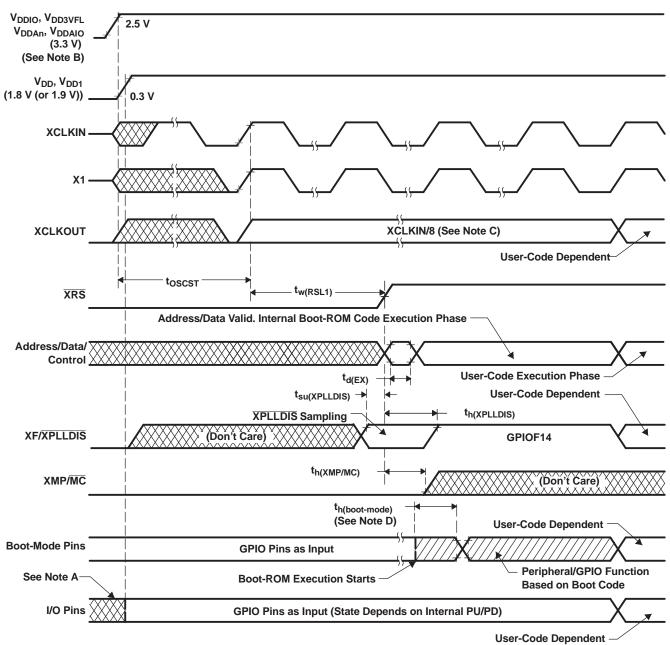

| 6-9  | Power-on Reset in Microcomputer Mode (XMP/MC = 0) (See Note A)       | 98         |

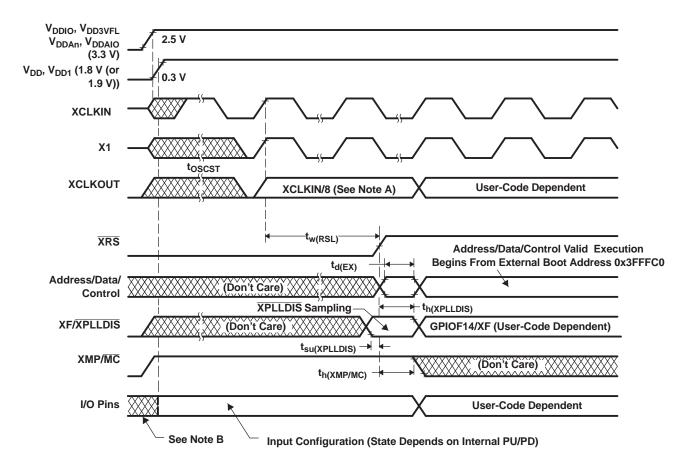

| 6-10 | Power-on Reset in Microprocessor Mode (XMP/MC = 1)                   | 99         |

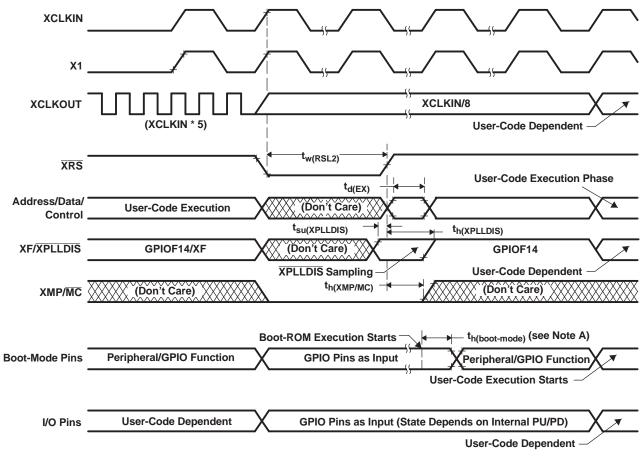

| 6-11 | Warm Reset in Microcomputer Mode                                     | 99         |

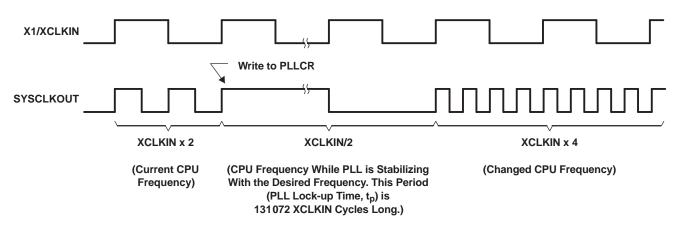

| 6-12 | Effect of Writing Into PLLCR Register                                | 99         |

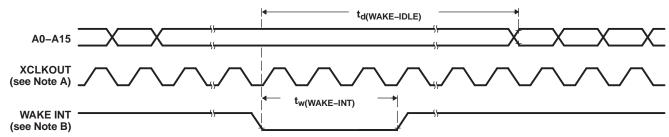

| 6-13 | IDLE Entry and Exit Timing                                           | <u>100</u> |

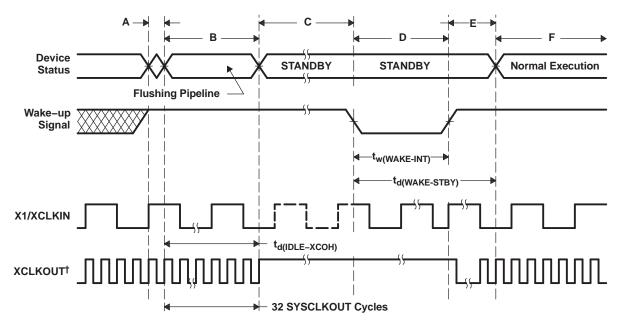

| 6-14 | STANDBY Entry and Exit Timing                                        | 102        |

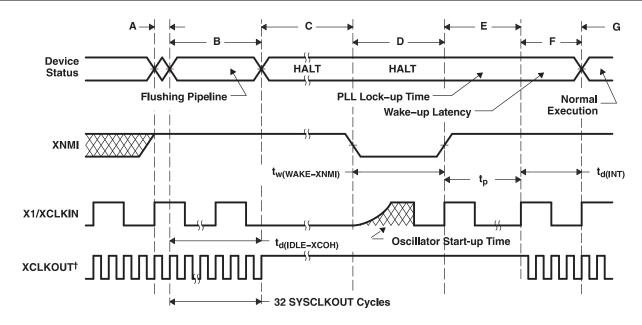

| 6-15 | HALT Wakeup Using XNMI                                               | <u>104</u> |

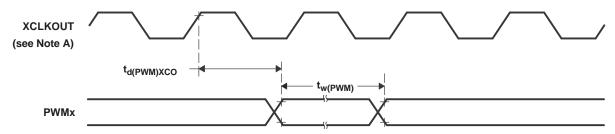

| 6-16 | PWM Output Timing                                                    | <u>105</u> |

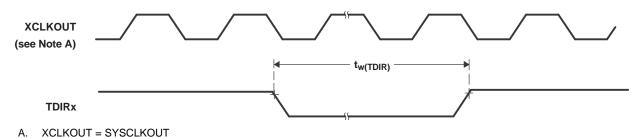

| 6-17 | TDIRx Timing                                                         | <u>106</u> |

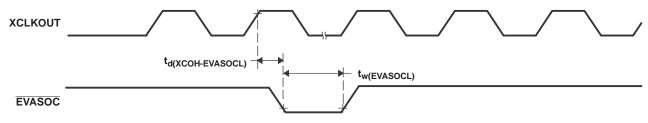

| 6-18 | EVASOC Timing                                                        | <u>106</u> |

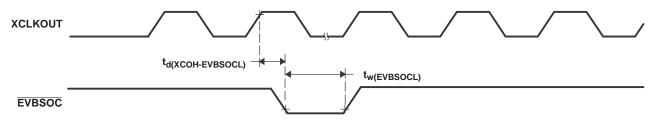

| 6-19 | EVBSOC Timing                                                        | <u>106</u> |

| 6-20 | External Interrupt Timing                                            | <u>107</u> |

| 6-21 | General-Purpose Output Timing                                        | <u>108</u> |

| 6-22 | GPIO Input Qualifier – Example Diagram for QUALPRD = 1               | <u>108</u> |

# SM320F2812-HT

| SGUS062A- | II INE | 2009_ | REVISE | η ΔΡΙ | DII 20 | <b>11</b> |

|-----------|--------|-------|--------|-------|--------|-----------|

| 3GU3U0ZA- | JUINE  | 2009- | KEVIOE | U AFI | ᇇᇉᇫ    | JIL       |

www.ti.com

| 6-23 | General-Purpose Input Timing                                 | <u>109</u> |

|------|--------------------------------------------------------------|------------|

| 6-24 | SPI Master Mode External Timing (Clock Phase = 0)            | <u>110</u> |

| 6-25 | SPI Master External Timing (Clock Phase = 1)                 | <u>112</u> |

| 6-26 | SPI Slave Mode External Timing (Clock Phase = 0)             | <u>114</u> |

| 6-27 | SPI Slave Mode External Timing (Clock Phase = 1)             | <u>116</u> |

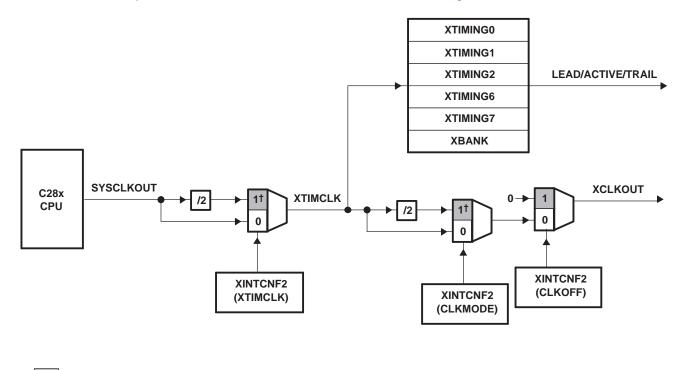

| 6-28 | Relationship Between XTIMCLK and SYSCLKOUT                   | <u>120</u> |

| 6-29 | Example Read Access                                          | 122        |

| 6-30 | Example Write Access                                         | <u>124</u> |

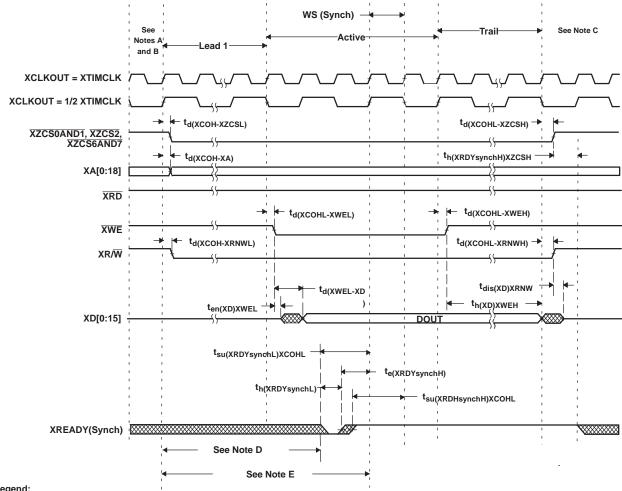

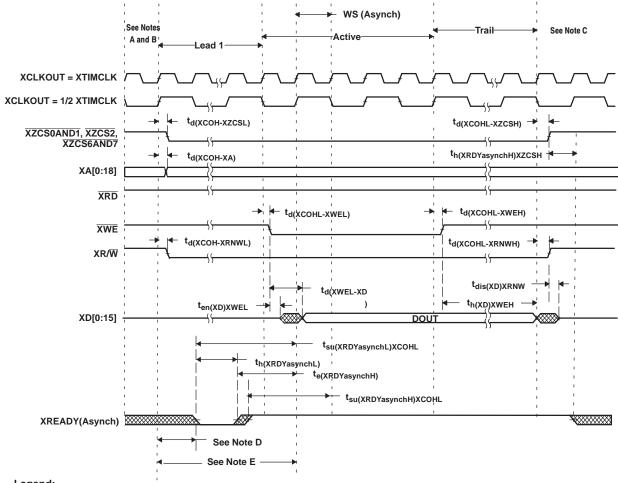

| 6-31 | Example Read With Synchronous XREADY Access                  | <u>126</u> |

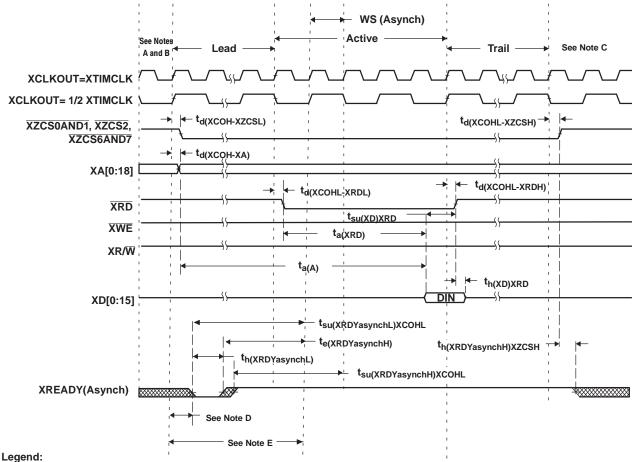

| 6-32 | Example Read With Asynchronous XREADY Access                 | <u>127</u> |

| 6-33 | Write With Synchronous XREADY Access                         | <u>129</u> |

| 6-34 | Write With Asynchronous XREADY Access                        | <u>130</u> |

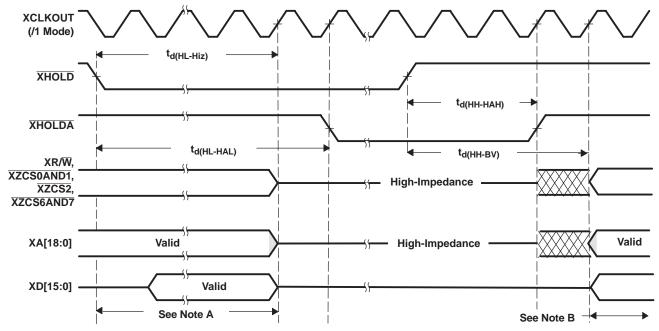

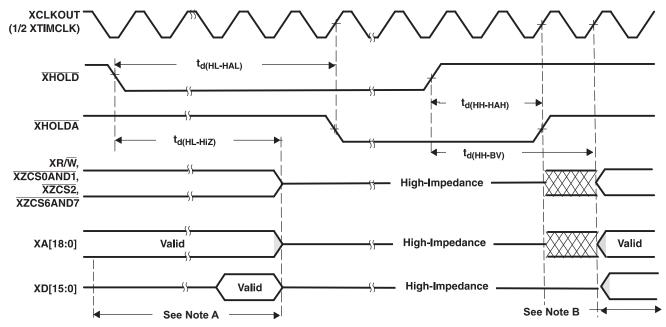

| 6-35 | External Interface Hold Waveform                             | 132        |

| 6-36 | XHOLD/XHOLDA Timing Requirements (XCLKOUT = 1/2 XTIMCLK)     | 133        |

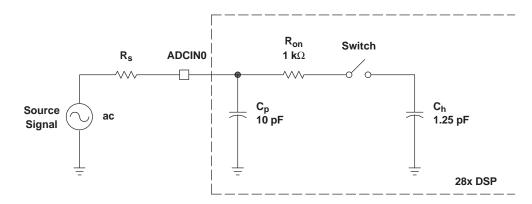

| 6-37 | ADC Analog Input Impedance Model                             | <u>137</u> |

| 6-38 | ADC Power-Up Control Bit Timing                              | <u>137</u> |

| 6-39 | Sequential Sampling Mode (Single-Channel) Timing             | 139        |

| 6-40 | Simultaneous Sampling Mode Timing                            | <u>140</u> |

| 6-41 | McBSP Receive Timing                                         | <u>144</u> |

| 6-42 | McBSP Transmit Timing                                        | <u>144</u> |

| 6-43 | McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 0 | <u>145</u> |

| 6-44 | McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 0 | <u>146</u> |

| 6-45 | McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 1 | <u>147</u> |

| 6-46 | McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 1 | <u>148</u> |

# **List of Tables**

| 2-1  | Hardware Features                                               | <u>14</u> |

|------|-----------------------------------------------------------------|-----------|

| 2-2  | Bare Die Information                                            | <u>15</u> |

| 2-3  | Signal Descriptions                                             | <u>17</u> |

| 3-1  | Addresses of Flash Sectors in F2812                             | <u>29</u> |

| 3-2  | Wait States                                                     | <u>30</u> |

| 3-3  | Boot Mode Selection                                             | 33        |

| 3-4  | Peripheral Frame 0 Registers                                    | 37        |

| 3-5  | Peripheral Frame 1 Registers                                    | 37        |

| 3-6  | Peripheral Frame 2 Registers                                    | 38        |

| 3-7  | Device Emulation Registers                                      | 39        |

| 3-8  | XINTF Configuration and Control Register Mappings               | <u>41</u> |

| 3-9  | XREVISION Register Bit Definitions                              | <u>41</u> |

| 3-10 | PIE Peripheral Interrupts                                       | <u>43</u> |

| 3-11 | PIE Configuration and Control Registers                         | 44        |

| 3-12 | External Interrupts Registers                                   | 45        |

| 3-13 | PLL, Clocking, Watchdog, and Low-Power Mode Registers           | 47        |

| 3-14 | PLLCR Register Bit Definitions                                  | 48        |

| 3-15 | Possible PLL Configuration Modes                                | 49        |

| 3-16 | F2812 Low-Power Modes                                           | 51        |

| 4-1  | CPU-Timers 0, 1, 2 Configuration and Control Registers          | 54        |

| 4-2  | Module and Signal Names for EVA and EVB                         | <br>55    |

| 4-3  | EVA Registers                                                   | 56        |

| 4-4  | ADC Registers                                                   | 64        |

| 4-5  | 3.3-V eCAN Transceivers for the SM320F2812 DSP                  |           |

| 4-6  | CAN Registers Map                                               | 68        |

| 4-7  | McBSP Register Summary                                          | 71        |

| 4-8  | SCI-A Registers                                                 |           |

| 4-9  | SCI-B Registers                                                 |           |

| 4-10 | SPI Registers                                                   |           |

| 4-11 | GPIO Mux Registers                                              |           |

| 4-12 | GPIO Data Registers                                             |           |

| 6-1  | Typical Current Consumption by Various Peripherals (at 150 MHz) |           |

| 6-2  | Recommended Low-Dropout Regulators                              |           |

| 6-3  | Clock Table and Nomenclature                                    |           |

| 6-4  | Input Clock Frequency                                           |           |

| 6-5  | XCLKIN Timing Requirements – PLL Bypassed or Enabled            |           |

| 6-6  | XCLKIN Timing Requirements – PLL Disabled                       | 95        |

| 6-7  | Possible PLL Configuration Modes                                |           |

| 6-8  | XCLKOUT Switching Characteristics (PLL Bypassed or Enabled)     | _         |

| 6-9  | Reset (XRS) Timing Requirements                                 |           |

| 6-10 | IDLE Mode Switching Characteristics                             | 100       |

| 6-11 | STANDBY Mode Switching Characteristics                          | 101       |

| 6-12 | HALT Mode Switching Characteristics                             | 103       |

| 6-13 | PWM Switching Characteristics                                   | 105       |

| 6-14 | Timer and Capture Unit Timing Requirements                      | 105       |

| 6-15 |                                                                 | 106       |

|      | <del>.</del>                                                    |           |

### SGUS062A-JUNE 2009-REVISED APRIL 2010

| 6-16 | External ADC Start-of-Conversion – EVB – Switching Characteristics                       | <u>106</u> |

|------|------------------------------------------------------------------------------------------|------------|

| 6-17 | Interrupt Switching Characteristics                                                      | <u>106</u> |

| 6-18 | Interrupt Timing Requirements                                                            |            |

| 6-19 | General-Purpose Output Switching Characteristics                                         |            |

| 6-20 | General-Purpose Input Timing Requirements                                                |            |

| 6-21 | SPI Master Mode External Timing (Clock Phase = 0)                                        |            |

| 6-22 | SPI Master Mode External Timing (Clock Phase = 1)                                        |            |

| 6-23 | SPI Slave Mode External Timing (Clock Phase = 0)                                         |            |

| 6-24 | SPI Slave Mode External Timing (Clock Phase = 1)                                         |            |

| 6-25 | Relationship Between Parameters Configured in XTIMING and Duration of Pulse              | <u>117</u> |

| 6-26 | XTIMING Register Configuration Restrictions                                              | <u>117</u> |

| 6-27 | Valid and Invalid Timing                                                                 |            |

| 6-28 | XTIMING Register Configuration Restrictions                                              | <u>118</u> |

| 6-29 | Valid and Invalid Timing when using Synchronous XREADY                                   | <u>118</u> |

| 6-30 | XTIMING Register Configuration Restrictions                                              |            |

| 6-31 | XTIMING Register Configuration Restrictions                                              |            |

| 6-32 | Asynchronous XREADY                                                                      |            |

| 6-33 | XINTF Clock Configurations                                                               | <u>119</u> |

| 6-34 | External Memory Interface Read Switching Characteristics                                 | 122        |

| 6-35 | External Memory Interface Read Timing Requirements                                       |            |

| 6-36 | External Memory Interface Write Switching Characteristics                                | <u>123</u> |

| 6-37 | External Memory Interface Read Switching Characteristics (Ready-on-Read, 1 Wait State)   | 125        |

| 6-38 | External Memory Interface Read Timing Requirements (Ready-on-Read, 1 Wait State)         | <u>125</u> |

| 6-39 | Synchronous XREADY Timing Requirements (Ready-on-Read, 1 Wait State)                     | 125        |

| 6-40 | Asynchronous XREADY Timing Requirements (Ready-on-Read, 1 Wait State)                    | 125        |

| 6-41 | External Memory Interface Write Switching Characteristics (Ready-on-Write, 1 Wait State) | <u>128</u> |

| 6-42 | Synchronous XREADY Timing Requirements (Ready-on-Write, 1 Wait State)                    | <u>128</u> |

| 6-43 | Asynchronous XREADY Timing Requirements (Ready-on-Write, 1 Wait State)                   |            |

| 6-44 | XHOLD/XHOLDA Timing Requirements (XCLKOUT = XTIMCLK)                                     |            |

| 6-45 | XHOLD/XHOLDA Timing Requirements (XCLKOUT = 1/2 XTIMCLK)                                 | <u>133</u> |

| 6-46 | DC Specifications                                                                        | <u>135</u> |

| 6-47 | AC Specifications                                                                        | <u>136</u> |

| 6-48 | Current Consumption                                                                      | <u>136</u> |

| 6-49 | ADC Power-Up Delays                                                                      | <u>137</u> |

| 6-50 | Sequential Sampling Mode Timing                                                          | <u>139</u> |

| 6-51 | Simultaneous Sampling Mode Timing                                                        | <u>140</u> |

| 6-52 | McBSP Timing Requirements                                                                | 142        |

| 6-53 | McBSP Switching Characteristics                                                          | <u>143</u> |

| 6-54 | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 0)               | <u>145</u> |

| 6-55 | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 0)         | <u>145</u> |

| 6-56 | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 0)               | <u>146</u> |

| 6-57 | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 0)         | <u>146</u> |

| 6-58 | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 1)               | <u>147</u> |

| 6-59 | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 1)         | <u>147</u> |

| 6-60 | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 1)               | <u>148</u> |

| 6-61 | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 1)         | <u>148</u> |

| 6-62 | Flash Parameters at 150-MHz SYSCLKOUT                                                    | <u>149</u> |

| 6-63 | Flash/OTP Access Timing                                                                  | <u>149</u> |

|      |                                                                                          |            |

| ww.ti.com | SGUS062A-JUNE 2009-REVISED APRIL 2010 |

|-----------|---------------------------------------|

|           |                                       |

www.ti.com

# **Digital Signal Processor**

Check for Samples: SM320F2812-HT

#### 1 Features

- High-Performance Static CMOS Technology

- 150 MHz (6.67 ns Cycle Time)

- Low Power (1.8 V Core at 135 MHz, 1.9 V, Core at 150 MHz, 3.3 V I/O) Design

- 3.3 V Flash Voltage

- JTAG Boundary Scan Support(1)

- High-Performance 32 Bit CPU (TMS320C28x)

- 16 x 16 and 32 x 32 MAC Operations

- 16 x 16 Dual MAC

- Harvard Bus Architecture

- Atomic Operations

- Fast Interrupt Response and Processing

- Unified Memory Programming Model

- 4M Linear Program Address Reach

- 4M Linear Data Address Reach

- Code-Efficient (in C/C++ and Assembly)

- TMS320F24x/LF240x Processor Source Code Compatible

- On-Chip Memory

- Flash Devices: Up to 128K x 16 Flash (Four 8K x 16 and Six 16K x 16 Sectors)

- ROM Devices: Up to 128K x 16 ROM

- 1K × 16 OTP ROM

- L0 and L1: 2 Blocks of 4K x 16 Each Single-Access RAM (SARAM)

- H0: 1 Block of 8K x 16 SARAM

- M0 and M1: 2 Blocks of 1K x 16 Each SARAM

- Boot ROM (4K x 16)

- With Software Boot Modes

- Standard Math Tables

- External Interface

- Up to 1M Total Memory

- Programmable Wait States

- Programmable Read/Write Strobe Timing

- Three Individual Chip Selects

- Clock and System Control

- Dynamic PLL Ratio Changes Supported

- On-Chip Oscillator

- Watchdog Timer Module

- Three External Interrupts

- Peripheral Interrupt Expansion (PIE) Block That Supports 45 Peripheral Interrupts

- 128 Bit Security Key/Lock

- Protects Flash/ROM/OTP and L0/L1 SARAM

- Prevents Firmware Reverse Engineering

- Three 32 Bit CPU Timers

- Motor Control Peripherals

- Two Event Managers (EVA, EVB)

- Compatible to 240xA Devices

- Serial Port Peripherals

- Serial Peripheral Interface (SPI)

- Two Serial Communications Interfaces (SCIs), Standard UART

- Enhanced Controller Area Network (eCAN)

- Multichannel Buffered Serial Port (McBSP)

With SPI Mode

- 12 Bit ADC, 16 Channels

- 2 x 8 Channel Input Multiplexer

- Two Sample-and-Hold

- Single/Simultaneous Conversions

- Fast Conversion Rate: 80 ns/12.5 MSPS

- Up to 56 Individually Programmable, Multiplexed General-Purpose Input / Output (GPIO) Pins

- Advanced Emulation Features

- Analysis and Breakpoint Functions

- Real-Time Debug via Hardware

- Development Tools Include

- ANSI C/C++ Compiler/Assembler/Linker

- Supports TMS320C24x<sup>™</sup>/240x Instructions

- Code Composer Studio™ IDE

- DSP/BIOS™

- JTAG Scan Controllers [Texas Instruments (TI) or Third-Party]

- Evaluation Modules

- Broad Third-Party Digital Motor Control Support

- Low-Power Modes and Power Savings

- IDLE, STANDBY, HALT Modes Supported

- Disable Individual Peripheral Clocks

TMS320C24x, Code Composer Studio, DSP/BIOS, C28x, TMS320C2000, TMS320C54x, TMS320C55x, TMS320C28x are trademarks of Texas Instruments.

eZdsp is a trademark of Spectrum Digital Incorporated.

<sup>(1)</sup> IEEE Standard 1149.1-1990, IEEE Standard Test-Access Port

# SGUSC62A-JUNE 2009-REVISED APRIL 2010

#### 1.1 SUPPORTS EXTREME TEMPERATURE APPLICATIONS

- Controlled Baseline

- One Assembly/Test Site

- One Fabrication Site

- Available in Extreme (–55°C/220°C) Temperature Range<sup>(2)</sup>

- Extended Product Life Cycle

- Extended Product-Change Notification

- Product Traceability

- Texas Instruments high temperature products utilize highly optimized silicon (die) solutions with design and process enhancements to maximize performance over extended temperatures.

- (2) Custom temperature ranges available

www.ti.com

#### 2 Introduction

This section provides a summary of the device features, lists the pin assignments, and describes the function of each pin. This document also provides detailed descriptions of peripherals, electrical specifications, parameter measurement information, and mechanical data about the available packaging.

### 2.1 Description

The SM320F2812 device, member of the C28xE DSP generation, is a highly integrated, high-performance solution for demanding control applications. The functional blocks and the memory maps are described in Section 3, Functional Overview.

Throughout this document SM320F2812 is abbreviated as F2812.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## 2.2 Device Summary

Table 2-1 provides a summary of the device features.

#### **Table 2-1. Hardware Features**

| FEATURE                                       |                   | F2812                                                    |

|-----------------------------------------------|-------------------|----------------------------------------------------------|

| Instruction Cycle (at 150 MHz)                |                   | 6.67 ns                                                  |

| Single-Access RAM (SARAM) (16 bit word)       |                   | 18K                                                      |

| 3.3 V On-Chip Flash (16 bit word)             |                   | 128K                                                     |

| On-Chip ROM (16-bit word)                     |                   | _                                                        |

| Code Security for On-Chip Flash/SARAM/OTP/ROM |                   | Yes                                                      |

| Boot ROM                                      |                   | Yes                                                      |

| OTP ROM (1K x 16)                             |                   | Yes                                                      |

| External Memory Interface                     |                   | Yes                                                      |

| Event Managers A and B (EVA and EVB)          |                   | EVA, EVB                                                 |

| General-Purpose (GP) Timers                   |                   | 4                                                        |

| Compare (CMP)/PWM                             |                   | 16                                                       |

| Capture (CAP)/QEP Channels                    |                   | 6/2                                                      |

| Watchdog Timer                                |                   | Yes                                                      |

| 12 Bit ADC                                    |                   | Yes                                                      |

| Channels                                      |                   | 16                                                       |

| 32 Bit CPU Timers                             |                   | 3                                                        |

| SPI                                           |                   | Yes                                                      |

| SCIA, SCIB                                    |                   | SCIA, SCIB                                               |

| CAN                                           |                   | Yes                                                      |

| McBSP                                         |                   | Yes                                                      |

| Digital I/O Pins (Shared)                     |                   | 56                                                       |

| External Interrupts                           |                   | 3                                                        |

| Supply Voltage                                |                   | 1.8-V Core, (135 MHz) 1.9-V Core<br>(150 MHz), 3.3-V I/O |

| Temperature Options                           | S: -55°C to 220°C | Yes                                                      |

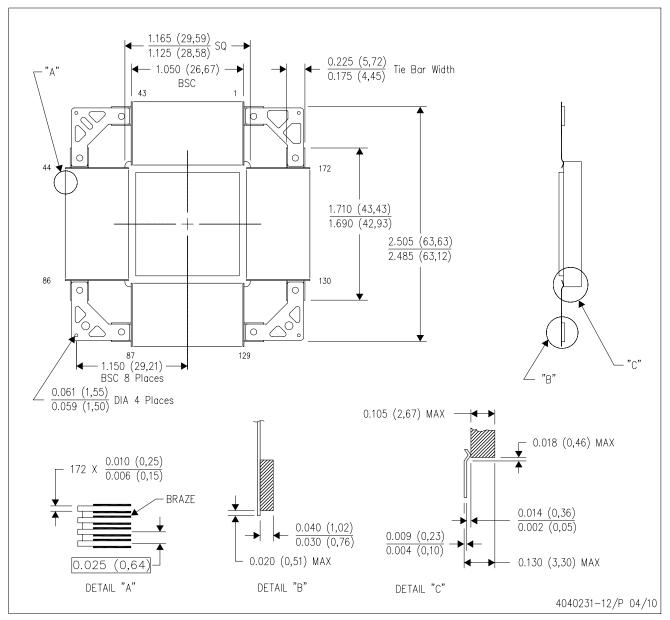

### 2.3 Die Layout

The SM320F2812 die layout is shown in Figure 2-1. See Table 2-3 for a description of each pad's function.

Figure 2-1. SM320F2812 Die Layout

**Table 2-2. Bare Die Information**

| DIE SIZE                                      | DIE PAD SIZE     | DIE PAD<br>COORDINATES | DIE<br>THICKNESS | DIE PAD<br>COMPOSITI<br>ON | BACKSIDE<br>FINISH     | BACKSIDE<br>POTENTIAL |

|-----------------------------------------------|------------------|------------------------|------------------|----------------------------|------------------------|-----------------------|

| 219.4 x 207.0 (mils);<br>5572.0 x 5258.0 (μm) | 55.0 x 64.0 (μm) | See Table 2-3          | 11.0 mils        | AlCu/TiN                   | Silicon with backgrind | Ground                |

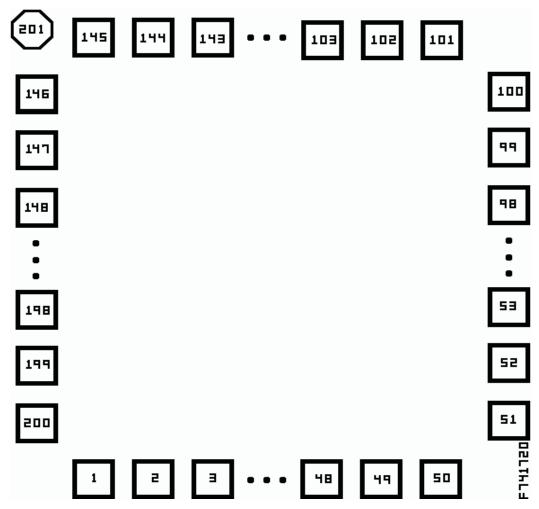

### 2.4 Pin Assignments

The SM320F2812 172-pin HFG ceramic quad flatpack (CQFP) pin assignments are shown in Figure 2-2. See Table 2-3 for a description of each pin's function(s).

Figure 2-2. SM320F2812 172-Pin HFG CQFP (Top View)

### 2.5 Signal Descriptions

Table 2-3 specifies the signals on the F2812 device. All digital inputs are TTL-compatible. All outputs are 3.3 V with CMOS levels. Inputs are not 5 V tolerant. A 100  $\mu$ A (or 20  $\mu$ A) pullup/pulldown is used.

Table 2-3. Signal Descriptions<sup>(1)</sup>

|        | PIN NO.        | DIE DAD | DIE PAD          | DIE PAD          |                      |                      |                          |

|--------|----------------|---------|------------------|------------------|----------------------|----------------------|--------------------------|

| NAME   | 172-PIN<br>HFG | NO.     | X-CENTER<br>(μm) | Y-CENTER<br>(μm) | I/O/Z <sup>(2)</sup> | PU/PD <sup>(3)</sup> | DESCRIPTION              |

|        |                |         |                  | XINTF SIG        | SNALS                |                      |                          |

| XA[18] | 154            | 173     | 42.6             | 2281.5           | O/Z                  | _                    |                          |

| XA[17] | 152            | 171     | 42.6             | 2485.3           | O/Z                  | _                    |                          |

| XA[16] | 149            | 167     | 42.6             | 2819.6           | O/Z                  | _                    |                          |

| XA[15] | 145            | 163     | 42.6             | 3182.9           | O/Z                  | _                    |                          |

| XA[14] | 141            | 157     | 42.6             | 3774.9           | O/Z                  | _                    |                          |

| XA[13] | 138            | 154     | 42.6             | 4029.4           | O/Z                  | _                    |                          |

| XA[12] | 135            | 151     | 42.6             | 4401.3           | O/Z                  | _                    |                          |

| XA[11] | 129            | 145     | 255.7            | 5057.5           | O/Z                  |                      |                          |

| XA[10] | 127            | 143     | 474.4            | 5057.5           | O/Z                  | _                    |                          |

| XA[9]  | 122            | 138     | 996.5            | 5057.5           | O/Z                  | _                    | 19-bit XINTF Address Bus |

| XA[8]  | 118            | 134     | 1492.4           | 5057.5           | O/Z                  | _                    |                          |

| XA[7]  | 116            | 131     | 1825.2           | 5057.5           | O/Z                  | _                    |                          |

| XA[6]  | 109            | 124     | 2566.0           | 5057.5           | O/Z                  | _                    |                          |

| XA[5]  | 106            | 121     | 2937.9           | 5057.5           | O/Z                  | _                    |                          |

| XA[4]  | 101            | 116     | 3518.7           | 5057.5           | O/Z                  | _                    |                          |

| XA[3]  | 83             | 96      | 5361.5           | 4471.5           | O/Z                  | _                    |                          |

| XA[2]  | 78             | 91      | 5361.5           | 3927.2           | O/Z                  | _                    |                          |

| XA[1]  | 42             | 49      | 5024.5           | 42.6             | O/Z                  | _                    |                          |

| XA[0]  | 18             | 24      | 2403.5           | 42.6             | O/Z                  |                      |                          |

| XD[15] | 144            | 162     | 42.6             | 3306.9           | I/O/Z                | PU                   |                          |

| XD[14] | 136            | 152     | 42.6             | 4277.3           | I/O/Z                | PU                   |                          |

| XD[13] | 95             | 110     | 4194.1           | 5057.5           | I/O/Z                | PU                   |                          |

| XD[12] | 94             | 109     | 4318.1           | 5057.5           | I/O/Z                | PU                   |                          |

| XD[11] | 72             | 85      | 5361.5           | 3382.2           | I/O/Z                | PU                   |                          |

| XD[10] | 71             | 84      | 5361.5           | 3258.3           | I/O/Z                | PU                   |                          |

| XD[9]  | 67             | 77      | 5361.5           | 2608.4           | I/O/Z                | PU                   |                          |

| XD[8]  | 64             | 74      | 5361.5           | 2312.1           | I/O/Z                | PU                   |                          |

| XD[7]  | 53             | 60      | 5361.5           | 1045.9           | I/O/Z                | PU                   | 16-bit XINTF Data Bus    |

| XD[6]  | 38             | 45      | 4586.0           | 42.6             | I/O/Z                | PU                   |                          |

| XD[5]  | 35             | 42      | 4281.2           | 42.6             | I/O/Z                | PU                   |                          |

| XD[4]  | 32             | 39      | 3966.6           | 42.6             | I/O/Z                | PU                   |                          |

| XD[3]  | 29             | 36      | 3652.0           | 42.6             | I/O/Z                | PU                   |                          |

| XD[2]  | 26             | 33      | 3337.5           | 42.6             | I/O/Z                | PU                   |                          |

| XD[1]  | 23             | 30      | 3022.9           | 42.6             | I/O/Z                | PU                   |                          |

| XD[0]  | 20             | 27      | 2708.3           | 42.6             | I/O/Z                | PU                   |                          |

<sup>(1)</sup> Typical drive strength of the output buffer for all pins is 4 mA except for TDO, XCLKOUT, XF, XINTF, EMU0, and EMU1 pins, which are 8 mA.

<sup>(2)</sup> I = Input, O = Output, Z = High impedance

<sup>(3)</sup> PU = pin has internal pullup; PD = pin has internal pulldown

| NAME      | PIN NO.<br>172-PIN<br>HFG | DIE PAD<br>NO. | DIE PAD<br>X-CENTER<br>(μm) | DIE PAD<br>Y-CENTER<br>(μm) | I/O/Z <sup>(2)</sup> | PU/PD <sup>(3)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|---------------------------|----------------|-----------------------------|-----------------------------|----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XMP/MC    | 17                        | 23             | 2308.2                      | 42.6                        | I                    | PD                   | Microprocessor/Microcomputer Mode Select. Switches between microprocessor and microcomputer mode. When high, Zone 7 is enabled on the external interface. When low, Zone 7 is disabled from the external interface and on-chip boot ROM may be accessed instead. This signal is latched into the XINTCNF2 register on a reset and the user can modify this bit in software. The state of the XMP/MC pin is ignored after reset. |

| XHOLD     | 155                       | 174            | 42.6                        | 2157.6                      | I                    | PU                   | External Hold Request. XHOLD, when active (low), requests the XINTF to release the external bus and place all buses and strobes into a high-impedance state. The XINTF releases the bus when any current access is complete and there are no pending accesses on the XINTF.                                                                                                                                                     |

| XHOLDA    | 80                        | 93             | 5361.5                      | 4137.4                      | O/Z                  | -                    | External Hold Acknowledge. XHOLDA is driven active (low) when the XINTF has granted a XHOLD request. All XINTF buses and strobe signals are in a high-impedance state. XHOLDA is released when the XHOLD signal is released. External devices should only drive the external bus when XHOLDA is active (low).                                                                                                                   |

| XZCS0AND1 | 43                        | 50             | 5148.5                      | 42.6                        | O/Z                  | _                    | XINTF Zone 0 and Zone 1 Chip Select. XZCS0AND1 is active (low) when an access to the XINTF Zone 0 or Zone 1 is performed.                                                                                                                                                                                                                                                                                                       |

| XZCS2     | 86                        | 100            | 5361.5                      | 4844.2                      | O/Z                  | _                    | XINTF Zone 2 Chip Select. XZCS2 is active (low) when an access to the XINTF Zone 2 is performed.                                                                                                                                                                                                                                                                                                                                |

| XZCS6AND7 | 130                       | 146            | 42.6                        | 4888.6                      | O/Z                  | _                    | XINTF Zone 6 and Zone 7 Chip Select.  XZCS6AND7 is active (low) when an access to the XINTF Zone 6 or Zone 7 is performed.                                                                                                                                                                                                                                                                                                      |

| XWE       | 82                        | 95             | 5361.5                      | 4347.5                      | O/Z                  | _                    | Write Enable. Active-low write strobe. The write strobe waveform is specified, per zone basis, by the Lead, Active, and Trail periods in the XTIMINGx registers.                                                                                                                                                                                                                                                                |

| XRD       | 41                        | 48             | 4900.6                      | 42.6                        | O/Z                  | _                    | Read Enable. Active-low read strobe. The read strobe waveform is specified, per zone basis, by the Lead, Active, and Trail periods in the XTIMINGx registers.  NOTE: The XRD and XWE signals are mutually exclusive.                                                                                                                                                                                                            |

| XR/W      | 50                        | 57             | 5361.5                      | 755.0                       | O/Z                  | _                    | Read Not Write Strobe. Normally held high. When low, XR/W indicates write cycle is active; when high, XR/W indicates read cycle is active.                                                                                                                                                                                                                                                                                      |

| XREADY    | 157                       | 176            | 42.6                        | 1972.4                      | I                    | PU                   | Ready Signal. Indicates peripheral is ready to complete the access when asserted to 1. XREADY can be configured to be a synchronous or an asynchronous input. See the timing diagrams for more details.                                                                                                                                                                                                                         |

|           | PIN NO.        |                |                             |                             |                      | `                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|----------------|----------------|-----------------------------|-----------------------------|----------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | 172-PIN<br>HFG | DIE PAD<br>NO. | DIE PAD<br>X-CENTER<br>(μm) | DIE PAD<br>Y-CENTER<br>(μm) | I/O/Z <sup>(2)</sup> | PU/PD <sup>(3)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |                |                | JTAG A                      | AND MISCELLA                | NEOUS SI             | GNALS                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| X1/XCLKIN | 75             | 88             | 5361.5                      | 3668.7                      | I                    |                      | Oscillator Input – input to the internal oscillator. This pin is also used to feed an external clock. The 28x can be operated with an external clock source, provided that the proper voltage levels be driven on the X1/XCLKIN pin. It should be noted that the X1/XCLKIN pin is referenced to the 1.8-V (or 1.9-V) core digital power supply (V <sub>DD</sub> ), rather than the 3.3-V I/O supply (V <sub>DDIO</sub> ). A clamping diode may be used to clamp a buffered clock signal to ensure that the logic-high level does not exceed V <sub>DD</sub> (1.8 V or 1.9 V) or a 1.8-V oscillator may be used. |

| X2        | 74             | 87             | 5361.5                      | 3582.6                      | 0                    |                      | Oscillator Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| XCLKOUT   | 117            | 132            | 1701.2                      | 5057.5                      | 0                    | -                    | Output clock derived from SYSCLKOUT to be used for external wait-state generation and as a general-purpose clock source. XCLKOUT is either the same frequency, 1/2 the frequency, or 1/4 the frequency of SYSCLKOUT. At reset, XCLKOUT = SYSCLKOUT/4. The XCLKOUT signal can be turned off by setting bit 3 (CLKOFF) of the XINTCNF2 register to 1.                                                                                                                                                                                                                                                             |

| TESTSEL   | 131            | 147            | 42.6                        | 4764.6                      | I                    | PD                   | Test Pin. Reserved for TI. Must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| XRS       | 156            | 175            | 42.6                        | 2077.8                      | I/O                  | PU                   | Device Reset (in) and Watchdog Reset (out).  Device reset. XRS causes the device to terminate execution. The PC points to the address contained at the location 0x3FFC0. When XRS is brought to a high level, execution begins at the location pointed to by the PC. This pin is driven low by the DSP when a watchdog reset occurs. During watchdog reset, the XRS pin is driven low for the watchdog reset duration of 512 XCLKIN cycles.  The output buffer of this pin is an open-drain with an internal pullup (100 μA, typical). It is recommended that this pin be driven by an open-drain device.       |

| TEST1     | 66             | 76             | 5361.5                      | 2522.3                      | I/O                  | _                    | Test Pin. Reserved for Tl. On F281x devices, TEST1 must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TEST2     | 65             | 75             | 5361.5                      | 2436.1                      | I/O                  | _                    | Test Pin. Reserved for Tl. On F281x devices, TEST2 must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | DIN NO                    |                |                             |                             |                      | `                    | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|---------------------------|----------------|-----------------------------|-----------------------------|----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | PIN NO.<br>172-PIN<br>HFG | DIE PAD<br>NO. | DIE PAD<br>X-CENTER<br>(μm) | DIE PAD<br>Y-CENTER<br>(μm) | I/O/Z <sup>(2)</sup> | PU/PD <sup>(3)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |                           |                |                             |                             |                      |                      | JTAG test reset with internal pulldown. TRST, when driven high, gives the scan system control of the operations of the device. If this signal is not connected or driven low, the device operates in its functional mode, and the test reset signals are ignored.  NOTE: Do not use pullup resistors on                                                                                                                                                                                                                         |

| TRST | 132                       | 148            | 42.6                        | 4684.8                      | ı                    | PD                   | $\overline{TRST}$ ; it has an internal pulldown device. In a low-noise environment, $\overline{TRST}$ can be left floating. In a high-noise environment, an additional pulldown resistor may be needed. The value of this resistor should be based on drive strength of the debugger pods applicable to the design. A 2.2-kΩ resistor generally offers adequate protection. Since this is application specific, it is recommended that each target board is validated for proper operation of the debugger and the application. |

| TCK  | 133                       | 149            | 42.6                        | 4605.1                      | I                    | PU                   | JTAG test clock with internal pullup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TMS  | 123                       | 139            | 872.5                       | 5057.5                      | I                    | PU                   | JTAG test-mode select (TMS) with internal pullup. This serial control input is clocked into the TAP controller on the rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                       |

| TDI  | 128                       | 144            | 350.4                       | 5057.5                      | I                    | PU                   | JTAG test data input (TDI) with internal pullup. TDI is clocked into the selected register (instruction or data) on a rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                       |

| TDO  | 124                       | 140            | 777.9                       | 5057.5                      | O/Z                  | _                    | JTAG scan out, test data output (TDO). The contents of the selected register (instruction or data) is shifted out of TDO on the falling edge of TCK.                                                                                                                                                                                                                                                                                                                                                                            |

| EMU0 | 133                       | 150            | 42.6                        | 4525.3                      | I/O/Z                | PU                   | Emulator pin 0. When TRST is driven high, this pin is used as an interrupt to or from the emulator system and is defined as input/output through the JTAG scan.                                                                                                                                                                                                                                                                                                                                                                 |

| EMU1 | 143                       | 161            | 42.6                        | 3430.9                      | I/O/Z                | PU                   | Emulator pin 1. When TRST is driven high, this pin is used as an interrupt to or from the emulator system and is defined as input/output through the JTAG scan.                                                                                                                                                                                                                                                                                                                                                                 |

|                    | DIN NO             |         | abie 2-3. 3i        |                     |                      | (COIIIII)            |                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|--------------------|---------|---------------------|---------------------|----------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | PIN NO.<br>172-PIN | DIE PAD | DIE PAD<br>X-CENTER | DIE PAD<br>Y-CENTER | I/O/Z <sup>(2)</sup> | PU/PD <sup>(3)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                           |

|                    | HFG                | NO.     | <b>(μm)</b>         | <b>(μm)</b>         |                      |                      |                                                                                                                                                                                                                                                                                                                                                                       |

|                    |                    |         | AD                  | C ANALOG IN         | PUT SIGNA            | ALS                  |                                                                                                                                                                                                                                                                                                                                                                       |

| ADCINA7            | 163                | 186     | 42.6                | 1253.9              | I                    |                      |                                                                                                                                                                                                                                                                                                                                                                       |

| ADCINA6            | 164                | 188     | 42.6                | 1094.3              | 1                    |                      |                                                                                                                                                                                                                                                                                                                                                                       |

| ADCINA5            | 165                | 190     | 42.6                | 954.0               | 1                    |                      | Fight channel analog inputs for                                                                                                                                                                                                                                                                                                                                       |

| ADCINA4            | 166                | 192     | 42.6                | 794.4               | 1                    |                      | Eight-channel analog inputs for Sample-and-Hold A. The ADC pins should                                                                                                                                                                                                                                                                                                |

| ADCINA3            | 167                | 194     | 42.6                | 654.1               | 1                    |                      | not be driven before V <sub>DDA1</sub> , V <sub>DDA2</sub> , and                                                                                                                                                                                                                                                                                                      |

| ADCINA2            | 168                | 196     | 42.6                | 513.9               | 1                    |                      | V <sub>DDAIO</sub> pins have been fully powered up.                                                                                                                                                                                                                                                                                                                   |

| ADCINA1            | 169                | 197     | 42.6                | 434.1               | 1                    |                      |                                                                                                                                                                                                                                                                                                                                                                       |