# **High-Density Synchronous Buck Converter Design Using TPS56xx Controllers**

# User's Guide

June 1999

Mixed-Signal Linear Products

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

### Preface

### **Read This First**

### About This Manual

This user's guide describes techniques for designing synchronous buck converters using TI's SLVP1111–114 evaluation modules (EVM) and TPS56xx ripple regulator controllers.

### How to Use This Manual

This document contains the following chapters:

- Chapter 1 Introduction

- Chapter 2 Design Procedure

- Chapter 3 Test Results

### Information About Cautions and Warnings

This book may contain cautions and warnings.

This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software or equipment.

This is an example of a warning statement.

A warning statement describes a situation that could potentially cause harm to <u>you</u>.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

### **Related Documentation From Texas Instruments**

- Synchronous Buck Converter Design Using TPS56xx Controllers in SLVP10x EVMs User's Guide (literature number SLVU007).

- □ TPS56xx data sheet (literature number SLVS177A)

- Designer's Notebook The TPS56xx Family of Power Supply Controllers (literature number SLVT140A)

- Designing Fast Response Synchronous Buck Regulators Using the TPS5210 (literaure number SLVA044).

### FCC Warning

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

### Trademarks

TI is a trademark of Texas Instruments Incorporated.

## Contents

| 1 | Introd<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Synchr<br>Hyster<br>Design<br>Design                                                                                 | 1-1         ronous Buck Regulator Operation       1-2         etic Control Operation       1-3         Strategy       1-4         Specification Summary       1-5         atic       1-7                           |

|---|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.6<br>1.7                                |                                                                                                                      | Materials       1-8         Layout       1-10                                                                                                                                                                      |

| 2 | <b>Desig</b> 2.1 2.2                      | TPS56<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9<br>2.1.10<br>Externa<br>2.2.1 | al Component Selection                                                                                                                                                                                             |

|   |                                           | 2.2.2<br>2.2.3<br>2.2.4<br>2.2.5                                                                                     | Input Capacitance2-14Output Filter Design2-14Switching Frequency Analysis2-17Power MOSFET Selection2-20                                                                                                            |

| 3 |                                           |                                                                                                                      |                                                                                                                                                                                                                    |

|   | 3.1                                       | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8                                                 | Jummary3-2Static Line and Load Regulation3-2Output Voltage Ripple3-2Efficiency and Power Losses3-2Output Start-Up and Overshoot3-2Frequency Variation3-3Load Current Transient Response3-3Features3-3Conclusion3-4 |

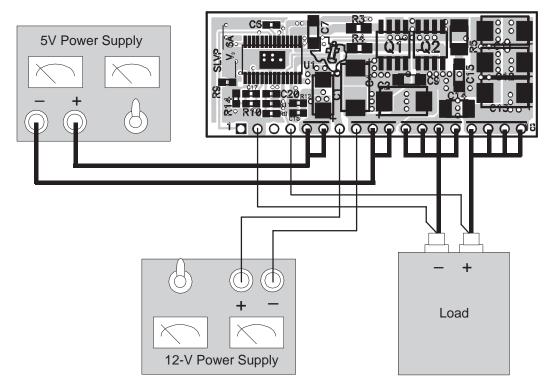

|   | 3.2                                       |                                                                                                                      | etup                                                                                                                                                                                                               |

|   | 3.3                                       | Test Re                                                                                                              | esults                                                                                                                                                                                                             |

# Figures

| 1-1       Simplified Synchronous Buck Converter Schematic       1-2         1-2       Simplified Hysteretic Controlled Output Voltage Waveform       1-3         1-3       SLVP111-114 EVM Converter Schematic Diagram       1-7         1-4       Top Assembly       1-10         1-5       Bottom Assembly (Top View)       1-10         1-6       Top Layer       1-10         1-7       Bottom Layer (Top View)       1-11         1-7       Bottom Jayer (Top View)       1-11         1-7       Bottom Layer (Top View)       1-11         2-7       Suppression Circuits       2-3         2-8       Gate Driver Block Diagram       2-12         2-6       Output Ripple Voltage Detail       2-12         2-6       Output Ripple Voltage Detail       3-3         3       SLVP111 Measured Suitching Frequency       3-8         3-1       Test Setup       3-6         2-2       SLVP111 Measured Start-Up (VIN)       Waveforms       3-9         3-7       SLVP111 Measured Start-Up (VIN)       Waveforms                                                                                                                                                       |      |                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------|

| 1-3       SLVP111–114 EVM Converter Schematic Diagram       1-7         1-4       Top Assembly       1-10         1-5       Bottom Assembly (Top View)       1-10         1-6       Top Layer       1-10         1-7       Bottom Layer (Top View)       1-11         1-7       Bottom Layer (Top View)       1-11         2-1       Bottom Layer (Top View)       1-11         2-2       Block Diagram Showing Noise Suppression Circuits       2-7         2-2       Block Diagram Showing Noise Suppression Circuits       2-7         2-3       V <sub>DS</sub> Sensing Circuit       2-8         2-4       Gate Driver Block Diagram       2-11         2-5       Output Ripple Voltage Detail       2-14         2-6       Output Ripple Voltage Detail       2-18         3-1       Test Setup       3-6         3-2       SLVP111 Measured Cod Regulation       3-7         3-4       SLVP111Measured Power Dissipation       3-8         5-5       SLVP111 Measured Start-Up (NHIBIT) Waveforms       3-9         3-6       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-10       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-11       SLVP111 Measured Start-Up (V <sub>IN</sub> ) W                                                                                | 1–1  | Simplified Synchronous Buck Converter Schematic 1-2          |

| 1-4       Top Assembly       1-10         1-5       Bottom Assembly (Top View)       1-10         1-6       Top Layer       1-10         1-7       Bottom Layer (Top View)       1-11         2-7       Block Diagram Showing Noise Suppression Circuits       2-7         2-3       Block Diagram Showing Noise Suppression Circuits       2-7         2-3       VDS Sensing Circuit       2-8         2-4       Gate Driver Block Diagram       2-11         2-5       I-V Characteristic Curve for Low-Side Gate Drivers       2-12         2-6       Output Ripple Voltage Detail       2-14         3-1       Test Setup       3-6         3-2       SLVP111 Measured Efficiency       3-7         3-3       SLVP111 Measured Efficiency       3-7         3-4       SLVP111 Measured Start-Up (VINIBIT) Waveforms       3-9         3-5       SLVP111 Measured Start-Up (VINIBIT) Waveforms       3-9         3-6       SLVP111 Measured Start-Up (VIN) Waveforms       3-10         3-10       SLVP111 Measured Cod Regulation       3-11         3-11       SLVP111 Measured Start-Up (VIN) Waveforms       3-10         3-10       SLVP111 Measured Start-Up (VIN) Waveforms       3-10         3-11 <t< td=""><td>1–2</td><td>Simplified Hysteretic Controlled Output Voltage Waveform 1-3</td></t<>                               | 1–2  | Simplified Hysteretic Controlled Output Voltage Waveform 1-3 |

| 1-5       Bottom Assembly (Top View)       1-10         1-6       Top Layer       1-10         1-7       Bottom Layer (Top Vlew)       1-11         1-1       TPS56xx Functional Block Diagram       2-3         2-2       Block Diagram Showing Noise Suppression Circuits       2-7         2-3       V <sub>DS</sub> Sensing Circuit       2-8         2-4       Gate Driver Block Diagram       2-11         2-5       I-V Characteristic Curve for Low-Side Gate Drivers       2-12         2-6       Output Ripple Voltage Detail       2-18         3-1       Test Setup       3-3         3-2       SLVP111 Measured Load Regulation       3-7         3-3       SLVP111 Measured Efficiency       3-7         -3       SLVP111 Measured Switching Frequency       3-8         3-5       SLVP111 Measured Switching Frequency       3-8         3-7       SLVP111 Measured Start-Up (V <sub>IN</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Coad Regulation       3-10         3-9       SLVP111 Measured Coad Transient Waveforms       3-10         3-10       SLVP111 Measured Start-Up (V <sub>CN</sub> ) Waveforms       3-11         3-11       SLVP112 Measured Start-Up (V <sub>IN</sub> )       3-12         3-13       S                                                                                | 1–3  | SLVP111–114 EVM Converter Schematic Diagram 1-7              |

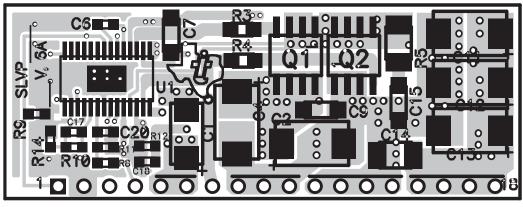

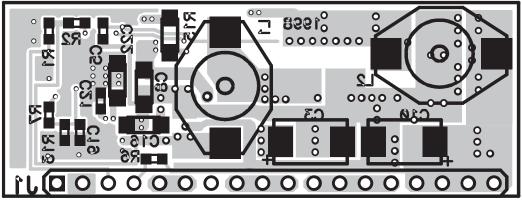

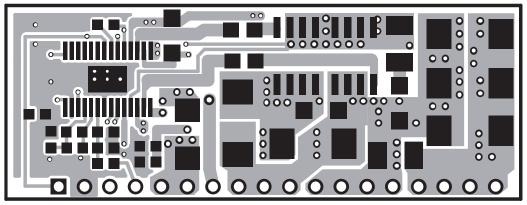

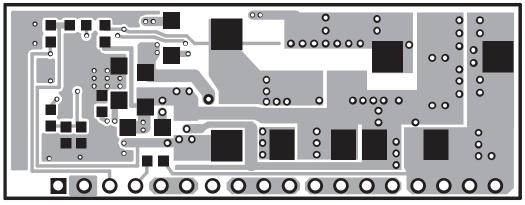

| 1-6       Top Layer (, 1-10         Bottom Layer (Top Vlew)       1-11         2       Bottom Layer (Top Vlew)       1-11         1       TPS56xx Functional Block Diagram       2-3         2       Block Diagram Showing Noise Suppression Circuits       2-7         2       Sensing Circuit       2-8         2-4       Gate Driver Block Diagram       2-11         2-5       I-V Characteristic Curve for Low-Side Gate Drivers       2-12         2-6       Output Ripple Voltage Detail       2-18         3-1       Test Setup       3-6         3-2       SLVP111 Measured Load Regulation       3-7         3-3       SLVP111Measured Efficiency       3-7         3-4       SLVP111Measured Switching Frequency       3-8         3-5       SLVP111Measured Start-Up (NHIBIT) Waveforms       3-9         3-7       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Start-Up (V <sub>N</sub> ) Waveforms       3-11         3-10       SLVP111 Measured Coad Regulation       3-11         3-11       SLVP111 Measured Coad Regulation       3-11         3-13       SLVP111 Measured Start-Up (V <sub>N</sub> ) Waveforms       3-10         3-14       SLVP111 Measured Start-Up (V <sub>N</sub> ) Wavefor                                                                | 1–4  |                                                              |

| 1-7       Bottom Layer (Top Vlew)       1-11         2-1       TPS56xx Functional Block Diagram       2-3         2-2       Block Diagram Showing Noise Suppression Circuits       2-7         3       V <sub>DS</sub> Sensing Circuit       2-8         2-4       Gate Driver Block Diagram       2-11         2-5       I-V Characteristic Curve for Low-Side Gate Drivers       2-12         2-6       Output Ripple Voltage Detail       2-18         3-1       Test Setup       3-6         3-2       SLVP111 Measured Lefficiency       3-7         3-3       SLVP111 Measured Dower Dissipation       3-8         3-5       SLVP111 Measured Switching Frequency       3-8         3-6       SLVP111 Measured Start-Up (INHIBIT) Waveforms       3-9         3-7       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-8       SLVP111 Measured Load Regulation       3-11         3-10       SLVP111 Measured Cad Regulation       3-11         3-11       SLVP111 Measured Start-Up (V <sub>N</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Cad Regulation       3-11         3-11       SLVP112 Measured Dead Regulation       3-11         3-12       SLVP111 Measured Start-Up (V <sub>N</sub> ) Waveforms       3-12                                                              | 1–5  |                                                              |

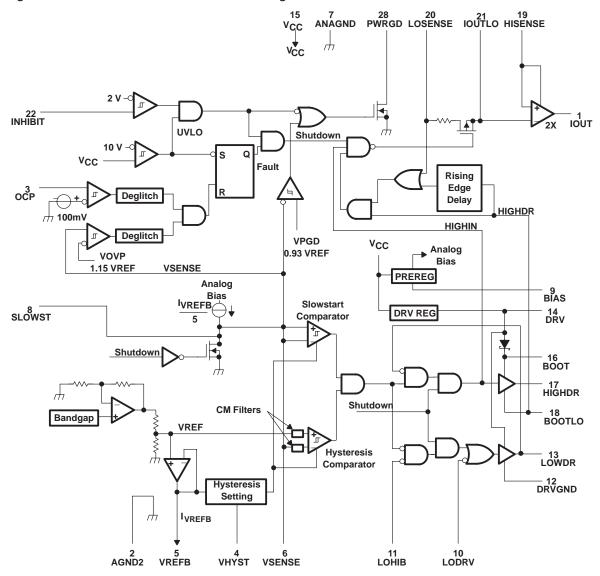

| 2-1TPS56xx Functional Block Diagram2-32-2Block Diagram Showing Noise Suppression Circuits2-72-3 $V_{DS}$ Sensing Circuit2-82-4Gate Driver Block Diagram2-112-5I-V Characteristic Curve for Low-Side Gate Drivers2-122-6Output Ripple Voltage Detail2-183-1Test Setup3-63-2SLVP111 Measured Load Regulation3-73-3SLVP111 Measured Efficiency3-73-4SLVP111 Measured Efficiency3-83-5SLVP111 Measured Switching Frequency3-83-6SLVP111 Measured Start-Up (INHIBIT) Waveforms3-93-7SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-103-9SLVP111 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-103-10SLVP111 Measured Load Regulation3-113-11SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-113-12SLVP111 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-103-13SLVP112 Measured Coad Regulation3-113-14SLVP112 Measured Efficiency3-123-13SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-133-15SLVP112 Measured Switching Frequency3-133-14SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-143-15SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-133-15SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-133-16SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-143-17SLVP112 Measured Start-Up (V <sub>IN</sub> ) Wavefor                                                              | 1–6  |                                                              |

| 2-2       Block Diagram Showing Noise Suppression Circuits       2-7         2-3       V <sub>DS</sub> Sensing Circuit       2-8         2-4       Gate Driver Block Diagram       2-11         2-5       I-V Characteristic Curve for Low-Side Gate Drivers       2-12         2-6       Output Ripple Voltage Detail       2-18         3-1       Test Setup       3-6         3-2       SLVP111 Measured Load Regulation       3-7         3-3       SLVP111 Measured Efficiency       3-7         3-4       SLVP111 Measured Power Dissipation       3-8         3-5       SLVP111 Measured Switching Frequency       3-8         3-6       SLVP111 Measured Start-Up (NHIBIT) Waveforms       3-9         3-7       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Coad Regulation       3-11         3-10       SLVP111 Measured Efficiency       3-12         3-11       SLVP111 Measured Coad Regulation       3-10         3-12       SLVP111 Measured Coad Regulation       3-11         3-11       SLVP112 Measured Coad Regulation       3-11         3-12       SLVP111 Measured Start-Up (V <sub>IN</sub> ) Waveforms       3-13                                                     | 1–7  | Bottom Layer (Top VIew) 1-11                                 |

| 2-3       V <sub>DS</sub> Sensing Circuit       2-8         2-4       Gate Driver Block Diagram       2-11         2-5       I–V Characteristic Curve for Low-Side Gate Drivers       2-12         2-6       Output Ripple Voltage Detail       2-18         2-6       Output Ripple Voltage Detail       2-18         2-7       Output Ripple Voltage Detail       2-18         3-7       SLVP111 Measured Load Regulation       3-7         3-3       SLVP111 Measured Efficiency       3-7         3-4       SLVP111 Measured Switching Frequency       3-8         3-5       SLVP111 Measured Switching Waveforms       3-9         3-7       SLVP111 Measured Start-Up (NHIBIT) Waveforms       3-9         3-8       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Load Transient Waveforms       3-10         3-9       SLVP111 Measured Load Regulation       3-11         3-10       SLVP112 Measured Load Regulation       3-11         3-11       SLVP112 Measured Efficiency       3-12         3-13       SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-11         3-13       SLVP112 Measured Coad Regulation       3-12         3-14       SLVP112 Measured Coad Regulation       3-12                                                                | 2–1  | TPS56xx Functional Block Diagram 2-3                         |

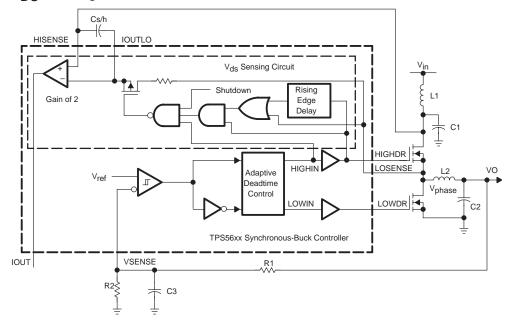

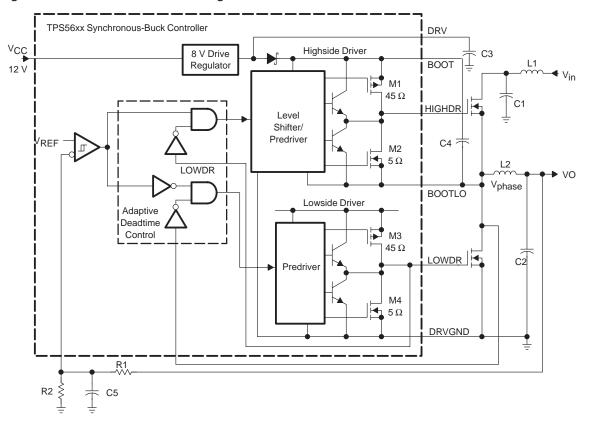

| 2-4       Gate Driver Block Diagram       2-11         2-5       I–V Characteristic Curve for Low-Side Gate Drivers       2-12         2-6       Output Ripple Voltage Detail       2-18         3-1       Test Setup       3-6         3-2       SLVP111 Measured Load Regulation       3-7         3-3       SLVP111 Measured Efficiency       3-7         3-4       SLVP111 Measured Power Dissipation       3-8         3-5       SLVP111 Measured Switching Frequency       3-8         3-6       SLVP111 Measured Start-Up (INHIBIT) Waveforms       3-9         3-7       SLVP111 Measured Start-Up (VCC) Waveforms       3-9         3-8       SLVP111 Measured Start-Up (VIN) Waveforms       3-10         3-9       SLVP111 Measured Start-Up (VIN) Waveforms       3-10         3-9       SLVP111 Measured Cod Transient Waveforms       3-11         3-10       SLVP111 Measured Load Regulation       3-11         3-11       SLVP112 Measured Efficiency       3-12         3-13       SLVP112 Measured Switching Frequency       3-13         3-14       SLVP112 Measured Switching Frequency       3-13         3-15       SLVP112 Measured Start-Up (VCC) Waveforms       3-14         3-15       SLVP112 Measured Start-Up (VCC) Waveforms </td <td>2–2</td> <td>Block Diagram Showing Noise Suppression Circuits 2-7</td> | 2–2  | Block Diagram Showing Noise Suppression Circuits 2-7         |

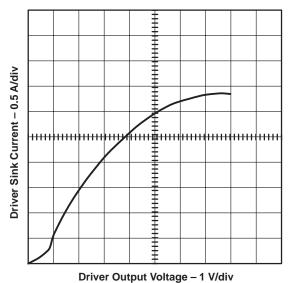

| 2-5I-V Characteristic Curve for Low-Side Gate Drivers2-122-6Output Ripple Voltage Detail2-183-1Test Setup3-63-2SLVP111 Measured Load Regulation3-73-3SLVP111 Measured Efficiency3-73-4SLVP111 Measured Power Dissipation3-83-5SLVP111 Measured Switching Frequency3-83-6SLVP111 Measured Switching Waveforms3-93-7SLVP111 Measured Start-Up (INHIBIT) Waveforms3-93-8SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-103-9SLVP111 Measured Load Transient Waveforms3-103-10SLVP112 Measured Load Regulation3-113-11SLVP112 Measured Efficiency3-123-13SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-123-14SLVP112 Measured Efficiency3-123-15SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-143-16SLVP112 Measured Start-Up (INHIBIT) Waveforms3-133-16SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-143-15SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-143-16SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-163-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Efficiency3-163-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Frequency<                                                                                                    | 2–3  | V <sub>DS</sub> Sensing Circuit                              |

| 2-6       Output Ripple Voltage Detail       2-18         3-1       Test Setup       3-6         3-2       SLVP111 Measured Load Regulation       3-7         3-3       SLVP111Measured Efficiency       3-7         3-4       SLVP111Measured Power Dissipation       3-8         3-5       SLVP111Measured Switching Frequency       3-8         3-6       SLVP111 Measured Switching Waveforms       3-9         3-7       SLVP111 Measured Start-Up (INHIBIT) Waveforms       3-9         3-8       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-11         3-10       SLVP111 Measured Load Transient Waveforms       3-11         3-11       SLVP112 Measured Efficiency       3-12         3-13       SLVP112 Measured Efficiency       3-12         3-14       SLVP112 Measured Switching Frequency       3-13         3-15       SLVP112 Measured Switching Waveforms       3-13         3-16       SLVP112 Measured Switching Waveforms       3-13         3-15       SLVP112 Measured Switching Waveforms       3-14         3-16       SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms                                          | 2–4  | Gate Driver Block Diagram 2-11                               |

| 3-1       Test Setup       3-6         3-2       SLVP111 Measured Load Regulation       3-7         3-3       SLVP111Measured Efficiency       3-7         3-4       SLVP111Measured Power Dissipation       3-8         3-5       SLVP111Measured Switching Frequency       3-8         3-6       SLVP111 Measured Switching Waveforms       3-9         3-7       SLVP111 Measured Start-Up (INHIBIT) Waveforms       3-9         3-8       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-10       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-11         3-11       SLVP111 Measured Coad Transient Waveforms       3-11         3-12       SLVP112 Measured Efficiency       3-12         3-13       SLVP112 Measured Efficiency       3-12         3-14       SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-13         3-15       SLVP112 Measured Start-Up (INHIBIT) Waveforms       3-13         3-16       SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-14         3-17       SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-14         3-18       SLVP  | 2–5  | I–V Characteristic Curve for Low-Side Gate Drivers           |

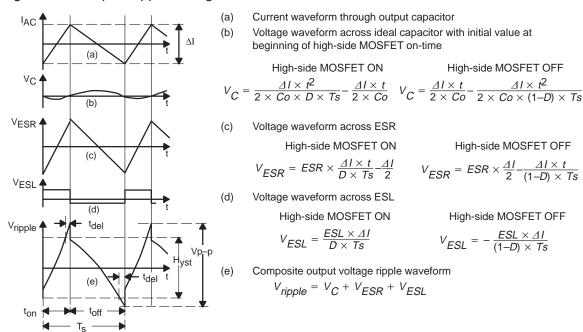

| 3-2       SLVP111 Measured Load Regulation       3-7         3-3       SLVP111Measured Efficiency       3-7         3-4       SLVP111Measured Power Dissipation       3-8         3-5       SLVP111Measured Switching Frequency       3-8         3-6       SLVP111 Measured Switching Waveforms       3-9         3-7       SLVP111 Measured Start-Up (INHIBIT) Waveforms       3-9         3-8       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-10       SLVP111 Measured Load Transient Waveforms       3-11         3-11       SLVP112 Measured Load Regulation       3-11         3-12       SLVP112 Measured Efficiency       3-12         3-13       SLVP112 Measured Switching Frequency       3-13         3-14       SLVP112 Measured Switching Frequency       3-13         3-15       SLVP112 Measured Switching Waveforms       3-13         3-14       SLVP112 Measured Switching Waveforms       3-13         3-15       SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-14         3-17       SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-15         3-18                         | 2–6  | Output Ripple Voltage Detail 2-18                            |

| 3-3SLVP111Measured Efficiency3-73-4SLVP111Measured Power Dissipation3-83-5SLVP111Measured Switching Frequency3-83-6SLVP111 Measured Switching Waveforms3-93-7SLVP111Measured Start-Up (INHIBIT) Waveforms3-93-8SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-103-9SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-103-10SLVP111 Measured Load Transient Waveforms3-113-11SLVP112 Measured Load Regulation3-113-12SLVP112 Measured Efficiency3-123-13SLVP112 Measured Switching Frequency3-133-14SLVP112 Measured Switching Waveforms3-133-15SLVP112 Measured Switching Frequency3-133-16SLVP112 Measured Switching Waveforms3-143-17SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-18SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-153-19SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Coad Transient Waveforms3-153-19SLVP113 Measured Load Regulation3-163-20SLVP113 Measured Coad Transient Waveforms3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Start-Up (V_IN)3-163-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Frequency3-173-25SLVP113 Measured Switching Frequency3-183-25SLVP113 Measu                                                                                                                                | 3–1  | Test Setup                                                   |

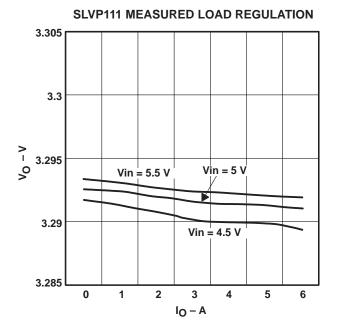

| 3-4       SLVP111Measured Power Dissipation       3-8         3-5       SLVP111Measured Switching Frequency       3-8         3-6       SLVP111 Measured Switching Waveforms       3-9         3-7       SLVP111Measured Start-Up (INHIBIT) Waveforms       3-9         3-8       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-10         3-9       SLVP111 Measured Start-Up (V <sub>IN</sub> ) Waveforms       3-10         3-10       SLVP111 Measured Load Transient Waveforms       3-11         3-11       SLVP112 Measured Load Regulation       3-11         3-12       SLVP112 Measured Efficiency       3-12         3-13       SLVP112 Measured Power Dissipation       3-12         3-14       SLVP112 Measured Switching Frequency       3-13         3-15       SLVP112 Measured Switching Waveforms       3-13         3-16       SLVP112 Measured Start-Up (INHIBIT) Waveforms       3-14         3-17       SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-14         3-18       SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms       3-15         3-19       SLVP112 Measured Coad Transient Waveforms       3-15         3-19       SLVP113 Measured Coad Regulation       3-16             | 3–2  | SLVP111 Measured Load Regulation 3-7                         |

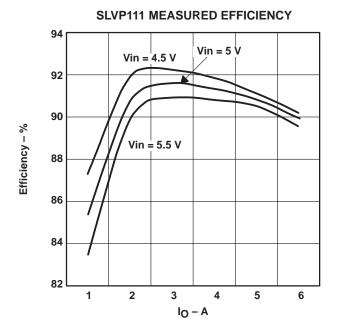

| 3-5SLVP111Measured Switching Frequency3-83-6SLVP111 Measured Switching Waveforms3-93-7SLVP111Measured Start-Up (INHIBIT) Waveforms3-93-8SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-103-9SLVP111 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-103-10SLVP111 Measured Load Transient Waveforms3-113-11SLVP112 Measured Load Regulation3-113-12SLVP112 Measured Efficiency3-123-13SLVP112 Measured Switching Frequency3-133-14SLVP112 Measured Switching Frequency3-133-15SLVP112 Measured Switching Waveforms3-143-16SLVP112 Measured Switching Waveforms3-143-17SLVP112 Measured Switching Waveforms3-143-18SLVP112 Measured Switching Waveforms3-133-14SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-17SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-153-19SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-153-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Switching Frequency3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                    | 3–3  | SLVP111Measured Efficiency 3-7                               |

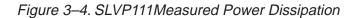

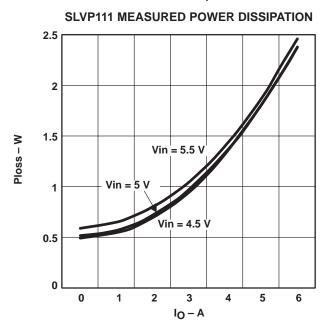

| 3-5SLVP111Measured Switching Frequency3-83-6SLVP111 Measured Switching Waveforms3-93-7SLVP111Measured Start-Up (INHIBIT) Waveforms3-93-8SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-103-9SLVP111 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-103-10SLVP111 Measured Load Transient Waveforms3-113-11SLVP112 Measured Load Regulation3-113-12SLVP112 Measured Efficiency3-123-13SLVP112 Measured Switching Frequency3-133-14SLVP112 Measured Switching Frequency3-133-15SLVP112 Measured Switching Waveforms3-143-16SLVP112 Measured Switching Waveforms3-143-17SLVP112 Measured Switching Waveforms3-143-18SLVP112 Measured Switching Waveforms3-133-14SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-17SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-153-19SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-153-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Switching Frequency3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                    | 3–4  | SLVP111Measured Power Dissipation                            |

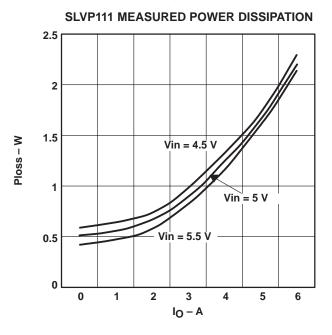

| 3-7SLVP111Measured Start-Up (INHIBIT) Waveforms3-93-8SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-103-9SLVP111Measured Start-Up (V <sub>IN</sub> ) Waveforms3-103-10SLVP111 Measured Load Transient Waveforms3-113-11SLVP112 Measured Load Regulation3-113-12SLVP112 Measured Power Dissipation3-123-13SLVP112 Measured Switching Frequency3-133-14SLVP112 Measured Switching Waveforms3-133-15SLVP112 Measured Switching Waveforms3-143-17SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-18SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-153-20SLVP112 Measured Load Regulation3-163-21SLVP113 Measured Load Regulation3-163-22SLVP113 Measured Efficiency3-163-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Frequency3-173-25SLVP113 Measured Switching Frequency3-183-25SLVP113 Measured Switching Frequency3-18                                                                                                                                                                                                                                                                                                                                                                                                                    | 3–5  |                                                              |

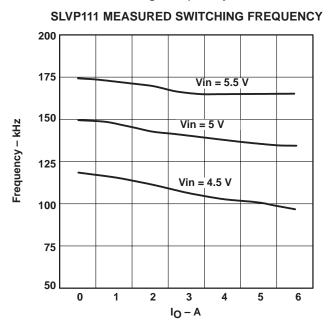

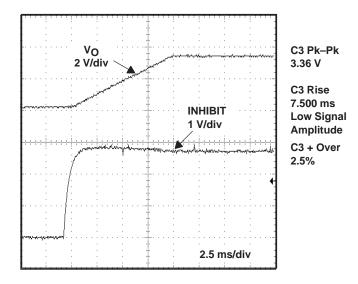

| 3-7SLVP111Measured Start-Up (INHIBIT) Waveforms3-93-8SLVP111 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-103-9SLVP111Measured Start-Up (V <sub>IN</sub> ) Waveforms3-103-10SLVP111 Measured Load Transient Waveforms3-113-11SLVP112 Measured Load Regulation3-113-12SLVP112 Measured Power Dissipation3-123-13SLVP112 Measured Switching Frequency3-133-14SLVP112 Measured Switching Waveforms3-133-15SLVP112 Measured Switching Waveforms3-143-17SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-18SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-153-20SLVP112 Measured Load Regulation3-163-21SLVP113 Measured Load Regulation3-163-22SLVP113 Measured Efficiency3-163-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Frequency3-173-25SLVP113 Measured Switching Frequency3-183-25SLVP113 Measured Switching Frequency3-18                                                                                                                                                                                                                                                                                                                                                                                                                    | 3–6  | SLVP111 Measured Switching Waveforms 3-9                     |

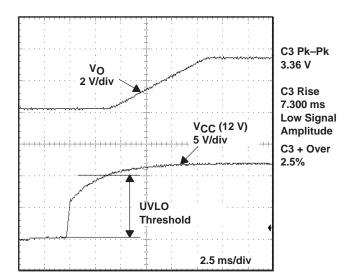

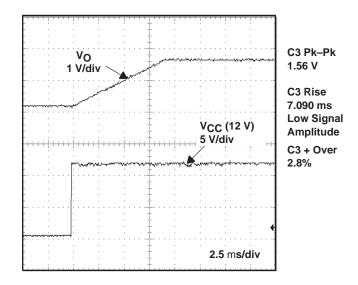

| 3-9SLVP111Measured Start-Up (V <sub>IN</sub> ) Waveforms3-103-10SLVP111 Measured Load Transient Waveforms3-113-11SLVP112 Measured Load Regulation3-113-12SLVP112 Measured Efficiency3-123-13SLVP112 Measured Power Dissipation3-123-14SLVP112 Measured Switching Frequency3-133-15SLVP112 Measured Switching Waveforms3-133-16SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-17SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-153-18SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-163-20SLVP113 Measured Load Transient Waveforms3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Switching Frequency3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Switching Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                      | 3–7  |                                                              |

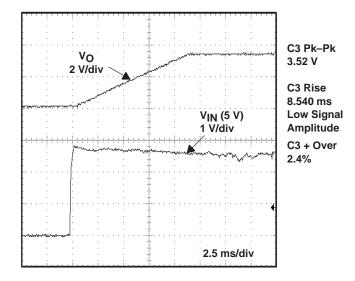

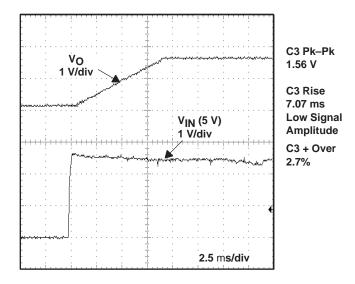

| 3-9SLVP111Measured Start-Up (V <sub>IN</sub> ) Waveforms3-103-10SLVP111 Measured Load Transient Waveforms3-113-11SLVP112 Measured Load Regulation3-113-12SLVP112 Measured Efficiency3-123-13SLVP112 Measured Power Dissipation3-123-14SLVP112 Measured Switching Frequency3-133-15SLVP112 Measured Switching Waveforms3-133-16SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-17SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-153-18SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-163-20SLVP113 Measured Load Transient Waveforms3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Switching Frequency3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Switching Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                      | 3–8  |                                                              |

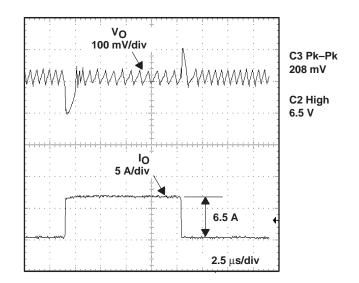

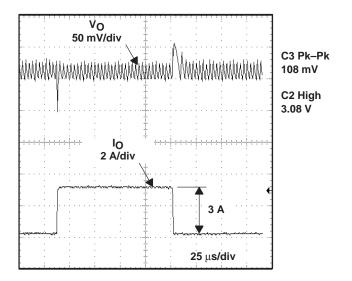

| 3-10SLVP111 Measured Load Transient Waveforms3-113-11SLVP112 Measured Load Regulation3-113-12SLVP112 Measured Efficiency3-123-13SLVP112 Measured Power Dissipation3-123-14SLVP112 Measured Switching Frequency3-133-15SLVP112 Measured Switching Waveforms3-133-16SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-17SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-153-18SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-163-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Switching Frequency3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Frequency3-183-25SLVP113 Measured Switching Frequency3-183-25SLVP113 Measured Switching Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3–9  |                                                              |

| 3-12SLVP112 Measured Efficiency3-123-13SLVP112 Measured Power Dissipation3-123-14SLVP112 Measured Switching Frequency3-133-15SLVP112 Measured Switching Waveforms3-133-16SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-17SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-143-18SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-163-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Switching Frequency3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Frequency3-183-25SLVP113 Measured Switching Waveforms3-183-26SLVP113 Measured Switching Frequency3-183-25SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3–10 |                                                              |

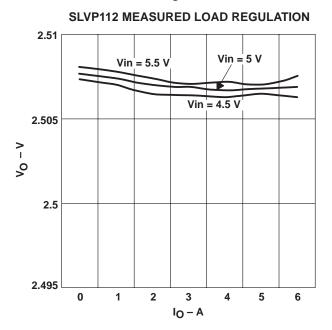

| 3-13SLVP112 Measured Power Dissipation3-123-14SLVP112 Measured Switching Frequency3-133-15SLVP112 Measured Switching Waveforms3-133-16SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-17SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-143-18SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-163-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Power Dissipation3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Vaveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3–11 | SLVP112 Measured Load Regulation                             |

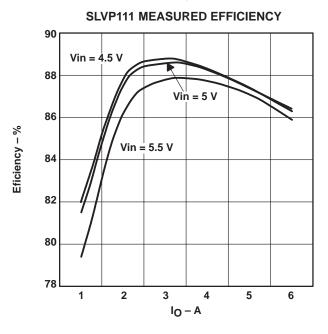

| 3-13SLVP112 Measured Power Dissipation3-123-14SLVP112 Measured Switching Frequency3-133-15SLVP112 Measured Switching Waveforms3-133-16SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-17SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-143-18SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-163-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Power Dissipation3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Vaveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3–12 | SLVP112 Measured Efficiency                                  |

| 3-14SLVP112 Measured Switching Frequency3-133-15SLVP112 Measured Switching Waveforms3-133-16SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-17SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-143-18SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-163-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Power Dissipation3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3–13 |                                                              |

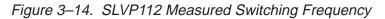

| 3-15SLVP112 Measured Switching Waveforms3-133-16SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-17SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-143-18SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-163-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Power Dissipation3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3–14 | •                                                            |

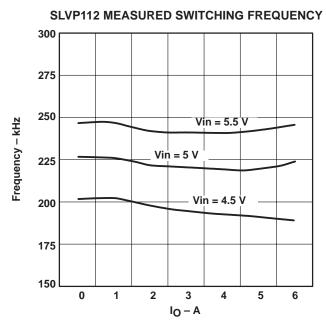

| 3-16SLVP112 Measured Start-Up (INHIBIT) Waveforms3-143-17SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-143-18SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-153-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Efficiency3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3–15 |                                                              |

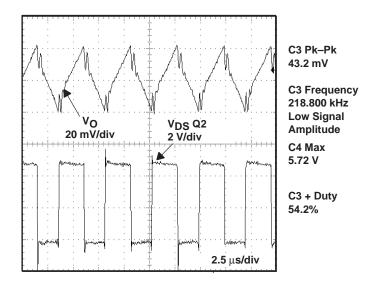

| 3-17SLVP112 Measured Start-Up (V <sub>CC</sub> ) Waveforms3-143-18SLVP112 Measured Start-Up (V <sub>IN</sub> ) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-153-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Power Dissipation3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3–16 |                                                              |

| 3-18SLVP112 Measured Start-Up (VIN) Waveforms3-153-19SLVP112 Measured Load Transient Waveforms3-153-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Power Dissipation3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3–17 |                                                              |

| 3-19SLVP112 Measured Load Transient Waveforms3-153-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Power Dissipation3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3–18 |                                                              |

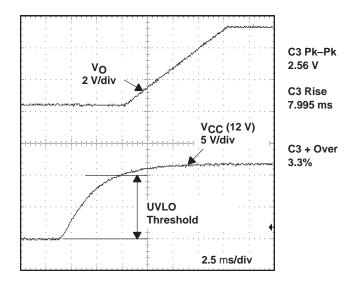

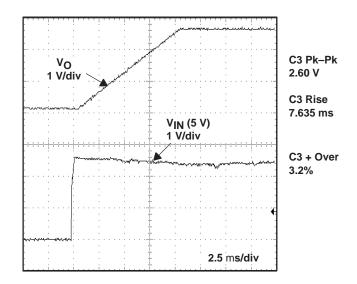

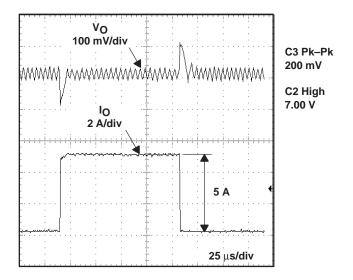

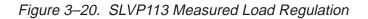

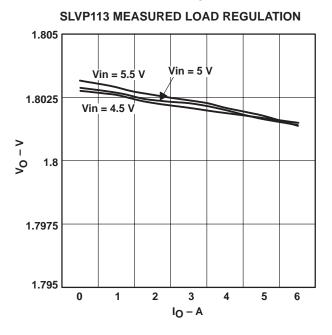

| 3-20SLVP113 Measured Load Regulation3-163-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Power Dissipation3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3–19 |                                                              |

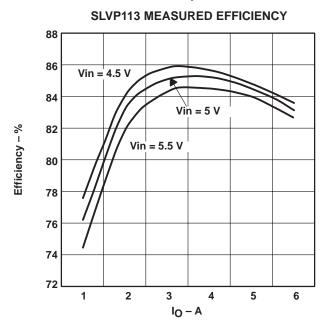

| 3-21SLVP113 Measured Efficiency3-163-22SLVP113 Measured Power Dissipation3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3–20 |                                                              |

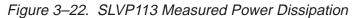

| 3-22SLVP113 Measured Power Dissipation3-173-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3–21 | •                                                            |

| 3-23SLVP113 Measured Switching Frequency3-173-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3–22 |                                                              |

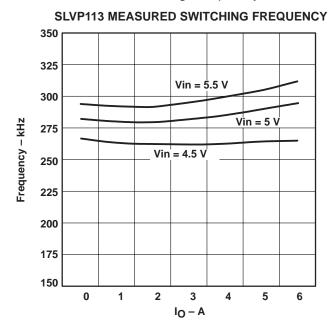

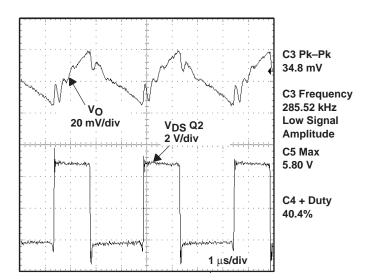

| 3-24SLVP113 Measured Switching Waveforms3-183-25SLVP113 Measured Start-Up (INHIBIT) Waveforms3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3–23 | •                                                            |

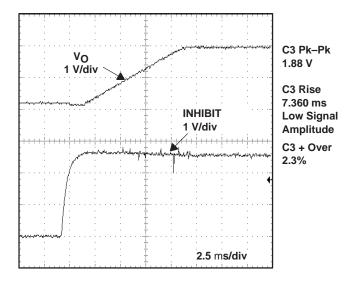

| 3–25 SLVP113 Measured Start-Up (INHIBIT) Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                                                              |

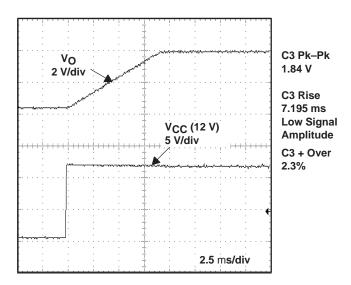

| 3–27 | SLVP113 Measured Start-Up (VIN) Waveforms              | 3-19 |

|------|--------------------------------------------------------|------|

| 3–28 | SLVP113 Measured Load Transient Waveforms              |      |

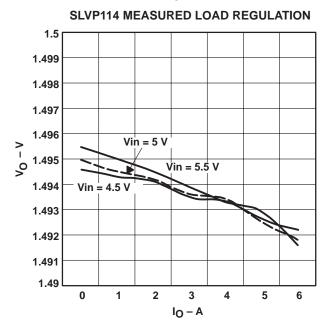

| 3–29 | SLVP114 Measured Load Regulation                       | 3-20 |

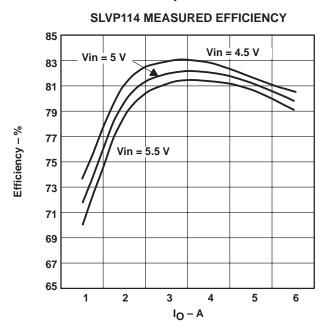

| 3–30 | SLVP114 Measured Efficiency                            | 3-21 |

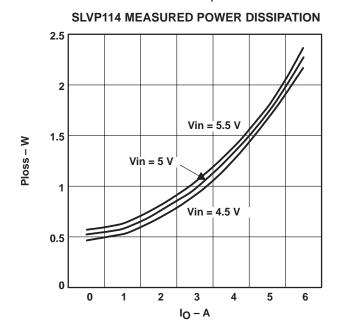

| 3–31 | SLVP114 Measured Power Dissipation                     | 3-21 |

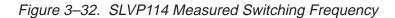

| 3–32 | SLVP114 Measured Switching Frequency                   | 3-22 |

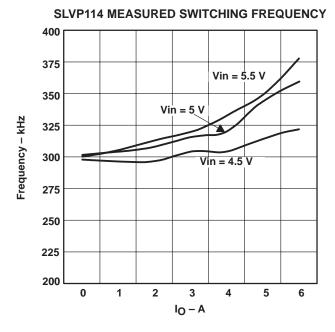

| 3–33 | SLVP114 Measured Switching Waveforms                   | 3-22 |

| 3–34 | SLVP114 Measured Start-Up (INHIBIT) Waveforms          | 3-23 |

| 3–35 | SLVP114 Measured Start-Up (V <sub>CC</sub> ) Waveforms | 3-23 |

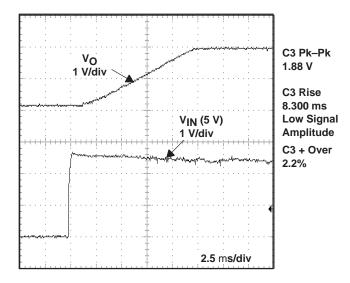

| 3–36 | SLVP114 Measured Start-Up (VIN) Waveforms              | 3-24 |

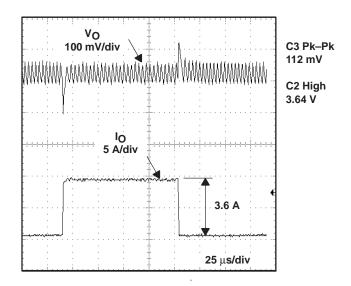

| 3–37 | SLVP114 Measured Load Transient Waveforms              | 3-24 |

### **Tables**

| 1–1 | Summary of EVM Converter Modules       | 1-4 |

|-----|----------------------------------------|-----|

| 1–2 | EVM Converter Operating Specifications | 1-5 |

| 1–3 | SLVP111–114 EVMs Bill of Materials     | 1-8 |

### **Chapter 1**

### Introduction

The SLVP111/112/113/114 evaluation modules (EVMs) have been designed and tested using the TPS56xx hysteretic controllers. These boards are synchronous dc-dc buck converters with fixed output voltages of 3.3 V, 2.5 V, 1.8 V and 1.5 V respectively. They use only surface mount components and are design examples of how to use TI's TPS56xx controllers in high density, low loss applications with tight static and dynamic output voltage requirements. Detailed test results taken from the EVMs are presented.

Design simplicity, low component count, and lower cost make buck converters popular solutions where low input voltages are available for the converter and where isolation is not a requirement.

This user's guide describes techniques for designing synchronous buck converters using TI's SLVP111–114 EVMs and TPS56xx ripple regulator controllers. Synchronous buck converters provide an elegant power supply solution for rapidly transitioning DSP loads (such as the Texas Instruments TMS320C62x/67x family), fast memory, and similar processors. An order of magnitude improvement in dynamic response of this converter over standard control methods reduces hold-up capacitance needs near the transitioning loads, thus saving cost and board space.

### Topic

#### Page

| 1.1 | Synchronous Buck Regulator Operation1-2 |

|-----|-----------------------------------------|

| 1.2 | Hysteretic Control Operation1-3         |

| 1.3 | Design Strategy1-4                      |

| 1.4 | Design Specification Summary1-5         |

| 1.5 | Schematic 1–7                           |

| 1.6 | Bill of Materials1-8                    |

| 1.7 | Board Layout 1–10                       |

### 1.1 Synchronous Buck Regulator Operation

The synchronous buck converter is a variation of the traditional buck converter. The main switching device is usually a power MOSFET and is driven in the same manner as in a traditional buck converter. The freewheeling rectifier, usually a Schottky device, is replaced by a power MOSFET and is driven in a complementary or synchronous fashion relative to the main switching device; when one MOSFET is on, the other is off. The freewheeling MOSFET is selected so that its ON voltage drop is less than the forward drop of the original freewheeling rectifier, thus increasing conversion efficiency. A very important design issue when using a synchronous buck converter is preventing cross-conduction of the two power MOSFETs, i.e., preventing both MOSFETs from being on simultaneously. A small amount of deadtime is necessary.

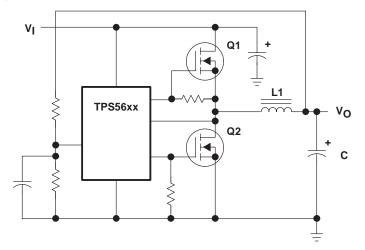

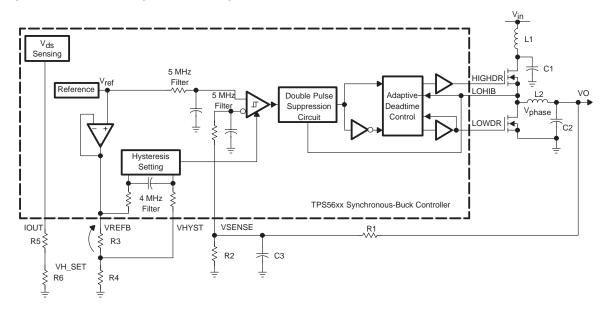

Figure 1 shows a simplified schematic of a synchronous buck converter. The TPS56xx senses the output voltage and then drives Q1 and Q2 depending on the sensed voltage. The TPS56xx senses the voltage at the junction of Q1, Q2, and L1 and uses it to actively prevent simultaneous conduction of Q1 and Q2.

Figure 1–1. Simplified Synchronous Buck Converter Schematic

### **1.2 Hysteretic Control Operation**

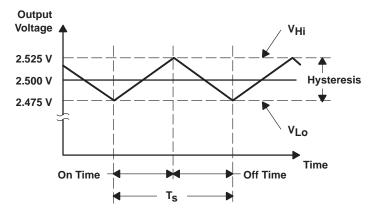

Hysteretic control, also called bang-bang control or ripple regulator control, maintains the output voltage within the hysteresis band centered about the internal reference voltage. Figure 1-2 shows a simplified example of a hysteretic controlled output voltage using the TPS5625 with a reference voltage of 2.500 V and a hysteresis band of 50 mV. If the output voltage is at or below the level of the reference minus one-half of the hysteresis band  $(V_{LO} = 2.475 \text{ V})$ , the TPS5625 turns off the low-side MOSFET (Q2 in Figure 1-1) and turns on the high-side MOSFET (Q1 in Figure 1-1) of the synchronous buck converter power stage. This is the power stage on-state, and it causes the output voltage to increase. When the output voltage reaches or exceeds the reference plus one-half of the hysteresis band ( $V_{Hi} = 2.525 V$ ), the TPS5625 turns off the high-side MOSFET and turns on the low-side MOSFET. This is the power stage off-state, and it causes the output voltage to decrease. This hysteretic method of control keeps the output voltage within the hysteresis band around the reference voltage. If output-load current steps or input-voltage transients force the output voltage out of the hysteresis band, the TPS5625 sets the power-stage MOSFETs in the continuous on or off state as required to return the output voltage to the hysteresis band. Thus, the output voltage is corrected as quickly as the output filter allows. There are no error amplifier sensing and adjusting delays, as is the case with either voltageor current-mode controllers. Other advantages of hysteretic control include no loop compensation design and no input filter interaction problems.

Figure 1–2. Simplified Hysteretic Controlled Output Voltage Waveform

### 1.3 Design Strategy

The SLVP111–114 evaluation modules (EVMs) are optimized for 5-V main input voltage and 6-A output current. The EVMs need an additional low current 12-V (30 mA max) input voltage for the controller. TI's application report, *Providing a DSP Power Solution from 5 V or 3.3 V Only Systems*, TI literature number SPRA525 describes how one can implement a simple boost circuit for 5-V only input voltage applications. These EVMs are pin to pin compatible with SLVP104/105/106/115 evaluation boards with 8 A output current, which combine surface mount and through hole components. This surface mount version has the same length, 2", and width, 0.75", but the height is significantly lower, 0.375" versus 0.6" for through hole version.

The TI SLVP111–114 evaluation modules (EVM) provide synchronous buck converter circuits for evaluating the capabilities of the TPS56xx family of ripple regulator controllers. The EVM converters can provide proven, demonstrated reference designs to aid in the rapid development of application-specific synchronous buck converters. Output capacities of the EVM converters are optimized for the Siliconix Si4410 power MOSFET device.

The 6-ampere output current level is a reasonable selection criteria for powering circuit cards with multiple DSPs, and for providing the regulated voltage to other hardware on the circuit card. Component size can be reduced for designs requiring lower power levels.

The TPS56xx controllers each provide one of four popular output voltage levels. The last two digits of the part number correlate to the set-point voltage level: TPS5633 is the 3.3-V controller, TPS5625 is the 2.5-V controller, TPS5618 is the 1.8-V controller, and TPS5615 is the 1.5-V controller. Many digital devices, memories, and DSP I/O circuits use the 3.3-V level. The core of the TMS320C6201 requires 2.5-V. All of the other DSPs in the TMS320C62x and the TMS320C67x family need 1.8 V. The GTL bus, as well as various processors and future DSPs, may require the 1.5-V controller. An external resistor divider can be used to fine tune the output voltages of these controllers for other applications including output voltages up to approximately  $V_{\rm IN}$  – 0.5 V.

Table 1–1 summarizes the four EVM converter modules.

| Table 1–1. Summary of EVM | Converter Modules |

|---------------------------|-------------------|

|---------------------------|-------------------|

| EVM Part Number | EVM Board<br>Number | Controller | Output<br>Voltage | Max. Output<br>Current |

|-----------------|---------------------|------------|-------------------|------------------------|

| TPS5633EVM-111  | SLVP111             | TPS5633    | 3.3 V             | 6 A†                   |

| TPS5625EVM-112  | SLVP112             | TPS5625    | 2.5 V             | 6 A†                   |

| TPS5618EVM-113  | SLVP113             | TPS5618    | 1.8 V             | 6 A†                   |

| TPS5615EVM-114  | SLVP114             | TPS5615    | 1.5 V             | 6 A†                   |

<sup>†</sup> Output current is limited by the temperature rise of the power MOSFETs chosen. Higher or lower current designs are possible.

### 1.4 Design Specification Summary

This section summarizes the design requirements of the EVM converters. Although every attempt was made to accurately describe the performance of the EVM converters and the TPS56xx controllers, in case of conflicts, the TPS56xx data sheet takes precedence over this document.

The TPS56xx family of controllers provides the necessary regulation functions. In addition to a reference voltage accuracy of  $\pm 1\%$  over the full operating temperature range, the controller has remote sense inputs to provide a precisely regulated output voltage. The controller also provides undervoltage lock-out, overload protection, overvoltage protection, and overtemperature protection. The controller has a logic level INHIBIT input to control the converter turn-on and turn-off and a power good output to indicate output voltage status. Undervoltage lock-out prevents operation of the power supply when the 12 Vdc input voltage is not sufficient for proper operation. Overload protection protects the power supply from accidental overloads or short circuits. Overvoltage protection prevents damage to the load in the event of an internal power supply failure or presence of high voltages on the output from an external condition. Both overvoltage and overcurrent cause a latched shutdown. Both power MOSFETs are driven to an OFF state. Recovery from shutdown requires removal of the 12 V control input supply for reset. Table 1-2 lists the operating specifications of the EVM converters.

| Specification                                                                                                     | Min                          | Тур                          | Мах                          | Units                    |

|-------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|--------------------------|

| Power input voltage range                                                                                         | 4.5                          |                              | 6                            | V                        |

| Control input voltage range                                                                                       | 10.8                         |                              | 13.2                         | V                        |

| Static voltage tolerance <sup>†</sup><br>SLVP111 (3.3 V)<br>SLVP112 (2.5 V)<br>SLVP113 (1.8 V)<br>SLVP114 (1.5 V) | 3.27<br>2.47<br>1.78<br>1.48 | 3.30<br>2.50<br>1.80<br>1.50 | 3.33<br>2.53<br>1.82<br>1.52 | V<br>V<br>V              |

| Line regulation <sup>‡</sup>                                                                                      |                              | ± 0.05%                      | ± 0.1%                       |                          |

| Load regulation§                                                                                                  |                              | ± 0.2%                       | ±0.4%                        |                          |

| Transient response¶                                                                                               |                              | ± 100<br>50                  |                              | mV pk<br>μsec            |

| Output current range#                                                                                             | 0                            |                              | 6                            | А                        |

| Current limit#                                                                                                    |                              |                              | 10                           | А                        |

| Operating frequency <sup>☆</sup><br>SLVP111 (3.3 V)<br>SLVP112 (2.5 V)<br>SLVP113 (1.8 V)<br>SLVP114 (1.8 V)      |                              | 135<br>225<br>295<br>360     |                              | kHz<br>kHz<br>kHz<br>kHz |

| Specification        | Min | Тур   | Max | Units  |

|----------------------|-----|-------|-----|--------|

| Output ripple        |     |       |     |        |

| SLVP111 (3.3 V)      |     | 66    |     | mV p–p |

| SLVP112 (2.5 V)      |     | 50    |     | mV p–p |

| SLVP113 (1.8 V)      |     | 36    |     | mV p–p |

| SLVP114 (1.5 V)      |     | 30    |     | mV p–p |

| Efficiency, 6 A load |     |       |     |        |

| SLVP111 (3.3 V)      |     | 90%   |     |        |

| SLVP112 (2.5 V)      |     | 86.4% |     |        |

| SLVP113 (1.8 V)      |     | 83.2% |     |        |

| SLVP114 (1.5 V)      |     | 79.8% |     |        |

| Efficiency, 4 A load |     |       |     |        |

| SLVP111 (3.3 V)      |     | 91.6% |     |        |

| SLVP112 (2.5 V)      |     | 88.6% |     |        |

| SLVP113 (1.8 V)      |     | 85.1% |     |        |

| SLVP114 (1.5 V)      |     | 81.9% |     |        |

### Table 1–2. EVM Converter Operating Specifications (Continued)

† Vi = 5 V, Io = 6 A

$\ddagger$  Io = 6 A, Vi = 5 V ±10%

§ Vi = 5 V

$\P$  Vi = 5 V, Io stepped repetitively from 0 A to 6.5 A

<sup>#</sup> Output current rating is limited by thermal considerations. Load currents above this rating may cause damage to the power supply.

|| Unless otherwise specified, all test conditions are  $T_A = 25$  °C, Vi = 5 V, Io = 6 A, Vo = nominal. \*Vi = 5 V, Io = 6 A, Vo = nominal

### 1.5 Schematic

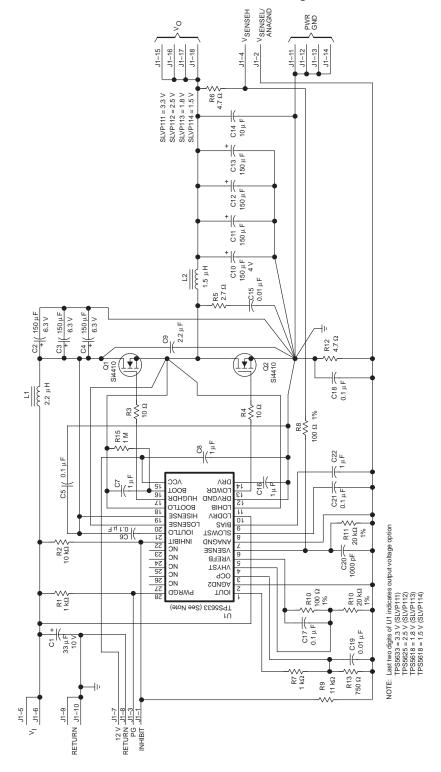

Figure 1–3 shows the EVM converter schematic diagram. The schematic diagrams for the other EVM converters are identical except for the controller IC used.

Figure 1–3. SLVP111–114 EVM Converter Schematic Diagram

### 1.6 Bill of Materials

Table 1–3 lists materials required for the SLVP111–114 EVMs.

| Ref Des | Part Number        | Description                                            | MFG       |

|---------|--------------------|--------------------------------------------------------|-----------|

| C1      | 10TPA33M           | Capacitor, POSCAP, 33 μF, 10 V, 20%                    | Sanyo     |

| C2      | 6TPB150M           | Capacitor, POSCAP, 150 μF, 6.3 V, 20%                  | Sanyo     |

| C3      | 6TPB150M           | Capacitor, POSCAP, 150 μF, 6.3 V, 20%                  | Sanyo     |