# MVME2600 Series Single Board Computer Installation and Use

#### V2600A/IH3

July 2001 Edition

© Copyright 1998, 2001 Motorola, Inc.

All rights reserved.

Printed in the United States of America.

Motorola<sup>®</sup> and the Motorola symbol are registered trademarks of Motorola, Inc.

AIX<sup>®</sup> is a registered trademark of International Business Machines Corporation.

PowerPC® is a registered trademark of International Business Machines.

SNAPHAT<sup>®</sup>, TIMEKEEPER<sup>®</sup>, and ZEROPOWER<sup>®</sup> are registered trademarks of STMicroelectronics.

All other products mentioned in this document are trademarks or registered trademarks of their respective holders.

## Safety Summary

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result in personal injury or damage to the equipment.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. If the equipment is supplied with a three-conductor AC power cable, the power cable must be plugged into an approved three-contact electrical outlet, with the grounding wire (green/yellow) reliably connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards and local electrical regulatory codes.

#### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in any explosive atmosphere such as in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment could result in an explosion and cause injury or damage.

#### Keep Away From Live Circuits Inside the Equipment.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified service personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Service personnel should not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, such personnel should always disconnect power and discharge circuits before touching components.

#### Use Caution When Exposing or Handling a CRT.

Breakage of a Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, do not handle the CRT and avoid rough handling or jarring of the equipment. Handling of a CRT should be done only by qualified service personnel using approved safety mask and gloves.

#### Do Not Substitute Parts or Modify Equipment.

Do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that all safety features are maintained.

#### **Observe Warnings in Manual.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

To prevent serious injury or death from dangerous voltages, use extreme caution when handling, testing, and adjusting this equipment and its components.

### Flammability

All Motorola PWBs (printed wiring boards) are manufactured with a flammability rating of 94V-0 by UL-recognized manufacturers.

### **EMI** Caution

This equipment generates, uses and can radiate electromagnetic energy. It may cause or be susceptible to electromagnetic interference (EMI) if not installed and used with adequate EMI protection.

### **Lithium Battery Caution**

This product contains a lithium battery to power the clock and calendar circuitry.

Danger of explosion if battery is replaced incorrectly. Replace battery only with the same or equivalent type recommended by the equipment manufacturer. Dispose of used batteries according to the manufacturer's instructions.

Il y a danger d'explosion s'il y a remplacement incorrect de la batterie. Remplacer uniquement avec une batterie du même type ou d'un type équivalent recommandé par le constructeur. Mettre au rebut les batteries usagées conformément aux instructions du fabricant.

Explosionsgefahr bei unsachgemäßem Austausch der Batterie. Ersatz nur durch denselben oder einen vom Hersteller empfohlenen Typ. Entsorgung gebrauchter Batterien nach Angaben des Herstellers.

### **CE Notice (European Community)**

Motorola Computer Group products with the CE marking comply with the EMC Directive (89/336/EEC). Compliance with this directive implies conformity to the following European Norms:

EN55022 "Limits and Methods of Measurement of Radio Interference Characteristics of Information Technology Equipment"; this product tested to Equipment Class B

EN50082-1:1997 "Electromagnetic Compatibility—Generic Immunity Standard, Part 1. Residential, Commercial and Light Industry"

System products also fulfill EN60950 (product safety) which is essentially the requirement for the Low Voltage Directive (73/23/EEC).

Board products are tested in a representative system to show compliance with the above mentioned requirements. A proper installation in a CE-marked system will maintain the required EMC/safety performance.

In accordance with European Community directives, a "Declaration of Conformity" has been made and is on file within the European Union. The "Declaration of Conformity" is available on request. Please contact your sales representative.

### Notice

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to the Motorola Computer Group website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Motorola, Inc.

It is possible that this publication may contain reference to or information about Motorola products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

### Limited and Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

### **About This Manual**

| Summary of Changes              | xviii |

|---------------------------------|-------|

| Overview of Contents            | xviii |

| Comments and Suggestions        | xix   |

| Conventions Used in This Manual | xx    |

### CHAPTER 1 Hardware Preparation and Installation

| Introduction                                               | 1-1  |

|------------------------------------------------------------|------|

| Equipment Required                                         | 1-3  |

| Overview of Startup Procedure                              | 1-3  |

| Unpacking Instructions                                     | 1-5  |

| Hardware Configuration                                     |      |

| MVME2603/2604 Base Board Preparation                       |      |

| Cache Mode Control (J3)                                    |      |

| Flash Bank Selection (J10)                                 |      |

| Serial Port 4 Receive Clock Configuration (J16)            |      |

| Serial Port 4 Transmit Clock Configuration (J17)           |      |

| Serial Port 4 Transmit Clock Receiver Buffer Control (J20) | 1-11 |

| Serial Port 3 Transmit Clock Configuration (J18)           | 1-12 |

| System Controller Selection (J22)                          | 1-13 |

| Remote Status and Control                                  | 1-14 |

| MVME712M Transition Module Preparation                     | 1-14 |

| Serial Ports 1-4 DCE/DTE Configuration                     | 1-17 |

| Serial Port 4 Clock Configuration                          | 1-17 |

| P2 Adapter Preparation                                     | 1-24 |

| MVME761 Transition Module Preparation                      | 1-25 |

| Serial Ports 1 and 2                                       | 1-27 |

| Configuration of Serial Ports 3 and 4                      | 1-27 |

| P2 Adapter Preparation (Three-Row)                         | 1-32 |

| P2 Adapter Preparation (Five-Row)                          | 1-33 |

| Hardware Installation                                      |      |

| RAM200 Memory Mezzanine Installation                       |      |

| PMC Module Installation                                    |      |

| PMC Carrier Board Installation                             |      |

| MVME2603/2604 VME Module Installation                      |      |

| MVME712M Transition Module Installation |  |

|-----------------------------------------|--|

| MVME761 Transition Module Installation  |  |

| System Considerations                   |  |

| MVME2603/2604 VME Module                |  |

### CHAPTER 2 Operating Instructions

| Introduction                       |      |

|------------------------------------|------|

| Applying Power                     |      |

| ABORT Switch (S1)                  |      |

| RESET Switch (S2)                  |      |

| Front Panel Indicators (DS1 – DS6) |      |

| Memory Maps                        |      |

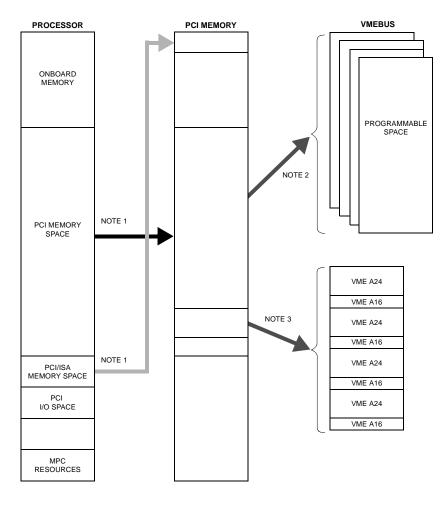

| Processor Memory Map               |      |

| Default Processor Memory Map       |      |

| PCI Local Bus Memory Map           |      |

| VMEbus Memory Map                  |      |

| Programming Considerations         |      |

| PCI Arbitration                    |      |

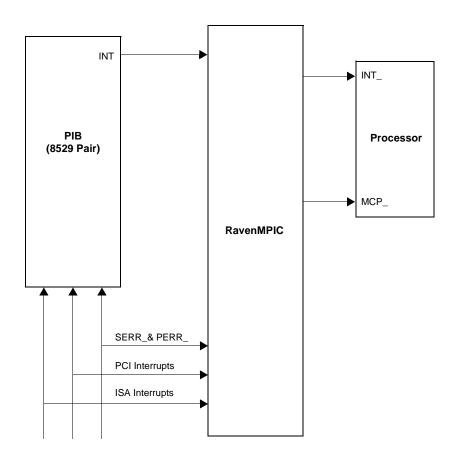

| Interrupt Handling                 |      |

| DMA Channels                       |      |

| Sources of Reset                   |      |

| Endian Issues                      | 2-15 |

| Processor/Memory Domain            | 2-15 |

| PCI Domain                         | 2-15 |

| VMEbus Domain                      | 2-16 |

### CHAPTER 3 Functional Description

| Introduction                  | 3-1 |

|-------------------------------|-----|

| Features                      | 3-1 |

| General Description           | 3-3 |

| Block Diagram                 |     |

| SCSI Interface                | 3-5 |

| SCSI Termination              | 3-5 |

| Ethernet Interface            | 3-6 |

| PCI Mezzanine Interface       | 3-7 |

| VMEbus Interface              | 3-8 |

| ISA Super I/O Device (ISASIO) | 3-8 |

| Asynchronous Serial Ports     | 3-9 |

| Parallel Port                 | 3-9 |

| Disk Drive Controller3-10Keyboard and Mouse Interface3-10PCI-ISA Bridge (PIB) Controller3-10Real-Time Clock/NVRAM/Timer Function3-11Programmable Timers3-12Interval Timers3-1216-Bit Timers3-13Serial Communications Interface3-13Z8536 CIO Device3-14Base Module Feature Register3-14P2 Signal Multiplexing3-15ABORT Switch (S1)3-16RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-22Serial Interface Modules3-22Serial Interface Modules3-22 |                              |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|

| PCI-ISA Bridge (PIB) Controller3-10Real-Time Clock/NVRAM/Timer Function3-11Programmable Timers3-12Interval Timers3-1216-Bit Timers3-13Serial Communications Interface3-13Z8536 CIO Device3-14Base Module Feature Register3-14P2 Signal Multiplexing3-15ABORT Switch (S1)3-16RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                           | Disk Drive Controller        | 3-10 |

| PCI-ISA Bridge (PIB) Controller3-10Real-Time Clock/NVRAM/Timer Function3-11Programmable Timers3-12Interval Timers3-1216-Bit Timers3-13Serial Communications Interface3-13Z8536 CIO Device3-14Base Module Feature Register3-14P2 Signal Multiplexing3-15ABORT Switch (S1)3-16RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                           | Keyboard and Mouse Interface | 3-10 |

| Real-Time Clock/NVRAM/Timer Function3-11Programmable Timers3-12Interval Timers3-1216-Bit Timers3-13Serial Communications Interface3-13Z8536 CIO Device3-14Base Module Feature Register3-14P2 Signal Multiplexing3-15ABORT Switch (S1)3-16RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                              |                              |      |

| Interval Timers3-1216-Bit Timers3-13Serial Communications Interface3-13Z8536 CIO Device3-14Base Module Feature Register3-14P2 Signal Multiplexing3-15ABORT Switch (S1)3-16RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                             |                              |      |

| 16-Bit Timers.3-13Serial Communications Interface3-13Z8536 CIO Device.3-14Base Module Feature Register3-14P2 Signal Multiplexing3-15ABORT Switch (S1)3-16RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power.3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory.3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                            | Programmable Timers          | 3-12 |

| Serial Communications Interface3-13Z8536 CIO Device3-14Base Module Feature Register3-14P2 Signal Multiplexing3-15ABORT Switch (S1)3-16RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                        | Interval Timers              | 3-12 |

| Serial Communications Interface3-13Z8536 CIO Device3-14Base Module Feature Register3-14P2 Signal Multiplexing3-15ABORT Switch (S1)3-16RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                        | 16-Bit Timers                | 3-13 |

| Base Module Feature Register3-14P2 Signal Multiplexing3-15ABORT Switch (S1)3-16RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                                                        |                              |      |

| P2 Signal Multiplexing3-15ABORT Switch (S1)3-16RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                                                                                        | Z8536 CIO Device             | 3-14 |

| ABORT Switch (S1)3-16RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                                                                                                                  | Base Module Feature Register | 3-14 |

| ABORT Switch (S1)3-16RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                                                                                                                  | P2 Signal Multiplexing       | 3-15 |

| RESET Switch (S2)3-16Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                                                                                                                                       |                              |      |

| Front Panel Indicators (DS1 – DS6)3-17Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                                                                                                                                                            |                              |      |

| Polyswitches (Resettable Fuses)3-18I/O Power3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                                                                                                                                                                                                  |                              |      |

| I/O Power.3-18Speaker Control3-19PM603/604 Processor3-19Flash Memory.3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                                                                                                                                                                                                                                   |                              |      |

| PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |      |

| PM603/604 Processor3-19Flash Memory3-20RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Speaker Control              |      |

| RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |      |

| RAM200 Memory Module3-20MVME712M Transition Module3-21MVME761 Transition Module3-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Flash Memory                 | 3-20 |

| MVME712M Transition Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |      |

| Serial Interface Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MVME761 Transition Module    |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Serial Interface Modules     | 3-22 |

### CHAPTER 4 Connector Pin Assignments

| MVME2603/2604 Connectors             | 4-1  |

|--------------------------------------|------|

| Common Connectors                    | 4-3  |

| LED Mezzanine Connector J1           | 4-3  |

| Debug Connector J2                   | 4-4  |

| Floppy/LED Connector J4              | 4-7  |

| PCI Expansion Connector J5           | 4-8  |

| Keyboard and Mouse Connectors J6, J8 | 4-11 |

| DRAM Mezzanine Connector J7          | 4-12 |

| PCI Mezzanine Card Connectors        | 4-15 |

| VMEbus Connector P1                  | 4-18 |

| MVME712M-Compatible Versions         | 4-19 |

| VMEbus Connector P2                  | 4-19 |

| SCSI Connector                       | 4-21 |

| Serial Ports 1-4                     | 4-22 |

| Parallel Connector                   |      |

|                                      |      |

| Ethernet AUI Connector               |  |

|--------------------------------------|--|

| MVME761-Compatible Versions          |  |

| VMEbus Connector P2                  |  |

| Serial Ports 1 and 2                 |  |

| Serial Ports 3 and 4                 |  |

| Parallel Connector                   |  |

| Ethernet 10BaseT/100BaseTX Connector |  |

### CHAPTER 5 PPCBug

| Overview              |  |

|-----------------------|--|

| Memory Requirements   |  |

| PPCBug Implementation |  |

| Using the Debugger    |  |

| Debugger Commands     |  |

| Diagnostic Tests      |  |

### CHAPTER 6 CNFG and ENV Commands

| Overview                                 |  |

|------------------------------------------|--|

| CNFG – Configure Board Information Block |  |

| ENV – Set Environment                    |  |

| Configuring the PPCBug Parameters        |  |

| Configuring the VMEbus Interface         |  |

### APPENDIX A Specifications

| Cooling Requirements | Specifications       |     |

|----------------------|----------------------|-----|

|                      | Cooling Requirements |     |

| FCC Compliance       | FCC Compliance       | A-3 |

### APPENDIX B Serial Interconnections

| Introduction              | B-1 |

|---------------------------|-----|

| Asynchronous Serial Ports | B-1 |

| Synchronous Serial Ports  |     |

| EIA-232-D Connections     |     |

| Interface Characteristics | B-5 |

| EIA-530 Connections       | B-6 |

| Interface Characteristics | B-8 |

| Proper Grounding          | B-9 |

| 1 0                       |     |

### APPENDIX C Troubleshooting CPU Boards: Solving Startup Problems

| IntroductionC-1 |

|-----------------|

|-----------------|

### APPENDIX D Related Documentation

| Motorola Computer Group Documents | D-1 |

|-----------------------------------|-----|

| Manufacturers' Documents          | D-2 |

| Related Specifications            | D-5 |

| Figure 1-1. MVME2603/2604 Base Board Block Diagram                   | 1-2  |

|----------------------------------------------------------------------|------|

| Figure 1-2. MVME2603/2604 Switches, Headers, Connectors, Fuses, LEDs | 1-9  |

| Figure 1-3. MVME712M Connector and Header Locations                  | 1-16 |

| Figure 1-4. J15 Clock Line Configuration                             | 1-17 |

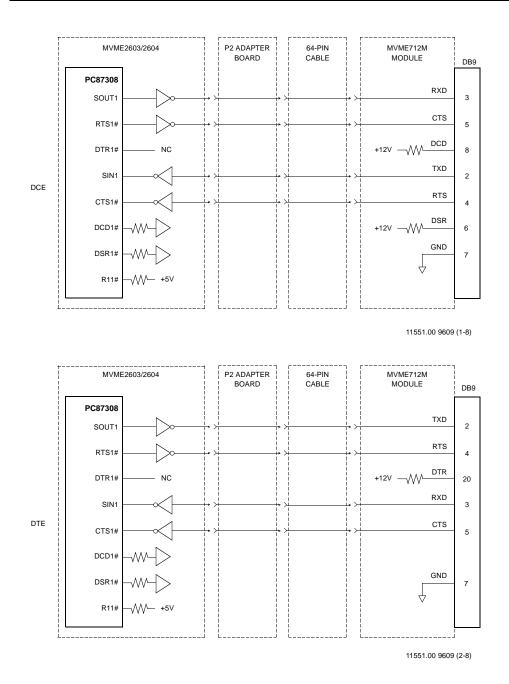

| Figure 1-5. MVME712M Serial Port 1 DCE/DTE Configuration             | 1-18 |

| Figure 1-6. MVME712M Serial Port 2 DCE/DTE Configuration             | 1-19 |

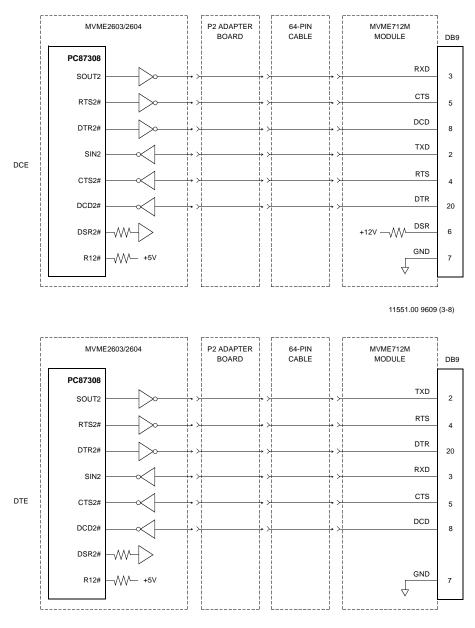

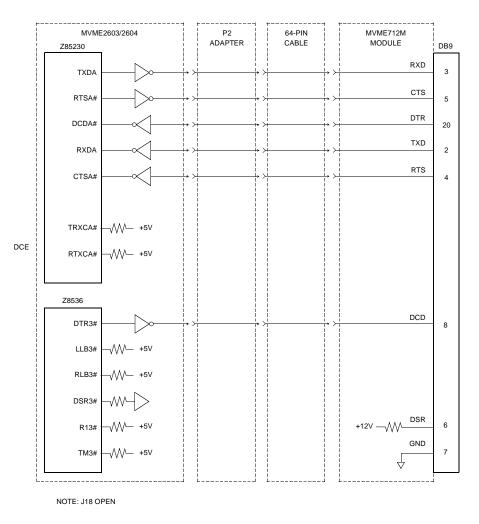

| Figure 1-7. MVME712M Serial Port 3 DCE Configuration                 | 1-20 |

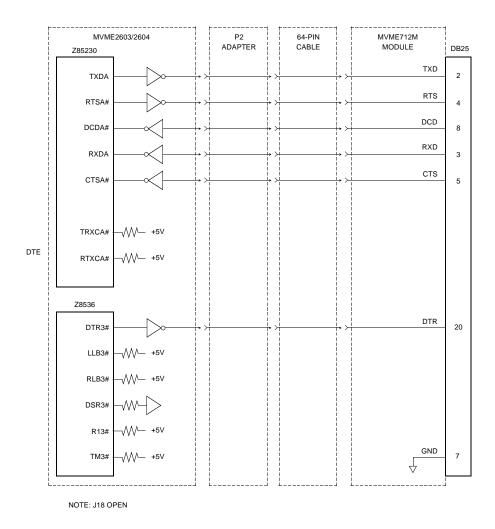

| Figure 1-8. MVME712M Serial Port 3 DTE Configuration                 | 1-21 |

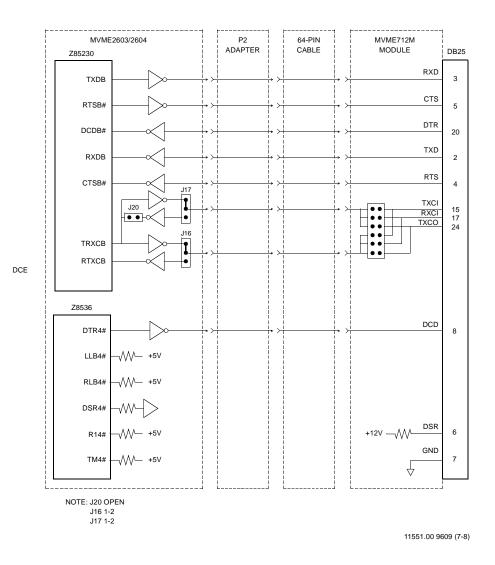

| Figure 1-9. MVME712M Serial Port 4 DCE Configuration                 | 1-22 |

| Figure 1-10. MVME712M Serial Port 4 DTE Configuration                | 1-23 |

| Figure 1-11. MVME712M P2 Adapter Component Placement                 | 1-24 |

| Figure 1-12. MVME761 Connector and Header Locations                  | 1-26 |

| Figure 1-13. MVME761 Serial Ports 1 and 2 (DCE Only)                 | 1-29 |

| Figure 1-14. MVME761 Serial Ports 3 and 4 DCE Configuration          | 1-30 |

| Figure 1-15. MVME761 Serial Ports 3 and 4 DTE Configuration          | 1-31 |

| Figure 1-16. MVME761 P2 Adapter (Three-Row) Component Placement      | 1-33 |

| Figure 1-17. MVME761 P2 Adapter (Five-Row) Component Placement       | 1-34 |

| Figure 1-18. RAM200 Placement on MVME2603/2604                       | 1-37 |

| Figure 1-19. PMC Module Placement on MVME2603/2604                   | 1-39 |

| Figure 1-20. PMC Carrier Board Placement on MVME2603/2604            | 1-41 |

| Figure 1-21. MVME712M/MVME2603/2604 Cable Connections                | 1-47 |

| Figure 1-22. MVME761/MVME2603/2604 Cable Connections                 | 1-49 |

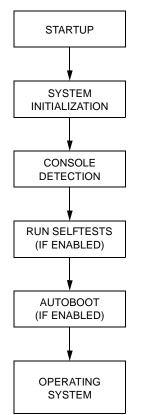

| Figure 2-1. PPCBug System Startup                                    | 2-2  |

| Figure 2-2. VMEbus Master Mapping                                    | 2-9  |

| Figure 2-3. MVME2603/MVME2604 Interrupt Architecture                 | 2-12 |

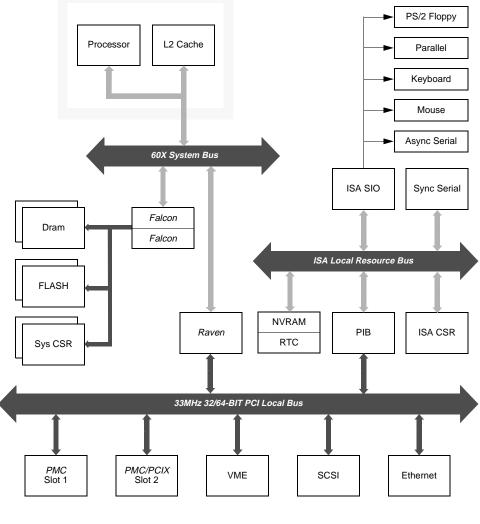

| Figure 3-1. MVME2603/2604 Block Diagram                              | 3-4  |

| Table 1-1. Startup Overview                                | 1-3  |

|------------------------------------------------------------|------|

| Table 1-2. MVME712M Port/Jumper Correspondence             | 1-17 |

| Table 2-1. Processor Default View of the Memory Map        | 2-6  |

| Table 2-2. PCI Arbitration Assignments                     | 2-10 |

| Table 2-3. IBC DMA Channel Assignments                     | 2-13 |

| Table 2-4. Classes of Reset and Effectiveness              | 2-14 |

| Table 3-1. MVME2603/2604 Features                          | 3-1  |

| Table 3-2. P2 Multiplexing Sequence                        | 3-15 |

| Table 3-3. Fuse Assignments                                | 3-18 |

| Table 3-4. SIM Type Identification                         | 3-23 |

| Table 4-1. LED Mezzanine Connector                         | 4-3  |

| Table 4-2. Debug Connector                                 |      |

| Table 4-3. Floppy/LED Connector                            | 4-7  |

| Table 4-4. PCI Expansion Connector                         | 4-8  |

| Table 4-5. Keyboard Connector                              | 4-11 |

| Table 4-6. Mouse Connector                                 | 4-11 |

| Table 4-7. DRAM Mezzanine Connector                        | 4-12 |

| Table 4-8. PCI Mezzanine Card Connector                    | 4-15 |

| Table 4-8. PCI Mezzanine Card Connector (Continued)        | 4-16 |

| Table 4-9. VMEbus Connector P1                             | 4-18 |

| Table 4-10. VMEbus Connector P2 (MVME712M I/O Mode)        | 4-19 |

| Table 4-11. SCSI Connector (MVME712M)                      | 4-21 |

| Table 4-12. Serial Connections—MVME712M Ports 1-4          | 4-22 |

| Table 4-13. Parallel I/O Connector (MVME712M)              | 4-23 |

| Table 4-14. Ethernet AUI Connector (MVME712M)              | 4-24 |

| Table 4-15. VMEbus Connector P2 (MVME761 I/O Mode)         | 4-25 |

| Table 4-16. Serial Connections—Ports 1 and 2 (MVME761)     | 4-26 |

| Table 4-17. Serial Connections—Ports 3 and 4 (MVME761)     | 4-27 |

| Table 4-18. Parallel I/O Connector (MVME761)               | 4-28 |

| Table 4-19. Ethernet 10BaseT/100BaseTX Connector (MVME761) |      |

| Table 5-1. Debugger Commands                               | 5-4  |

| Table 5-2. Diagnostic Test Groups                          | 5-8  |

| Table A-1. MVME2603/2604 Specifications                    | A-1  |

| Table B-1. EIA-232-D Interconnect Signals                  | B-3  |

|                                                            |      |

| Table B-2. EIA-232-D Interface Transmitter Characteristics | B-5 |

|------------------------------------------------------------|-----|

| Table B-3. EIA-232-D Interface Receiver Characteristics    | B-5 |

| Table B-4. MVME761 EIA-530 Interconnect Signals            | B-6 |

| Table B-5. EIA-530 Interface Transmitter Characteristics   | B-8 |

| Table B-6. EIA-530 Interface Receiver Characteristics      | B-9 |

| Table C-1. Troubleshooting MVME2603/2604 Boards            | C-1 |

# **About This Manual**

This manual provides general information, hardware preparation and installation instructions, operating instructions, and a functional description of the MVME2603/2604 family of single board computers.

As of the publication date, the information presented in this manual applies to the following MVME2603 and MVME2604 models:

| Model Number      | Description                           |

|-------------------|---------------------------------------|

| MVME2603-1121C to | 200 MHz MPC603, 16MB–256MB ECC DRAM,  |

| MVME2603-1161C    | 9MB Flash                             |

| MVME2603-3121 to  | 200 MHz MPC603, 16MB–256MB ECC DRAM,  |

| MVME2603-3161     | 9MB Flash                             |

| MVME2603-4121 to  | 200 MHz MPC603, 16MB–128MB ECC DRAM,  |

| MVME2603-4151     | 9MB Flash                             |

| MVME2603-5121 to  | 200 MHz MPC603, 16MB–32MB ECC DRAM,   |

| MVME2603-5131     | 9MB Flash                             |

| MVME2604-1321 to  | 333 MHz MPC604, 16MB–256MB ECC DRAM,  |

| MVME2604-1361     | 9MB Flash                             |

| MVME2604-4321 to  | 333 MHz MPC604, 16MB–256MB ECC DRAM,  |

| MVME2604-4361     | 9MB Flash                             |

| MVME2604-1401 to  | 400 MHz MPC604, 0–512MB ECC DRAM, 9MB |

| MVME2604-1471     | Flash                                 |

| MVME2604-3321 to  | 400 MHz MPC604, 16MB–256MB ECC DRAM,  |

| MVME2604-3361     | 9MB Flash                             |

| MVME2604-3401 to  | 400 MHz MPC604, 0–512MB ECC DRAM, 9MB |

| MVME2604-3471     | Flash                                 |

| MVME2604-4401 to  | 400 MHz MPC604, 0–512MB ECC DRAM, 9MB |

| MVME2604-4471     | Flash                                 |

# **Summary of Changes**

This is the third edition of the *Installation and Use* manual. It supersedes the May 1998 edition and incorporates the following updates.

| Date      | Changes                                                                                                                                                                                                                                                                           | Replaces   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| July 2001 | All data referring to the VME CSR Bit Set Register<br>(VCSR_SET) and VME CSR Bit Clear Register<br>(VCSR_CLR) has been deleted. These registers of<br>the Universe II are unavailable for implementation<br>as intended by the MVME materials and the<br>Universe II User Manual. | V2600A/IH2 |

# **Overview of Contents**

Chapter 1, *Hardware Preparation and Installation*, provides general information, hardware preparation and installation instructions, operating instructions, and a functional description of the MVME2603/2604 family of single board computers.

Chapter 2, *Operating Instructions*, supplies information for use of the MVME2603/2604 family of single board computers in a system configuration.

Chapter 3, *Functional Description*, describes the MVME2603/2604 single board computer on a block diagram level.

Chapter 4, *Connector Pin Assignments*, provides pin assignments for the interconnect signals for the MVME2603/2604 family of single board computers.

Chapter 5, *PPCBug*, describes the basics of PPCBug and its architecture, describes the monitor (interactive command portion of the firmware) in detail, and gives information on actually using the PPCBug debugger and the special commands.

Chapter 6, *CNFG and ENV Commands*, contains information about the **CNFG** and **ENV** commands. These two commands are used to change configuration information and command parameters interactively.

Appendix A, *Specifications*, lists the general specifications for MVME2603/2604 base boards.

Appendix B, *Serial Interconnections*, describes the MVME2603/2604 serial communications interfaces.

Appendix C, *Troubleshooting CPU Boards: Solving Startup Problems*, supplies the user with troubleshooting tips before having to call for help.

Appendix D, *Related Documentation*, lists all documentation related to the MVME2603/2604 single board computer.

# **Comments and Suggestions**

Motorola welcomes and appreciates your comments on its documentation. We want to know what you think about our manuals and how we can make them better. Mail comments to:

Motorola Computer Group Reader Comments DW164 2900 S. Diablo Way Tempe, Arizona 85282

You can also submit comments to the following e-mail address: reader-comments@mcg.mot.com

In all your correspondence, please list your name, position, and company. Be sure to include the title and part number of the manual and tell how you used it. Then tell us your feelings about its strengths and weaknesses and any recommendations for improvements.

# **Conventions Used in This Manual**

The following typographical conventions are used in this document:

#### bold

is used for user input that you type just as it appears; it is also used for commands, options and arguments to commands, and names of programs, directories and files.

#### italic

is used for names of variables to which you assign values. Italic is also used for comments in screen displays and examples, and to introduce new terms.

#### courier

is used for system output (for example, screen displays, reports), examples, and system prompts.

#### <Enter>, <Return> or <CR>

<CR> represents the carriage return or Enter key.

#### Ctrl

represents the Control key. Execute control characters by pressing the Ctrl key and the letter simultaneously, for example, **Ctrl-d**.

# Introduction

The MVME2603/2604 is a single-slot VME module equipped with a PowerPC<sup>®</sup> Series microprocessor. The MVME2603 is equipped with a PowerPC 603<sup>TM</sup> microprocessor; the MVME2604 has a PowerPC 604<sup>TM</sup> microprocessor. 256KB L2 cache (level 2 secondary cache memory) is available as an option on all versions.

The complete MVME2603/2604 consists of the base board plus:

- □ An ECC DRAM module (RAM200) for memory

- □ An optional PCI mezzanine card (PMC) for additional versatility

- □ An optional carrier board for additional PCI expansion

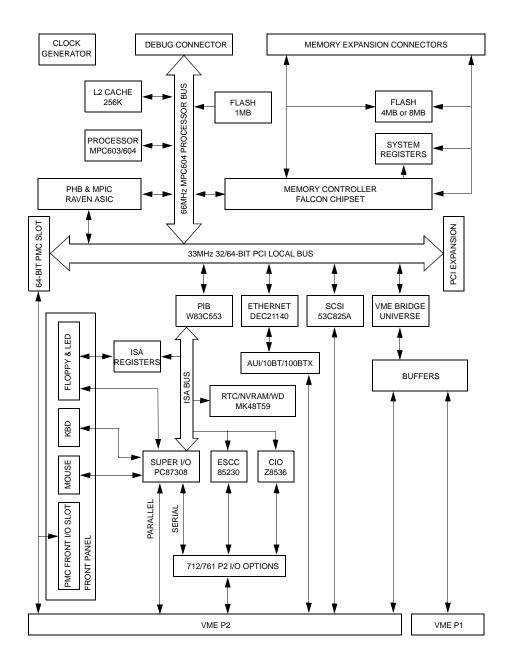

The block diagram in Figure 1-1 illustrates the architecture of the MVME2603/2604 base board.

Figure 1-1. MVME2603/2604 Base Board Block Diagram

1

1

# **Equipment Required**

The following equipment is required to complete an MVME2603/2604 system:

- □ VME system enclosure

- □ System console terminal

- Operating system (and/or application software)

- Disk drives (and/or other I/O) and controllers

- □ Transition module (MVME712M or MVME761) and connecting cables

MVME2603/2604 VME modules are factory-configured for I/O handling via either MVME712M or MVME761 transition modules.

# **Overview of Startup Procedure**

The following table lists the things you will need to do before you can use this board and tells where to find the information you need to perform each step. Be sure to read this entire chapter, including all Caution and Warning notes, before you begin.

| What you need to do                                                             | Refer to                                                                                                                                                                                     |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unpack the hardware.                                                            | Unpacking Instructions on page 1-5                                                                                                                                                           |

| Configure the hardware by setting jumpers on the boards and transition modules. | <i>MVME2603/2604 Base Board Preparation</i> on page 1-6<br>and <i>MVME712M Transition Module Preparation</i> on<br>page 1-14 or <i>MVME761 Transition Module Preparation</i><br>on page 1-25 |

| Ensure memory mezzanines are properly installed on the base board.              | RAM200 Memory Mezzanine Installation on page 1-35                                                                                                                                            |

| Install the MVME2603/2604 VME module in the chassis.                            | <i>MVME2603/2604 VME Module Installation</i> on page 1-42                                                                                                                                    |

| Table | 1-1. | Startup | Overview |

|-------|------|---------|----------|

|-------|------|---------|----------|

| What you need to do                                | Refer to                                                                                                                                                |  |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Install the transition module in the chassis.      | <i>MVME712M Transition Module Installation</i> on page 1-44 or <i>MVME761 Transition Module Installation</i> on page 1-48                               |  |

| Connect a console terminal.                        | <i>System Considerations</i> on page 1-50, MVME2603/2604<br>VME module                                                                                  |  |

| Connect any other equipment you                    | Chapter 4, Connector Pin Assignments                                                                                                                    |  |

| will be using.                                     | For more information on optional devices and<br>equipment, refer to the documentation provided with the<br>equipment.                                   |  |

| Power up the system.                               | Applying Power on page 2-1                                                                                                                              |  |

|                                                    | Appendix C, Troubleshooting CPU Boards: Solving<br>Startup Problems                                                                                     |  |

| Note that the debugger initializes                 | Using the Debugger on page 5-3                                                                                                                          |  |

| the MVME2603/2604.                                 | You may also wish to obtain the <i>PPCBug Firmware</i><br><i>Package User's Manual</i> , listed in Appendix D, <i>Related</i><br><i>Documentation</i> . |  |

| Initialize the system clock.                       | <i>Using the Debugger</i> on page 5-3, Debugger Commands, the <b>SET</b> command                                                                        |  |

| Examine and/or change<br>environmental parameters. | Chapter 6, CNFG and ENV Commands                                                                                                                        |  |

| Program the board as needed for your applications. | MVME2600 Series Single Board Computer<br>Programmer's Reference Guide, listed in Appendix D,<br>Related Documentation.                                  |  |

Table 1-1. Startup Overview (Continued)

# **Unpacking Instructions**

**Note** If the shipping carton is damaged upon receipt, request that the carrier's agent be present during the unpacking and inspection of the equipment.

Unpack the equipment from the shipping carton. Refer to the packing list and verify that all items are present. Save the packing material for storing and reshipping of equipment.

Avoid touching areas of integrated circuitry; static discharge can damage circuits.

# **Hardware Configuration**

To produce the desired configuration and ensure proper operation of the MVME2603/2604, you may need to carry out certain hardware modifications before installing the module.

The MVME2603/2604 provides software control over most options: by setting bits in control registers after installing the module in a system, you can modify its configuration. (The MVME2603/2604 control registers are described in Chapter 3, *Functional Description*, and/or in the *MVME2600 Series Single Board Computer Programmer's Reference Guide*, as listed in Appendix D, *Related Documentation*.)

Some options, however, are not software-programmable. Such options are controlled through manual installation or removal of header jumpers or interface modules on the base board or the associated transition module.

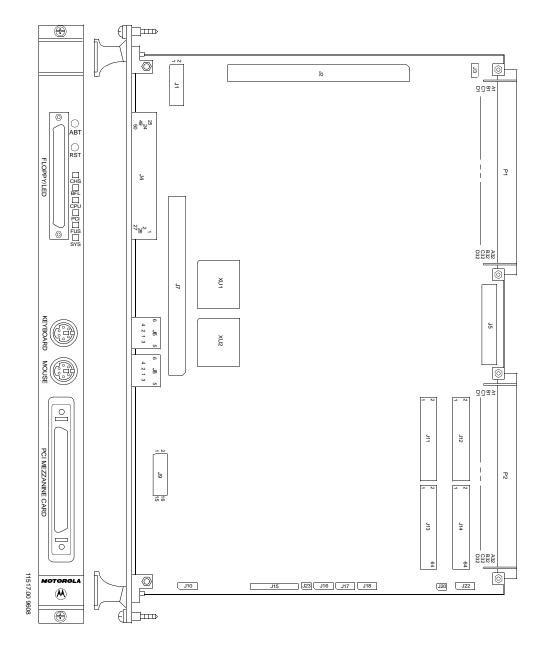

# **MVME2603/2604 Base Board Preparation**

Figure 1-2 on page 1-9 illustrates the placement of the switches, jumper headers, connectors, and LED indicators on the MVME2603/2604. Manually configurable items on the base board include:

- □ Cache mode control (J3)

- □ Flash bank selection (J10)

- □ Serial Port 4 receive clock configuration (J16)

- □ Serial Port 4 transmit clock configuration (J17)

- □ Serial Port 4 transmit clock receiver buffer control (J20)

- □ Serial Port 3 transmit clock configuration (J18)

- □ System controller selection (J22)

In conjunction with the serial port settings on the base board, serial ports on the associated MVME712M or MVME761 transition module are also manually configurable. For a discussion of the configurable items on the transition module, refer to *MVME712M Transition Module Preparation* on page 1-14, *MVME761 Transition Module Preparation* on page 1-25, or to the respective user's manuals for the transition modules (listed in Appendix D, *Related Documentation*) as necessary.

The MVME2603/2604 is factory tested and shipped with the configurations described in the following sections. The MVME2603/2604's required and factory-installed debug monitor, PPCBug, operates with those factory settings.

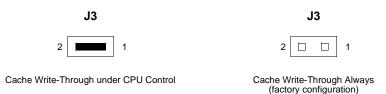

### **Cache Mode Control (J3)**

256KB of L2 cache memory is available on the MVME2603/2604. L2 cache operation is transparent to users, but its write-through mode is configurable via header J3 on older boards. *On newer MVME2603/2604 boards, header J3 is not provided*. With a jumper installed on J3, cache write-through is under CPU control. With the jumper removed, cache write-through occurs in all cases.

### Flash Bank Selection (J10)

The MVME2603/2604 base board has provision for 1MB of 16-bit Flash memory. The RAM200 memory mezzanine accommodates 4MB or 8MB of additional 64-bit Flash memory.

The Flash memory is organized in either one or two banks, each bank either 16- or 64-bits wide. Both banks contain the onboard debugger, PPCBug.

To enable Flash bank A (4MB or 8MB of firmware resident on solderedin devices on the RAM200 mezzanine), place a jumper across header J10 pins 1 and 2. To enable Flash bank B (1MB of firmware located in sockets on the base board), place a jumper across header J10 pins 2 and 3.

Flash Bank B Enabled (1MB, Sockets)

(factory configuration)

### Serial Port 4 Receive Clock Configuration (J16)

In synchronous serial communications, you can configure Serial Port 4 on the MVME2603/2604 to use the clock signals provided by the RxC signal line. On *MVME712M-compatible* versions of the base board, header J16 configures port 4 to either drive or receive RxC. The factory configuration has port 4 set to receive RxC. J16 remains open on MVME761-compatible versions.

To complete the configuration of Serial Port 4, you must set the following configuration headers as well:

- □ J17 (Serial Port 4 transmit clock configuration)

- □ J20 (Serial Port 4 transmit clock receiver buffer control)

- □ J15 on the MVME712M transition module or J3 on the MVME761 transition module (Serial Port 4 clock configuration)

Figure 1-9 and Figure 1-10 (for the MVME712M) and Figure 1-14 and Figure 1-15 (for the MVME761) diagram the overall jumper settings required on the MVME2603/2604 and transition module for a Serial Port 4 DCE or DTE configuration.

For additional details on the configuration of those headers, refer to *MVME712M Transition Module Preparation* on page 1-14, *MVME761 Transition Module Preparation* on page 1-25, or to the respective user's manuals for the transition modules (listed in Appendix D, *Related Documentation*) as necessary.

Figure 1-2. MVME2603/2604 Switches, Headers, Connectors, Fuses, LEDs

1

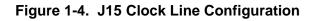

### Serial Port 4 Transmit Clock Configuration (J17)

In synchronous serial communications, you can configure Serial Port 4 on the MVME2603/2604 to use the clock signals provided by the TxC signal line. Header J17 configures port 4 to either drive or receive TxC. The factory configuration has port 4 set to receive TxC.

To complete the configuration of Serial Port 4, you must set the following configuration headers as well:

- □ J16 (Serial Port 4 receive clock configuration)

- □ J20 (Serial Port 4 transmit clock receiver buffer control)

- □ J15 on the MVME712M transition module or J3 on the MVME761 transition module (Serial Port 4 clock configuration)

Figure 1-9 and Figure 1-10 (for the MVME712M) and Figure 1-14 and Figure 1-15 (for the MVME761) diagram the overall jumper settings required on the MVME2603/2604 and transition module for a Serial Port 4 DCE or DTE configuration.

For additional details on the configuration of those headers, refer to *MVME712M Transition Module Preparation* on page 1-14, *MVME761 Transition Module Preparation* on page 1-25, or to the respective user's manuals for the transition modules (listed in Appendix D, *Related Documentation*) as necessary.

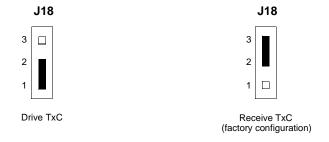

Receive TxC (factory configuration)

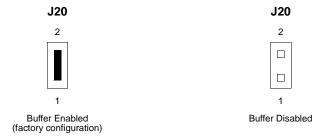

# Serial Port 4 Transmit Clock Receiver Buffer Control (J20)

As described in other sections, a complete configuration of Serial Port 4 requires that you set the following jumper headers on the MVME2603/2604 or the transition module:

- □ J16 (Serial Port 4 receive clock configuration) on *MVME712Mcompatible* versions of the base board

- □ J17 (Serial Port 4 transmit clock configuration)

- □ J20 (Serial Port 4 transmit clock receiver buffer control) on *MVME712M-compatible* versions of the base board

- □ J15 on the MVME712M transition module or J3 on the MVME761 (Serial Port 4 clock configuration)

A transmit clock receiver buffer (controlled by header J20) is associated with Serial Port 4. Installing a jumper on J20 enables the buffer. Removing the jumper disables the buffer. The factory configuration has the Serial Port 4 buffer enabled.

J20 remains open on MVME761-compatible versions. On MVME712Mcompatible versions, J20 is set in tandem with J17 to configure the Serial Port 4 transmit clock. If one deviates from the factory configuration, so must the other.

Figure 1-9 and Figure 1-10 (for the MVME712M) and Figure 1-14 and Figure 1-15 (for the MVME761) diagram the overall jumper settings required on the MVME2603/2604 and transition module for a Serial Port 4 DCE or DTE configuration.

For additional details on the configuration of those headers, refer to *MVME712M Transition Module Preparation* on page 1-14, *MVME761 Transition Module Preparation* on page 1-25, or to the respective user's manuals for the transition modules (listed in Appendix D, *Related Documentation*) as necessary.

## Serial Port 3 Transmit Clock Configuration (J18)

In synchronous serial communications using the MVME761 transition module, you can configure Serial Port 3 on the MVME2603/2604 to use the clock signals provided by the TxC signal line. On *MVME761-compatible* versions of the base board, header J18 configures port 3 to either drive or receive TxC. The factory configuration has port 3 set to receive TxC. J18 remains open on MVME712M-compatible versions.

To complete the configuration of Serial Port 3, you must set J2 on the MVME761 transition module (Serial Port 3 clock configuration) as well.

Figure 1-7 and Figure 1-8 (for the MVME712M) and Figure 1-14 and Figure 1-15 (for the MVME761) diagram the overall jumper settings required on the MVME2603/2604 and transition module for a Serial Port 3 DCE or DTE configuration.

For additional details on the configuration of the MVME761 headers, refer to *MVME761 Transition Module Preparation* on page 1-25 or to the user's manual for the module (listed in Appendix D, *Related Documentation*).

### System Controller Selection (J22)

The MVME2603/2604 is factory-configured as a VMEbus system controller by jumper header J22. If you select the "automatic" system controller function by placing a jumper on J22 pins 2 and 3, the MVME2603/2604 determines whether it is the system controller by its position on the bus. If the board is in the first slot from the left, it configures itself as the system controller. If the MVME2603/2604 is not to be system controller under any circumstances, place the jumper on J22 pins 1 and 2. When the board is functioning as system controller, the SCON LED is turned on.

Not System Controller

J22 3 2 1 □

Auto System Controller

(factory configuration)

J22 3 □ 2 □ 1 □

System Controller

### **Remote Status and Control**

The MVME2603/2604 front panel LEDs and switches are mounted on a removable mezzanine board. Removing the LED mezzanine makes the mezzanine connector (J1, a keyed double-row 14-pin connector) available for service as a remote status and control connector. In this application, J1 can be connected to a user-supplied external cable to carry the Reset and Abort signals and the LED lines to a control panel located apart from the MVME2603/2604. Maximum cable length is 15 feet.

Table 4-1 in Chapter 4, *Connector Pin Assignments* lists the pin numbers and signal mnemonics for J1.

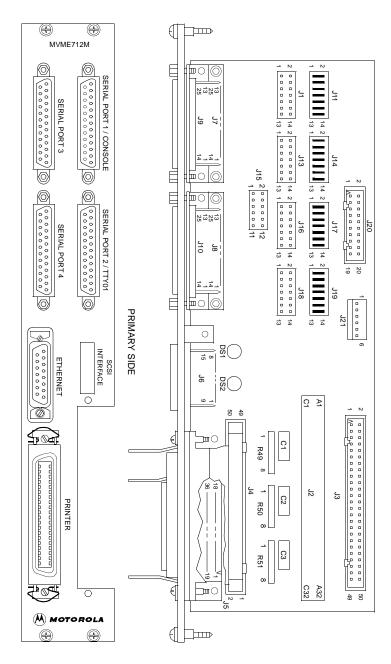

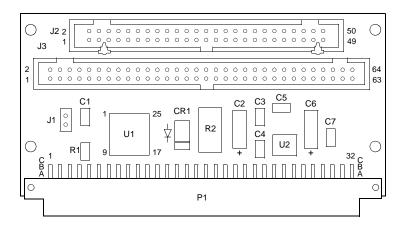

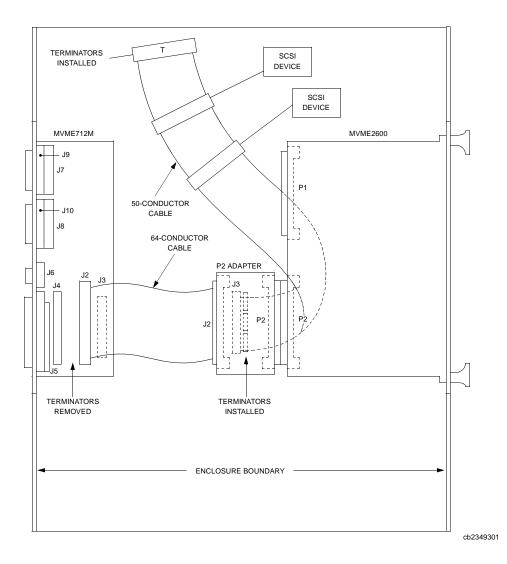

# **MVME712M Transition Module Preparation**

The MVME712M transition module (Figure 1-3) and P2 adapter board are used in conjunction with the MVME2603/2604 base board.

The features of the MVME712M include:

- □ A parallel printer port

- □ An Ethernet interface supporting AUI connections

- □ One synchronous/asynchronous, and three asynchronous only, EIA-232-D multiprotocol serial ports

- An SCSI interface (via P2 adapter) for connection to both internal and external devices

- Socket-mounted SCSI terminating resistors for end-of-cable or middle-of-cable configurations

- Provision for modem connection

- □ Green LED for SCSI terminator power; yellow LED for Ethernet transceiver power

The features of the P2 adapter board include:

A 50-pin connector for SCSI cabling to the MVME712M and/or to other SCSI devices

- Socket-mounted SCSI terminating resistors for end-of-cable or middle-of-cable configurations

- □ Fused SCSI terminator power developed from the +5VDC present at connector P2

- □ A 64-pin DIN connector to interface the EIA-232-D, parallel, SCSI, and Ethernet signals to the MVME712M

Figure 1-3. MVME712M Connector and Header Locations

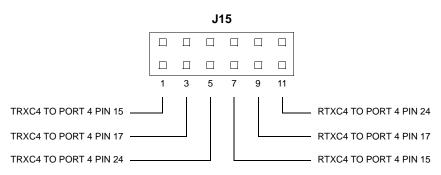

## Serial Ports 1-4 DCE/DTE Configuration

Serial ports 1 through 4 are configurable as modems (DCE) for connection to terminals, or as terminals (DTE) for connection to modems. The MVME712M is shipped with the serial ports configured for DTE operation. Serial port DCE/DTE configuration is accomplished by positioning jumpers on one of two headers per port. The following table lists the serial ports with their corresponding jumper headers.

| Serial Port | Board<br>Connector | Panel Connector        | Jumper<br>Header |

|-------------|--------------------|------------------------|------------------|

| Port 1      | J7                 | SERIAL PORT 1/ CONSOLE | J1/J11           |

| Port 2      | J8                 | SERIAL PORT 2/ TTY     | J16/J17          |

| Port 3      | J9                 | SERIAL PORT 3          | J13/J14          |

| Port 4      | J10                | SERIAL PORT 4          | J18/J19          |

Table 1-2.

MVME712M Port/Jumper Correspondence

The next six figures illustrate the MVME2603/2604 base board and MVME712M transition module with the interconnections and jumper settings for DCE/DTE configuration on each serial port.

# Serial Port 4 Clock Configuration

Port 4 can be configured via J15 (Figure 1-4)to use the TrxC4 and RtxC4 signal lines. Part of the configuration is done with headers J16, J17, and J20 on the MVME2603/2604 (Figure 1-9 and Figure 1-10).

1

11551.00 9609 (4-8)

11551.00 9609 (5-8)

#### Figure 1-7. MVME712M Serial Port 3 DCE Configuration

11551.00 9609 (6-8)

#### Figure 1-8. MVME712M Serial Port 3 DTE Configuration

Figure 1-9. MVME712M Serial Port 4 DCE Configuration

Figure 1-10. MVME712M Serial Port 4 DTE Configuration

### **P2 Adapter Preparation**

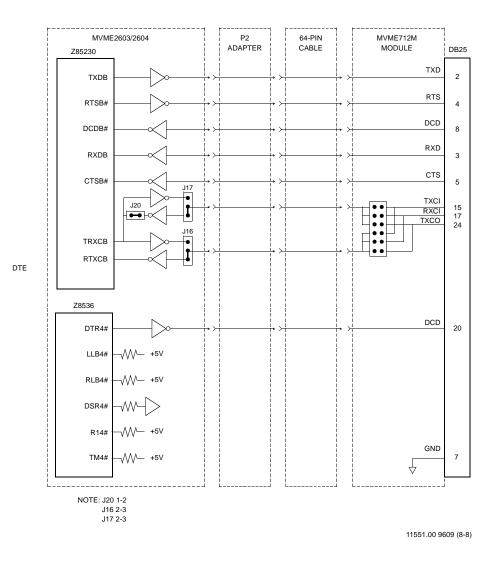

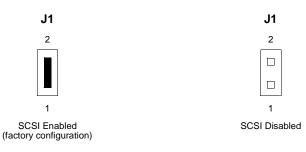

Preparation of the P2 adapter for the MVME712M consists of removing or installing the SCSI terminating resistors. Figure 1-11 illustrates the location of the resistors, fuse, and connectors.

For further information on the preparation of the transition module and the P2 adapter, refer to the user's manual for the MVME712M (listed in Appendix D, *Related Documentation*) as necessary.

Figure 1-11. MVME712M P2 Adapter Component Placement

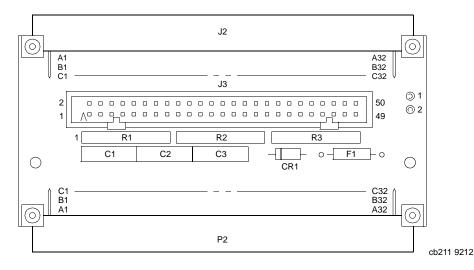

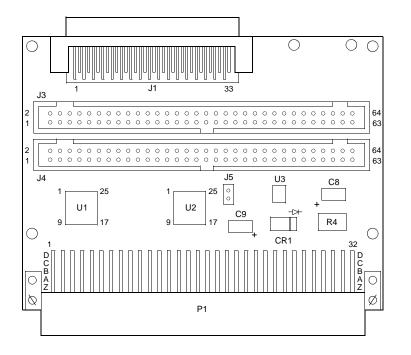

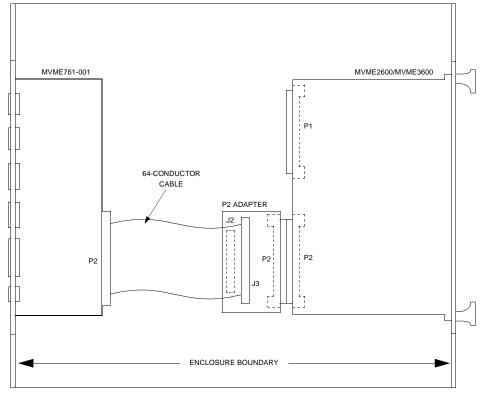

# **MVME761 Transition Module Preparation**

The MVME761 transition module (Figure 1-12) and P2 adapter board are used in conjunction with the MVME2603/2604 base board.

The features of the MVME761 include:

- □ A parallel printer port (IEEE 1284-I compliant)

- □ An Ethernet interface supporting 10BaseT/100BaseTX connections

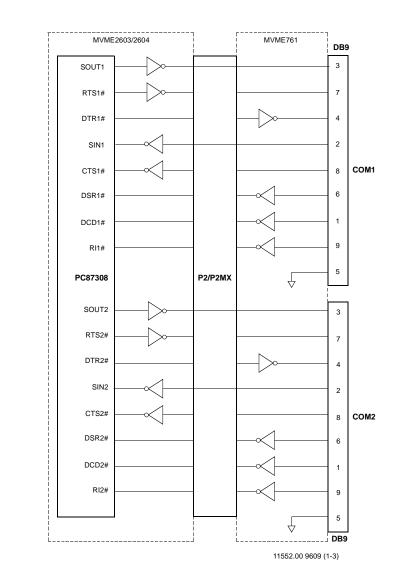

- Two EIA-232-D asynchronous serial ports (identified as COM1 and COM2 on the front panel)

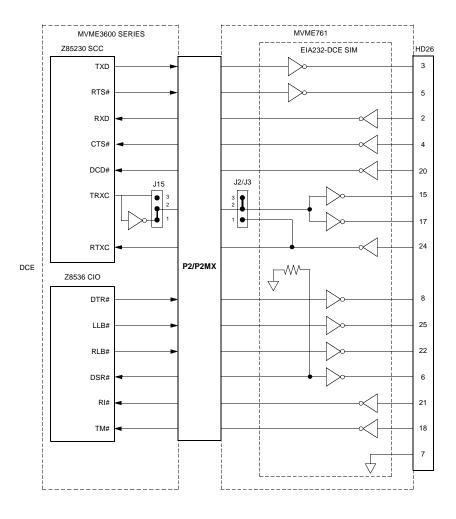

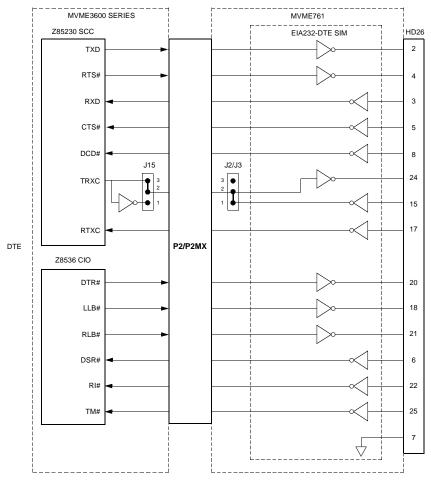

- Two synchronous serial ports (SERIAL 3 and SERIAL 4 on the front panel), configurable for EIA-232-D, EIA-530, V.35, or X.21 protocols

- Two 60-pin Serial Interface Module (SIM) connectors, used on configuring serial ports 3 and 4

The features of the P2 adapter board for the MVME761 include:

- □ A 50-pin connector for SCSI cabling to SCSI devices

- □ Jumper-selectable SCSI terminating resistors

- Fused SCSI terminator power developed from the +5V DC present at connector P2

- □ A 64-pin 3M connector to the MVME761

1-26

#### Serial Ports 1 and 2

On MVME761-compatible models of the MVME2603/2604 base board, the asynchronous serial ports (Serial Ports 1 and 2) are configured permanently as data circuit-terminating equipment (DCE). The port configuration is illustrated in Figure 1-13 on page 1-29.

### **Configuration of Serial Ports 3 and 4**

The synchronous serial ports, Serial Port 3 and Serial Port 4, are configurable through a combination of serial interface module (SIM) selection and jumper settings. The following table lists the SIM connectors and jumper headers corresponding to each of the synchronous serial ports.

| Synchronous<br>Port | Board<br>Connector | SIM<br>Connector | Jumper<br>Header |

|---------------------|--------------------|------------------|------------------|

| Port 3              | J7                 | J1               | J2               |

| Port 4              | J8                 | J12              | J3               |

Port 3 is routed to board connector J7. Port 4 is available at board connector J8. Eight serial interface modules are available:

- □ EIA-232-D (DCE and DTE)

- □ EIA-530 (DCE and DTE)

- □ V.35 (DCE and DTE)

- □ X.21 (DCE and DTE)

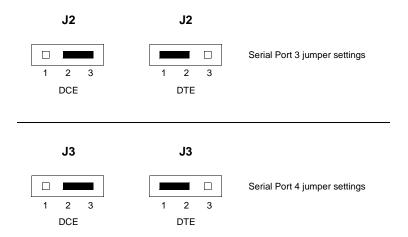

You can configure Serial Ports 3 and 4 for any of the above serial protocols by installing the appropriate serial interface module and setting the corresponding jumper. SIMs can be ordered separately as required. Headers J2 and J3 are used to configure Serial Port 3 and Serial Port 4, respectively, in tandem with SIM selection. With the jumper in position 1-2, the port is configured as a DTE. With the jumper in position 2-3, the port is configured as a DCE. *The jumper setting of the port should match the configuration of the corresponding SIM module*.

When installing the SIM modules, note that the headers are keyed for proper orientation.

For further information on the preparation of the transition module, refer to the user's manual for the MVME761 (listed in Appendix D, *Related Documentation*) as necessary.

The next three figures illustrate the MVME2603/2604 base board and MVME761 transition module with the interconnections and jumper settings for DCE/DTE configuration on each serial port.

DCE

11552.00 9802 (2-5)

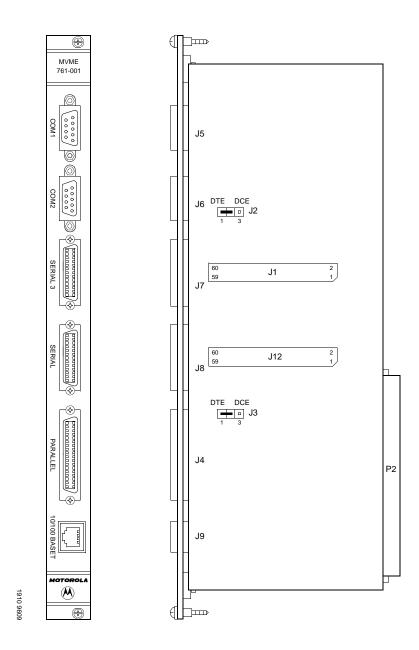

#### Figure 1-14. MVME761 Serial Ports 3 and 4 DCE Configuration

11552.00 9802 (4-5)

#### Figure 1-15. MVME761 Serial Ports 3 and 4 DTE Configuration

## P2 Adapter Preparation (Three-Row)

The P2 adapter for the MVME761 transition module routes the synchronous and asynchronous serial, parallel, and Ethernet signals to the MVME761. The P2 adapter also has a 50-pin female connector (J2) that carries 8-bit SCSI signals from the MVME2603/2604. To run SCSI devices, you may install an additional transition module that is equipped with a SCSI port, such as the MVME712B.

Preparation of the P2 adapter for the MVME761 consists of installing a jumper on header J1 to enable the SCSI terminating resistors if necessary. Figure 1-16 illustrates the location of the jumper header, resistors, fuse, and connectors.

For further information on the preparation of the transition module and the P2 adapter, refer to the user's manual for the MVME761 (listed in Appendix D, *Related Documentation*) as necessary.

1933 9610

#### Figure 1-16. MVME761 P2 Adapter (Three-Row) Component Placement

## P2 Adapter Preparation (Five-Row)

The MVME761 transition module uses a five-row P2 adapter to transfer the synchronous and asynchronous serial, parallel, and Ethernet signals to and from the MVME2600 series VME module. The P2 adapter has a 68-pin female connector (J1) that carries 16-bit SCSI signals from the MVME2600. (To run SCSI devices, you may install an optional front panel extension, MVME761EXT, next to the MVME761. The panel extension supplies both 8- and 16-bit SCSI.) The P2 adapter for the MVME761 also supports PMC I/O via connectors J3 and J4.

Preparation of the P2 adapter for the MVME761 consists of installing a jumper on header J5 to enable the SCSI terminating resistors if necessary. Figure 1-17 illustrates the location of the jumper header and connectors.

For further information on the preparation of the transition module and the P2 adapter, refer to the user's manual for the MVME761 (listed in Appendix D, *Related Documentation*) as necessary.

Figure 1-17. MVME761 P2 Adapter (Five-Row) Component Placement

1

1999 9701

# **Hardware Installation**

The following sections discuss the placement of mezzanine cards on the MVME2603/2604 base board, the installation of the complete MVME2603/2604 VME module assembly and transition module into a VME chassis, and the system considerations relevant to the installation. Before installing the MVME2603/2604, ensure that the serial ports and all header jumpers are configured as desired.

In most cases, the mezzanine cards—the RAM200 ECC DRAM module, the optional PCI mezzanine (if applicable), and the optional carrier board for additional PCI expansion (if applicable)—are already in place on the MVME2603/2604. The user-configurable jumpers are accessible with the mezzanines installed.

Should it be necessary to install mezzanines on the base board, refer to the following sections for a brief description of the installation procedure.

Wrist Strap

Motorola strongly recommends that you use an antistatic wrist strap and a conductive foam pad when installing or upgrading a system. Electronic components, such as disk drives, computer boards, and memory modules, can be extremely sensitive to electrostatic discharge (ESD). After removing the component from its protective wrapper or from the system, place the component flat on a grounded, static-free surface (and, in the case of a board, component side up). Do not slide the component over any surface.

If an ESD station is not available, you can avoid damage resulting from ESD by wearing an antistatic wrist strap (available at electronics stores) that is attached to an active electrical ground. Note that a system chassis may not be grounded if it is unplugged.

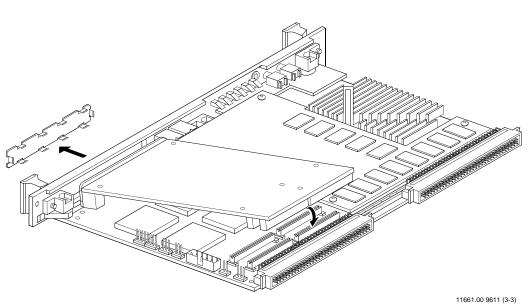

### **RAM200 Memory Mezzanine Installation**

The RAM200 DRAM mezzanine mounts on top of the MVME2603/2604 base board. To upgrade or install a RAM200 mezzanine, refer to Figure 1-18 and proceed as follows:

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

- Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system. Remove chassis or system cover(s) as necessary for access to the VME modules.

Inserting or removing modules with power applied may result in damage to module components.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

3. Carefully remove the MVME2603/2604 from its VMEbus card slot and lay it flat, with connectors P1 and P2 facing you.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits.

Place the RAM200 mezzanine module on top of the base board. Connector J9 on the underside of the RAM200 should connect smoothly with the corresponding connector J7 on the MVME2603/2604.

11661.00 9611 (2-3)

#### Figure 1-18. RAM200 Placement on MVME2603/2604

- 5. Insert the four short Phillips screws through the holes at the corners of the RAM200, into the standoffs on the MVME2603/2604. Tighten the screws.

- 6. Reinstall the MVME2603/2604 assembly in its proper card slot. Be sure the module is well seated in the backplane connectors. Do not damage or bend connector pins.

- 7. Replace the chassis or system cover(s), reconnect the system to the AC or DC power source, and turn the equipment power on.

#### **PMC Module Installation**

PCI mezzanine card (PMC) modules mount beside the RAM200 mezzanine on top of the MVME2603/2604 base board. To install a PMC module, refer to Figure 1-19 and proceed as follows:

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

- Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system. Remove chassis or system cover(s) as necessary for access to the VME modules.

Inserting or removing modules with power applied may result in damage to module components.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

3. Carefully remove the MVME2603/2604 from its VMEbus card slot and lay it flat, with connectors P1 and P2 facing you.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits.

4. Remove the PCI filler from the front panel.

#### Figure 1-19. PMC Module Placement on MVME2603/2604

- 5. Slide the edge connector of the PMC module into the front panel opening from behind and place the PMC module on top of the base board. The four connectors on the underside of the PMC module should then connect smoothly with the corresponding connectors (J11/12/13/14) on the MVME2603/2604.

- Insert the two short Phillips screws through the holes at the forward corners of the PMC module, into the standoffs on the MVME2603/2604. Tighten the screws.

- 7. Reinstall the MVME2603/2604 assembly in its proper card slot. Be sure the module is well seated in the backplane connectors. Do not damage or bend connector pins.

- 8. Replace the chassis or system cover(s), reconnect the system to the AC or DC power source, and turn the equipment power on.

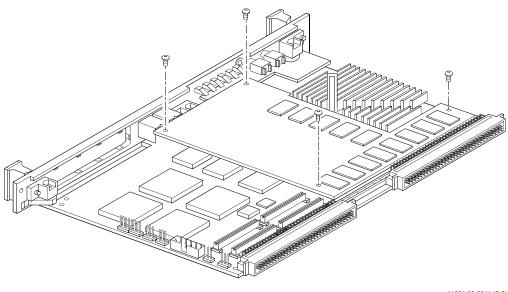

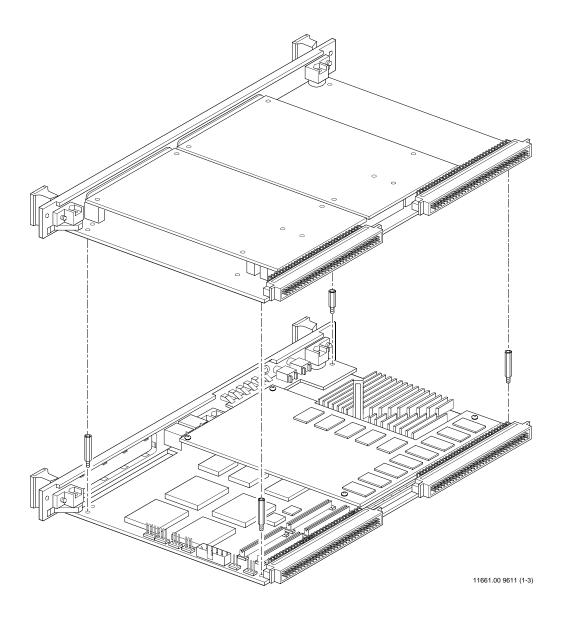

## **PMC Carrier Board Installation**

PCI mezzanine card (PMC) carrier boards mount above the RAM200 mezzanine and (if installed) PMC module on the MVME2603/2604 base board. To install a PMC carrier board for additional PCI expansion, refer to Figure 1-20 and proceed as follows:

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

- Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system. Remove chassis or system cover(s) as necessary for access to the VME modules.

Inserting or removing modules with power applied may result in damage to module components.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

3. Carefully remove the MVME2603/2604 from its VMEbus card slot and lay it flat, with connectors P1 and P2 facing you.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits.

4. If PMC modules are to be installed on the carrier board, install the modules at this point.

#### Figure 1-20. PMC Carrier Board Placement on MVME2603/2604

5. Remove the LED module screw located at the upper front corner of the base board. Install a short (0.394 inch) standoff in its place.

1

- 6. At the other three corners of the base board, install long (0.737 inch) standoffs.

- 7. Place the PMC carrier board on top of the base board. The connector on the underside of the carrier board should connect smoothly with the corresponding connector J5 (located between P1 and P2) on the MVME2603/2604.

- Insert the four short Phillips screws through the holes at the corners of the carrier board, into the standoffs on the MVME2603/2604. Tighten the screws.

- 9. Reinstall the MVME2603/2604 assembly in its proper card slot. Be sure the module is well seated in the backplane connectors. Do not damage or bend connector pins.

- 10. Replace the chassis or system cover(s), reconnect the system to the AC or DC power source, and turn the equipment power on.

#### MVME2603/2604 VME Module Installation

With mezzanine board(s) installed and headers properly configured, proceed as follows to install the MVME2603/2604 in the VME chassis:

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

- Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system. Remove chassis or system cover(s) as necessary for access to the VME modules.

Inserting or removing modules with power applied may result in damage to module components.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

- 3. Remove the filler panel from the card slot where you are going to install the MVME2603/2604.

- If you intend to use the MVME2603/2604 as system controller, it must occupy the left-most card slot (Slot 1). The system controller must be in Slot 1 to correctly initiate the bus-grant daisy-chain and to ensure proper operation of the IACK daisychain driver.

- If you do not intend to use the MVME2603/2604 as system controller, it can occupy any unused double-height card slot.

- 4. Slide the MVME2603/2604 into the selected card slot. Be sure the module is well seated in the P1 and P2 connectors on the backplane. Do not damage or bend connector pins.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits

- 5. Secure the MVME2603/2604 in the chassis with the screws provided, making good contact with the transverse mounting rails to minimize RF emissions.

- 6. On the chassis backplane, remove the INTERRUPT ACKNOWLEDGE (IACK) and BUS GRANT (BG) jumpers from the header for the card slot occupied by the MVME2603/2604.

- **Note** Some VME backplanes (for example, those used in Motorola "Modular Chassis" systems) have an auto-jumpering feature for automatic propagation of the IACK and BG signals. Step 6 does not apply to such backplane designs.

- 7. If necessary, install an MVME712M or MVME761 transition module and cable it to the MVME2603/2604 as described in the following sections of this document.

- 8. Replace the chassis or system cover(s), cable peripherals to the panel connectors as appropriate, reconnect the system to the AC or DC power source, and turn the equipment power on.

#### **MVME712M Transition Module Installation**

This section applies to MVME712M-compatible models of the MVME2603/2604 VME module. With the MVME2603/2604 installed, refer to Figure 1-21 and proceed as follows to install an MVME712M transition module:

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

- 2. Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system. Remove chassis or system cover(s) as necessary for access to the VME modules.

The MVME2600, MVME712-compatible models will be damaged if mistakenly connected to the MVME761 transition modules instead of the correct MVME712 family of boards.

**Note** In models of the MVME2603/2604 that are configured for MVME712M I/O mode, the pin assignments of VMEbus connector P2 are fully compatible with other transition modules of the MVME712 series.

Inserting or removing modules with power applied may result in damage to module components.