## IBM

# IBM PowerPC 750GX and 750GL RISC Microprocessor

User's Manual

Version 1.2

© Copyright International Business Machines Corporation 2004, 2006

All Rights Reserved

Printed in the United States of America March 2006.

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both:

IBM POWER PowerPC 750

IBM Logo PowerPC PowerPC Architecture

PowerPC Logo

IEEE is a registered trademark in the United States, owned by the Institute of Electrical and Electronics Engineers.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Division 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351

The IBM home page can be found at **ibm.com**

The IBM Microelectronics Division home page can be found at ibm.com/chips

gx\_title.fm.(1.2) March 27, 2006

| List of Figures                                             | 13   |

|-------------------------------------------------------------|------|

| List of Tables                                              | 15   |

| About This Manual                                           | 19   |

| Who Should Read This Manual                                 | 19   |

| Related Publications                                        | 19   |

| Conventions Used in This Manual                             | . 20 |

| Using This Manual with the Programming Environments Manual  | . 22 |

| 1. PowerPC 750GX Overview                                   | 23   |

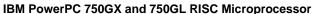

| 1.1 750GX Microprocessor Overview                           | . 23 |

| 1.2 750GX Microprocessor Features                           | . 25 |

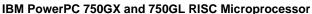

| 1.2.1 Instruction Flow                                      |      |

| 1.2.1.1 Instruction Queue and Dispatch Unit                 | 29   |

| 1.2.1.2 Branch Processing Unit (BPU)                        |      |

| 1.2.1.3 Completion Unit                                     |      |

| 1.2.2 Independent Execution Units                           | 31   |

| 1.2.2.1 Integer Units (IUs)                                 | . 31 |

| 1.2.2.2 Floating-Point Unit (FPU)                           | . 31 |

| 1.2.2.3 Load/Store Unit (LSU)                               |      |

| 1.2.2.4 System Register Unit (SRU)                          |      |

| 1.2.3 Memory Management Units (MMUs)                        |      |

| 1.2.4 On-Chip Level 1 Instruction and Data Caches           |      |

| 1.2.5 On-Chip Level 2 Cache Implementation                  |      |

| 1.2.6 System Interface/Bus Interface Unit (BIU)             |      |

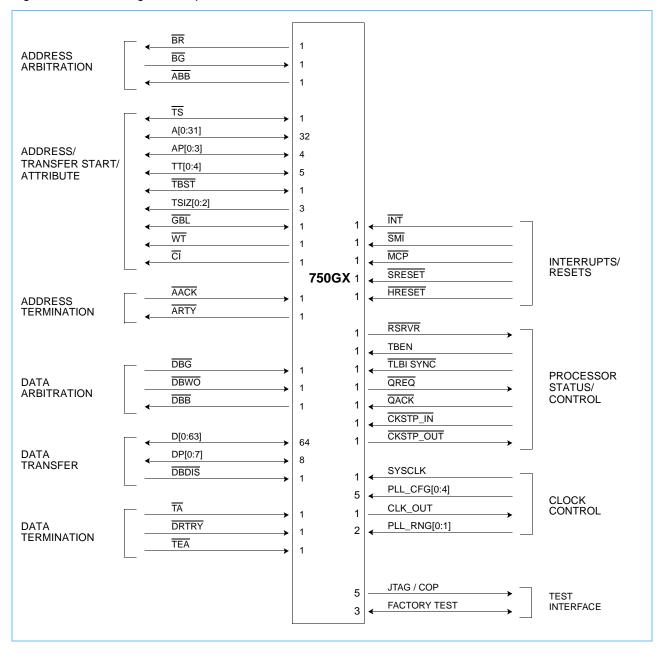

| 1.2.7 Signals                                               |      |

| 1.2.8 Signal Configuration                                  |      |

| 1.2.9 Clocking                                              |      |

| 1.3 750GX Microprocessor Implementation                     |      |

| 1.4 PowerPC Registers and Programming Model                 | . 42 |

| 1.5 Instruction Set                                         |      |

| 1.5.1 PowerPC Instruction Set                               |      |

| 1.5.2 750GX Microprocessor Instruction Set                  | . 47 |

| 1.6 On-Chip Cache Implementation                            | . 47 |

| 1.6.1 PowerPC Cache Model                                   | . 47 |

| 1.6.2 750GX Microprocessor Cache Implementation             | . 47 |

| 1.7 Exception Model                                         | . 48 |

| 1.7.1 PowerPC Exception Model                               | . 48 |

| 1.7.2 750GX Microprocessor Exception Implementation         | . 49 |

| 1.8 Memory Management                                       | 51   |

| 1.8.1 PowerPC Memory-Management Model                       | . 51 |

| 1.8.2 750GX Microprocessor Memory-Management Implementation | . 52 |

| 1.9 Instruction Timing                                      | . 52 |

| 1.10 Power Management                                       |      |

| 1.11 Thermal Management                                     |      |

| 1.12 Performance Monitor                                    |      |

|                                                             |      |

| ۷. ا | Programming Model                                           | . 5/  |

|------|-------------------------------------------------------------|-------|

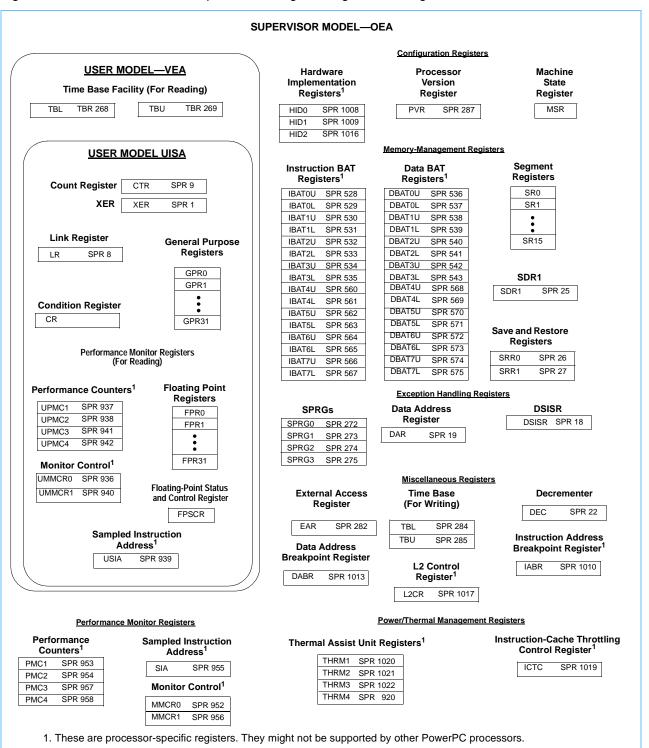

|      | 2.1 PowerPC 750GX Processor Register Set                    | 57    |

|      | 2.1.1 Register Set                                          |       |

|      | 2.1.2 PowerPC 750GX-Specific Registers                      | 64    |

|      | 2.1.2.1 Instruction Address Breakpoint Register (IABR)      | 64    |

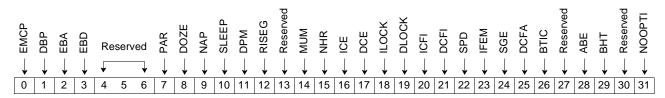

|      | 2.1.2.2 Hardware-Implementation-Dependent Register 0 (HID0) | 65    |

|      | 2.1.2.3 Hardware-Implementation-Dependent Register 1 (HID1) | 70    |

|      | 2.1.2.4 Hardware-Implementation-Dependent Register 2 (HID2) | 71    |

|      | 2.1.2.5 Performance-Monitor Registers                       | 72    |

|      | 2.1.3 Instruction Cache Throttling Control Register (ICTC)  | 77    |

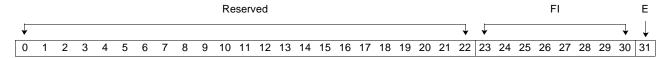

|      | 2.1.4 Thermal-Management Registers (THRMn)                  | 78    |

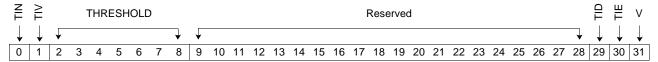

|      | 2.1.4.1 Thermal-Management Registers 1–2 (THRM1–THRM2)      | 78    |

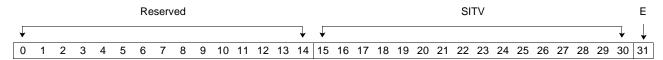

|      | 2.1.4.2 Thermal-Management Register 3 (THRM3)               | 79    |

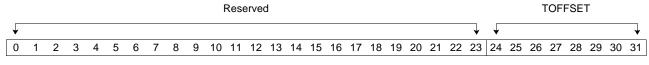

|      | 2.1.4.3 Thermal-Management Register 4 (THRM4)               | 80    |

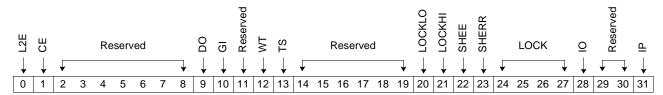

|      | 2.1.5 L2 Cache Control Register (L2CR)                      | 81    |

|      | 2.2 Operand Conventions                                     | 82    |

|      | 2.2.1 Data Organization in Memory and Data Transfers        |       |

|      | 2.2.2 Alignment and Misaligned Accesses                     | 82    |

|      | 2.2.3 Floating-Point Operand and Execution Models—UISA      | 83    |

|      | 2.2.3.1 Denormalized Number Support                         | 83    |

|      | 2.2.3.2 Non-IEEE Mode (Nondenormalized Mode)                | 83    |

|      | 2.2.3.3 Time-Critical Floating-Point Operation              |       |

|      | 2.2.3.4 Floating-Point Storage Access Alignment             | 84    |

|      | 2.2.3.5 Optional Floating-Point Graphics Instructions       | 84    |

|      | 2.3 Instruction Set Summary                                 | 86    |

|      | 2.3.1 Classes of Instructions                               |       |

|      | 2.3.1.1 Definition of Boundedly Undefined                   |       |

|      | 2.3.1.2 Defined Instruction Class                           | 87    |

|      | 2.3.1.3 Illegal Instruction Class                           | 88    |

|      | 2.3.1.4 Reserved Instruction Class                          | 89    |

|      | 2.3.2 Addressing Modes                                      | 89    |

|      | 2.3.2.1 Memory Addressing                                   | 89    |

|      | 2.3.2.2 Memory Operands                                     | 89    |

|      | 2.3.2.3 Effective Address Calculation                       | 90    |

|      | 2.3.2.4 Synchronization                                     | 90    |

|      | 2.3.3 Instruction Set Overview                              | 91    |

|      | 2.3.4 PowerPC UISA Instructions                             | 92    |

|      | 2.3.4.1 Integer Instructions                                | 92    |

|      | 2.3.4.2 Floating-Point Instructions                         | 95    |

|      | 2.3.4.3 Load-and-Store Instructions                         |       |

|      | 2.3.4.4 Branch and Flow-Control Instructions                |       |

|      | 2.3.4.5 System Linkage Instruction—UISA                     |       |

|      | 2.3.4.6 Processor Control Instructions—UISA                 |       |

|      | 2.3.4.7 Memory Synchronization Instructions—UISA            | . 113 |

|      | 2.3.5 PowerPC VEA Instructions                              |       |

|      | 2.3.5.1 Processor Control Instructions—VEA                  |       |

|      | 2.3.5.2 Memory Synchronization Instructions—VEA             | . 114 |

|      | 2.3.5.3 Memory Control Instructions—VEA                     |       |

|      | 2.3.5.4 Optional External Control Instructions              |       |

|      | 2.3.6 PowerPC OEA Instructions                              | . 118 |

|    | 2.3.6.1 System Linkage Instructions—OEA                                             | . 118 |

|----|-------------------------------------------------------------------------------------|-------|

|    | 2.3.6.2 Processor Control Instructions—OEA                                          |       |

|    | 2.3.6.3 Memory Control Instructions—OEA                                             |       |

|    | 2.3.7 Recommended Simplified Mnemonics                                              |       |

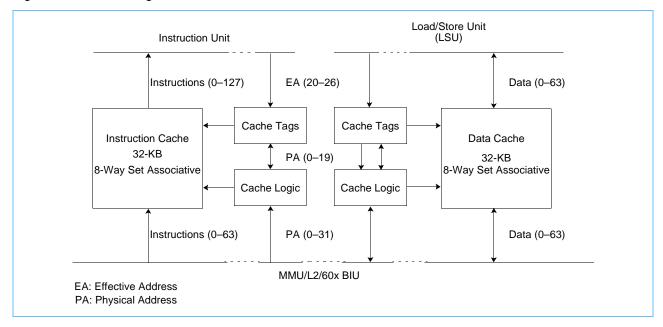

| 3. | Instruction-Cache and Data-Cache Operation                                          | 121   |

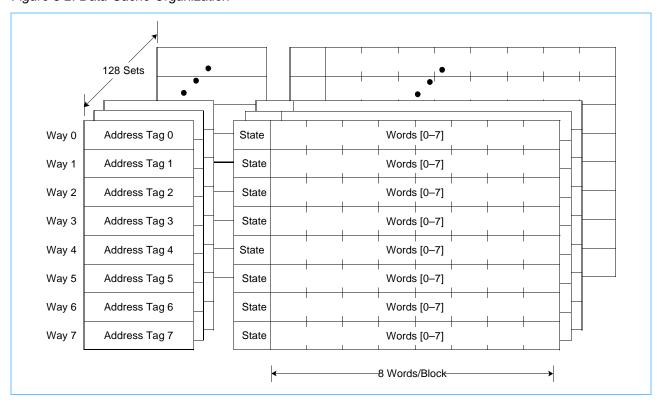

| •  | 3.1 Data-Cache Organization                                                         |       |

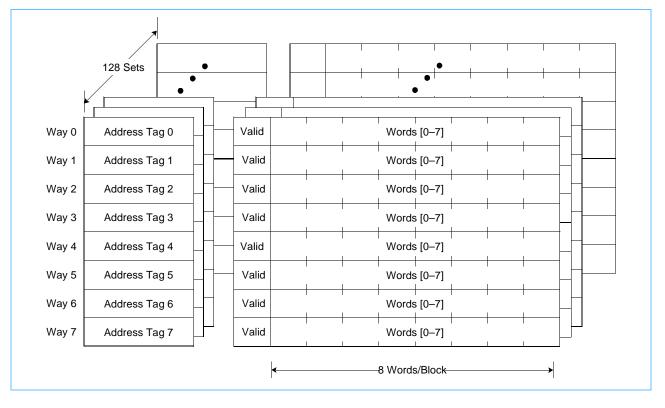

|    | 3.2 Instruction-Cache Organization                                                  |       |

|    | 3.3 Memory and Cache Coherency                                                      |       |

|    | 3.3.1 Memory/Cache Access Attributes (WIMG Bits)                                    |       |

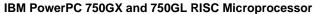

|    | 3.3.2 MEI Protocol                                                                  |       |

|    | 3.3.2.1 MEI Hardware Considerations                                                 |       |

|    | 3.3.3 Coherency Precautions in Single-Processor Systems                             |       |

|    | 3.3.4 Coherency Precautions in Multiprocessor Systems                               |       |

|    | 3.3.5 PowerPC 750GX-Initiated Load/Store Operations                                 |       |

|    | 3.3.5.1 Performed Loads and Stores                                                  |       |

|    | 3.3.5.2 Sequential Consistency of Memory Accesses                                   |       |

|    | 3.3.5.3 Atomic Memory References                                                    |       |

|    | 3.4 Cache Control                                                                   |       |

|    | 3.4.1 Cache-Control Parameters in HID0                                              |       |

|    | 3.4.1.1 Data-Cache Flash Invalidation                                               |       |

|    | 3.4.1.2 Enabling and Disabling the Data Cache                                       |       |

|    | 3.4.1.3 Locking the Data Cache                                                      |       |

|    | 3.4.1.4 Instruction-Cache Flash Invalidation                                        |       |

|    | 3.4.1.5 Enabling and Disabling the Instruction Cache                                |       |

|    | 3.4.1.6 Locking the Instruction Cache                                               |       |

|    | 3.4.2 Cache-Control Instructions                                                    |       |

|    | 3.4.2.1 Data Cache Block Touch (dcbt) and Data Cache Block Touch for Store (dcbtst) |       |

|    | 3.4.2.2 Data Cache Block Zero (dcbz)                                                |       |

|    | 3.4.2.3 Data Cache Block Store (dcbst)                                              | . 135 |

|    | 3.4.2.4 Data Cache Block Flush (dcbf)                                               | . 135 |

|    | 3.4.2.5 Data Cache Block Invalidate (dcbi)                                          | . 135 |

|    | 3.4.2.6 Instruction Cache Block Invalidate (icbi)                                   | . 136 |

|    | 3.5 Cache Operations                                                                | . 136 |

|    | 3.5.1 Cache-Block-Replacement/Castout Operations                                    |       |

|    | 3.5.2 Cache Flush Operations                                                        |       |

|    | 3.5.3 Data-Cache Block-Fill Operations                                              | . 139 |

|    | 3.5.4 Instruction-Cache Block-Fill Operations                                       | . 139 |

|    | 3.5.5 Data-Cache Block-Push Operations                                              | . 139 |

|    | 3.6 L1 Caches and 60x Bus Transactions                                              | . 139 |

|    | 3.6.1 Read Operations and the MEI Protocol                                          | . 140 |

|    | 3.6.2 Bus Operations Caused by Cache-Control Instructions                           | . 141 |

|    | 3.6.3 Snooping                                                                      | . 142 |

|    | 3.6.4 Snoop Response to 60x Bus Transactions                                        |       |

|    | 3.6.5 Transfer Attributes                                                           | . 145 |

|    | 3.7 MEI State Transactions                                                          | . 147 |

|    |                                                                                     |       |

| 4. | Exceptions                                                                          | 151   |

|    | 4.1 PowerPC 750GX Microprocessor Exceptions                                         | . 152 |

| 4.2   | 2 Exception Recognition and Priorities                               | 153 |

|-------|----------------------------------------------------------------------|-----|

| 4.3   | 3 Exception Processing                                               | 156 |

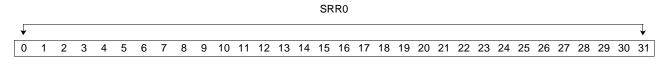

|       | 4.3.1 Machine Status Save/Restore Register 0 (SRR0)                  | 156 |

|       | 4.3.2 Machine Status Save/Restore Register 1 (SRR1)                  |     |

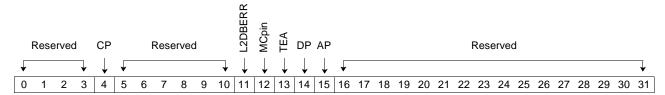

|       | 4.3.3 Machine State Register (MSR)                                   |     |

|       | 4.3.4 Enabling and Disabling Exceptions                              |     |

|       | 4.3.5 Steps for Exception Processing                                 |     |

|       | 4.3.6 Setting MSR[RI]                                                |     |

|       | 4.3.7 Returning from an Exception Handler                            |     |

| 4.4   | 4 Process Switching                                                  |     |

|       | 5 Exception Definitions                                              |     |

|       | 4.5.1 System Reset Exception (0x00100)                               |     |

|       | 4.5.1.1 Soft Reset                                                   |     |

|       | 4.5.1.2 Hard Reset                                                   |     |

|       | 4.5.2 Machine-Check Exception (0x00200)                              |     |

|       | 4.5.2.1 Machine-Check Exception Enabled (MSR[ME] = 1)                |     |

|       | 4.5.2.2 Checkstop State (MSR[ME] = 0)                                |     |

|       | 4.5.3 DSI Exception (0x00300)                                        |     |

|       | 4.5.4 ISI Exception (0x00400)                                        |     |

|       | 4.5.5 External Interrupt Exception (0x00500)                         |     |

|       | 4.5.6 Alignment Exception (0x00600)                                  |     |

|       | 4.5.7 Program Exception (0x00700)                                    |     |

|       | 4.5.8 Floating-Point Unavailable Exception (0x00800)                 |     |

|       | 4.5.9 Decrementer Exception (0x00900)                                |     |

|       | 4.5.10 System Call Exception (0x00C00)                               |     |

|       | 4.5.11 Trace Exception (0x00D00)                                     |     |

|       | 4.5.12 Floating-Point Assist Exception (0x00E00)                     |     |

|       | 4.5.13 Performance-Monitor Interrupt (0x00F00)                       |     |

|       | 4.5.14 Instruction Address Breakpoint Exception (0x01300)            |     |

|       | 4.5.15 System Management Interrupt (0x01400)                         |     |

|       | 4.5.16 Thermal-Management Interrupt Exception (0x01700)              |     |

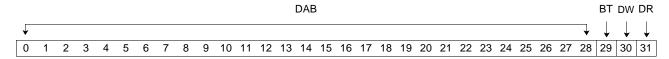

|       | 4.5.17 Data Address Breakpoint Exception                             |     |

|       | 4.5.17.1 Data Address Breakpoint Register (DABR)                     |     |

|       | 4.5.18 Soft Stops                                                    |     |

|       | 4.5.19 Exception Latencies                                           | 176 |

|       | 4.5.20 Summary of Front-End Exception Handling                       | 176 |

|       | 4.5.21 Timer Facilities                                              |     |

|       | 4.5.22 External Access Instructions                                  | 177 |

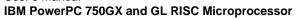

| 5. Me | emory Management                                                     | 179 |

|       | 1 MMU Overview                                                       |     |

| ٥.    | 5.1.1 Memory Addressing                                              |     |

|       | 5.1.2 MMU Organization                                               |     |

|       | 5.1.3 Address-Translation Mechanisms                                 |     |

|       | 5.1.4 Memory-Protection Facilities                                   |     |

|       | 5.1.5 Page History Information                                       |     |

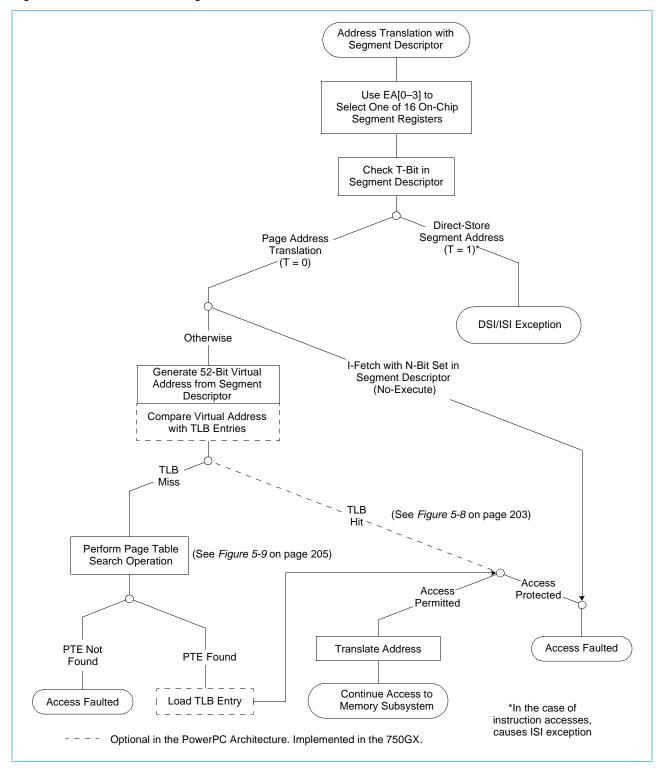

|       | 5.1.6 General Flow of MMU Address Translation                        |     |

|       | 5.1.6.1 Real-Addressing Mode and Block-Address-Translation Selection |     |

|       | 5.1.6.2 Page-Address-Translation Selection                           |     |

|       | 5.1.7 MMU Exceptions Summary                                         |     |

|       |                                                                      |     |

|    | 5.1.8 MMU Instructions and Register Summary                       | 194 |

|----|-------------------------------------------------------------------|-----|

|    | 5.2 Real-Addressing Mode                                          | 195 |

|    | 5.3 Block-Address Translation                                     | 196 |

|    | 5.4 Memory Segment Model                                          | 196 |

|    | 5.4.1 Page History Recording                                      |     |

|    | 5.4.1.1 Referenced Bit                                            | 197 |

|    | 5.4.1.2 Changed Bit                                               | 198 |

|    | 5.4.1.3 Scenarios for Referenced and Changed Bit Recording        | 198 |

|    | 5.4.2 Page Memory Protection                                      | 199 |

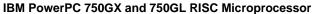

|    | 5.4.3 TLB Description                                             | 199 |

|    | 5.4.3.1 TLB Organization                                          |     |

|    | 5.4.3.2 TLB Invalidation                                          |     |

|    | 5.4.4 Page-Address-Translation Summary                            |     |

|    | 5.4.5 Page Table-Search Operation                                 |     |

|    | 5.4.6 Page Table Updates                                          |     |

|    | 5.4.7 Segment Register Updates                                    | 207 |

| _  | Instruction Timing                                                | 000 |

| о. | Instruction Timing                                                |     |

|    | 6.1 Terminology and Conventions                                   |     |

|    | 6.2 Instruction Timing Overview                                   |     |

|    | 6.3 Timing Considerations                                         |     |

|    | 6.3.1 General Instruction Flow                                    |     |

|    | 6.3.2 Instruction Fetch Timing                                    |     |

|    | 6.3.2.1 Cache Arbitration                                         |     |

|    | 6.3.2.2 Cache Hit                                                 |     |

|    | 6.3.2.3 Cache Miss                                                |     |

|    | 6.3.2.4 L2 Cache Access Timing Considerations                     |     |

|    | 6.3.2.5 Instruction Dispatch and Completion Considerations        |     |

|    | 6.3.2.6 Rename Register Operation                                 |     |

|    |                                                                   |     |

|    | 6.4 Execution-Unit Timings                                        |     |

|    | 6.4.1.1 Branch Folding                                            |     |

|    | 6.4.1.2 Branch Instructions and Completion                        |     |

|    | 6.4.1.3 Branch Prediction and Resolution                          |     |

|    | 6.4.2 Integer Unit Execution Timing                               |     |

|    | 6.4.3 Floating-Point Unit Execution Timing                        |     |

|    | 6.4.4 Effect of Floating-Point Exceptions on Performance          |     |

|    | 6.4.5 Load/Store Unit Execution Timing                            |     |

|    | 6.4.6 Effect of Operand Placement on Performance                  |     |

|    | 6.4.7 Integer Store Gathering                                     |     |

|    | 6.4.8 System Register Unit Execution Timing                       |     |

|    | 6.5 Memory Performance Considerations                             |     |

|    | 6.5.1 Caching and Memory Coherency                                |     |

|    | 6.5.2 Effect of TLB Miss                                          |     |

|    | 6.6 Instruction Scheduling Guidelines                             |     |

|    | 6.6.1 Branch, Dispatch, and Completion-Unit Resource Requirements |     |

|    | 6.6.1.1 Branch-Resolution Resource Requirements                   |     |

|    | 6.6.1.2 Dispatch-Unit Resource Requirements                       |     |

|    |                                                                   |     |

|    | 6.6.1.3 Completion-Unit Resource Requirements                                         | . 237 |

|----|---------------------------------------------------------------------------------------|-------|

|    | 6.7 Instruction Latency Summary                                                       | . 238 |

|    |                                                                                       |       |

| 7. | Signal Descriptions                                                                   | 249   |

|    | 7.1 Signal Configuration                                                              |       |

|    | 7.2 Signal Descriptions                                                               |       |

|    | 7.2.1 Address-Bus Arbitration Signals                                                 |       |

|    | 7.2.1.1 Bus Request (BR)—Output                                                       |       |

|    | 7.2.1.2 Bus Grant ( <del>BG</del> )—Input                                             |       |

|    | 7.2.1.3 Address Bus Busy (ABB)                                                        |       |

|    | 7.2.2 Address Transfer Start Signals                                                  |       |

|    | 7.2.2.1 Transfer Start (TS)                                                           |       |

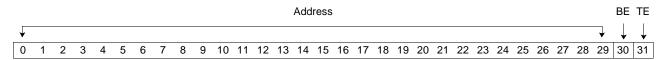

|    | 7.2.3 Address Transfer Signals                                                        | . 254 |

|    | 7.2.3.1 Address Bus (A[0-31])                                                         |       |

|    | 7.2.3.2 Address-Bus Parity (AP[0–3])                                                  |       |

|    | 7.2.4 Address Transfer Attribute Signals                                              |       |

|    | 7.2.4.1 Transfer Type (TT[0-4])                                                       | . 256 |

|    | 7.2.4.2 Transfer Size (TSIZ[0-2])—Output                                              | . 258 |

|    | 7.2.4.3 Transfer Burst (TBST)                                                         | . 259 |

|    | 7.2.4.4 Cache Inhibit (CI)—Output                                                     | . 260 |

|    | 7.2.4.5 Write-Through (WT)—Output                                                     |       |

|    | 7.2.4.6 Global (GBL)                                                                  |       |

|    | 7.2.5 Address Transfer Termination Signals                                            |       |

|    | 7.2.5.1 Address Acknowledge (AACK)—Input                                              |       |

|    | 7.2.5.2 Address Retry (ARTRY)                                                         |       |

|    | 7.2.6 Data-Bus Arbitration Signals                                                    |       |

|    | 7.2.6.1 Data-Bus Grant (DBG)—Input                                                    |       |

|    | 7.2.6.2 Data-Bus Write-Only (DBWO)                                                    |       |

|    | 7.2.6.3 Data Bus Busy (DBB)                                                           |       |

|    | 7.2.7 Data-Transfer Signals                                                           |       |

|    | 7.2.7.1 Data Bus (DH[0–31], DL[0–31])                                                 |       |

|    | 7.2.7.2 Data-Bus Parity (D <u>P[0–7])</u>                                             |       |

|    | 7.2.7.3 Data Bus Disable (DBDIS)—Input                                                |       |

|    | 7.2.8 Data-Transfer Termination Signals                                               |       |

|    | 7.2.8.1 Transfer Acknowledge (TA)—Input                                               |       |

|    | 7.2.8.2 Data Retry (DRTRY)—Input                                                      |       |

|    | 7.2.8.3 Transfer Error Acknowledge (TEA)—Input                                        |       |

|    | 7.2.9 System Status Signals                                                           |       |

|    | 7.2.9.1 Interrupt (INT)— Input                                                        |       |

|    | 7.2.9.2 System Management Interrupt (SMI)—Input                                       |       |

|    | 7.2.9.3 Machine-Check Interrupt (MCP)—Input                                           |       |

|    | 7.2.9.4 Checkstop Input (CKSTP_IN)—Input                                              |       |

|    | 7.2.9.5 Checkstop Output (CKSTP_OUT)—Output                                           |       |

|    | 7.2.10 Reset Signals                                                                  |       |

|    | 7.2.10.1 Hard Reset (HRESET)—Input                                                    |       |

|    | 7.2.10.2 Soft Reset (SRESET)—Input  7.2.11 Processor Status Signals                   |       |

|    | 7.2.11.1 Quiescent Request (QREQ)—Output                                              |       |

|    | 7.2.11.1 Quiescent Request (QREQ)—Output  7.2.11.2 Quiescent Acknowledge (QACK)—Input |       |

|    | 7.2.11.3 Reservation (RSRV)—Output                                                    |       |

|    | 1.2.11.0 Neservation (Notv)—Output                                                    | . 213 |

|    | 7.2.11.4 Time Base Enable (TBEN)—Input                |       |

|----|-------------------------------------------------------|-------|

|    | 7.2.11.5 TLB Invalidate Synchronize (TLBISYNC)—Input  | 274   |

|    | 7.2.12 Processor Mode Selection Signals               | 274   |

|    | 7.2.13 I/O Voltage Select Signals                     | 275   |

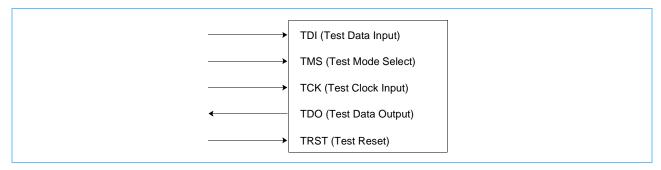

|    | 7.2.14 Test Interface Signals                         |       |

|    | 7.2.14.1 IEEE 1149.1a-1993 Interface Description      | 275   |

|    | 7.2.14.2 LSSD_MODE                                    |       |

|    | 7.2.14.3 L1_TSTCLK                                    |       |

|    | 7.2.14.4 L2_TSTCLK                                    |       |

|    | 7.2.14.5 BVSEL                                        |       |

|    | 7.2.15 Clock Signals                                  |       |

|    | 7.2.15.1 System Clock (SYSCLK)—Input                  |       |

|    | 7.2.15.2 Clock Out (CLK_OUT)—Output                   |       |

|    | 7.2.15.3 PLL Configuration (PLL_CFG[0:4])—Input       |       |

|    | 7.2.15.4 PLL Range (PLL_RNG[0:1])—Input               |       |

|    | 7.2.16 Power and Ground Signals                       | 278   |

| 0  | Bus Interface Operation                               | 270   |

| Ο. | 8.1 Bus Interface Overview                            |       |

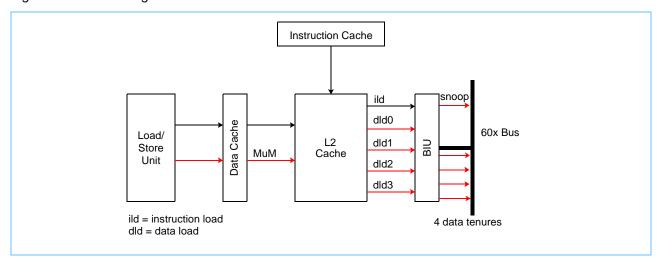

|    | 8.1.1 Operation of the Instruction and Data L1 Caches |       |

|    | 8.1.2 Operation of the Bus Interface                  |       |

|    | 8.1.3 Bus Signal Clocking                             |       |

|    | 8.1.4 Optional 32-Bit Data Bus Mode                   |       |

|    | 8.1.5 Direct-Store Accesses                           |       |

|    | 8.2 Memory-Access Protocol                            |       |

|    | 8.2.1 Arbitration Signals                             |       |

|    | 8.2.2 Miss-under-Miss                                 |       |

|    | 8.2.2.1 Miss-under-Miss and System Performance        |       |

|    | 8.2.2.2 Speculative Loads and Conditional Branches    |       |

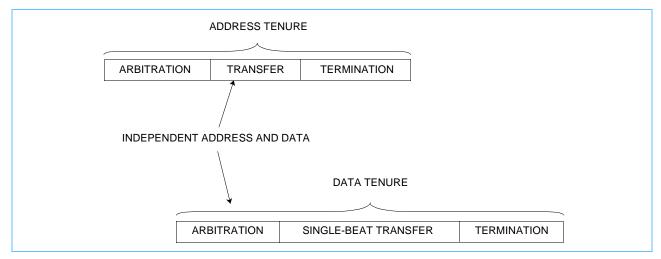

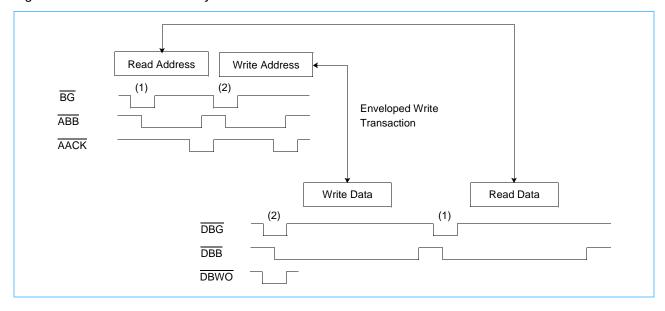

|    | 8.3 Address-Bus Tenure                                |       |

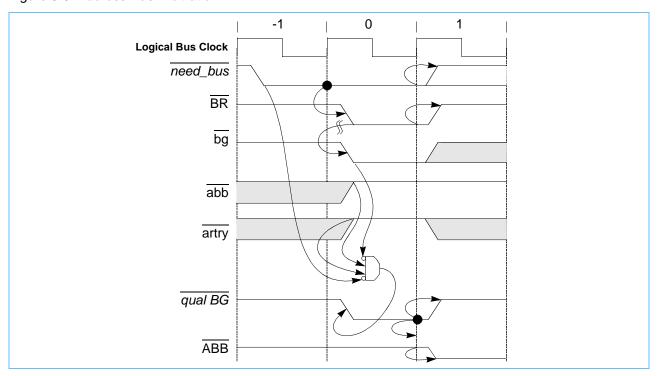

|    | 8.3.1 Address-Bus Arbitration                         |       |

|    | 8.3.2 Address Transfer                                |       |

|    | 8.3.2.1 Address-Bus Parity                            |       |

|    | 8.3.2.2 Address Transfer Attribute Signals            |       |

|    | 8.3.2.3 Burst Ordering During Data Transfers          |       |

|    | 8.3.2.4 Effect of Alignment in Data Transfers         |       |

|    | 8.3.2.5 Alignment of External Control Instructions    | 300   |

|    | 8.3.3 Address Transfer Termination                    | 300   |

|    | 8.4 Data-Bus Tenure                                   | 301   |

|    | 8.4.1 Data-Bus Arbitration                            | . 301 |

|    | 8.4.1.1 Using the DBB Signal                          | 302   |

|    | 8.4.2 Data-Bus Write-Only                             | . 303 |

|    | 8.4.3 Data Transfer                                   |       |

|    | 8.4.4 Data-Transfer Termination                       |       |

|    | 8.4.4.1 Normal Single-Beat Termination                |       |

|    | 8.4.4.2 Data-Transfer Termination Due to a Bus Error  |       |

|    | 8.4.5 Memory Coherency—MEI Protocol                   |       |

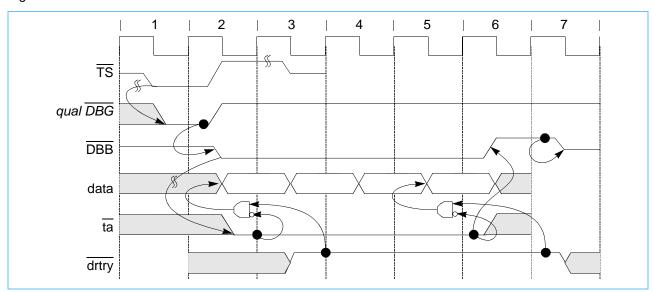

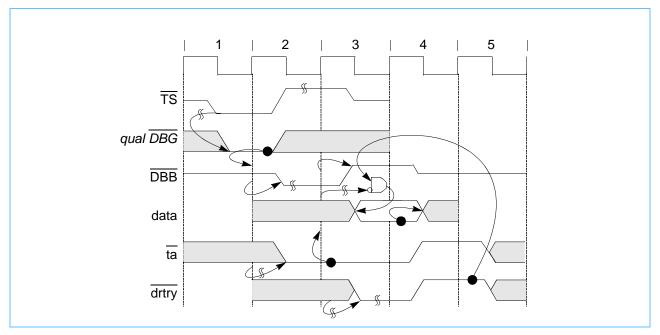

|    | 8.5 Timing Examples                                   | 309   |

|    | 8.6 Optional Bus Configuration                        | 316   |

|    | 8.6.1 32-Bit Data Bus Mode                            | 316   |

|    | 8.6.2 No-DRTRY Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 318                                                                       |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|    | 8.7 Processor State Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 319                                                                       |

|    | 8.7.1 Support for the Iwarx and stwcx. Instruction Pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |

|    | 8.7.2 TLBISYNC Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 319                                                                       |

|    | 8.8 IEEE 1149.1a-1993 Compliant Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 319                                                                       |

|    | 8.8.1 JTAG/COP Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 319                                                                       |

|    | 8.9 Using Data-Bus Write-Only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 320                                                                       |

| 9. | L2 Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 323                                                                       |

|    | 9.1 L2 Cache Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 323                                                                       |

|    | 9.2 L2 Cache Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 323                                                                       |

|    | 9.3 L2 Cache Control Register (L2CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 329                                                                       |

|    | 9.4 L2 Cache Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 329                                                                       |

|    | 9.5 L2 Cache Global Invalidation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 329                                                                       |

|    | 9.6 L2 Cache Used as On-Chip Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                           |

|    | 9.6.1 Locking the L2 Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |

|    | 9.6.1.1 Loading the Locked L2 Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                           |

|    | 9.6.1.2 Locked Cache Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |

|    | 9.7 Data-Only and Instruction-Only Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

|    | 9.8 L2 Cache Test Features and Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |

|    | 9.8.1 L2CR Support for L2 Cache Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |

|    | 9.8.2 L2 Cache Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |

|    | 9.9 L2 Cache Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 333                                                                       |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |

| 10 | ). Power and Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 335                                                                       |

| 10 | ). Power and Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |

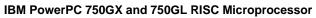

| 10 | 10.1 Dynamic Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 335                                                                       |

| 10 | 10.1 Dynamic Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 335<br>335                                                                |

| 10 | 10.1 Dynamic Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 335<br>335<br>337                                                         |

| 10 | 10.1 Dynamic Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |

| 10 | 10.1 Dynamic Power Management  10.2 Programmable Power Modes  10.2.1 Power Management Modes  10.2.1.1 Full On Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |

| 10 | 10.1 Dynamic Power Management 10.2 Programmable Power Modes 10.2.1 Power Management Modes 10.2.1.1 Full On Mode 10.2.1.2 Doze Mode 10.2.1.3 Nap Mode 10.2.1.4 Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

| 10 | 10.1 Dynamic Power Management  10.2 Programmable Power Modes  10.2.1 Power Management Modes  10.2.1.1 Full On Mode  10.2.1.2 Doze Mode  10.2.1.3 Nap Mode  10.2.1.4 Sleep Mode  10.2.1.5 Dynamic Power Reduction                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

| 10 | 10.1 Dynamic Power Management  10.2 Programmable Power Modes  10.2.1 Power Management Modes  10.2.1.1 Full On Mode  10.2.1.2 Doze Mode  10.2.1.3 Nap Mode  10.2.1.4 Sleep Mode  10.2.1.5 Dynamic Power Reduction  10.2.2 Power Management Software Considerations                                                                                                                                                                                                                                                                                                                                                    |                                                                           |

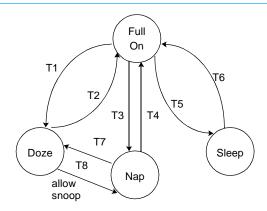

| 10 | 10.1 Dynamic Power Management  10.2 Programmable Power Modes  10.2.1 Power Management Modes  10.2.1.1 Full On Mode  10.2.1.2 Doze Mode  10.2.1.3 Nap Mode  10.2.1.4 Sleep Mode  10.2.1.5 Dynamic Power Reduction  10.2.2 Power Management Software Considerations  10.3 750GX Dual PLL Feature                                                                                                                                                                                                                                                                                                                       | 335<br>335<br>337<br>337<br>337<br>339<br>339<br>340                      |

| 10 | 10.1 Dynamic Power Management 10.2 Programmable Power Modes 10.2.1 Power Management Modes 10.2.1.1 Full On Mode 10.2.1.2 Doze Mode 10.2.1.3 Nap Mode 10.2.1.4 Sleep Mode 10.2.1.5 Dynamic Power Reduction 10.2.2 Power Management Software Considerations 10.3 750GX Dual PLL Feature 10.3.1 Overview                                                                                                                                                                                                                                                                                                                | 335<br>335<br>337<br>337<br>337<br>339<br>339<br>340<br>340               |

| 10 | 10.1 Dynamic Power Management 10.2 Programmable Power Modes 10.2.1 Power Management Modes 10.2.1.1 Full On Mode 10.2.1.2 Doze Mode 10.2.1.3 Nap Mode 10.2.1.4 Sleep Mode 10.2.1.5 Dynamic Power Reduction 10.2.2 Power Management Software Considerations 10.3 750GX Dual PLL Feature 10.3.1 Overview 10.3.2 Configuration Restriction on Frequency Transitions                                                                                                                                                                                                                                                      | 335<br>335<br>337<br>337<br>337<br>339<br>339<br>340<br>340               |

| 10 | 10.1 Dynamic Power Management 10.2 Programmable Power Modes 10.2.1 Power Management Modes 10.2.1.1 Full On Mode 10.2.1.2 Doze Mode 10.2.1.3 Nap Mode 10.2.1.4 Sleep Mode 10.2.1.5 Dynamic Power Reduction 10.2.2 Power Management Software Considerations 10.3 750GX Dual PLL Feature 10.3.1 Overview 10.3.2 Configuration Restriction on Frequency Transitions 10.3.3 Dual PLL Implementation                                                                                                                                                                                                                       | 335<br>335<br>337<br>337<br>337<br>339<br>340<br>340<br>341               |

| 10 | 10.1 Dynamic Power Management  10.2 Programmable Power Modes  10.2.1 Power Management Modes  10.2.1.1 Full On Mode  10.2.1.2 Doze Mode  10.2.1.3 Nap Mode  10.2.1.4 Sleep Mode  10.2.1.5 Dynamic Power Reduction  10.2.2 Power Management Software Considerations  10.3 750GX Dual PLL Feature  10.3.1 Overview  10.3.2 Configuration Restriction on Frequency Transitions  10.3 Dual PLL Implementation                                                                                                                                                                                                             | 335<br>335<br>337<br>337<br>337<br>339<br>340<br>340<br>341<br>341        |

| 10 | 10.1 Dynamic Power Management 10.2 Programmable Power Modes 10.2.1 Power Management Modes 10.2.1.1 Full On Mode 10.2.1.2 Doze Mode 10.2.1.3 Nap Mode 10.2.1.4 Sleep Mode 10.2.1.5 Dynamic Power Reduction 10.2.2 Power Management Software Considerations 10.3 750GX Dual PLL Feature 10.3.1 Overview 10.3.2 Configuration Restriction on Frequency Transitions 10.3.3 Dual PLL Implementation 10.4 Thermal Assist Unit 10.4.1 Thermal Assist Unit Overview                                                                                                                                                          | 335<br>335<br>337<br>337<br>337<br>339<br>340<br>340<br>341<br>342<br>343 |

| 10 | 10.1 Dynamic Power Management 10.2 Programmable Power Modes 10.2.1 Power Management Modes 10.2.1.1 Full On Mode 10.2.1.2 Doze Mode 10.2.1.3 Nap Mode 10.2.1.4 Sleep Mode 10.2.1.5 Dynamic Power Reduction 10.2.2 Power Management Software Considerations 10.3 750GX Dual PLL Feature 10.3.1 Overview 10.3.2 Configuration Restriction on Frequency Transitions 10.3 Dual PLL Implementation 10.4 Thermal Assist Unit 10.4.1 Thermal Assist Unit Overview 10.4.2 Thermal Assist Unit Operation                                                                                                                       | 335 335 337 337 337 339 340 340 341 342 343                               |

| 10 | 10.1 Dynamic Power Management 10.2 Programmable Power Modes 10.2.1 Power Management Modes 10.2.1.1 Full On Mode 10.2.1.2 Doze Mode 10.2.1.3 Nap Mode 10.2.1.4 Sleep Mode 10.2.1.5 Dynamic Power Reduction 10.2.2 Power Management Software Considerations 10.3 750GX Dual PLL Feature 10.3.1 Overview 10.3.2 Configuration Restriction on Frequency Transitions 10.3 Dual PLL Implementation 10.4 Thermal Assist Unit 10.4.1 Thermal Assist Unit Overview 10.4.2 Thermal Assist Unit Operation 10.4.2.1 TAU Single-Threshold Mode                                                                                    | 335 335 337 337 337 339 340 340 341 343 343                               |

| 10 | 10.1 Dynamic Power Management 10.2 Programmable Power Modes 10.2.1 Power Management Modes 10.2.1.1 Full On Mode 10.2.1.2 Doze Mode 10.2.1.3 Nap Mode 10.2.1.4 Sleep Mode 10.2.1.5 Dynamic Power Reduction 10.2.2 Power Management Software Considerations 10.3 750GX Dual PLL Feature 10.3.1 Overview 10.3.2 Configuration Restriction on Frequency Transitions 10.3 Dual PLL Implementation 10.4 Thermal Assist Unit 10.4.1 Thermal Assist Unit Overview 10.4.2 Thermal Assist Unit Operation 10.4.2.1 TAU Single-Threshold Mode 10.4.2.2 TAU Dual-Threshold Mode                                                   | 335 335 337 337 337 339 340 340 341 342 343 343 344 345                   |

| 10 | 10.1 Dynamic Power Management 10.2 Programmable Power Modes 10.2.1 Power Management Modes 10.2.1.1 Full On Mode 10.2.1.2 Doze Mode 10.2.1.3 Nap Mode 10.2.1.4 Sleep Mode 10.2.1.5 Dynamic Power Reduction 10.2.2 Power Management Software Considerations 10.3 750GX Dual PLL Feature 10.3.1 Overview 10.3.2 Configuration Restriction on Frequency Transitions 10.3 Dual PLL Implementation 10.4 Thermal Assist Unit 10.4.1 Thermal Assist Unit Overview 10.4.2 Thermal Assist Unit Operation 10.4.2.1 TAU Single-Threshold Mode                                                                                    | 335 335 337 337 337 339 340 340 341 342 343 344 345                       |

| 10 | 10.1 Dynamic Power Management 10.2 Programmable Power Modes 10.2.1 Power Management Modes 10.2.1.1 Full On Mode 10.2.1.2 Doze Mode 10.2.1.3 Nap Mode 10.2.1.4 Sleep Mode 10.2.1.5 Dynamic Power Reduction 10.2.2 Power Management Software Considerations 10.3 750GX Dual PLL Feature 10.3.1 Overview 10.3.2 Configuration Restriction on Frequency Transitions 10.3 Dual PLL Implementation 10.4 Thermal Assist Unit 10.4.1 Thermal Assist Unit Overview 10.4.2 Thermal Assist Unit Operation 10.4.2.1 TAU Single-Threshold Mode 10.4.2.2 TAU Dual-Threshold Mode 10.4.2.3 750GX Junction Temperature Determination | 335 335 337 337 337 339 340 340 341 342 343 344 344 345 346               |

| 11.1 Performance-Monitor Interrupt                                     | . 349 |

|------------------------------------------------------------------------|-------|

| 11.2 Special-Purpose Registers Used by Performance Monitor             | . 350 |

| 11.2.1 Performance-Monitor Registers                                   |       |

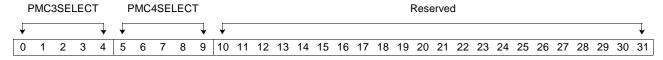

| 11.2.1.1 Monitor Mode Control Register 0 (MMCR0)                       |       |

| 11.2.1.2 User Monitor Mode Control Register 0 (UMMCR0)                 |       |

| 11.2.1.3 Monitor Mode Control Register 1 (MMCR1)                       |       |

| 11.2.1.4 User Monitor Mode Control Register 1 (UMMCR1)                 |       |

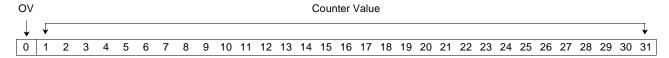

| 11.2.1.5 Performance-Monitor Counter Registers (PMCn)                  |       |

| 11.2.1.6 User Performance-Monitor Counter Registers (UPMC1–UPMC4)      |       |

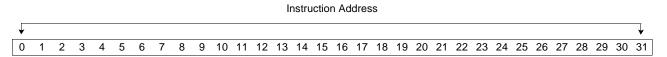

| 11.2.1.7 Sampled Instruction Address Register (SIA)                    |       |

| 11.2.1.8 User Sampled Instruction Address Register (USIA)              | . 355 |

| 11.3 Event Counting                                                    | . 355 |

| 11.4 Event Selection                                                   | . 356 |

| 11.5 Notes                                                             | . 356 |

| 11.6 Debug Support                                                     | . 357 |

| 11.6.1 Overview                                                        | . 357 |

| 11.6.2 Data-Address Breakpoint                                         | . 357 |

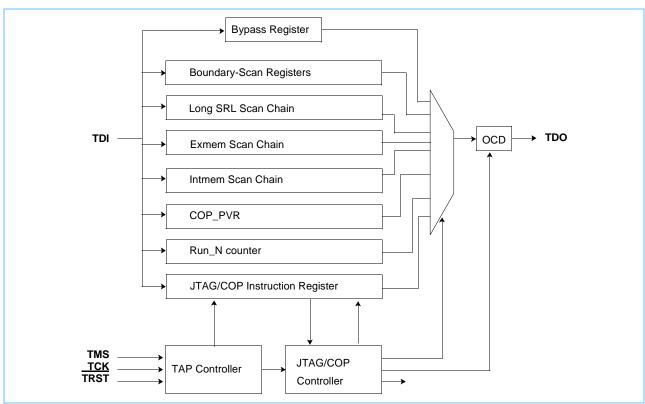

| 11.7 JTAG/COP Functions                                                | . 357 |

| 11.7.1 Introduction                                                    | . 357 |

| 11.7.2 Processor Resources Available through JTAG/COP Serial Interface | . 357 |

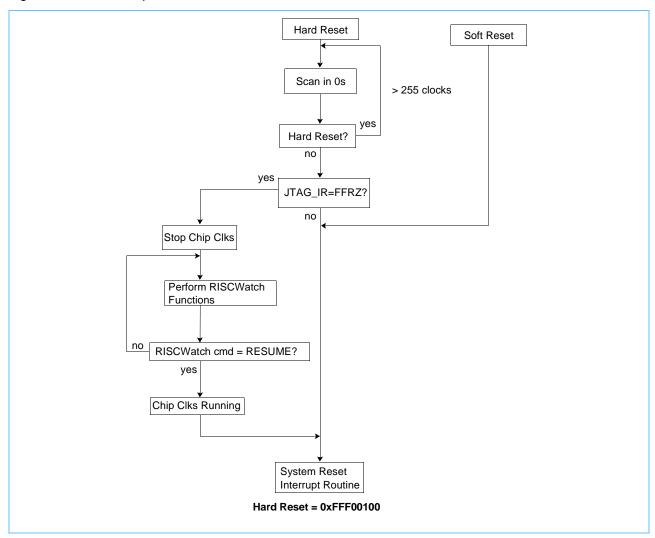

| 11.8 Resets                                                            | . 359 |

| 11.8.1 Hard Reset                                                      | . 359 |

| 11.8.2 Soft Reset                                                      |       |

| 11.8.3 Reset Sequence                                                  | . 360 |

| 11.9 Checkstops                                                        | . 361 |

| 11.9.1 Checkstop Sources                                               | . 361 |

| 11.9.2 Checkstop Control Bits                                          |       |

| 11.9.3 Open-Collector-Driver States during Checkstop                   |       |

| 11.9.4 Vacancy Slot Application                                        | . 362 |

| 11.10 750GX Parity                                                     | . 363 |

| 11.10.1 Parity Control and Status                                      |       |

| 11.10.2 Enabling Parity Error Detection                                |       |

| 11.10.3 Parity Errors                                                  | . 364 |

| Acronyms and Abbreviations                                             | 365   |

| ndex                                                                   | 369   |

| Navialan I an                                                          | 277   |

| Revision Log                                                           | 3//   |

### **List of Figures**

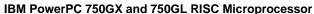

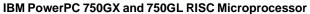

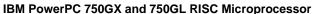

| Figure 1-1.  | 750GX Microprocessor Block Diagram                                   | 25  |

|--------------|----------------------------------------------------------------------|-----|

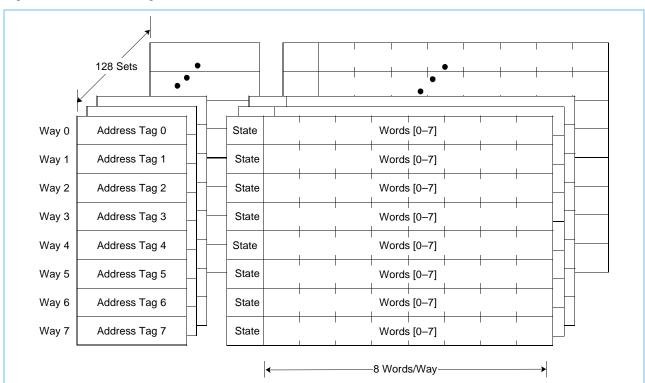

| Figure 1-2.  | L1 Cache Organization                                                | 34  |

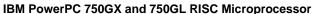

| Figure 1-3.  | System Interface                                                     | 37  |

| Figure 1-4.  | 750GX Microprocessor Signal Groups                                   | 39  |

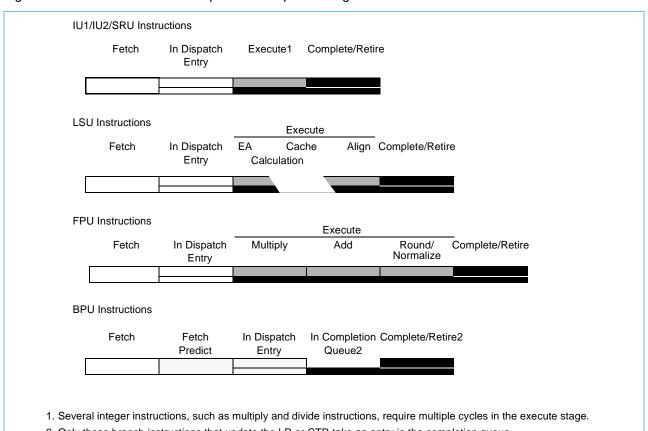

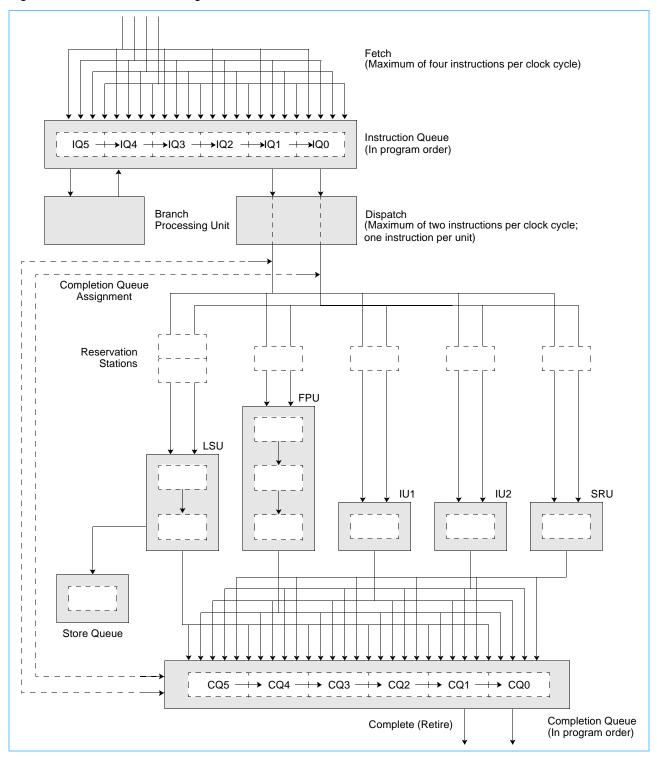

| Figure 1-5.  | Pipeline Diagram                                                     | 53  |

| Figure 2-1.  | PowerPC 750GX Microprocessor Programming Model—Registers             | 58  |

| Figure 3-1.  | Cache Integration                                                    | 122 |

| Figure 3-2.  | Data-Cache Organization                                              | 123 |

| Figure 3-3.  | Instruction-Cache Organization                                       | 125 |

| Figure 3-4.  | MEI Cache-Coherency Protocol—State Diagram (WIM = 001)               | 128 |

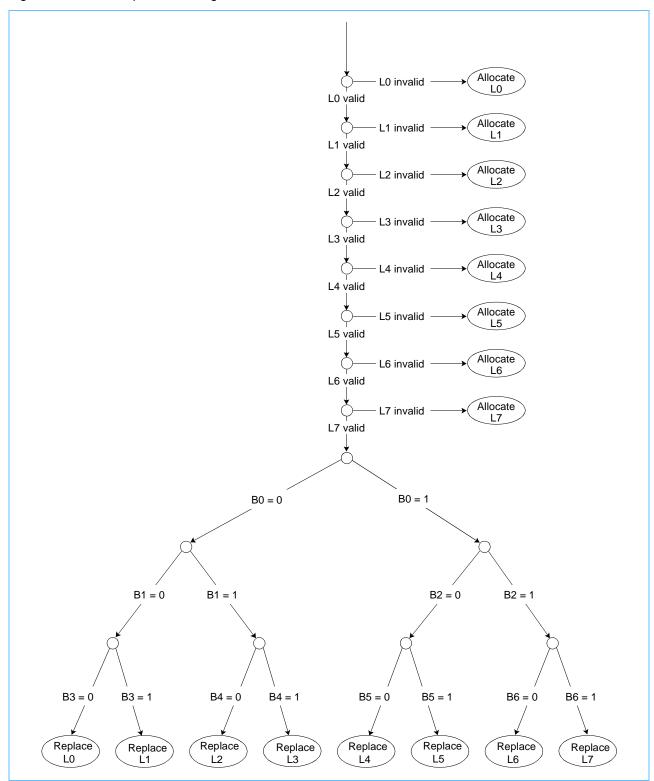

| Figure 3-5.  | PLRU Replacement Algorithm                                           |     |

| Figure 3-6.  | 750GX Cache Addresses                                                | 140 |

| Figure 4-1.  | SRESET Asserted During HRESET                                        | 164 |

| Figure 5-1.  | MMU Conceptual Block Diagram                                         | 183 |

| Figure 5-2.  | PowerPC 750GX Microprocessor IMMU Block Diagram                      | 184 |

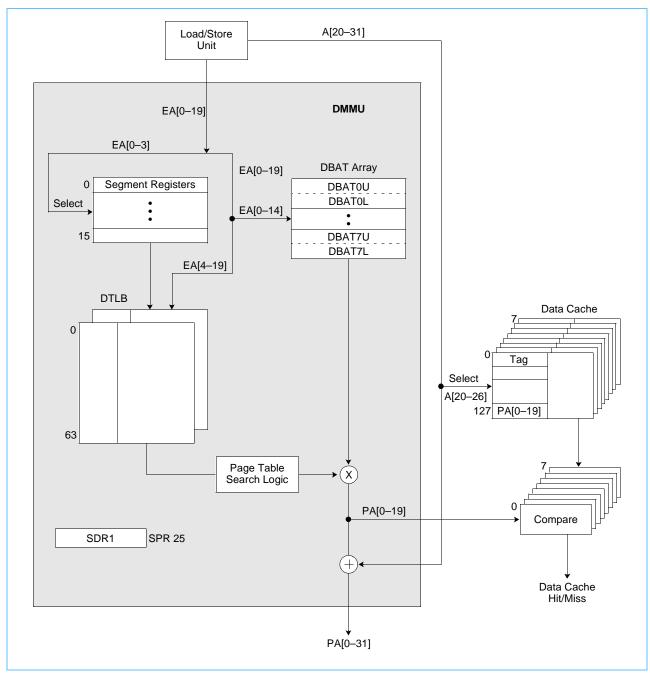

| Figure 5-3.  | 750GX Microprocessor DMMU Block Diagram                              | 185 |

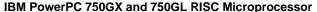

| Figure 5-4.  | Address-Translation Types                                            | 187 |

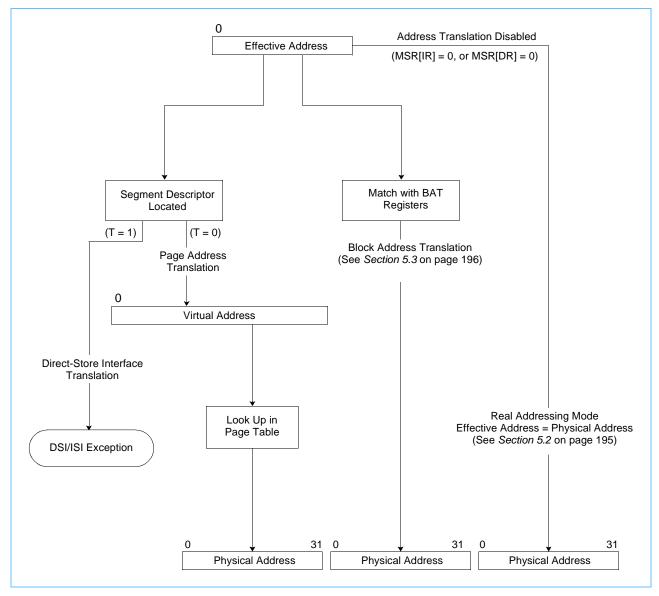

| Figure 5-5.  | General Flow of Address Translation (Real-Addressing Mode and Block) | 189 |

| Figure 5-6.  | General Flow of Page and Direct-Store Interface Address Translation  | 191 |

| Figure 5-7.  | Segment Register and DTLB Organization                               | 200 |

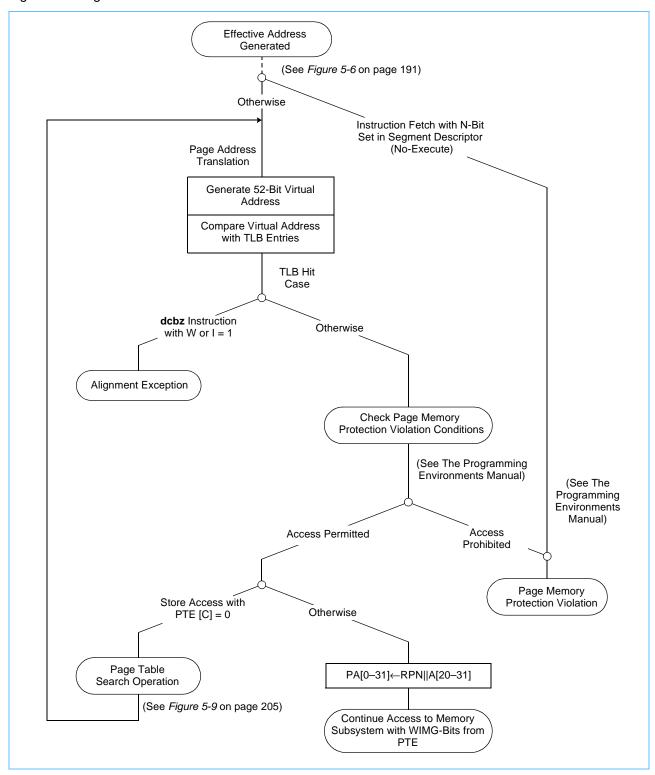

| Figure 5-8.  | Page-Address-Translation Flow—TLB Hit                                | 203 |

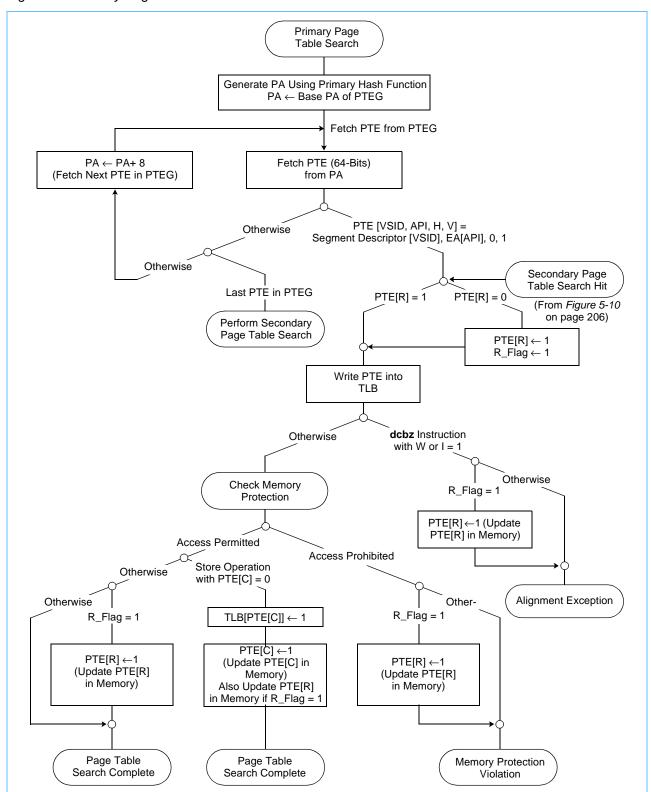

| Figure 5-9.  | Primary Page Table Search                                            | 205 |

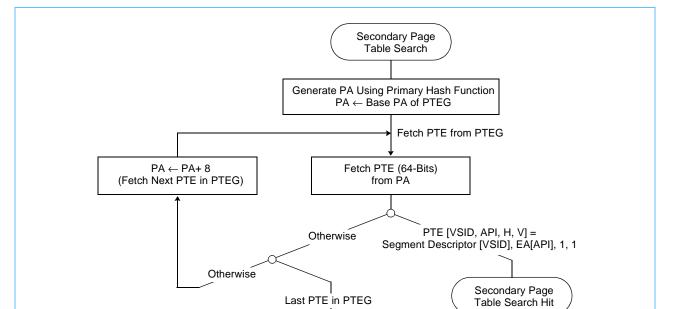

| Figure 5-10. | Secondary Page-Table-Search Flow                                     | 206 |

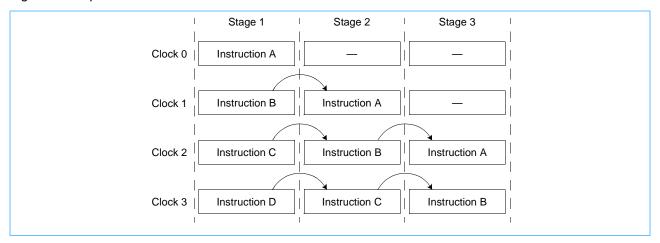

| Figure 6-1.  | Pipelined Execution Unit                                             | 212 |

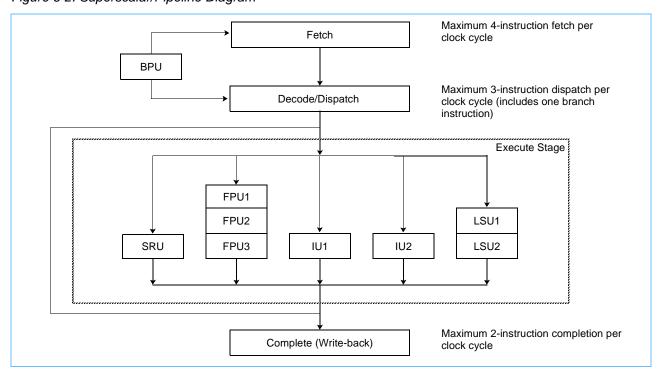

| Figure 6-2.  | Superscalar/Pipeline Diagram                                         | 212 |

| Figure 6-3.  | PowerPC 750GX Microprocessor Pipeline Stages                         | 214 |

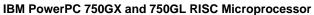

| Figure 6-4.  | Instruction Flow Diagram                                             | 218 |

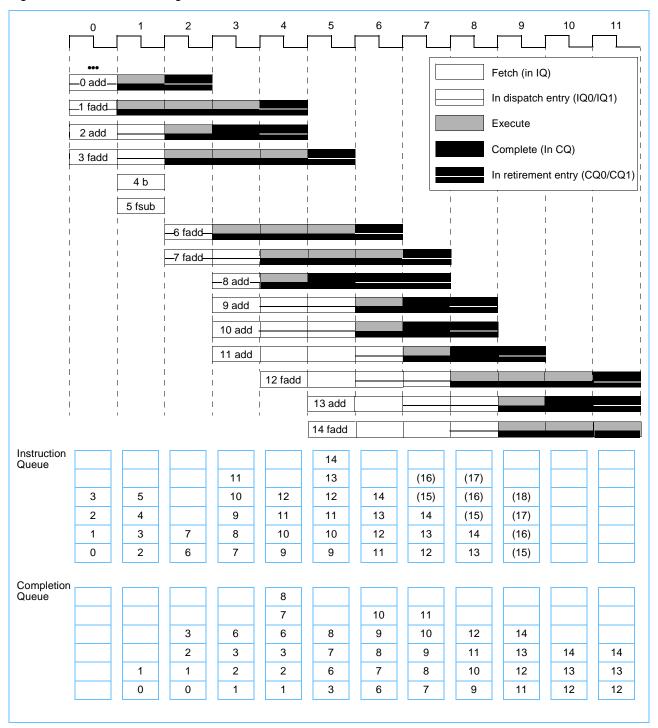

| Figure 6-5.  | Instruction Timing—Cache Hit                                         | 220 |

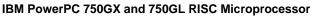

| Figure 6-6.  | Instruction Timing—Cache Miss                                        | 223 |

| Figure 6-7.  | Branch Taken                                                         | 227 |

| Figure 6-8.  | Removal of Fall-Through Branch Instruction                           | 227 |

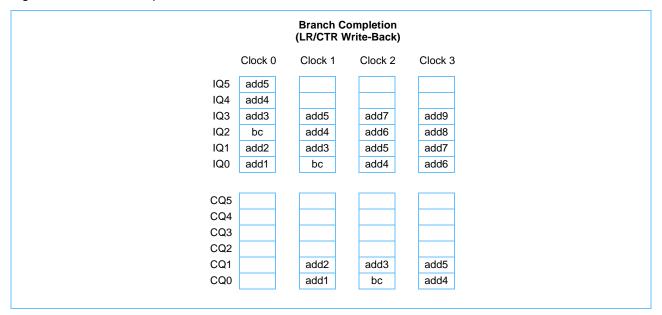

| Figure 6-9.  | Branch Completion                                                    | 228 |

| Figure 6-10. | Branch Instruction Timing                                            | 231 |

| Figure 7-1.  | 750GX Signal Groups                                                  | 250 |

| Figure 8-1.  | Bus Interface Address Buffers                                        | 280 |

| Figure 8-2.  | Timing Diagram Legend                                                | 283 |

| Figure 8-3.  | Overlapping Tenures on the 750GX Bus for a Single-Beat Transfer      | 284 |

| Figure 8-4.  | Cache Diagram for Miss-under-Miss Feature                            | 286 |

#### User's Manual

#### IBM PowerPC 750GX and 750GL RISC Microprocessor

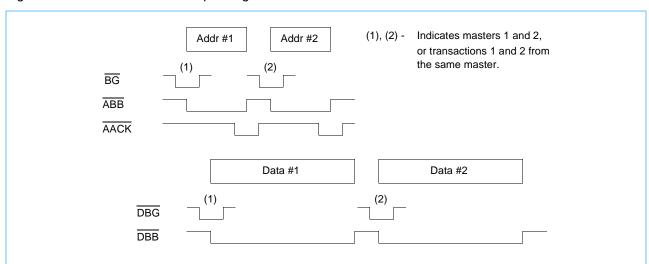

| Figure 8-5.  | First Level Address Pipelining                         | 287 |

|--------------|--------------------------------------------------------|-----|

| Figure 8-6.  | Address-Bus Arbitration                                | 290 |

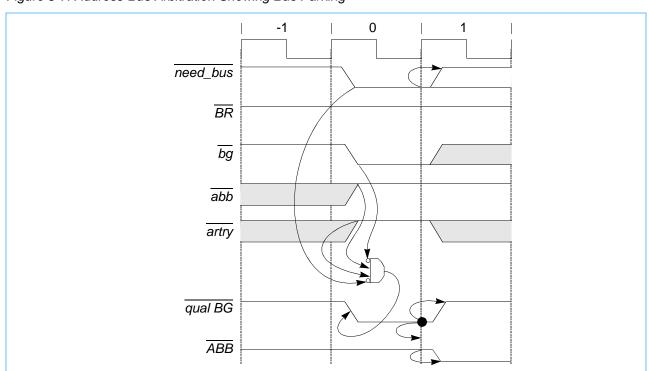

| Figure 8-7.  | Address-Bus Arbitration Showing Bus Parking            | 291 |

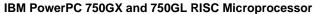

| Figure 8-8.  | Address-Bus Transfer                                   | 293 |

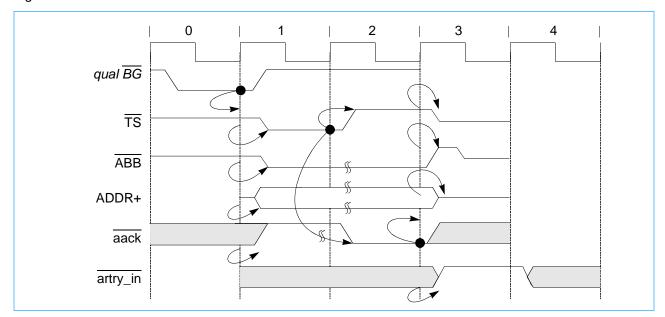

| Figure 8-9.  | Snooped Address Cycle with ARTRY                       | 301 |

| Figure 8-10. | Data-Bus Arbitration                                   | 302 |

| Figure 8-11. | Normal Single-Beat Read Termination                    | 304 |

| Figure 8-12. | Normal Single-Beat Write Termination                   | 305 |

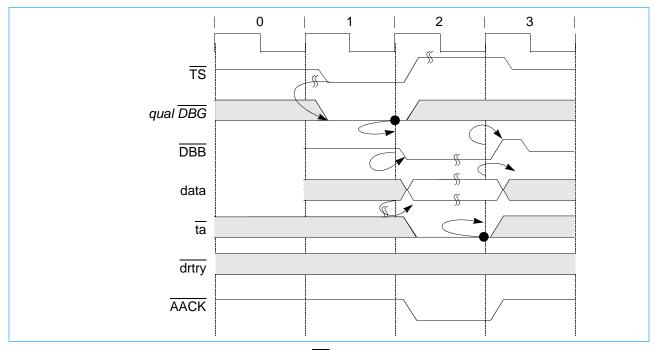

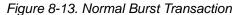

| Figure 8-13. | Normal Burst Transaction                               | 305 |

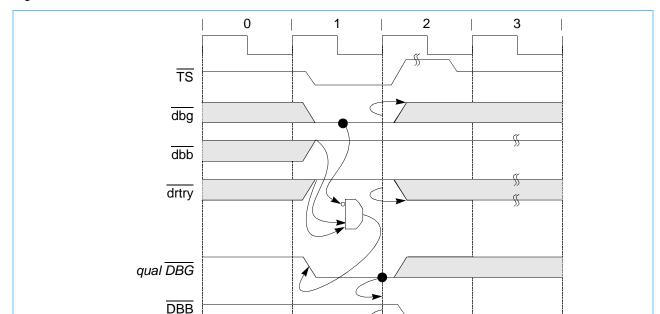

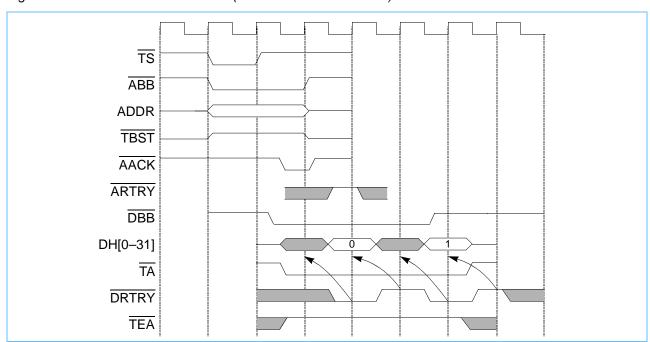

| Figure 8-14. | Termination with DRTRY                                 | 306 |

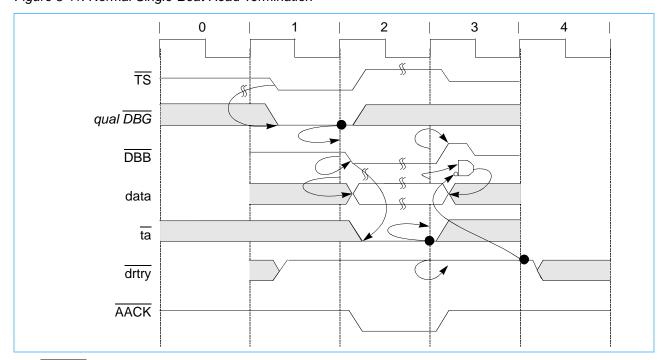

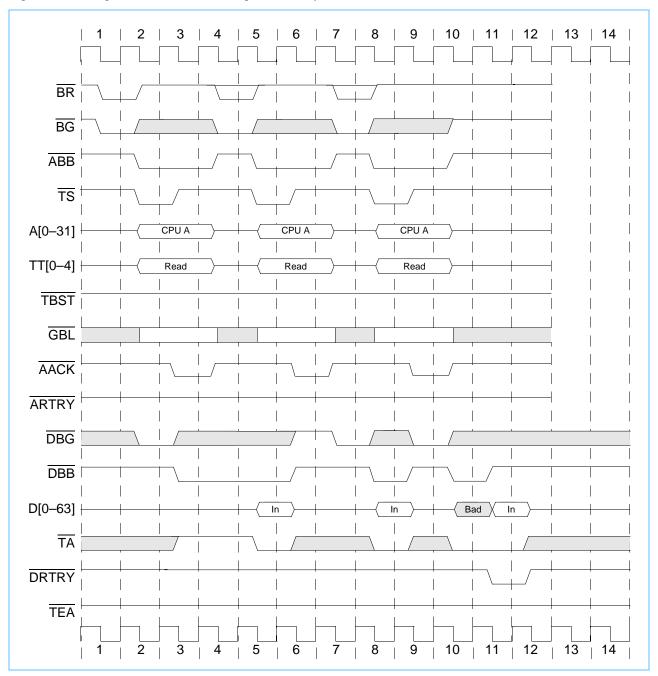

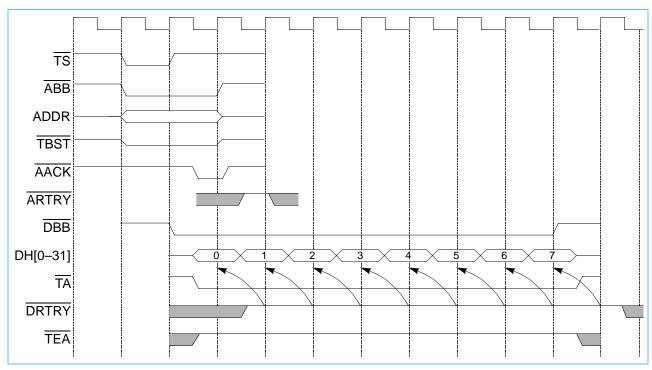

| Figure 8-15. | Read Burst with TA Wait States and DRTRY               | 307 |

| Figure 8-16. | MEI Cache-Coherency Protocol—State Diagram (WIM = 001) | 309 |

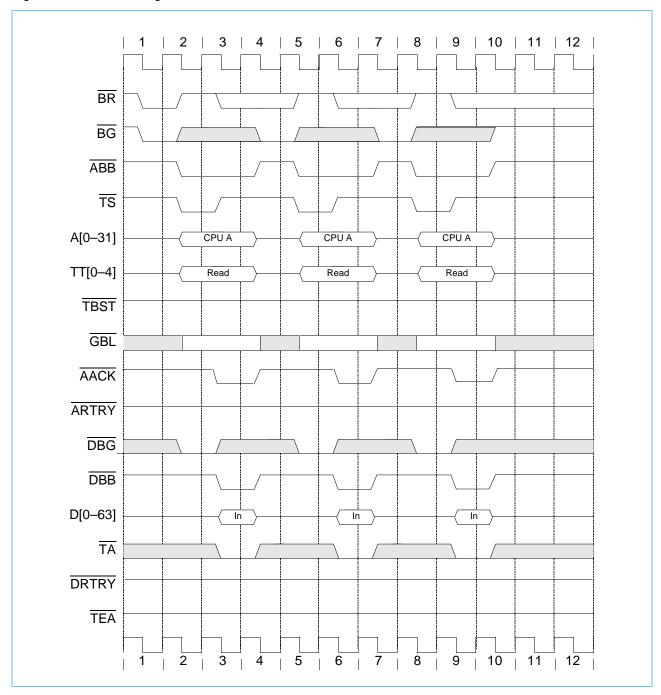

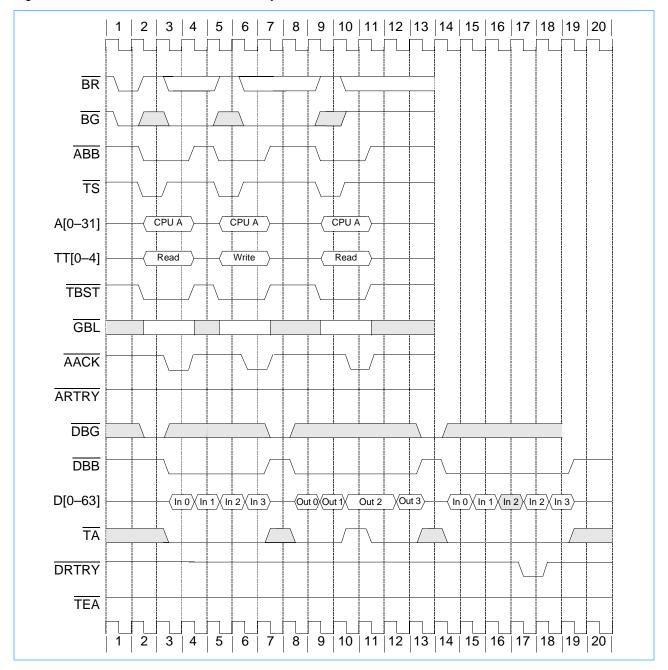

| Figure 8-17. | Fastest Single-Beat Reads                              | 310 |

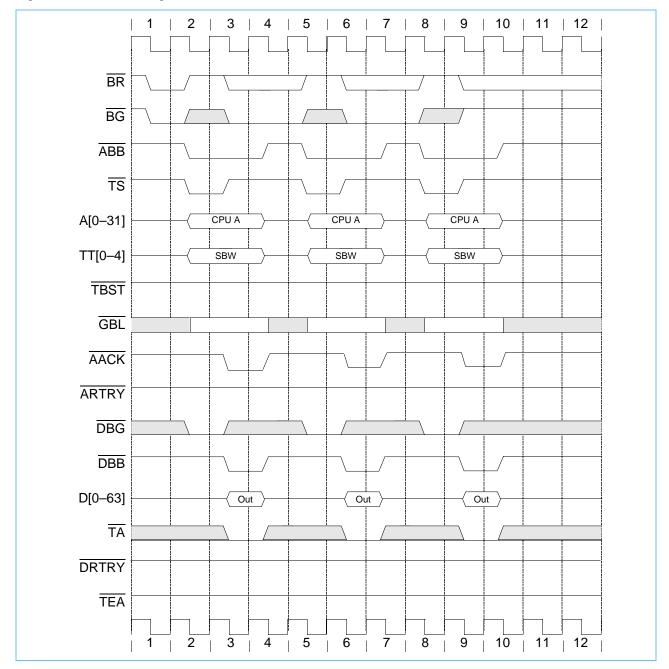

| Figure 8-18. | Fastest Single-Beat Writes                             | 311 |

| Figure 8-19. | Single-Beat Reads Showing Data-Delay Controls          | 312 |

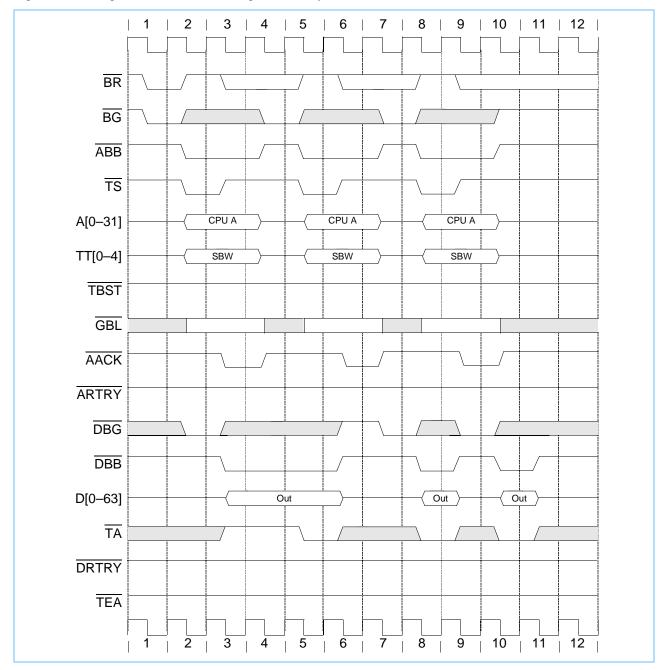

| Figure 8-20. | Single-Beat Writes Showing Data-Delay Controls         | 313 |

| Figure 8-21. | Burst Transfers with Data-Delay Controls               | 314 |

| Figure 8-22. | Use of Transfer Error Acknowledge (TEA)                | 315 |

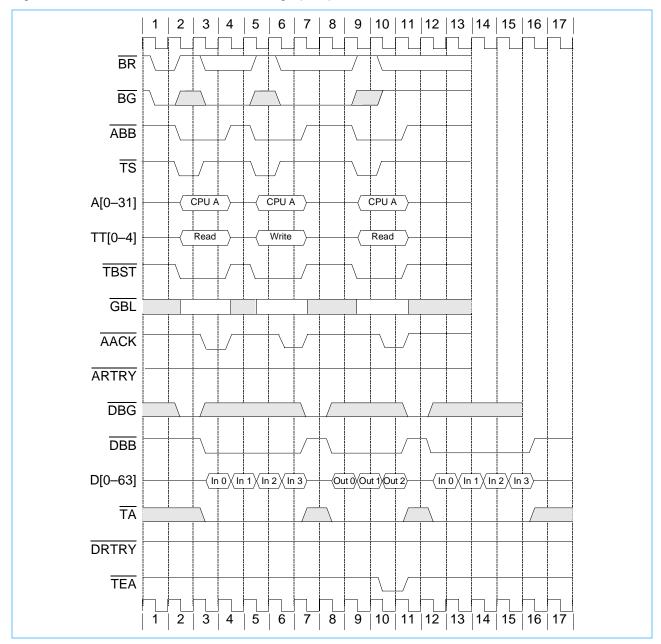

| Figure 8-23. | 32-Bit Data-Bus Transfer (8-Beat Burst)                | 317 |

| Figure 8-24. | 32-Bit Data-Bus Transfer (2-Beat Burst with DRTRY)     | 317 |

| Figure 8-25. | IEEE 1149.1a-1993 Compliant Boundary-Scan Interface    | 320 |

| Figure 8-26. | Data-Bus Write-Only Transaction                        | 320 |

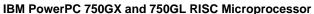

| Figure 9-1.  | L2 Cache                                               | 327 |

| Figure 10-1. | 750GX Power States                                     | 336 |

| Figure 10-2. | Dual PLL Block Diagram                                 | 342 |

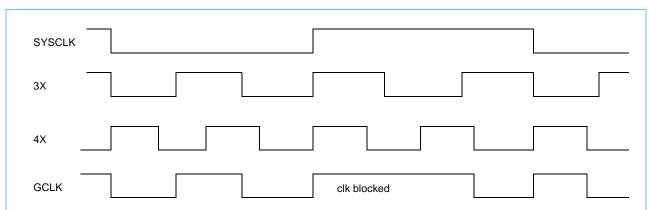

| Figure 10-3. | Dual PLL Switching Example, 3X to 4X                   | 343 |

| Figure 10-4. | Thermal Assist Unit Block Diagram                      | 344 |

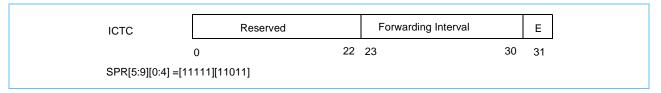

| Figure 10-5. | Instruction Cache Throttling Control SPR Diagram       | 347 |

| Figure 11-1. | 750GX IEEE 1149.1a-1993/COP Organization               | 358 |

| Figure 11-2. | Reset Sequence                                         | 360 |

#### **List of Tables**

| Table 1-1.  | Architecture-Defined Registers (Excluding SPRs)                | 42  |

|-------------|----------------------------------------------------------------|-----|

| Table 1-2.  | Architecture-Defined SPRs Implemented                          | 43  |

| Table 1-3.  | Implementation-Specific Registers                              | 44  |

| Table 1-4.  | 750GX Microprocessor Exception Classifications                 | 49  |

| Table 1-5.  | Exceptions and Conditions                                      | 50  |

| Table 2-1.  | Additional MSR Bits                                            | 60  |

| Table 2-2.  | Additional SRR1 Bits                                           | 62  |

| Table 2-3.  | Valid THRM1/THRM2 Bit Settings                                 | 79  |

| Table 2-4.  | Memory Operands                                                | 82  |

| Table 2-5.  | Floating-Point Operand Data-Type Behavior                      | 84  |

| Table 2-6.  | Floating-Point Result Data-Type Behavior                       | 85  |

| Table 2-7.  | Integer Arithmetic Instructions                                | 92  |

| Table 2-8.  | Integer Compare Instructions                                   | 93  |

| Table 2-9.  | Integer Logical Instructions                                   | 94  |

| Table 2-10. | Integer Rotate Instructions                                    | 95  |

| Table 2-11. | Integer Shift Instructions                                     | 95  |

| Table 2-12. | Floating-Point Arithmetic Instructions                         | 96  |

| Table 2-13. | Floating-Point Multiply/Add Instructions                       | 96  |

| Table 2-14. | Floating-Point Rounding and Conversion Instructions            | 97  |

| Table 2-15. | Floating-Point Compare Instructions                            | 97  |

| Table 2-16. | Floating-Point Status and Control Register Instructions        | 97  |

| Table 2-17. | Floating-Point Move Instructions                               | 98  |

| Table 2-18. | Integer Load Instructions                                      | 99  |

| Table 2-19. | Integer Store Instructions                                     | 101 |

| Table 2-20. | Integer Load-and-Store with Byte-Reverse Instructions          | 102 |

| Table 2-21. | Integer Load-and-Store Multiple Instructions                   | 102 |

| Table 2-22. | Integer Load-and-Store String Instructions                     | 103 |

| Table 2-23. | Floating-Point Load Instructions                               | 104 |

| Table 2-24. | Floating-Point Store Instructions                              | 105 |

| Table 2-25. | Store Floating-Point Single Behavior                           | 105 |

| Table 2-26. | Store Floating-Point Double Behavior                           | 105 |

| Table 2-27. | Branch Instructions                                            | 107 |

| Table 2-28. | Condition Register Logical Instructions                        | 107 |

| Table 2-29. | Trap Instructions                                              | 108 |

| Table 2-30. | System Linkage Instruction—UISA                                | 108 |

| Table 2-31. | Move-to/Move-from Condition Register Instructions              | 108 |

| Table 2-32. | Move-to/Move-from Special-Purpose Register Instructions (UISA) | 109 |

| Table 2-33. | PowerPC Encodings                                              | 109 |

| Table 2-34. | SPR Encodings for 750GX-Defined Registers (mfspr)               | 112 |

|-------------|-----------------------------------------------------------------|-----|

| Table 2-35. | Memory Synchronization Instructions—UISA                        | 113 |

| Table 2-36. | Move-from Time Base Instruction                                 | 114 |

| Table 2-37. | Memory Synchronization Instructions—VEA                         | 115 |

| Table 2-38. | User-Level Cache Instructions                                   | 116 |

| Table 2-39. | External Control Instructions                                   | 117 |

| Table 2-40. | System Linkage Instructions—OEA                                 | 118 |

| Table 2-41. | Move-to/Move-from Machine State Register Instructions           | 118 |

| Table 2-42. | Move-to/Move-from Special-Purpose Register Instructions (OEA)   | 118 |

| Table 2-43. | Supervisor-Level Cache-Management Instruction                   | 119 |

| Table 2-44. | Segment Register Manipulation Instructions                      | 119 |

| Table 2-45. | Translation Lookaside Buffer Management Instruction             | 120 |

| Table 3-1.  | MEI State Definitions                                           | 127 |

| Table 3-2.  | PLRU Bit Update Rules                                           | 138 |

| Table 3-3.  | PLRU Replacement Block Selection                                | 138 |

| Table 3-4.  | Bus Operations Caused by Cache-Control Instructions (WIM = 001) | 141 |

| Table 3-5.  | Response to Snooped Bus Transactions                            | 143 |

| Table 3-6.  | Address/Transfer Attribute Summary                              | 146 |