# **AW8 Series**

**(AW8, AW8-MAX)**

Intel Pentium 4 System Board Socket 775

User's Manual

4200-0454-03 Rev. 1.01

# **Copyright and Warranty Notice**

The information in this document is subject to change without notice and does not represent a commitment on part of the vendor, who assumes no liability or responsibility for any errors that may appear in this manual.

No warranty or representation, either expressed or implied, is made with respect to the quality, accuracy or fitness for any particular part of this document. In no event shall the manufacturer be liable for direct, indirect, special, incidental or consequential damages arising from any defect or error in this manual or product.

Product names appearing in this manual are for identification purpose only and trademarks and product names or brand names appearing in this document are the property of their respective owners.

This document contains materials protected under International Copyright Laws. All rights reserved. No part of this manual may be reproduced, transmitted or transcribed without the expressed written permission of the manufacturer and authors of this manual.

If you do not properly set the motherboard settings, causing the motherboard to malfunction or fail, we cannot guarantee any responsibility.

# **Table of Contents**

| Cnapter | 1. Introduction                                | 1-1  |

|---------|------------------------------------------------|------|

| 1-1.    | Features & Specifications                      | 1-1  |

| 1-2.    | Layout Diagram                                 | 1-3  |

| Chapter | 2. Hardware Setup                              | 2-1  |

| 2-1.    | Install The Motherboard                        |      |

| 2-2.    | Install CPU, Heatsink and Fan Assembly         | 2-2  |

| 2-3.    | Install System Memory                          | 2-4  |

| 2-4.    | Connectors, Headers and Switches               | 2-6  |

|         | (1). ATX Power Input Connectors                | 2-6  |

|         | (2). FAN Power Connectors                      | 2-7  |

|         | (3). CMOS Memory Clearing Header               | 2-8  |

|         | (4). Wake-up Header                            | 2-9  |

|         | (5). Back Panel Audio Connection Slot          | 2-10 |

|         | (6). Front Panel Switches & Indicators Headers |      |

|         | (7). Additional IEEE1394 Port Headers          |      |

|         | (8). Additional USB Port Headers               |      |

|         | (9). GURU Clock Connection Header              |      |

|         | (10). Floppy and IDE Disk Drive Connectors     |      |

|         | (11). POST Code Display                        |      |

|         | (12). Serial ATA Connectors                    |      |

|         | (13). PCI Express x16 Slot                     |      |

|         | (14). PCI Express x1 Slots                     |      |

|         | (15). Back Panel Connectors                    | 2-20 |

| Chapter | 3. BIOS Setup                                  | 3-1  |

| 3-1.    | µGuru <sup>™</sup> Utility                     | 3-2  |

| 3-2.    | Standard CMOS Features                         | 3-10 |

| 3-3.    | Advanced BIOS Features                         | 3-12 |

| 3-4.    | Advanced Chipset Features                      | 3-15 |

| 3-5.    | Integrated Peripherals                         | 3-17 |

| 3-6.    | Power Management Setup                         | 3-20 |

| 3-7.    | PnP/PCI Configurations                         | 3-23 |

| 3-8.    | Load Fail-Safe Defaults                        | 3-24 |

| 3-9.    | Load Optimized Defaults                        | 3-24 |

| 3-10.   | Set Password                                   |      |

| 3-11.   | Save & Exit Setup                              |      |

| 3-12. Ex    | xit Without Saving                                  | 3-24       |

|-------------|-----------------------------------------------------|------------|

| Appendix A. | Install Intel Chipset Software Installation Utility | A-1        |

| Appendix B. | Install Intel Matrix Storage Technology RAID Driver | B-1        |

| Appendix C. | Install Audio Driver                                |            |

| Appendix D. | Install BCM LAN Driver                              | <i>D-1</i> |

| Appendix E. | Install Sil3132 SATA Driver (AW8-MAX)               | E-1        |

| Appendix F. | Install USB 2.0 Driver                              | F-1        |

| Appendix G. | Install ABIT µGuru Utility                          | <i>G-1</i> |

| Appendix H. | POST Code Definition                                | Н-1        |

| Appendix I. | Troubleshooting (Need Assistance?)                  | <i>I-1</i> |

| Appendix J. | How to Get Technical Support                        |            |

Introduction 1-1

# Chapter 1. Introduction

# 1-1. Features & Specifications

#### 1. CPU

- Designed for Intel® Pentium 4 / Pentium D LGA775 processors with 1066/800 MHz FSB

- Supports Intel® Hyper-Threading / XD-bit / EM64T / EIST Technology

#### 2. Chipset

Intel<sup>®</sup> 955X / Intel<sup>®</sup> ICH7R Express Chipset

#### 3. Memory

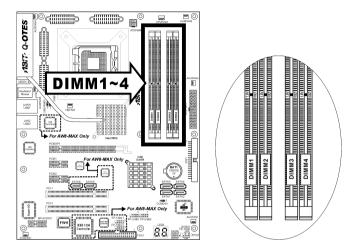

- Four 240-pin DIMM slots (Un-buffered Non-ECC DIMM)

- Supports Dual channel DDR2 667/533 (Max. 8GB)

#### 4. PCI-E x16 Graphic

• Delivers up to 8GB/s per direction for 3.5 times more bandwidth than AGP8X

#### 5. ABIT Engineered

- ABIT uGuru<sup>™</sup> 2005 Technology (ABIT OC Guru / ABIT EQ / ABIT Flash Menu / ABIT Black Box)

- ABIT CPU ThermalGuard<sup>™</sup> Technology

- ABIT AudioMAX HD 7.1 Technology

#### 6. SATAII 3G RAID

- Intel<sup>®</sup> Matrix Storage Technology supports RAID 0/1/5/10

- Supports SATA AHCI, providing native command queuing and native hot plug

# 7. 2<sup>nd</sup> PCIE SATAII 3G

OnBoard Silicon Image PCIE SATAII 3G RAID controller (For model AW8-MAX only)

#### 8. Dual PCI-E Gigabit LAN

OnBoard Dual PCI-E Gigabit LAN controller supports 10/100/1000Mbps Ethernet (For model AW8-MAX only)

#### 9. IEEE 1394b

Supports 2 Ports IEEE 1394b at 800 Mb/s transfer rate and 1 port 1394a (For model AW8-MAX only)

#### 10. Audio

- ABIT AudioMAX HD 7.1-channel Intel<sup>®</sup> High Definition Audio with Dolby Master Studio

- Supports auto jack sensing and optical S/PDIF In/Out

#### 11. Internal I/O Connectors

- 1x PCI Express x16 slot

- 2x PCI-E x1 slots

1-2 Chapter 1

- 2x PCI slots

- 1x AudioMAX slot

- 1x Floppy port

- 1x UDMA 100/66/33 connector

- 2x SATA connectors (For model AW8-MAX only)

- 4x SATA connectors

- 2x USB 2.0 headers

- 2x IEEE1394b headers (For model AW8-MAX only)

- 1x FP-Audio header

- 1x CD-IN header

#### 12. Back Panel I/O

- ABIT Q-OTES<sup>™</sup> Technology

- 1x PS/2 keyboard, 1x PS/2 mouse

- 1x IEEE1394a connector (For model AW8-MAX only)

- 4x USB 2.0 connectors

- 2x RJ-45 Gigabit LAN connectors

#### 13. Miscellaneous

- ATX form factor (305mm x 245mm)

- \* Specifications and information contained herein are subject to change without notice.

Introduction 1-3

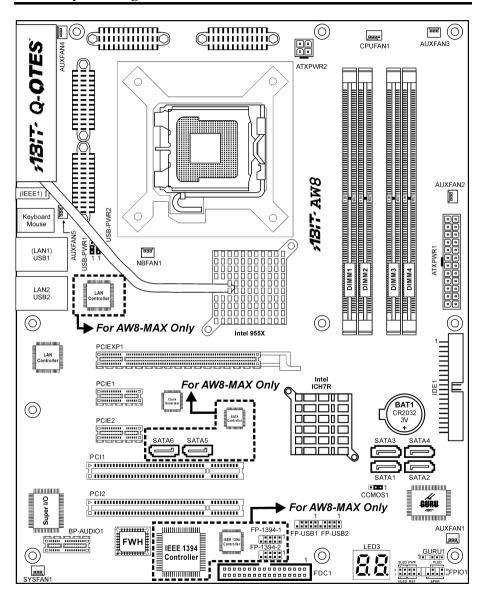

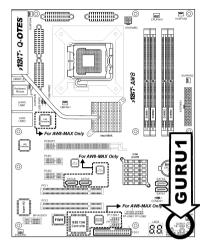

# 1-2. Layout Diagram

1-4 Chapter 1

# Chapter 2. Hardware Setup

**Before installation:** Turn off the power supply switch (fully turn off the +5V standby power), or disconnect the power cord before installing or unplugging any connectors or add-on cards. Failing to do so may cause the motherboard components or add-on cards to malfunction or become damaged.

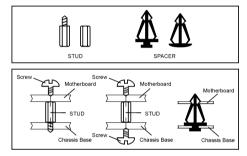

### 2-1. Install The Motherboard

Most computer chassis have a base with many mounting holes to allow the motherboard to be securely attached, and at the same time, prevent the system from short circuits. There are two ways to attach the motherboard to the chassis base:

- 1. use studs, or

- 2. use spacers

In principle, the best way to attach the board is to use studs. Only if you are unable to do this should you attach the board with spacers. Line up the holes on the board with the mounting holes on the chassis. If the holes line up and there are screw holes, you can attach the board with studs. If the holes line up and there are only slots, you can only attach with spacers. Take the tip of the spacers and insert them into the slots. After doing this to all the slots, you can slide the board into position aligned with slots. After the board has been positioned, check to make sure everything is OK before putting the chassis back on.

**ATTENTION:** To prevent shorting the PCB circuit, please REMOVE the metal studs or spacers if they are already fastened on the chassis base and are without mounting-holes on the motherboard to align with.

2-2 Chapter 2

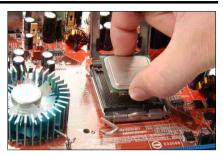

# 2-2. Install CPU, Heatsink and Fan Assembly

In order to protect the contact pins, please pay attention to these notices:

- 1. A maximum 20 cycles of CPU installation is recommended.

- Never touch the contact pins with fingers or any object.

- 3. Always put on the cap when the CPU is not in use.

1. Place the board so as to let the lever hook of the socket is on your left side. Use your left thumb and forefinger to hold the lever hook, pull it away from the retention tab.

2. Rotate the lever to fully open position.

**3.** Use your right thumb on the bottom-right side of the load plate and lift it up to fully open position.

**4.** Use your right thumb and forefinger to grasp the CPU package. Be sure to grasp on the edge of the substrate, and face the Pin-1 indicator toward the bottom-left side. Aim at the socket and place the CPU package vertical down into the socket.

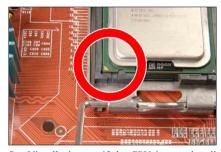

**5.** Visually inspect if the CPU is seated well into the socket. The alignment key must be located in the notch of package.

**6.** Use your left hand to hold the load plate, and use your right thumb to peel the cap off.

The cap plays an important role in protecting contact pins. In order to prevent bent pin, PUT ON the cap after operation or testing.

7. Lower the plate onto the CPU package. Engage the load lever while gently pressing down the load plate.

**8.** Secure the lever with the hook under retention tab.

**9.** Place the heatsink and fan assembly onto the socket. Align the four fasteners toward the four mounting holes on the motherboard.

It is strongly recommended that you use an air-cooled fan heatsink designed for the LGA775 processor.

For detailed information on how to install your heatsink and fan assembly, please refer to the instruction manual came packed with the heatsink and fan assembly you bought

**10.** Press each of the four fasteners down into the mounting holes.

**11.** Rotate the fastener clock-wise to lock the heatsink and fan assembly into position.

12. Attach the four-pin power plug from the heatsink and fan assembly to the CPU FAN connector.

2-4 Chapter 2

# 2-3. Install System Memory

The Intel® 955X Express Chipset MCH memory interface is designed with Flex Memory Technology supporting single-channel or dual-channel DDR2 memory configurations.

- To reach the optimum performance in dual-channel configurations, install identical DDR2 DIMM pairs for each channel.

- Install DIMMs with the same CAS latency. To reach the optimum compatibility, obtain memory

modules from the same vendor.

- Due to chipset resource allocation, the system may detect less than 4GB of system memory in the installation of four 1GB DDR2 memory modules.

- Due to chipset limitation, 128MB DIMM modules or double-sided x16 memory chips are not supported.

There are several methods of different DDR2 configurations depending on how the DIMMs are populated on each system memory channel:

• [Single Channel]: only one channel is populated.

| Method | Channel A |       | Channel B |       |

|--------|-----------|-------|-----------|-------|

| Methou | DIMM1     | DIMM2 | DIMM3     | DIMM4 |

| 1      | 512MB     | =     | =         | -     |

| 2      | -         | 512MB | =         | -     |

| 3      | ı.        | i.    | 512MB     | -     |

| 4      | =         | =     | =         | 512MB |

| 5      | 512MB     | 512MB | =         | -     |

| 6      | -         | =     | 512MB     | 512MB |

[Dual Channel Asymmetric]: both channels are populated, but each channel has a different amount of total memory. (Channel  $A \neq Channel B$ )

| Method | Channel A |       | Channel B |       |

|--------|-----------|-------|-----------|-------|

| Method | DIMM1     | DIMM2 | DIMM3     | DIMM4 |

| 1      | 512MB     | =     | 256MB     | =     |

| 2      | -         | 256MB | -         | 512MB |

| 3      | 512MB     | =     | =         | 256MB |

| 4      | -         | 256MB | 512MB     | -     |

| 5      | 256MB     | 256MB | 256MB     | -     |

| 6      | 256MB     | 256MB | -         | 256MB |

| 7      | 256MB     | =     | 256MB     | 256MB |

| 8      | -         | 256MB | 256MB     | 256MB |

| 9      | 256MB     | 256MB | 512MB     | 512MB |

| 10     | 256MB     | 256MB | 256MB     | 512MB |

[Dual Channel Symmetric]: both channels are populated where each channel has the same amount of total memory. (Channel A = Channel B)

| Method | Channel A |       | Channel B |       |

|--------|-----------|-------|-----------|-------|

|        | DIMM1     | DIMM2 | DIMM3     | DIMM4 |

| 1      | 512MB     | =     | 512MB     | =     |

| 2      | -         | 512MB | =         | 512MB |

| 3      | 512MB     | =     | =         | 512MB |

| 4      | -         | 512MB | 512MB     | -     |

| 5      | 256MB     | 256MB | 512MB     | -     |

| 6      | 256MB     | 256MB | =         | 512MB |

| 7      | 512MB     | -     | 256MB     | 256MB |

| 8      | -         | 512MB | 256MB     | 256MB |

| 9      | 512MB     | 256MB | 512MB     | 256MB |

| 10     | 256MB     | 512MB | 256MB     | 512MB |

Power off the computer and unplug the AC power cord before installing or removing memory modules.

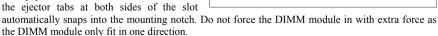

- Locate the DIMM slot on the board

- 2. Hold two edges of the DIMM module carefully, keep away of touching connectors.

- 3. Align the notch key on the module with the rib on the slot

- Firmly press the module into the slots until the ejector tabs at both sides of the slot

5. To remove the DIMM modules, push the two ejector tabs on the slot outward simultaneously, and then pull out the DIMM module.

ATTENTION: Static electricity can damage the electronic components of the computer or optional boards. Before starting these procedures, ensure that you are discharged of static electricity by touching a grounded metal object briefly.

2-6 Chapter 2

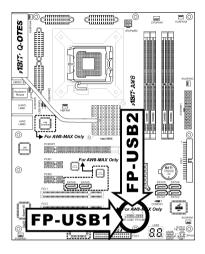

# 2-4. Connectors, Headers and Switches

Here we will show you all of the connectors, headers and switches, and how to connect them. Please read the entire section for necessary information before attempting to finish all the hardware installation inside the computer chassis. A complete enlarged layout diagram is shown in Chapter 1 for all the position of connectors and headers on the board that you may refer to.

**WARNING:** Always power off the computer and unplug the AC power cord before adding or removing any peripheral or component. Failing to so may cause severe damage to your motherboard and/or peripherals. Plug in the AC power cord only after you have carefully checked everything.

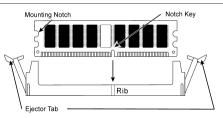

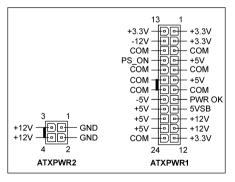

#### (1). ATX Power Input Connectors

This motherboard provides two power connectors to connect ATX12V power supplier.

**NOTE:** This 24-pin power connector "ATXPWR1" is compliant to the former 20-pin type. Pay attention to the orientation when doing so (Pin-11, 12, 23, and 24 should be left un-connected).

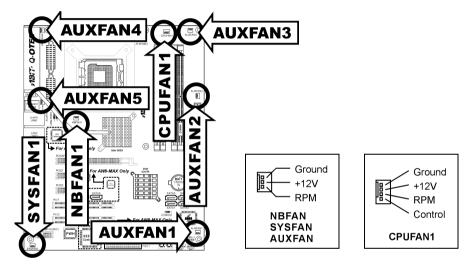

#### (2). FAN Power Connectors

These connectors each provide power to the cooling fans installed in your system.

- CPUFAN1: CPU Fan Power Connector

- NBFAN1: Chipset Fan Power Connector

- SYSFAN1: System Fan Power Connector

- AUXFAN1 ~ 5: Auxiliary Fan Power Connector

WARNING: These fan connectors are not jumpers. DO NOT place jumper caps on these connectors.

2-8 Chapter 2

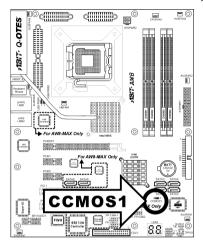

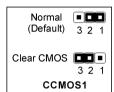

## (3). CMOS Memory Clearing Header

This header uses a jumper cap to clear the CMOS memory.

- Pin 1-2 shorted (default): Normal operation.

- Pin 2-3 shorted: Clear CMOS memory.

**WARNING:** Turn the power off first (including the +5V standby power) before clearing the CMOS memory. Failing to do so may cause your system to work abnormally or malfunction.

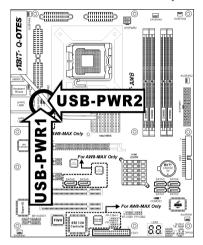

#### (4). Wake-up Header

These headers use a jumper cap to enable/disable the wake-up function.

#### • USB-PWR1:

Pin 1-2 shorted (default): Disable wake-up function support at USB1 port. Pin 2-3 shorted: Enable wake-up function support at USB1 port.

#### • USB-PWR2:

Pin 1-2 shorted (default): Disable wake-up function support at USB2 port. Pin 2-3 shorted: Enable wake-up function support at USB2 port

2-10 Chapter 2

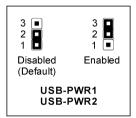

#### (5). Back Panel Audio Connection Slot

The slot "BP-AUDIO1" provides the audio input/output connection at back panel through an audio daughter-card.

#### NOTE: Install this daughter-card at slot "BP-AUDIO1".

- S/PDIF Out: This connector provides an S/PDIF-Out connection through optical fiber to digital

multimedia devices.

- S/PDIF In: This connector provides an S/PDIF-In connection through optical fiber to digital

multimedia devices.

**Line-In:** Connects to the line out from external audio sources.

- **Mic-In:** Connects to the plug from external microphone.

- Line-Out: Connects to the front left and front right channel in the 7.1-channel or regular 2-channel audio system.

- Cen/Sub: Connects to the center and subwoofer channel in the 7.1 channel audio system.

- R.L./R.R. (Rear Left / Rear Right): Connects to the rear left and rear right channel in the 7.1 channel audio system.

- S.L./S.R. (Surround Left / Surround Right): Connects to the surround left and surround right channel in the 7.1 channel audio system.

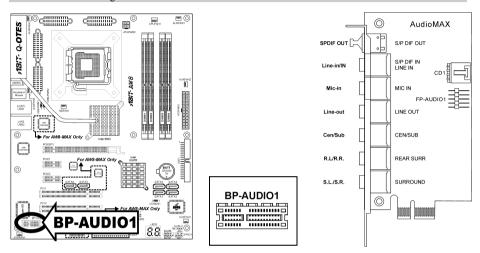

#### S/PDIF Connection:

Along with the motherboard package you can find an audio daughter-card and a roll of optical fiber cable for S/PDIF connection.

#### S/PDIF Input Connection:

- 1. Plug the end with 3.5mm adapter into the [JK1] jack on this daughter-card. (This jack is used for either optical or line input.)

- 2. Remove the rubber protection-cap at the other end. Plug it into the [Digital-Out] (SPDIF-Out) jack on your digital multimedia device.

#### • S/PDIF Output Connection:

- 1. Pull out the 3.5mm adapter at one end. Keep this adapter with its protection-cap covered in save place. Plug the rest of this end into the [SPDIF-O] jack on this daughter-card.

- Remove the rubber protection-cap at the other end. Plug it into the [Digital-In] (SPDIF-In) jack on your digital multimedia device.

2-12 Chapter 2

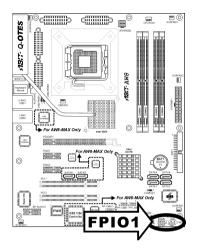

#### (6). Front Panel Switches & Indicators Headers

This header is used for connecting switches and LED indicators on the chassis front panel.

Watch the power LED pin position and orientation. The mark "+" align to the pin in the figure below stands for positive polarity for the LED connection. Please pay attention to connect these headers. A wrong orientation will only cause the LED not lighting, but a wrong connection of the switches could cause system malfunction.

- HLED (Pin 1, 3):

Connects to the HDD LED cable of chassis front panel.

- RST (Pin 5, 7):

Connects to the Reset Switch cable of chassis front panel.

- SPKR (Pin 13, 15, 17, 19): Connects to the System Speaker cable of chassis.

- SLED (Pin 2, 4):

Connects to the Suspend LED cable (if there is one) of chassis front panel.

- PWR (Pin 6, 8):

Connects to the Power Switch cable of chassis front panel.

- PLED (Pin 16, 18, 20):

Connects to the Power LED cable of chassis front panel.

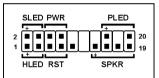

# (7). Additional IEEE1394 Port Headers

These headers each provide one additional IEEE1394 port connection through an extension cable and bracket.

#### AW8-MAX:

|   |                        | Pin | Pin Assignment | Pin | Pin Assignment |

|---|------------------------|-----|----------------|-----|----------------|

| F | 7 5 3 1                | 1   | TPA0 +         | 2   | TPA0 -         |

|   |                        | 3   | Ground         | 4   | Ground         |

|   | 10 8 6 4 2             | 5   | TPB0 +         | 6   | TPB0 -         |

|   | FP-1394-1<br>FP-1394-2 | 7   | +12V           | 8   | +12V           |

|   |                        | 9   | NC             | 10  | Ground         |

2-14 Chapter 2

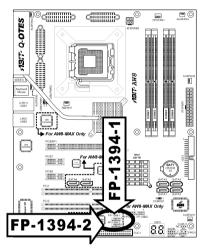

# (8). Additional USB Port Headers

These headers each provide 2 additional USB 2.0 ports connection through an USB cable designed for USB 2.0 specifications.

|                    | Pin | Pin Assignment | Pin | Pin Assignment |

|--------------------|-----|----------------|-----|----------------|

| 7 5 3 1            | 1   | VCC            | 2   | VCC            |

|                    | 3   | Data0 -        | 4   | Data1 -        |

| 108642             | 5   | Data0 +        | 6   | Data1 +        |

| FP-USB1<br>FP-USB2 | 7   | Ground         | 8   | Ground         |

|                    | 9   | NC             | 10  | NC             |

# (9). GURU Clock Connection Header

This header is reserved for connecting ABIT's exclusive GURU Clock.

2-16 Chapter 2

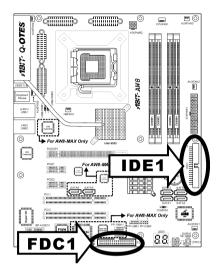

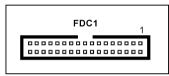

#### (10). Floppy and IDE Disk Drive Connectors

The FDC1 connector connects up to two floppy drives with a 34-wire, 2-connector floppy cable. Connect the single end at the longer length of ribbon cable to the FDC1 on the board, the two connectors on the other end to the floppy disk drives connector. Generally you need only one floppy disk drive in your system.

**NOTE:** The red line on the ribbon cable must be aligned with pin-1 on both the FDC1 port and the floppy connector.

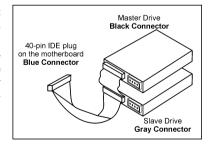

Each of the IDE port connects up to two IDE drives at Ultra ATA/100 mode by one 40-pin, 80-conductor, and 3-connector Ultra ATA/66 ribbon cables.

Connect the single end (blue connector) at the longer length of ribbon cable to the IDE port of this board, the other two ends (gray and black connector) at the shorter length of the ribbon cable to the connectors of your hard drives.

**NOTE:** Make sure to configure the "Master" and "Slave" relation before connecting two drives by one single ribbon cable. The red line on the ribbon cable must be aligned with pin-1 on both the IDE port and the hard-drive connector.

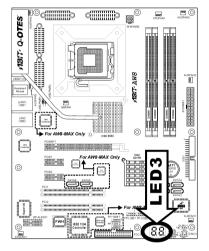

#### (11). POST Code Display

This is an LED device to display the "POST" Code, the acronym of Power On Self Test. The computer will execute the POST action whenever you power on the computer. The POST process is controlled by the BIOS. It is used to detect the status of the computer's main components and peripherals. Each POST Code corresponds to different checkpoints that are also defined by the BIOS in advance. For example, "memory presence test" is an important checkpoint and its POST Code is "C1". When the BIOS execute any POST item, it will write the corresponding POST Code into the address 80h. If the POST passes, the BIOS will process the next POST item and write the next POST Code into the address 80h. If the POST fails, we can check the POST Code in address 80h to find out where the problem lies.

This LED device also displays the "POST" Code of AC2005, an "uGuru" chipset developed exclusively by ABIT computer.

**NOTE:** The decimal point lights up when executing the AC2005 POST action.

See Appendix for both AWARD and AC2005 POST Code definition.

2-18 Chapter 2

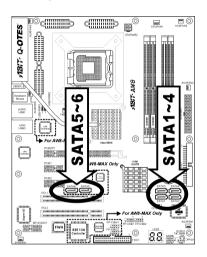

#### (12). Serial ATA Connectors

These connectors are provided to attach one Serial ATA device at each channel via Serial ATA cable.

This motherboard provides RAID 0, RAID 1, RAID5 and RAID10 configuration for Serial ATA hard drives through the Intel ICH7R chipset. You may configure a disk array by the Intel Matrix Storage Technology RAID Driver option ROM utility.

For model "AW8-MAX", two additional SATA connectors (SATA5 and SATA6 hard drives through the Silicon Image chipset) are provided. You may configure a disk array by the Sil3132 SATA Driver option ROM utility.

For more information on how to configure the function mode for SATA, please refer to the item "On-Chip SATA Mode" in the BIOS menu of "On-Chip IDE Device".

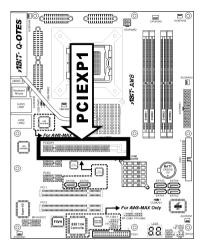

## (13). PCI Express x16 Slot

This slot is used to attach the next generation of graphics architecture.

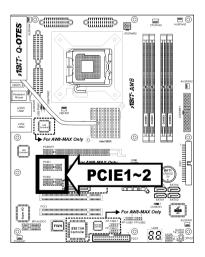

## (14). PCI Express x1 Slots

These slots are used to attach the next generation of I/O architecture.

2-20 Chapter 2

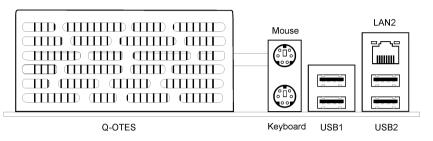

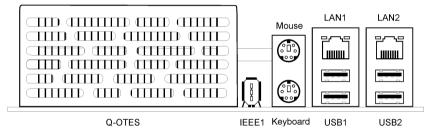

#### (15). Back Panel Connectors

#### AW8:

#### AW8-MAX:

- **IEEE1:** Connects to devices of IEEE1394 protocol. (For model AW8-MAX only)

- Mouse: Connects to PS/2 mouse.

- Keyboard: Connects to PS/2 keyboard.

- LAN1: Connects to Local Area Network (For model AW8-MAX only).

- LAN2: Connects to Local Area Network.

- USB1/USB2: Connects to USB devices such as scanner, digital speakers, monitor, mouse, keyboard, hub, digital camera, joystick etc.

BIOS Setup 3-1

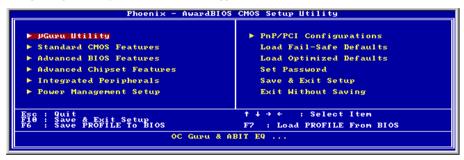

# **Chapter 3. BIOS Setup**

This motherboard provides a programmable EEPROM that you can update the BIOS utility. The BIOS (Basic Input/Output System) is a program that deals with the basic level of communication between processor and peripherals. Use the BIOS Setup program only when installing motherboard, reconfiguring system, or prompted to "Run Setup". This chapter explains the Setup Utility of BIOS utility.

After powering up the system, the BIOS message appears on the screen, the memory count begins, and then the following message appears on the screen:

#### PRESS DEL TO ENTER SETUP

If this message disappears before you respond, restart the system by pressing <Ctrl> + <Alt> + <Del> keys, or by pressing the Reset button on computer chassis. Only when it failed by these two methods can you restart the system by powering it off and then back on.

After pressing <Del> key, the main menu screen appears.

NOTE: In order to increase system stability and performance, our engineering staffs are constantly improving the BIOS menu. The BIOS setup screens and descriptions illustrated in this manual are for your reference only, and may not completely match with what you see on your screen.

3-2 Chapter 3

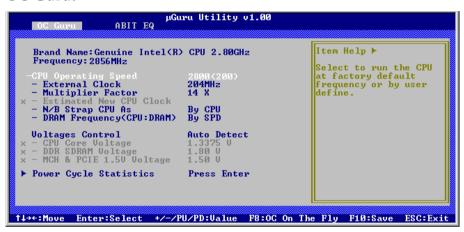

# 3-1. μGuru<sup>TM</sup> Utility

There are two setup menus in this  $\mu$ Guru utility. You may switch between these two by clicking the left or right arrow key on keyboard:

#### OC Guru:

#### **Brand Name:**

This item displays the CPU model name installed on this motherboard.

#### Frequency:

This item displays the processor speed of the CPU installed on this motherboard.

#### **CPU Operating Speed:**

This item displays the CPU operating speed according to the type and speed of your CPU. You can also select the [User Define] option to enter the manual option.

#### **User Define:**

**WARNING:** The wrong settings of the multiplier and external clock in certain circumstances may cause CPU damage. Setting the working frequency higher than the PCI chipset or processor specs, may cause abnormal memory module functioning, system hangs, hard disk drive data lose, abnormal functioning of the VGA card, or abnormal functioning with other add-on cards. Using non-specification settings for your CPU is not the intention of this explanation. These should be used for engineering testing, not for normal applications.

There will be no guaranty for the settings beyond specification, any damage of any component on this motherboard or peripherals result therein is not our responsibility.

BIOS Setup 3-3

#### \* External Clock:

This item selects the external clock frequency. Due to the specification limit of the CPU you installed, the speed you set over its standard bus speed is supported, but not guaranteed.

#### **\*** Multiplier Factor:

This item displays the multiplier factor for the CPU you installed.

#### **★** Estimated New CPU Clock:

This item displays an estimated CPU processor speed.

#### **☀** N/B Strap CPU As:

This item sets the external hardware reset strap assigned to MCH (Memory Controller Hub).

To set this option manually:

- Select [PSB533] for CPU of 133MHz FSB frequency.

- Select [PSB800] for CPU of 200MHz FSB frequency.

- Select [PSB1066] for CPU of 266MHz FSB frequency.

#### **\*** DRAM Frequency:

This item determines the DRAM frequency.

#### **Voltages Control:**

This option allows you to switch between the default and user-defined voltages. Leave this setting to default unless the current voltage setting cannot be detected or is not correct. The option "User Define" enables you to select the following voltages manually.

#### **\*** CPU Core Voltage:

This item selects the CPU core voltage.

#### **☀** DDR SDRAM Voltage:

This item selects the voltage for DRAM slot.

#### **\*** MCH & PCIE 1.5V Voltage:

This item selects the voltage for MCH & PCIE slot.

3-4 Chapter 3

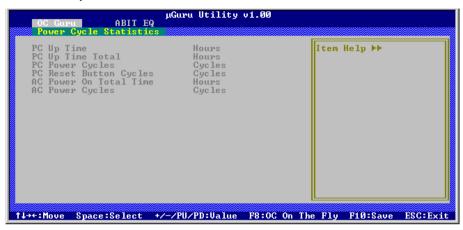

#### **Power Cycle Statistics:**

Click <Enter> key to enter its submenu:

These items display the power cycle statistics for each element.

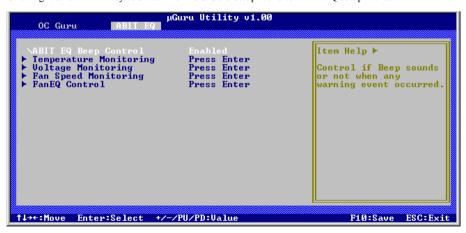

# **ABIT EQ:**

Click right-arrow <->> key to switch from OC Guru setup menu to ABIT EQ setup menu:

#### **ABIT EQ Beep Control:**

This item allows you to enable or disable ABIT EQ Beep Control function.

BIOS Setup 3-5

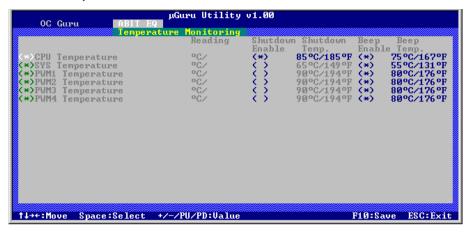

# **\\$** Temperature Monitoring:

Click <Enter> key to enter its submenu:

#### **CPU Temperature/System Temperature/PWM Temperature:**

These items display the temperature of CPU, System, and Power Module.

#### \* Shutdown Enable:

Use <Space> key to enable system shutdown function. If the CPU/System/PWM's temperature exceeds the shutdown temperature limit, the system would shutdown automatically.

#### \* Shutdown Temp.:

This items sets the temperature that would shutdown the system automatically in order to prevent system overheats.

#### **☀** Beep Enable:

Use <Space> key to enable warning beeps function. Once the system has detected that the CPU/System/PWM's temperature exceeded the beep temperature limit, warning beeps will sound.

#### ★ Beep Temp.:

This item selects the warning temperature limit.

**NOTE:** The shutdown temperature must be set above the warning temperature.

3-6 Chapter 3

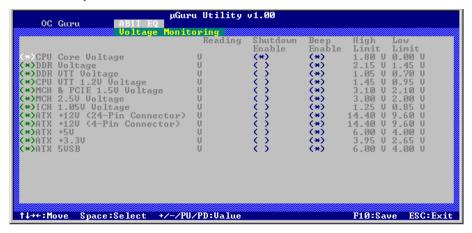

# **Voltage Monitoring:**

Click <Enter> key to enter its submenu:

#### All Voltages:

These items display the voltage of each element.

#### \* Shutdown Enable:

Use <Space> key to enable system shutdown function. If the voltage of corresponding element is higher/lower than the high/low limit, the system would automatically shutdown.

#### **☀** Beep Enable:

Use <Space> key to enable warning beeps function. If the voltage of corresponding element is higher/lower than the high/low limit, warning beeps will sound.

#### **☀** High/Low Limit:

These items set the high and low voltage limit.

**NOTE:** The value of high limit must be set above the one of low limit.

BIOS Setup 3-7

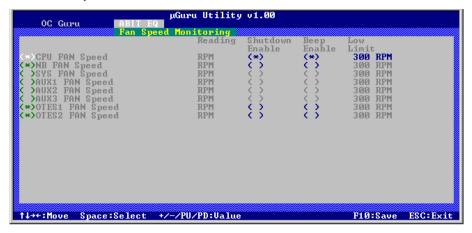

# **Solution** Fan Speed Monitoring:

Click <Enter> key to enter its submenu:

#### CPU/NB/SYS/AUX/OTES FAN Speed:

These items display the speed of the fans connected to CPU, NB, SYS, AUX1 and AUX2 FAN headers.

#### \* Shutdown Enable:

Use <Space> key to enable system shutdown function. Once the system has detected that the fan speed is lower than the low limit value, system will shutdown automatically.

#### **☀** Beep Enable:

Use <Space> key to enable warning beeps function. If the fan speed is lower than the low limit value, warning beeps will sound.

#### \* Low Limit:

These items set the low limit of fan speed.

**NOTE:** Only the fans with 3-pin plugs provide the speed monitoring function.

3-8 Chapter 3

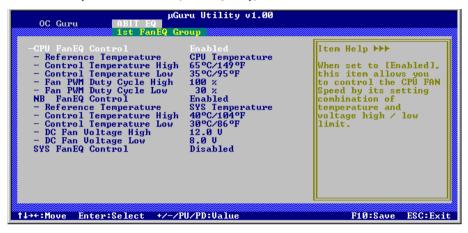

### **♦** FanEQ Control:

Click <Enter> key to enter its submenu (1st FanEQ Group):

#### CPU/NB/SYS FanEQ Control:

When set to [Enabled], these items control the CPU, NB, and/or SYS fan speed by the following setting combinations.

#### **\*** Reference Temperature:

This item selects the reference point for taking temperature among the available options of CPU, SYS, and PWM Temperature, but there is only one "CPU Temperature" item to choose for the "CPU FanEQ Control".

#### **\*** Control Temperature High/Low:

These items set the high and low temperature limit that you want to do the fan speed control.

#### **★** Fan PWM Duty Cycle High/Low:

These items set the high and low limit of PWM duty cycle that you want to provide the fan with.

#### **☀** DC Fan Voltage High/Low:

These items set the high and low voltage limit that you want to provide the fan with.

NOTE: The value of high limit must be set above the one of low limit.

BIOS Setup 3-9

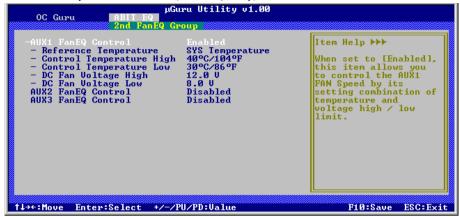

Click <Enter> key to enter its submenu (2<sup>nd</sup> FanEQ Group):

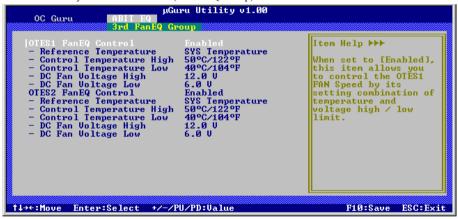

Click <Enter> key to enter its submenu (3<sup>rd</sup> FanEQ Group):

## **AUX/OTES FanEQ Control:**

When set to [Enabled], these items control the AUX/OTES fan speed by the following setting combinations.

#### **\*** Reference Temperature:

This item selects the reference point for taking temperature among the available options of CPU, SYS, and PWM Temperature, but there is only one "CPU Temperature" item to choose for the "CPU FanEQ Control".

## **\*** Control Temperature High/Low:

These items set the high and low temperature limit that you want to do the fan speed control.

## **★** DC Fan Voltage High/Low:

These items set the high and low voltage limit that you want to provide the fan with.

NOTE: The value of high limit must be set above the one of low limit.

3-10 Chapter 3

## 3-2. Standard CMOS Features

This section contains the basic configuration parameters of the BIOS. These parameters include date, hour, VGA card, FDD, and HDD settings.

## Date (mm:dd:yy):

This item sets the date you specify (usually the current date) in the format of [Month], [Date], and [Year].

## Time (hh:mm:ss):

This item sets the time you specify (usually the current time) in the format of [Hour], [Minute], and [Second].

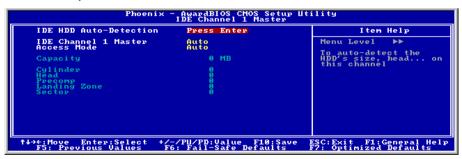

# ☼ IDE Channel 1 Master/Slave, IDE Channel 2 Master/Slave, IDE Channel 3 Master/Slave, IDE Channel 4 Master/Slave:

Click <Enter> key to enter its submenu:

**NOTE:** The items "IDE Channel 3 Master/Slave" and "IDE Channel 4 Master/Slave" appear only when the item "On-Chip SATA" in the "On-Chip IDE Device" menu is set to [Enhanced Mode], or set to [Auto] when SATA ports are connected with devices.

BIOS Setup 3-11

#### **IDE HDD Auto-Detection:**

This item allows you to detect the parameters of IDE drives by pressing <Enter> key. The parameters will be shown on the screen automatically.

## IDE Channel 1 Master/Slave, IDE Channel 2 Master/Slave, Extended IDE Drive:

When set to [Auto], the BIOS will automatically check what kind of IDE drive you are using. If you want to define your own drive by yourself, set it to [Manual] and make sure you fully understand the meaning of the parameters. Please refer to the instruction manual provided by the device's manufacturer to get the setting right.

## **Access Mode:**

This item selects the mode to access your IDE devices. Leave this item to its default [Auto] setting to detect the access mode of your HDD automatically.

## Capacity:

This item displays the approximate capacity of the disk drive. Usually the size is slightly greater than the size of a formatted disk given by a disk-checking program.

## Cylinder:

This item configures the numbers of cylinders.

## Head:

This item configures the numbers of read/write heads.

## Precomp:

This item displays the number of cylinders at which to change the write timing.

## Landing Zone:

This item displays the number of cylinders specified as the landing zone for the read/write heads.

#### Sector:

This item configures the numbers of sectors per track.

## **Back to Standard CMOS Features Setup Menu:**

#### Drive A & Drive B:

This item sets the type of floppy drives (usually only Drive A) installed.

## Floppy 3 Mode Support:

This item allows you to use "3 Mode Floppy Drive" in Japanese computer systems by selecting drive A, B, or both. Leave this item to its default [Disabled] setting if you are not using this Japanese standard floppy drive.

3-12 Chapter 3

## Halt On:

This item determines whether the system stops if an error is detected during system boot-up.

[All Errors]: The system-boot will stop whenever the BIOS detect a non-fatal error.

[No Errors]: The system-boot will not stop for any error detected.

[All, But Keyboard]: The system-boot will stop for all errors except a keyboard error.

[All, But Diskette]: The system-boot will stop for all errors except a diskette error.

[All, But Disk/Key]: The system-boot will stop for all errors except a diskette or keyboard error.

## **Base Memory:**

This item displays the amount of base memory installed in the system. The value of the base memory is typically 640K for system with 640K or more memory size installed on the motherboard.

## **Extended Memory:**

This item displays the amount of extended memory detected during system boot-up.

## **Total Memory:**

This item displays the total memory available in the system.

## 3-3. Advanced BIOS Features

```

Phoenix - huardBIOS CMOS Setup Utility

Advanced BIOS Features

CPU L3 Cache

Hyper-Threading Technology Enabled

Unick Power on Self Test Enabled

Figure First Boot Priority Press Enter

First Boot Device Flore

First Boot Device Flore

First Boot Device Flore

First Boot Device Flore

Boot Other Device IDE CROM

Boot Other Device IDS Sabled

Swap Flore

Boot Security Option

Security Option

MPS Version Ctrl For OS 1.4

Report No FDD For OS No

Delay IDE Initial (Secs) Pull Screen LOGO Show Disabled

↑++: Move Enter: Select +/-/PU/PD: Value F10: Save ESC: Exit F1: General Help

F5: Previous Values F6: Fail-Safe Defaults

```

## CPU L3 Cache:

This item is used to enable the L3 cache (default setting), and appears only for certain CPU (Intel Pentium 4 processor with HT Technology Extreme Edition) that possesses L3 cache.

## **Hyper-Threading Technology**

This item is used to enable the functionality of the processor with Hyper-Threading Technology and will appear only when using such processor.

The Hyper-Threading Technology helps your PC work more efficiently by maximizing processor resources and enabling a single processor to run two separate threads of software simultaneously, bringing forth greater performance and system responsiveness when running multiple applications at once.

BIOS Setup 3-13

## **Quick Power On Self Test:**

When set to [Enabled], this item speeds up the Power On Self Test (POST) after powering on the system. The BIOS shorten or skip some check during the POST.

## **♥** CPU Feature:

Click <Enter> key to enter its submenu:

```

Phoenix - AwardBIOS CMOS Setup Utility

CPU Feature

Delay Prior to Thermal 16 Min

Thermal Management 1 Thermal Monitor 1

Thermal Management 1 Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monitor 1

Thermal Monit

```

## **Delay Prior to Thermal:**

This item selects the delay time before thermal activation.

## Thermal Management

This item selects the type of thermal monitoring.

#### \* TM2 Bus Ratio

This item represents the frequency (bus ratio) of the throttled performance state that will be initiated when the on-die sensor goes from not hot to hot).

## **☀** TM2 Bus VID

This item represents the voltage of the throttled performance state that will be initiated when the on-die sensor goes from not hot to hot.

## Limit CPUID MaxVal

When set to [Enabled], this item limits the CPUID maximum value to 3, which is usually required for older OS like Windows NT4.0.

Leave this item to its default [Disabled] settings for OS like Windows XP.

## C1E Function

This item appears only for certain processors with the C1E (Enhanced Halt State) Function. When set to [Enabled], the processor will further reduce the total power consumption.

## **Execute Disable Bit**

This item appears only for certain processors with the Execute Disable Bit (XD bit) feature. When set to [Enabled], this item allows the processor to prevent data pages from being used by malicious software to execute code and provide memory protection.

3-14 Chapter 3

#### **EIST Function**

This item appears only for certain processors with the EIST (Enhanced Intel SpeedStep Technology) Function. When set to [Enabled], EIST will dynamically switch between multiple frequency and voltage points to optimize the power and performance balance of the processor and system based on demand.

## **Back to Advanced BIOS Features Setup Menu:**

## **Hard Disk Boot Priority:**

This item selects the hard disks booting priority. By pressing <Enter> key, you can enter its submenu where the hard disks detected can be selected for the booting sequence to boot up system.

This item functions only when there is the option of [Hard Disk] in any one of the First/Second/Third Boot Device items.

## First Boot Device / Second Boot Device / Third Boot Device / Boot Other Device:

Select the drive to boot first, second and third in the [First Boot Device], [Second Boot Device], and [Third Boot Device] items respectively. The BIOS will boot the operating system according to the sequence of the drive selected. Set [Boot Other Device] to [Enabled] if you wish to boot from another device other than these three items.

## **Swap Floppy Drive:**

When set to [Enabled], and the system is booting from the floppy drive, the system will boot from drive B instead of the regular drive A. There must be two floppy drives connected in the system to use this function.

## **Boot Up Floppy Seek:**

When set to [Enabled], the BIOS will check whether the floppy disk drive is installed or not.

## **Boot Up NumLock Status:**

This item determines the default state of the numeric keypad at system booting up.

**[On]:** The numeric keypad functions as number keys.

**[Off]:** The numeric keypad functions as arrow keys.

## **Security Option:**

This item determines when the system will prompt for password - every time the system boots or only when enters the BIOS setup.

[Setup]: The password is required only when accessing the BIOS Setup.

[System]: The password is required each time the computer boots up.

**NOTE:** Don't forget your password. If you forget the password, you will have to open the computer case and clear all information in the CMOS before you can start up the system. But by doing this, you will have to reset all previously set options.

## MPS Version Ctrl For OS:

This item specifies which version of MPS (Multi-Processor Specification) this motherboard will use. Leave this item to its default setting.

#### AW8 Series

BIOS Setup 3-15

## Report No FDD For OS:

When set to [Yes], this item allows you to run some older operating system without floppy disk drive. Leave this item to its default setting.

## **Delay IDE Initial (Secs):**

This item allows the BIOS to support some old or special IDE devices by prolonging this delay time. A larger value will give more delay time to the device for which to initialize and to prepare for activation.

## Full Screen LOGO Show:

This item determines to show the full screen logo when booting.

# 3-4. Advanced Chipset Features

```

Phoenix - AwardBIOS CMOS Setup Utility

Advanced Chipset Features

DRAM Timing Selectable By SPD Item Help

- CAS Latency Time Auto

- RASH to CASH Delay Auto

- RASH Precharge (tRAS) Auto

- RASH Precharge (tRAS) Auto

- Memory Hole At 15M-16M Disabled

- PCI Express Root Port Func Press Enter

- DRAM Data Integrity Mode BCC

- DEG Force XI Init Display First PCI Slot

Timit Display First PCI Slot

T++: Move Enter: Select +/-/PU/PD: Value F18: Save ESC: Exit F1: General Help

- F5: Previous Values F6: Fail-Safe Defaults F7: Optimized Defaults

```

## **DRAM Timing Selectable:**

This item sets the optimal timings for the following four items, depending on the memory module you are using. The default setting "By SPD" configures these four items by reading the contents in the SPD (Serial Presence Detect) device. The EEPROM on the memory module stores critical parameter information about the module, such as memory type, size, speed, voltage interface, and module banks.

## **\*** CAS Latency Time:

This item controls the latency between the DRAM read command and the time that the data becomes actually available.

## \* RAS# to CAS# Delay

This item controls the latency between the DRAM active command and the read/write command.

## \* RAS# Precharge:

This item controls the idle clocks after issuing a precharge command to the DRAM.

## **☀** Precharge Delay (tRAS):

This item controls the number of DRAM clocks used for the DRAM parameters.

3-16 Chapter 3

## Memory Hole At 15M-16M:

When set to [Enabled], the memory address space at 15M-16M will be reserved for ISA expansion cards that specifically requires this setting. This makes the memory from 15MB and up unavailable to the system. Leave this item to its default setting.

## **PCI Express Root Port Func:**

Click <Enter> key to enter its submenu:

```

Phoenix - AwardBIOS CMOS Setup Utility

PCI Express Root Port Func

PCI Express Slot 1 Auto Item Help

PCI Express Slot 2 Auto

PCI-E Compliancy Mode v1.8a

Menu Level >>

T++: Move Enter: Select +/-/PU/PD: Value F10: Save ESC: Exit F1: General Help

F5: Previous Values F6: Fail-Safe Defaults F7: Optimized Defaults

```

## PCI Express Slot 1 / PCI Express Slot 2:

This option enables or disables the PCI Express port function.

## **PCI-E Compliancy Mode:**

This item selects the mode for PCI Express add-on card.

## **Back to Advanced Chipset Features Setup Menu:**

## **DRAM Data Integrity Mode**

This item selects the type of DRAM in your system. ECC is "Error Checking and Correction". Choose the ECC option only when your memory is ECC type.

## PEG Force X1

When set to [Enabled], this item forces the PEG port down to x1 mode.

## **Init Display First:**

This item selects whether to initiates from "PCI Express Slot" or "PCI Slot" first when system boots up.

BIOS Setup 3-17

## 3-5. Integrated Peripherals

## **On-Chip IDE Device:**

Click <Enter> key to enter its submenu:

## **IDE Bus Master:**

This option enables or disables the IDE bus mastering capability under the DOS environment.

## **On-Chip IDE-1 Controller:**

This item selects whether to enable or disable the IDE-1 controller.

## **On-Chip SATA Mode:**

This item determines the mode for on-chip Serial ATA.

[IDE]: The on-chip Serial ATA served as IDE mode.

[RAID]: The on-chip Serial ATA served as RAID mode.

[AHCI]: The on-chip Serial ATA served as AHCI (Advanced Host Controller Interface) mode for advanced performance and usability.

**NOTE:** The [RAID] option is only available when the item "On-Chip SATA" is set to [Enhanced Mode].

3-18 Chapter 3

## On-Chip SATA:

This item determines the function for on-chip Serial ATA.

[Disabled]: Disable the Serial ATA controller.

[Auto]: Allows the Serial ATA controller to be arranged by BIOS automatically.

[Combined Mode]: Parallel ATA and Serial ATA are combined together. Supports up to 4 IDE drives.

[Enhanced Mode]: Enable both Parallel ATA and Serial ATA. Supports up to 6 IDE drives.

[SATA Only]: The SATA is operating in legacy mode.

**NOTE:** This option is configurable only when the item [On-Chip SATA Mode] is set to [IDE].

| Mode      | IDE<br>Channel<br>1 Master | IDE<br>Channel<br>1 Slave | IDE<br>Channel<br>2 Master | IDE<br>Channel<br>2 Slave | IDE<br>Channel<br>3 Master | IDE<br>Channel<br>3 Slave | IDE<br>Channel<br>4 Master | IDE<br>Channel<br>4 Slave |

|-----------|----------------------------|---------------------------|----------------------------|---------------------------|----------------------------|---------------------------|----------------------------|---------------------------|

| Enhanced  | IDE1<br>Master             | IDE1<br>Slave             | None                       | None                      | SATA1                      | SATA3                     | SATA2                      | SATA4                     |

| Combined  | IDE1<br>Master             | IDE1<br>Slave             | SATA2                      | SATA4                     | None                       | None                      | None                       | None                      |

| SATA Only | SATA1                      | SATA3                     | SATA2                      | SATA4                     | None                       | None                      | None                       | None                      |

NOTE: The option [Enhanced Mode] does not support the Windows 98/ME operation system.

## **SATA PORT Speed Settings:**

This item selects the mode for SATA PORT.

#### **\*** PATA IDE Mode:

This item determines the function mode for "IDE1" connector.

[IDE-1]: "IDE1" connector served as [Primary Master] and [Primary Slave] channel. "SATA2" and "SATA4" connector served as [Secondary Master] and [Secondary Slave] channel. The remaining "SATA1" and "SATA3" connectors are disabled.

[IDE-2]: "IDE1" connector served as [Secondary Master] and [Secondary Slave] channel. "SATA1" and "SATA3" connector served as [Primary Master] and [Primary Slave] channel. The remaining "SATA2" and "SATA4" connectors are disabled.

Refer to the following table for the relationships between IDE and SATA ports.

| PATA IDE<br>Mode | IDE<br>Channel<br>1 Master | IDE<br>Channel<br>1 Slave | IDE<br>Channel<br>2 Master |               | IDE<br>Channel<br>3 Master | IDE<br>Channel<br>3 Slave | IDE<br>Channel<br>4 Master | IDE<br>Channel<br>4 Slave |

|------------------|----------------------------|---------------------------|----------------------------|---------------|----------------------------|---------------------------|----------------------------|---------------------------|

| Primary          | IDE1<br>Master             | IDE1<br>Slave             | SATA2                      | SATA4         | None                       | None                      | None                       | None                      |

| Secondary        | SATA1                      | SATA3                     | IDE1<br>Master             | IDE1<br>Slave | None                       | None                      | None                       | None                      |

**NOTE:** This option is configurable only when the item [On-Chip SATA] is set to [Combined Mode].

BIOS Setup 3-19

## \* SATA Mode:

This item displays the variety modes for SATA Mode.

## **On-Chip PCI Device:**

Click <Enter> key to enter its submenu:

## **On-Chip USB Controller:**

This option enables or disables the USB controller.

## **\*** USB 2.0 Controller:

This option enables or disables the USB 2.0 controller.

## **\*** USB Keyboard Support:

This item allows you to select [BIOS] for using USB keyboard in DOS environment, or [OS] in OS environment.

#### **\*** USB Mouse Support:

This item allows you to select [BIOS] for using USB mouse in DOS environment, or [OS] in OS environment.

## **On-Chip Audio Controller:**

This option enables or disables the audio controller.

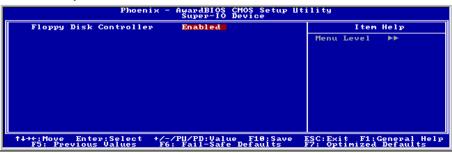

## Super-IO Device:

Click <Enter> key to enter its submenu:

3-20 Chapter 3

## Floppy Disk Controller

This option enables or disables the floppy disk controller.

## **Onboard PCI Device:**

Click <Enter> key to enter its submenu:

```

Phoenix - AwardBIOS CMOS Setup Utility

Onboard PCI Device

IEEE 1394 Controller

Serial ATA Controller Enabled

- SATA RAID ROM

Network 1 Controller Enabled

Network 2 Controller Enabled

- Invoke Boot Agent Disabled

Network 2 Controller Enabled

- Invoke Boot Agent Disabled

- Invoke Boot Agent Disabled

- The Figure Enabled

- The Figure Enabled Bisabled

**The Figure Enter: Select +/-/FU/PD: Value F10: Save ESC: Exit F1: General Help

F5: Previous Values F6: Fail-Safe Defaults F7: Optimized Defaults

```

## **IEEE 1394 Controller:**

This option enables or disables the IEEE 1394 controller.

## Serial ATA Controller

This option enables or disables the Serial ATA controller.

## \* SATA RAID ROM

This item allows you to use the boot ROM of on-chip Serial ATA RAID to boot-up system.

## Network 1/ Network 2 Controller:

This option enables or disables the LAN controller.

## **☀** Invoke Boot Agent:

This item allows you to use the boot ROM (instead of a disk drive) to boot-up the system and access the local area network directly.

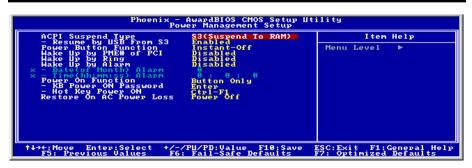

# 3-6. Power Management Setup

BIOS Setup 3-21

## **ACPI Suspend Type:**

This item selects the type of Suspend mode.

[S1(PowerOn-Suspend)]: Enables the Power On Suspend function.

[S3(Suspend-To-RAM)]: Enables the Suspend to RAM function.

## \* Resume by USB From S3:

When set to [Enabled], this item allows you to use a USB device to wake up a system that is in the S3 (STR - Suspend To RAM) state. This item can be configured only if the item "ACPI Suspend Type" is set to [S3(STR)].

#### **Power Button Function:**

This item selects the method of powering off your system:

[Delay 4 Sec.]: Pushing the power button for more than 4 seconds will power off the system. This will prevent the system from powering off in case you accidentally hit or pushed the power button.

[Instant-Off]: Pressing and then releasing the power button at once will immediately power off the system.

## WakeUp by PME# of PCI:

When set to [Enabled], access to the onboard LAN or a PCI card such as a modem or LAN card will cause the system to wake up. The PCI card must support the wake up function.

## WakeUp by Ring:

Two options are available: Disabled or Enabled. The default setting is *Disabled*. When set to *Enabled*, any event affecting from Modem Ring will awaken a system that has powered down.

## WakeUp by Alarm:

When set to [Enabled], you can set the date and time you would like the Soft-Off PC to power-on in the "Date (of Month) Alarm" and "Time (hh:mm:ss) Alarm" items. However, if the system is being accessed by incoming calls or the network (Resume On Ring/LAN) prior to the date and time set in these items, the system will give priority to the incoming calls or network instead.

## **☀** Date (of Month) Alarm

[0]: This option power-on the system everyday according to the time set in the "Time (hh:mm:ss) Alarm" item.

[1-31]: This option selects a date you would like the system to power-on. The system will power-on on the date set, and the time set in the "Time (hh:mm:ss) Alarm" item.

## \* Time (hh:mm:ss) Alarm

This item sets the time you would like the system to power-on.

3-22 Chapter 3

#### **Power On Function**

This item selects the way you want your system to power on.

[Password]: Use a password to power on the system, select this option then press <Enter>. Enter your password. You can enter up to 5 characters. Type in exactly the same password to confirm, and then press <Enter>.

[Hot KEY]: Use any of the function keys between <F1> to <F12> to power on the system.

[Mouse Left]: Double click the mouse left button to power on the system.

[Mouse Right]: Double click the mouse right button to power on the system.

[Any KEY]: Use any keyboard keys to power on the system.

**[Button Only]:** Use only the power button to power on the system.

**[Keyboard 98]:** Use the power-on button on the "Keyboard 98" compatible keyboard to power on the system.

**NOTE:** To enable this "Power On" function, the wake-up header of [USB-PWR1] and [USB-PWR2] must be set to [Enabled] position. Please refer to the configuration of "Wake-up Header" [USB-PWR1] and [USB-PWR2] in section 2-4, chapter 2.

**NOTE:** The mouse wake up function can only be used with the PS/2 mouse, not with the COM port or USB type. Some PS/2 mice cannot wake up the system because of compatible problems. If the specs of your keyboard are too old, it may fail to power on.

#### **★** KB Power ON Password:

This item sets the password required in order to power on your computer.

**NOTE:** Do not forget your password, or you will have to clear the CMOS and reset all parameters in order to utilize this function again.

#### **\*** Hot Kev Power ON:

This item powers on the system by pressing <Ctrl> key plus one of each function key (<F1 $> \sim <$ F12>) simultaneously.

## Restore On AC Power Loss

This item selects the system action after an AC power failure.

**[Power Off]:** When power returns after an AC power failure, the system's power remains off. You must press the Power button to power-on the system.

[Power On]: When power returns after an AC power failure, the system's power will be powered on automatically.

[Last State]: When power returns after an AC power failure, the system will return to the state where you left off before power failure occurs. If the system's power is off when AC power failure occurs, it will remain off when power returns. If the system's power is on when AC power failure occurs, the system will power-on when power returns.

BIOS Setup 3-23

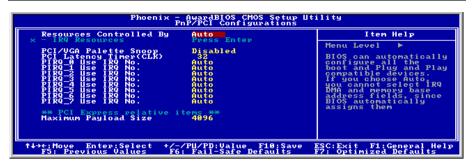

## 3-7. PnP/PCI Configurations

## **Resources Controlled By:**

This item configures all of the boot and Plug-and-Play compatible devices.

[Auto(ESCD)]: The system will automatically detect the settings.

[Manual]: Choose the specific IRQ resources in the "IRQ Resources" menu.

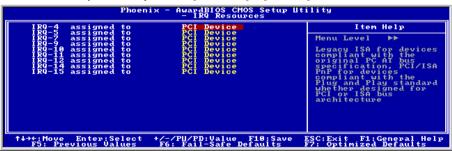

## **\*** IRO Resources:

Click <Enter> key to enter its submenu:

This item sets each system interrupt to either [PCI Device] or [Reserved].

## PCI/VGA Palette Snoop:

This item determines whether the MPEG ISA/VESA VGA cards can work with PCI/VGA or not.

[Enabled]: MPEG ISA/VESA VGA cards work with PCI/VGA.

[Disabled]: MPEG ISA/VESA VGA cards do not work with PCI/VGA.

## PIRQ 0 Use IRQ No. ~ PIRQ 7 Use IRQ No.:

This item specifies the IRQ number manually or automatically for the devices installed on PCI slots.

## Maximum Payload Size

This item sets the maximum TLP payload size for the PCI Express devices.

3-24 Chapter 3

## 3-8. Load Fail-Safe Defaults

This option loads the BIOS default values for the most stable, minimal-performance system operations.

## 3-9. Load Optimized Defaults

This option loads the BIOS default values that are factory settings for optimal-performance system operations.

## 3-10. Set Password

This option protects the BIOS configuration or restricts access to the computer itself.

## 3-11. Save & Exit Setup

This option saves your selections and exits the BIOS setup menu.

## 3-12. Exit Without Saving

This option exits the BIOS setup menu without saving any changes.

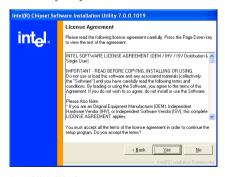

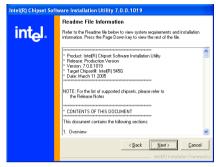

# **Appendix A. Install Intel Chipset Software Installation Utility**

**NOTE:** Please install this Intel Chipset driver first after having installed the Windows operating system.

The installation procedures and screen shots in this section are based on Windows XP operating system. For those of other OS, please follow its on-screen instructions

Insert the Driver & Utility CD into CD-ROM drive. It should execute the installation program automatically. If not, double-click the execution file at the main directory of this CD to enter the installation menu.

After entering the installation menu, move your curser to [Drivers] tab. Click [Intel Chipset Software Installation Utility]. The following screen appears.

Click [Next].

2. Click [Yes].

3. Click [Next].

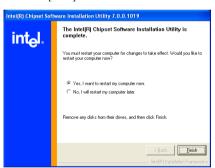

**4.** Choose [Yes, I want to restart my computer now.], and click [Finish] to complete setup.

A-2 Appendix A

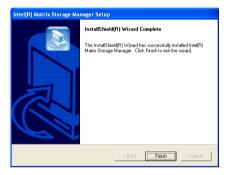

# Appendix B. Install Intel Matrix Storage Technology RAID Driver

The installation procedures and screen shots in this section are based on Windows XP operating system. For those of other OS, please follow its on-screen instructions.

Insert the Driver & Utility CD into CD-ROM drive. It should execute the installation program automatically. If not, double-click the execution file at the main directory of this CD to enter the installation menu.

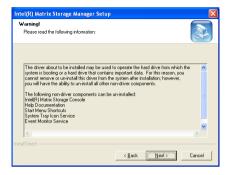

After entering the installation menu, move your curser to [Drivers] tab. Click [Intel Matrix Storage Technology RAID Driver]. The following screen appears.

**NOTE:** To install this program, you have to enable the item "RAID Function" first in the BIOS menu of "On-Chip SATA Mode".

1. Click [Next].

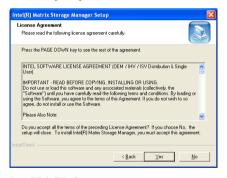

2. Click [Next].

Click [Yes].

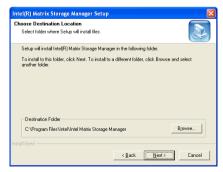

Click [Next].

B-2 Appendix B

## 5. Click [Next].

6. Click [Finish] to complete setup.

Install Audio Driver C-1

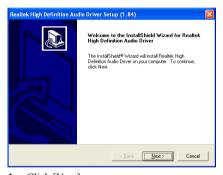

# Appendix C. Install Audio Driver

The installation procedures and screen shots in this section are based on Windows XP operating system. For those of other OS, please follow its on-screen instruction.

Insert the Driver & Utility CD into CD-ROM drive, it should execute the installation program automatically. If not, double-click the execution file at the main directory of this CD to enter the installation menu.

After entering the installation menu, move your curser to [Drivers] tab. Click [Audio Driver]. The following screen appears.

1. Click [Next].

**2.** Choose [Yes, I want to restart my computer now.], and click [Finish] to complete setup.

C-2 Appendix C

Install BCM LAN Driver D-1

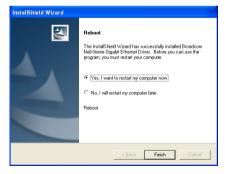

# Appendix D. Install BCM LAN Driver

The installation procedures and screen shots in this section are based on Windows XP operating system. For those of other OS, please follow its on-screen instruction.

Insert the Driver & Utility CD into CD-ROM drive, it should execute the installation program automatically. If not, double-click the execution file at the main directory of this CD to enter the installation menu.

After entering the installation menu, move your curser to [Drivers] tab. Click [BCM LAN Driver]. The following screen appears.

1. Click [Next].

**2.** Choose [Yes, I want to restart my computer now.], and click [Finish] to complete setup.

D-2 Appendix D

# Appendix E. Install Sil3132 SATA Driver (AW8-MAX)

The installation procedures and screen shots in this section are based on Windows XP operating system. For those of other OS, please follow its on-screen instruction.

Insert the Driver & Utility CD into CD-ROM drive, it should execute the installation program automatically. If not, double-click the execution file at the main directory of this CD to enter the installation menu.

After entering the installation menu, move your curser to [Drivers] tab. Click [Sil3132 SATA Driver]. The following screen appears.

1. Click [Next].

2. Click [No].

3. Click [OK].

4. Click [Next].

5. Click [Next].

**6.** Click [Continue Anyway].

E-2 Appendix E

7. Choose [I accept the terms in the license agreement], and click [Next].

8. Click [Next].

9. Click [Finish].

10. Click [Finish] to complete setup..

Install USB 2.0 Driver F-1

# Appendix F. Install USB 2.0 Driver

**NOTE:** The "USB 2.0 Driver" packed in the "Driver & Utility CD" is currently available for Windows 9x and ME only. To install this driver for Windows XP or Windows 2000, you have to download their latest service pack first from Microsoft's web site.

F-2 Appendix F

# Appendix G. Install ABIT µGuru Utility

The installation procedures and screen shots in this section are based on Windows XP operating system. For those of other OS, please follow its on-screen instruction

Insert the Driver & Utility CD into CD-ROM drive, it should execute the installation program automatically. If not, double-click the execution file at the main directory of this CD to enter the installation menu.

After entering the installation menu, move your curser to [ABIT Utility] tab. Click [ABIT Guru]. The following screen appears.

1. Click [Next].

2. Click [Next].

**3.** Choose [Yes, I want to restart my computer now.], and click [Finish] to complete setup.

G-2 Appendix G

# **Appendix H. POST Code Definition**

## **AWARD POST Code Definitions**

| CF Test CMOS R/W functionality  Early chipset initialization: -Disable shadow RAM -Disable L2 cache (socket 7 or below) -Program basic chipset registers  Detect memory -Auto-detection of DRAM size, type and ECC -Auto-detection of L2 cache (socket 7 or below)  C3 Expand compressed BIOS code to DRAM  C5 Call chipset hook to copy BIOS back to E000 & F000 shadow RAM  01 Expand the Xgroup codes locating in physical address 1000:0  03 Initial Superio_Early_Init switch  05 1. Blank out screen 2. Clear CMOS error flag  1. Clear 8042 interface 2. Initialize 8042 self-test  08 1. Test special keyboard controller for Winbond 977 series Super I/O chips 2. Enable keyboard interface 1. Disable PS/2 mouse interface (optional) 3. Reset keyboard for Winbond 977 series Super I/O chips  Test F000h segment shadow to see whether it is R/W-able or not. If test fails, keep beeping the speaker  10 Auto detect flash type to load appropriate flash R/W codes into the run time area in F000 for ESCD & DMI support  12 Use walking I's algorithm to check out interface in CMOS circuitry. Also set real-time clock power status, and then check for override  14 Program chipset default values into chipset. Chipset default values are MODBINable by OEM customers  16 Initial onboard clock generator if Early_Init_Onboard_Generator is defined. See also POST 26.  18 Detect CPU information including brand, SMI type (Cyrix or Intel) and CPU level (586 or 686)  18 Initial interrupts vector table. If no special specified, all H/W interrupts are directed to SPURIOUS_INT_HDLR & S/W interrupts to SPURIOUS_soft_HDLR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | POST (hex) | Description                                                                              |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| -Disable shadow RAM -Disable L2 cache (socket 7 or below) -Program basic chipset registers  Detect memory -Auto-detection of DRAM size, type and ECC -Auto-detection of L2 cache (socket 7 or below)  C3 Expand compressed BIOS code to DRAM  C5 Call chipset hook to copy BIOS back to E000 & F000 shadow RAM  01 Expand the Xgroup codes locating in physical address 1000:0  03 Initial Superio Early_Init switch  05 1. Blank out screen 2. Clear CMOS error flag  1. Clear 8042 interface 2. Initialize 8042 self-test  08 1. Test special keyboard controller for Winbond 977 series Super I/O chips 2. Enable keyboard interface 1. Disable PS/2 mouse interface (optional) 2. Auto detect ports for keyboard & mouse followed by a port & interface swap (optional) 3. Reset keyboard for Winbond 977 series Super I/O chips  0E Test F000h segment shadow to see whether it is R/W-able or not. If test fails, keep beeping the speaker  10 Auto detect flash type to load appropriate flash R/W codes into the run time area in F000 for ESCD & DMI support  12 Use walking 1's algorithm to check out interface in CMOS circuitry. Also set real-time clock power status, and then check for override  14 Program chipset default values into chipset. Chipset default values are MODBINable by OEM customers  16 Initial onboard clock generator if Early_Init_Onboard_Generator is defined. See also POST 26.  18 Detect CPU information including brand, SMI type (Cyrix or Intel) and CPU level (586 or 686)  Initial interrupts vector table. If no special specified, all H/W interrupts are directed to SPURIOUS_INT_HDLR & S/W interrupts to SPURIOUS_soft_HDLR.                                                                                                                                                                                                                                                                                                                                                                                                                                       | CF         | Test CMOS R/W functionality                                                              |  |  |  |  |  |  |  |

| -Disable L2 cache (socket 7 or below) -Program basic chipset registers  Detect memory -Auto-detection of DRAM size, type and ECC -Auto-detection of L2 cache (socket 7 or below)  Expand compressed BIOS code to DRAM  C5 Call chipset hook to copy BIOS back to E000 & F000 shadow RAM  01 Expand the Xgroup codes locating in physical address 1000:0  Initial Superio_Early_Init switch  05 I. Blank out screen 2. Clear CMOS error flag  1. Clear 8042 interface 2. Initialize 8042 self-test  08 I. Test special keyboard controller for Winbond 977 series Super I/O chips 2. Enable keyboard interface  1. Disable PS/2 mouse interface (optional) 2. Auto detect ports for keyboard & mouse followed by a port & interface swap (optional) 3. Reset keyboard for Winbond 977 series Super I/O chips  Test F000h segment shadow to see whether it is R/W-able or not. If test fails, keep beeping the speaker  10 Auto detect flash type to load appropriate flash R/W codes into the run time area in F000 for ESCD & DMI support  12 Use walking 1's algorithm to check out interface in CMOS circuitry. Also set real-time clock power status, and then check for override  14 Program chipset default values into chipset. Chipset default values are MODBINable by OEM customers  16 Initial onboard clock generator if Early_Init_Onboard_Generator is defined. See also POST 26.  18 Detect CPU information including brand, SMI type (Cyrix or Intel) and CPU level (586 or 686)  Initial interrupts vector table. If no special specified, all H/W interrupts are directed to SPURIOUS_INT_HDLR & S/W interrupts to SPURIOUS_soft_HDLR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | ÿ <u>1</u>                                                                               |  |  |  |  |  |  |  |

| -Program basic chipset registers  Detect memory  -Auto-detection of DRAM size, type and ECC -Auto-detection of L2 cache (socket 7 or below)  C3 Expand compressed BIOS code to DRAM  C5 Call chipset hook to copy BIOS back to E000 & F000 shadow RAM  01 Expand the Xgroup codes locating in physical address 1000:0  03 Initial Superio_Early_Init switch  05 1. Blank out screen 2. Clear CMOS error flag  1. Clear 8042 interface 2. Initialize 8042 self-test  08 1. Test special keyboard controller for Winbond 977 series Super I/O chips 2. Enable keyboard interface 1. Disable PS/2 mouse interface (optional) 2. Auto detect ports for keyboard & mouse followed by a port & interface swap (optional) 3. Reset keyboard for Winbond 977 series Super I/O chips  OE Test F000h segment shadow to see whether it is R/W-able or not. If test fails, keep beeping the speaker  10 Auto detect flash type to load appropriate flash R/W codes into the run time area in F000 for ESCD & DMI support  12 Use walking 1's algorithm to check out interface in CMOS circuitry. Also set real-time clock power status, and then check for override  14 Program chipset default values into chipset. Chipset default values are MODBINable by OEM customers  16 Initial onboard clock generator if Early_Init_Onboard_Generator is defined. See also POST 26.  18 Detect CPU information including brand, SMI type (Cyrix or Intel) and CPU level (586 or 686)  Initial interrupts vector table. If no special specified, all H/W interrupts are directed to SPURIOUS_INT_HDLR & S/W interrupts to SPURIOUS_soft_HDLR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C0         |                                                                                          |  |  |  |  |  |  |  |