## ATCA-C110/1G AMC Carrier Blade

# Installation and Use

225254 420 000 AA

September 2005 Edition

© Copyright 2005 Motorola, Inc.

All rights reserved.

Printed in the United States of America.

### **Trademarks**

Motorola and the stylized M logo are trademarks registered in the U.S. Patent and Trademark Office.

PICMG, AdvancedTCA, and the AdvancedTCA logo are registered trademarks of PCI Industrial Computer Manufacturers Group.

PowerPC<sup>™</sup> and the PowerPC logo are trademarks of International Business Machines Corporation.

All other product or service names mentioned in this document are the property of their respective owners.

#### Safety Summary

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result in personal injury or damage to the equipment.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. If the equipment is supplied with a three-conductor AC power cable, the power cable must be plugged into an approved three-contact electrical outlet, with the grounding wire (green/yellow) reliably connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards and local electrical regulatory codes.

#### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in any explosive atmosphere such as in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment could result in an explosion and cause injury or damage.

#### Keep Away From Live Circuits Inside the Equipment.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified service personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Service personnel should not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, such personnel should always disconnect power and discharge circuits before touching components.

#### Use Caution When Exposing or Handling a CRT.

Breakage of a Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, do not handle the CRT and avoid rough handling or jarring of the equipment. Handling of a CRT should be done only by qualified service personnel using approved safety mask and gloves.

#### Do Not Substitute Parts or Modify Equipment.

Do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that all safety features are maintained.

#### **Observe Warnings in Manual.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

To prevent serious injury or death from dangerous voltages, use extreme caution when handling, testing, and adjusting this equipment and its components.

# Flammability

All Motorola PWBs (printed wiring boards) are manufactured with a flammability rating of 94V-0 by UL-recognized manufacturers.

# **EMI** Caution

This equipment generates, uses and can radiate electromagnetic energy. It may cause or be susceptible to electromagnetic interference (EMI) if not installed and used with adequate EMI protection.

# **Lithium Battery Caution**

This product contains a lithium battery to power the clock and calendar circuitry.

Danger of explosion if battery is replaced incorrectly. Replace battery only with the same or equivalent type recommended by the equipment manufacturer. Dispose of used batteries according to the manufacturer's instructions.

Il y a danger d'explosion s'il y a remplacement incorrect de la batterie. Remplacer uniquement avec une batterie du même type ou d'un type équivalent recommandé par le constructeur. Mettre au rebut les batteries usagées conformément aux instructions du fabricant.

Explosionsgefahr bei unsachgemäßem Austausch der Batterie. Ersatz nur durch denselben oder einen vom Hersteller empfohlenen Typ. Entsorgung gebrauchter Batterien nach Angaben des Herstellers.

**CE Notice (European Community)**

This is a Class A product. In a domestic environment, this product may cause radio interference, in which case the user may be required to take adequate measures.

Motorola products with the CE marking comply with the EMC Directive (89/336/EEC). Compliance with this directive implies conformity to the following European Norms:

EN55022 "Limits and Methods of Measurement of Radio Interference Characteristics of Information Technology Equipment"; this product tested to Equipment Class A

EN50082-1:1997 "Electromagnetic Compatibility—Generic Immunity Standard, Part 1. Residential, Commercial and Light Industry"

System products also fulfill EN60950 (product safety) which is essentially the requirement for the Low Voltage Directive (73/23/EEC).

Board products are tested in a representative system to show compliance with the above mentioned requirements. A proper installation in a CE-marked system will maintain the required EMC/safety performance.

In accordance with European Community directives, a "Declaration of Conformity" has been made and is on file within the European Union. The "Declaration of Conformity" is available on request. Please contact your sales representative.

## FCC Class A

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

Changes or modifications not expressly approved by Motorola could void the user's authority to operate the equipment.

Use only shielded cables when connecting peripherals to assure that appropriate radio frequency emissions compliance is maintained.

### **Industrie Canada**

This product meets the requirements of the Canadian Interference-Causing Equipment Standard ICES-003.

Cet appareil numérique est conforme à la norme NMB-003 du Canada.

### Notice

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to the Motorola Computer Group website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Motorola, Inc.

It is possible that this publication may contain reference to or information about Motorola products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

# Limited and Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

Motorola, Inc. Embedded Communications Computing 2900 South Diablo Way Tempe, Arizona 85282

# Contents

| Ab | out This Manual                                       |

|----|-------------------------------------------------------|

|    | Audience                                              |

|    | Summary of Changes                                    |

|    | Ordering Information                                  |

|    | Product Nomenclature                                  |

|    | Order Numbers                                         |

|    | Overview of Contents                                  |

|    | Comments and Suggestions                              |

|    | Conventions Used in This Manualxix<br>Signal Namesxix |

|    | Numeric notation:                                     |

|    | Miscellaneous notations                               |

|    | Typographical Conventions                             |

|    | Terms and Abbreviations                               |

|    |                                                       |

| 1  | ATCA-C110/1G Baseboard Preparation and Installation   |

|    | Introduction                                          |

|    | Product Description                                   |

|    | Baseboard Layout                                      |

|    | Equipment Required                                    |

|    | AMC Bay Locations                                     |

|    | Getting Started                                       |

|    | Overview of Startup Procedures                        |

|    | Unpacking Guidelines                                  |

|    | Hardware Configuration                                |

|    | Software Support                                      |

|    | Hardware Upgrades and Accessories                     |

|    | Installing the FIM on ATCA-C110/1G Board              |

|    | SO-DIMM Installation in a Non-Powered System          |

|    | Installing SO-DIMM                                    |

|    | Removing SO-DIMM                                      |

|    | Installing an AMC Module in a Powered System          |

|    |                                                       |

|    | Removing an AMC Module from a Powered System          |

|    | Rear Transition Modules                               |

|    | Switch Settings                                       |

|    | Before You Install or Remove an AdvancedTCA Blade     |

|    | Observe ESD Precautions                               |

|    | Watch for Bent Pins or Other Damage                   |

|    | Use Caution When Installing or Removing Blades        |

|    | Preserve EMI Compliance                               |

|    | Understand Hot Swap                                   |

|   | Control Elements                                     | 18 |

|---|------------------------------------------------------|----|

|   | Injector/Ejector Lever and Hot Swap Switch Mechanism | 18 |

|   | Verify Slot Usage                                    | 19 |

|   | Installing the ATCA-C110/1G in a Powered Chassis     | 19 |

|   | Removing the ATCA-C110/1G from a Powered Chassis     | 21 |

|   | Connecting to Peripherals                            | 22 |

|   |                                                      |    |

| 2 | Operating Instructions                               | 25 |

|   |                                                      |    |

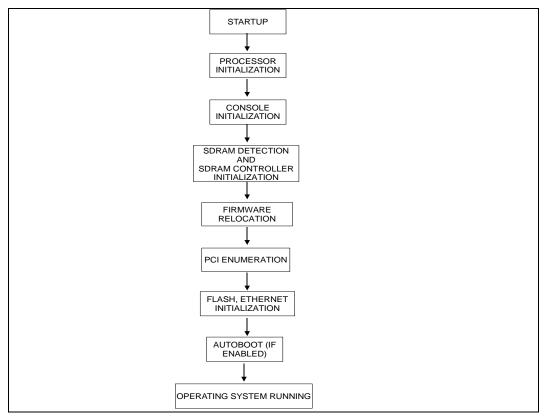

|   | System Initialization                                |    |

|   | Hot Swap Support                                     |    |

|   | Ejector Handles                                      |    |

|   | Indicator LEDs                                       |    |

|   | Booting with Firmware                                |    |

|   | Reset Sources                                        |    |

|   | Debug Support                                        | 21 |

|   |                                                      |    |

| 3 | U-Boot Firmware Overview                             | 29 |

|   | System Setup                                         | 29 |

|   | Serial Console Access                                |    |

|   | Configuring the TFTP Server                          | 29 |

|   | Configuring the BOOTP/DHCP Server                    | 30 |

|   | Configuring an NFS Server                            | 31 |

|   | Initialization of the ATCA-C110/1G Board             | 31 |

|   | Initial Steps                                        | 32 |

|   |                                                      |    |

| 4 | Functional Description                               | 35 |

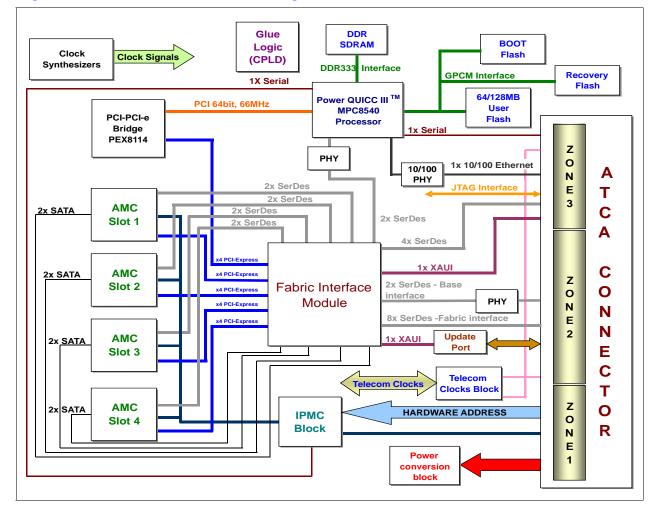

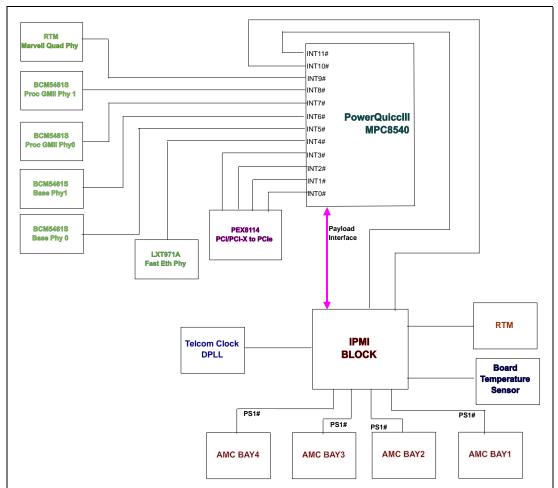

|   | ATCA-C110/1G Overview                                | 35 |

|   | ATCA Compliant features                              |    |

|   | Block Diagram – ATCA-C110/1G                         |    |

|   | Processor and Processor interfaces                   |    |

|   | СРИ                                                  | 38 |

|   | CPU Interfaces                                       | 38 |

|   | Integrated Memory Controller                         | 38 |

|   | Programmable Interrupt Controller                    | 38 |

|   | I2C Interface                                        | 39 |

|   | DUART Controller                                     | 39 |

|   | Local Bus Controller (LBC)                           |    |

|   | Three Speed Ethernet Controllers (TSEC)              |    |

|   | Fast Ethernet Controller                             | 39 |

|   | DMA Controller                                       |    |

|   | PCI/PCI-X Interface                                  |    |

|   | Main Memory                                          |    |

|   |                                                      |    |

|   | Onboard Memory                                       |    |

|   | Boot Device                                        | . 40 |

|---|----------------------------------------------------|------|

|   | System Management                                  | . 41 |

|   | IPMI                                               | . 41 |

|   | IPMB Interfaces                                    | . 42 |

|   | Private I2C Bus                                    | . 43 |

|   | Payload Interface                                  | . 43 |

|   | 8-bit Analog-to-Digital Converters (ADC)           | . 43 |

|   | AMC Power Limiting Control                         | . 43 |

|   | Telecom Clock Interface Control                    | . 43 |

|   | Digital IO                                         | . 44 |

|   | Fabric Interface Module                            | . 44 |

|   | Block Diagram – FIM                                | . 44 |

|   | PCI-Express Switch                                 | . 45 |

|   | PCI-Express to PCI Bridge                          | . 46 |

|   | Ethernet Switching Fabric                          | . 46 |

|   | SATA Multiplexer                                   | . 46 |

|   | I2C Bus Interface                                  | . 46 |

|   | I/O Subsystems                                     | . 47 |

|   | Onboard Devices                                    | . 47 |

|   | User Flash                                         | . 47 |

|   | AMC Bays                                           | . 47 |

|   | Programmable Logic Devices – CPLD                  | . 47 |

|   | PCI Interface                                      | . 48 |

|   | PCI-to-PCI-Express Bridge                          | . 48 |

|   | PCI-Express Interface                              | . 48 |

|   | Serial ATA interface                               | . 49 |

|   | Gigabit Ethernet - SerDes Interface                | . 49 |

|   | 10/100 Ethernet                                    | . 49 |

|   | Serial interface                                   | . 49 |

|   | I2C Bus                                            | . 50 |

|   | RTC interface                                      | . 50 |

|   | Power Supplies                                     | . 50 |

|   |                                                    |      |

| 5 | Controls, Indicators and Connector Pin Assignments | 51   |

|   |                                                    |      |

|   | Face plate and LEDs                                |      |

|   | Baseboard Connectors                               |      |

|   | FIM Connectors                                     |      |

|   | AMC Connectors                                     |      |

|   | Clocks                                             |      |

|   | Common Options Region                              |      |

|   | Fat Pipes Region                                   |      |

|   | Extended Options Region                            |      |

|   | ATCA Backplane Connectors                          |      |

|   | Zone 1 Connectors                                  |      |

|   | Zone 2 Connectors                                  | . 64 |

|   | Zone 3 Connectors                                            |

|---|--------------------------------------------------------------|

| 6 | Memory Map and Registers                                     |

|   | Memory Maps                                                  |

|   | Interrupt Mapping                                            |

|   | Shelf Management Registers (IPMI interface)                  |

|   | Digital IO                                                   |

|   | Payload Reset                                                |

|   | Boot ROM Selection                                           |

|   | Payload Power Enable                                         |

|   | I2C Address Map for MPC8540                                  |

|   | I2C Resources                                                |

|   | I2C to GPIO's Device Mappings - ATMega64-AMC Private I2C Bus |

|   | GPIO                                                         |

|   | Geographical addressing of AMC Bays on ATCA-C110/1G          |

|   | Ethernet Phy Address Map                                     |

|   |                                                              |

| Α | Troubleshooting                                              |

|   | Error List                                                   |

|   | Mechanical                                                   |

|   | During or After System Initialization                        |

|   | During Boot-up Procedure                                     |

|   | During Board Operation                                       |

|   |                                                              |

| В | Specifications                                               |

|   | Specifications                                               |

|   | Environmental and Physical Specifications                    |

|   | Power Requirements                                           |

|   | Standard Compliance                                          |

|   | EMC Compliance                                               |

|   |                                                              |

| С | Thermal Validation                                           |

|   | Thermal Requirements                                         |

|   | Thermally Significant Components                             |

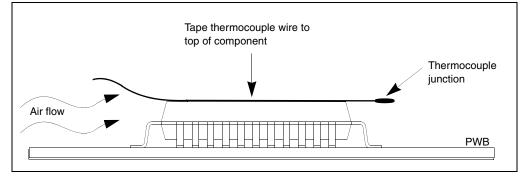

|   | Component Temperature Measurement                            |

|   | Preparation                                                  |

|   | Measuring Junction Temperature                               |

|   | Measuring Case Temperature                                   |

|   | Measuring Local Air Temperature                              |

| D | Related Documentation                                        |

| _ |                                                              |

|   | Embedded Communications Computing Documents                  |

| Manufacturers' Documents | . 100 |

|--------------------------|-------|

| Related Specifications   | . 101 |

Download from Www.Somanuals.com. All Manuals Search And Download.

# List of Figures

| Figure 1-1. Board Layout Diagram                                |     |

|-----------------------------------------------------------------|-----|

| Figure 1-2. Bay Locations on ATCA-C110/1G                       | . 4 |

| Figure 1-3. Fabric Interface Module Installation                | . 8 |

| Figure 1-4. SO-DIMM with Notch                                  | . 9 |

| Figure 1-5. SO-DIMM Socket and Projection                       | . 9 |

| Figure 1-6. Inserting SO-DIMM                                   | 10  |

| Figure 1-7. Inserted SO-DIMM locked into position               | 10  |

| Figure 1-8. Removing the SO-DIMM - pull retaining clips outward | 11  |

| Figure 1-9. Removing the SO-DIMM - slide module out             | 11  |

| Figure 1-10. Installing AMC Module in ATCA-C110/1G              | 13  |

| Figure 1-11. Switch Settings                                    | 16  |

| Figure 1-12. Injector/Ejector Lever Types for ATCA-C110/1G      | 19  |

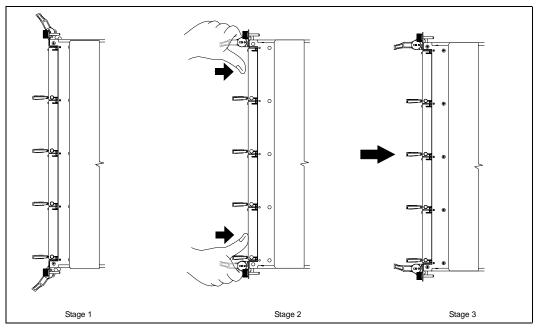

| Figure 1-13. ATCA-C110/1G Installation                          | 20  |

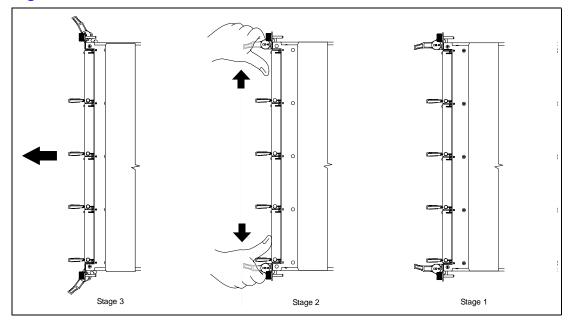

| Figure 1-14. ATCA-C110/1G Removal                               |     |

| Figure 4-1. ATCA-C110/1G Block Diagram                          | 37  |

| Figure 4-2. Primary and Secondary Boot Flash Connections        |     |

| Figure 4-3. IPMI Implementation on ATCA-C110/1G                 | 42  |

| Figure 4-4. Fabric Interface Module - Block Diagram             |     |

| Figure 5-1. Face plate LEDs                                     | 51  |

| Figure 5-2. Location of Baseboard Connectors                    | 52  |

| Figure 5-3. Location of the ATCA Connectors                     | 62  |

| Figure 6-1. Interrupt Routing Block Diagram                     | 72  |

| Figure C-1. Mounting a Thermocouple Under a Heatsink            |     |

| Figure C-2. Measuring Local Air Temperature                     | 98  |

Download from Www.Somanuals.com. All Manuals Search And Download.

# List of Tables

| Table 1. Ordering Information    xviii                                           |

|----------------------------------------------------------------------------------|

| Table 2. Accessories Ordering Information    xviii                               |

| Table 1-1. Startup Overview    5                                                 |

| Table 1-2. Default Switch Settings for SW1    16                                 |

| Table 1-3. Slot Usage Indicators    19                                           |

| Table 1-4. ATCA-C110/1G Onboard Connectors    23                                 |

| Table 1-5.    Serial Port Configuration Parameters for MPC8540    23             |

| Table 2-1. Reset Sources    26                                                   |

| Table 4-1. ATCA-C110/1G Overview         35                                      |

| Table 4-2. Port Configuration on PCI-Express Switch    45                        |

| Table 5-1. Face Plate LEDs    52                                                 |

| Table 5-2. Differential Signals between FIM and Baseboard    53                  |

| Table 5-3. FIM Connector J1 Pinout    54                                         |

| Table 5-4.    FIM Connector J2 Pinout    56                                      |

| Table 5-5. FIM Connector J3 Pinout    57                                         |

| Table 5-6.    FIM Connector J4 Pinout    58                                      |

| Table 5-7. AMC Connector Port Map    60                                          |

| Table 5-8. AMC Connector Port Mapping on ATCA-C110/1G    61                      |

| Table 5-9. Zone 1 Connector Pinouts    63                                        |

| Table 5-10.    Zone 2 Backplane Connector J20 Pinout - Rows A to D               |

| Table 5-11. Zone 2 Backplane Connector J20 Pinout - Rows E to H    64            |

| Table 5-12.    Zone 2 Backplane Connector J21 Pinout - Rows A to D               |

| Table 5-13.    Zone 2 Backplane Connector J22 Pinout - Rows A to D               |

| Table 5-14.    Zone 2 Backplane Connector J21 Pinout - Rows E to H               |

| Table 5-15.    Zone 2 Backplane Connector J22 Pinout - Rows E to H               |

| Table 5-16.    Zone 2 Backplane Connector J23 Pinout - Rows A to D               |

| Table 5-17. Zone 2 Backplane Connector J23 Pinout - Rows E to H    67            |

| Table 5-18.    Zone 3 Backplane Connector J30 Pinout - Rows A to D               |

| Table 5-19.    Zone 3 Backplane Connector J30 Pinout - Rows E to H               |

| Table 5-20.    Zone 3 Backplane Connector J31 Pinout - Rows A to D               |

| Table 5-21. Zone 3 Backplane Connector J31 Pinout - Rows E to H    68            |

| Table 5-22.    Zone 3 Backplane Connector J32 Pinout - Rows A to D               |

| Table 5-23.    Zone 3 Backplane Connector J32 Pinout - Rows E to H               |

| Table 6-1. Memory Address Map    71                                              |

| Table 6-2.    CS# Mapping of Main Memory on ATCA-C110/1G    71                   |

| Table 6-3. MPC8540 Interrupt Mapping         72                                  |

| Table 6-4. Private I2C Address Map - MPC8540    74                               |

| Table 6-5. Private I2C Address Map - ATmega8L    74                              |

| Table 6-6.    I2C to GPIO's Device Mappings - ATMega8 Private I2C Bus    Table 3 |

| Table 6-7. Private I2C Address Map - ATmega64-AMC micro-controller               |

| ble 6-8. I2C to GPIO's Device Mappings - ATMega64-AMC Private I2C Bus | 30 |

|-----------------------------------------------------------------------|----|

| ble 6-9. Geographical addressing of AMC Bays on ATCA-C110/1G          | 32 |

| ble 6-10. Ethernet Phy Address Map                                    | 32 |

| ble B-1. ATCA-C110/1G Environmental Specifications                    | 90 |

| Ible B-2. Power Requirements                                          | 91 |

| ble B-3. Standard Compliance                                          | 92 |

| ble C-1. Thermally Significant Components                             | 95 |

| ble D-1. Embedded Communications Computing Documents                  | 99 |

| ble D-2. Manufacturers' Documents                                     | 00 |

| ble D-3. Related Specifications                                       | 01 |

# About This Manual

This manual provides both general and functional descriptions of the product along with installation and removal instructions, firmware details, connector pin assignments, memory maps, troubleshooting information, specifications, thermal validation and related documentation details for the ATCA-C110/1G board.

The ATCA-C110/1G is a multi-function conventional AMC Carrier intended to be used in control and management applications on AdvancedTCA<sup>™</sup> systems. The board uses the MPC8540 as its Service Processor and has Gigabit Ethernet, UART, SATA and PCI Express as its I/O interfaces.

# **Audience**

This document is written for anyone who designs OEM systems, supplies additional capability to existing compatible systems, or works in a lab environment for experimental purposes. It is important to note that a basic knowledge of computers and digital logic is assumed; users must have a working understanding of AdvancedTCA and telecommunications. To use this document successfully, you should be familiar with the documents listed in Appendix D, *Related Documentation*, in particular documents related to the AMC.x and PICMG 3.x.

# **Summary of Changes**

This is the first release of ATCA-C110/1G Installation and Use Guide.

# **Ordering Information**

When ordering the board variants, upgrades and accessories, use the order numbers given below.

## **Product Nomenclature**

The following table lists the key for the product name extensions.

| АТСА-С110/1G-хх-ууу |                       |

|---------------------|-----------------------|

| 1G                  | Ethernet Fabric speed |

| xx                  | RAM size in GBytes    |

| ууу                 | CPU frequency in MHz  |

### **Order Numbers**

The table below is an excerpt from the blade's ordering information. Ask your local Motorola representative for the current ordering information.

#### **Table 1. Ordering Information**

| Order Number | Variant Name         | Description                         |

|--------------|----------------------|-------------------------------------|

| 121871       | ATCA-C110/1G-1GB-833 | AMC carrier board along with 1G FIM |

The table below is an excerpt from the blade's accessories ordering information. Ask your local Motorola representative for the current ordering information.

#### **Table 2. Accessories Ordering Information**

| Order Number | Accessory        | Description                              |

|--------------|------------------|------------------------------------------|

| 122375       | ACC/ARTM-C110/1G | Rear transition module for ATCA-C110/1G. |

# **Overview of Contents**

This manual is divided into the following chapters and appendices.

Chapter 1, *ATCA-C110/1G Baseboard Preparation and Installation*, includes instructions and diagrams for hardware preparation and installation and removal procedures.

Chapter 2, *Operating Instructions*, provides a description of basic operational characteristics of the ATCA-C110/1G including system initialization sequence, hot swap support, sources of reset, and the debug support.

Chapter 3, *U-Boot Firmware Overview*, gives a brief overview of U-Boot boot loader and host system set up.

Chapter 4, *Functional Description*, describes the ATCA-C110/1G on a block diagram level. It provides an explanation of the various components and the functional characteristics of the board.

Chapter 5, *Controls, Indicators and Connector Pin Assignments*, summarizes the LEDs and pin assignments provided on the ATCA-C110/1G baseboard.

Chapter 6, *Memory Map and Registers*, provides a description of memory maps and programming information including register reference, and memory structure.

Appendix A, *Troubleshooting*, provides a hint list for detecting possible errors which could be mechanical in nature or which could occur after power on, during boot-up or during board operation.

Appendix B, *Specifications*, lists the general specifications and compliance for ATCA-C110/1G boards.

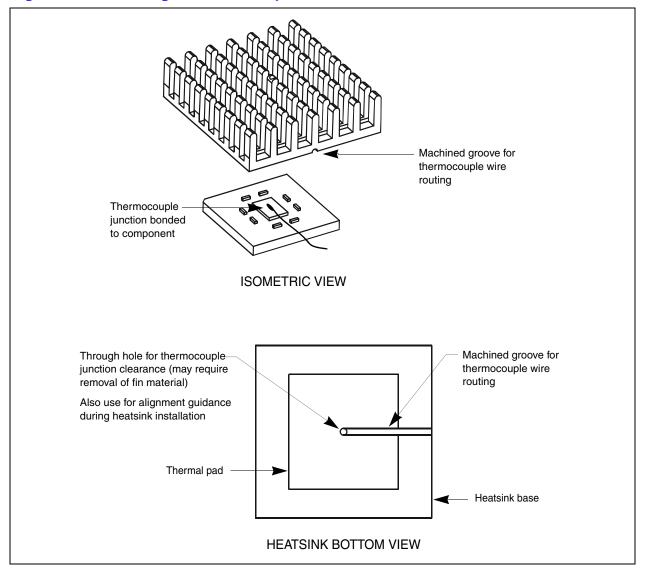

Appendix C, *Thermal Validation*, provides information about thermally significant components and an overview of how to measure various junction and case temperatures.

Appendix D, *Related Documentation*, lists other Motorola Computer Group documents, industry specifications, and additional sources of related information.

# **Comments and Suggestions**

Motorola welcomes and appreciates your comments on its documentation. We want to know what you think about our manuals and how we can make them better. Mail comments to:

Motorola, Inc. Embedded Communications Computing Group Reader Comments DW164 2900 S. Diablo Way Tempe, Arizona 85282

You can also submit comments to the following e-mail address: reader-comments@mcg.mot.com

In all your correspondence, please list your name, position, and company. Be sure to include the title and part number of the manual and tell how you used it. Then tell us your feelings about its strengths and weaknesses and any recommendations for improvements.

# **Conventions Used in This Manual**

### **Signal Names**

Differential signals are denoted by a trailing positive (+) or negative (-) symbol. For instance, TX+/TX- denotes a differential transmit signal pair.

A pound sign (#) following the signal name for signals which are level significant denotes that the signal is true or valid when the signal is low. For instance, RESET#.

A pound sign (#) following the signal name for signals which are edge significant denotes that the actions initiated by that signal occur on high to low transition.

Bussed signal groups are represented as BUSNAME [0:N-1] where N is the bus-width. For instance, an 8-bit address bus could be ADDR [0:7].

### **Numeric notation:**

Binary numbers are suffixed with 'b' (e.g. 01b), whereas hexadecimal numbers are prefixed with '0x' (e.g. 0x5F). Other numbers (e.g. 35) are decimal.

### **Miscellaneous notations**

The term AMC Carrier refers to the ATCA-C110/1G board/blade, and is used interchangeably.

The phrases Service Processor and MPC8540 are used interchangeably.

The term **xY** in reference to a serial link refers to a link with a width of Y Lanes. For example, an x4 PCI-Express link refers to that the PCI-Express link with a width of 4 lanes.

The term **Yx** indicates plurality in general. For example, a 2x SerDes interface refers to two SerDes interfaces each with one TX and RX pair for communication.

# **Typographical Conventions**

#### bold

is used for user input that you type just as it appears; it is also used for commands, options and arguments to commands, and names of programs, directories and files.

#### italic

is used for names of variables to which you assign values. Italic is also used for comments in screen displays and examples, and to introduce new terms.

#### courier

is used for system output (for example, screen displays, reports), examples, and system prompts.

#### <Enter>, <Return> or <CR>

represents the carriage return or Enter key.

#### Ctrl

represents the Control key. Execute control characters by pressing the **Ctrl** key and the letter simultaneously, for example, **Ctrl-d**.

**Note** Contains information that is not critical to the procedure, task, or information you are describing. Notes are usually used to give the reader a tip or additional information.

Identifies any risk of system failure, service interruption, or damage to equipment and should explicitly state the nature of the risk and specify how to reduce or avoid the risk.

Avoid touching areas of integrated circuitry; static discharge can damage circuits.

Use ESD

Wrist Strap

Identifies any risk of personal injury or loss of life and should explicitly state the nature of the risk and specify how to reduce or avoid the risk.

Before you install or remove a board Motorola strongly recommends that you use an

# **Terms and Abbreviations**

This document uses the following terms and abbreviations:

antistatic wrist strap and a conductive foam pad.

| Term                | Definition                                                                             |

|---------------------|----------------------------------------------------------------------------------------|

| ADC                 | Analog to Digital Converter                                                            |

| AMC                 | Advanced Mezzanine Card                                                                |

| ARTM                | AdvancedTCA Rear Transition Module                                                     |

| ATCA                | Advanced Telecom Computing Architecture                                                |

| BIB                 | Board Information Block                                                                |

| CL                  | CAS Latency (for SDRAM)                                                                |

| CLI                 | Command Line Interface                                                                 |

| СОР                 | Control and Observation Port (PowerPC JTAG debug port)                                 |

| CPLD                | Complex Programmable Logic Device                                                      |

| CPU                 | Central Processing Unit                                                                |

| DMA                 | Direct Memory Access                                                                   |

| DRAM                | Dynamic Random Access Memory                                                           |

| E <sup>2</sup> PROM | Electrically Erasable Programmable Read Only Memory                                    |

| FEC                 | Fast Ethernet Controller                                                               |

| FIM                 | Fabric Interface Module                                                                |

| GbE                 | Gigabit Ethernet                                                                       |

| GPCM                | General Purpose Chipselect Machine                                                     |

| I/O                 | Input/Output                                                                           |

| l <sup>2</sup> C    | Inter-Integrated Circuit Bus                                                           |

| IPMB                | Intelligent Platform Management Bus                                                    |

| IPMC                | Intelligent Peripheral Management Controller (also referred to as the IPMI Controller) |

| IPMI                | Intelligent Platform Management Interface                                              |

| JTAG                | Joint Test Action Group; test interface for digital logic circuits                     |

| LED                 | Light-Emitting Diode                                                                   |

| Term   | Definition                                                              |

|--------|-------------------------------------------------------------------------|

| MAC    | Medium Access Controller (for Ethernet)                                 |

| МІІ    | Media Independent Interface (for Ethernet)                              |

| МІМ    | Media Independent Interface Management                                  |

| NMI    | Non-maskable interrupts                                                 |

| NPTH   | Non-Plated Through-hole                                                 |

| PCA    | Printed Circuit Assembly                                                |

| РСВ    | Printed Circuit Board                                                   |

| PCI    | Peripheral Component Interconnect                                       |

| РНҮ    | Physical transceiver device for Ethernet                                |

| PICMG  | PCI Industrial Computer Manufacturers Group.                            |

| QoS    | Quality of Service                                                      |

| R/W    | Read/write                                                              |

| RS-232 | Recommended Standard -232C: interface standard for serial communication |

| RTC    | Real Time Clock                                                         |

| RTOS   | Real Time Operating System                                              |

| SDRAM  | Synchronous Dynamic Random Access Memory                                |

| SerDes | Serializer De-Serializer                                                |

| ShMC   | Shelf Management Controller                                             |

| SoC    | System on Chip                                                          |

| SPD    | Serial Presence Detect                                                  |

| SRAM   | Static Random Access Memory                                             |

| TBD    | To be decided                                                           |

| тс     | Traffic Class                                                           |

| UART   | Universal Asynchronous Receiver-Transmitter                             |

| UBOOT  | Universal Boot Code for PowerPC's                                       |

| UPM    | User-Programmable Machine                                               |

| VC     | Virtual Channel                                                         |

| VPD    | Vital Product Data                                                      |

| XAUI   | 10G Attachment Unit Interface                                           |

# ATCA-C110/1G Baseboard Preparation and Installation

# Introduction

This chapter outlines startup and safety instructions, hardware accessories details, switch settings, hardware preparation, installation and removal instructions.

# **Product Description**

The ATCA-C110/1G is an AdvancedTCA form factor blade acting as a multi-functional conventional AMC carrier and supporting a centralized fabric switching architecture. The board is built according to the *AdvancedTCA* and *AMC Specifications*. The board is designed for use in the AXP Application-Enabling Platform, but may also be installed into any ATCA shelf. The Operating Environment consists of Basic Blade Services (BBS) and Carrier Grade Linux (CGL).

The following are some of the features of the ATCA-C110/1G board:

- MPC8540 Service Processor

- DDR memory of capacity 1 GB with an operating frequency of 333 MHz

- 2 MB Boot Flash (with failure recovery capability) on the GPCM interface of the MPC8540 Processor

- PICMG 3.x features:

- ATCA Base Interface

- ATCA Fabric Interface

- ATCA compliant LEDs

- IPMI Interface

- Synchronization Clock Interface

- Update Ports

- AMC.x features

- Four B+ type AMC bays that support the following AMC Bay Interfaces:

- PCI-Express Interface link of 4 lanes (x4 PCI-Express link)

- 2x Gigabit Ethernet Interface

- 2x Serial ATA Link

- Three unique Geographical Address (GA) lines for each AMC module's IPMB address. The module's Management Controller communicates with the ATCA-C110/1G carrier board using IPMB.

- Support for AMC Interface Ports (refer to AMC Connectors on page 59 for more details)

1

- Onboard Devices such as:

- PCI to PCI-Express Bridge

- GigE PHYs

- BCM56502 GigE Switch (device on FIM)

- PEX8532 PCI-Express Switch (device on FIM)

- SATA Multiplexer (device on FIM)

The details of major onboard components are described in Chapter 4, Functional Description.

The fully assembled ATCA-C110/1G consists of:

- ATCA-C110/1G carrier board

- 1G Fabric Interface Module

- Rear Transition Module

- Four single-width, full height, B+ Connector type AMC modules

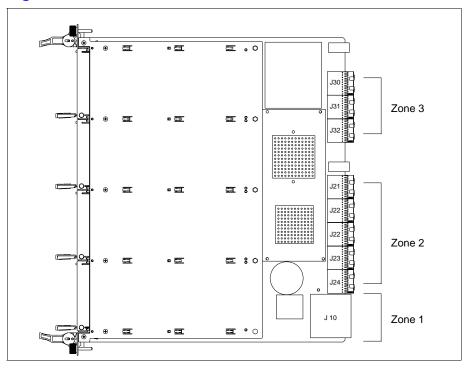

# **Baseboard Layout**

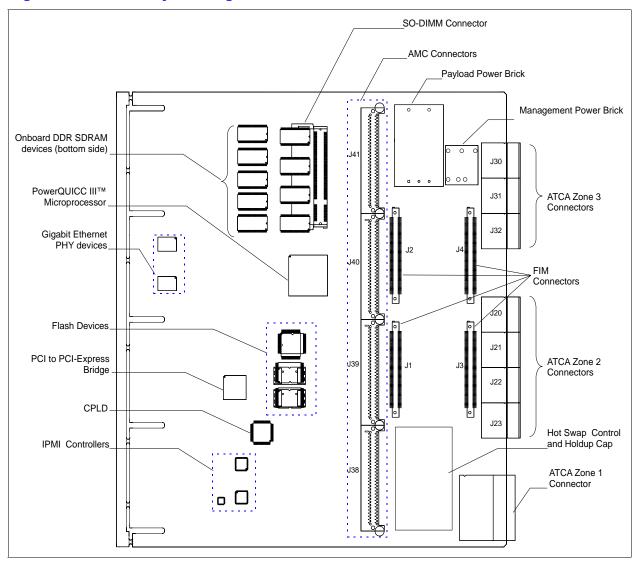

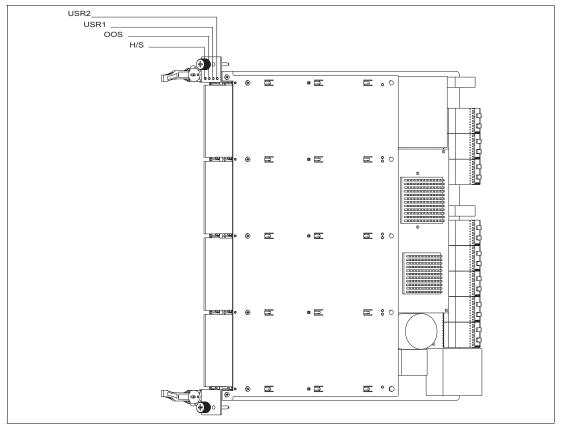

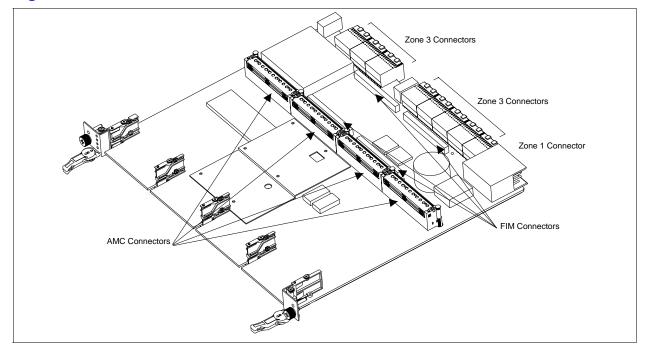

The figure below shows the placement of the components on the ATCA-C110/1G board.

#### Figure 1-1. Board Layout Diagram

# **Equipment Required**

To install the ATCA-C110/1G board you need the following equipment:

- PICMG 3.0 Compliant AdvancedTCA Modular Communications Platform AXP or any ATCA complaint chassis

- PICMG 3.1 Compliant Fabric Switch Blades supporting the Base and Fabric Interface

- PICMG 3.0 Compliant Shelf Manager with IPMI interoperability

- AMC B+ single-width, full-height modules

- ARTM-C110 Rear Transition Module and connecting cables

The ATCA-C110/1G has two face plates: top and bottom, which are mounted on the top strut and bottom strut, respectively. No front panel I/O is present on the ATCA-C110/1G board. See *Face plate and LEDs* on page 51 for more details.

The rear panel I/O is provided via a Rear Transition Module. Refer *Rear Transition Modules* on page 15 for more information.

# **AMC Bay Locations**

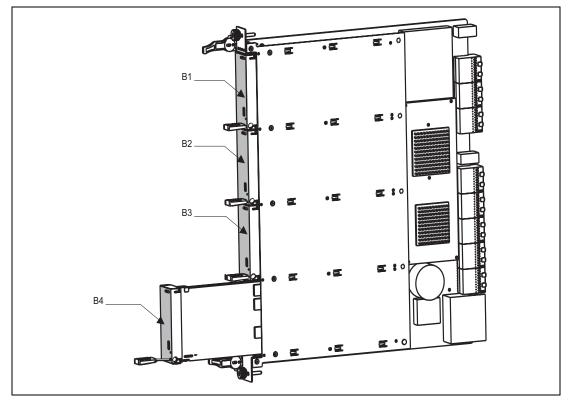

The ATCA-C110/1G is a conventional AMC carrier board with four B+ type AMC bays. Figure 1-2 shows AMC Bay locations on the ATCA-C110/1G board. An AMC Bay is a single AMC site on an AMC carrier.

Bays on a carrier are identified by an alphanumeric value representing the Bay layer and position. Bay layers are designated as A and B, while positions within each layer are designated as 1 through 4.

Bays are identified by a capital letter followed by a numeral. The letter shall be A for the lower Bay and B for the upper Bay, and also B for the Single Layer Bay. The number identifies the Bay's position. The Bay positions, Single Layer and Stacked, shall be numbered together, contiguously, starting with 1 at the top.

#### Figure 1-2. Bay Locations on ATCA-C110/1G

# **Getting Started**

This section provides an overview of the steps necessary to install the ATCA-C110/1G and a brief section on unpacking and ESD precautions.

### **Overview of Startup Procedures**

Table 1-1 lists the things you will need to do before you can use this board and tells where to find the information you need to perform each step. Be sure to read this entire chapter, including all Caution and Warning notes, before you begin.

### Table 1-1. Startup Overview

| What you need to do                                                                     | Refer to                                                                                                     |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Unpack the hardware.                                                                    | Unpacking Guidelines on page 5                                                                               |

| Make sure specifications and requirements are met.                                      | Appendix B, Specifications                                                                                   |

| Setting up hardware                                                                     | Hardware Configuration on page 6                                                                             |

| Install the onboard accessories, if applicable.                                         | Hardware Upgrades and Accessories on page 7                                                                  |

| Ensure Fabric Interface Module is installed.                                            | Installing the FIM on ATCA-C110/1G Board on page 7                                                           |

| Installing the ATCA-C110/1G on a chassis or shelf.                                      | Installing the ATCA-C110/1G in a Powered Chassis on page 19                                                  |

| Install RTM, if required.                                                               | The ARTM-C110 Rear Transition Module<br>Installation and Use Manual                                          |

| Install the B+ single-width, full-height, Advanced Mezzanine Cards on the ATCA-C110/1G. | <i>Installing an AMC Module in a Powered System</i> on page 12                                               |

| Install ATCA-C110/1G on chassis.                                                        | Installing the ATCA-C110/1G in a Powered Chassis on page 19                                                  |

| Connect any other equipment you will be using.                                          | Connecting to Peripherals on page 22 and<br>Chapter 5, Controls, Indicators and Connector Pin<br>Assignments |

| Initialize the System                                                                   | Chapter 2, Operating Instructions                                                                            |

| Familiarize yourself with U-Boot Firmware                                               | Chapter 3, U-Boot Firmware Overview                                                                          |

| Program your ATCA-C110/1G as needed by your application.                                | Chapter 6, Memory Map and Registers                                                                          |

### **Unpacking Guidelines**

Unpack the equipment from the shipping carton. Refer to the packing list and verify that all items are present. Save the packing material for storing and reshipping of equipment.

**Note** If the shipping carton is damaged upon receipt, request that the carrier's agent be present during the unpacking and inspection of the equipment.

5

Avoid touching areas of integrated circuitry; static discharge can damage circuits.

Wrist Strap

Motorola strongly recommends that you use an antistatic wrist strap and a conductive foam pad when installing or upgrading a system. Electronic components, such as disk drives, computer boards, and memory modules, can be extremely sensitive to electrostatic discharge (ESD). After removing the component from its protective wrapper or from the system, place the component flat on a grounded, static-free surface (and, in the case of a board, component side up). Do not slide the component over any surface.

If an ESD station is not available, you can avoid damage resulting from ESD by wearing an antistatic wrist strap (available at electronics stores) that is attached to an active electrical ground. Note that a system chassis may not be grounded if it is unplugged.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

# **Hardware Configuration**

This section discusses certain hardware and software tasks that may need to be performed prior to installing the blade in a shelf.

The ATCA-C110/1G board has been factory tested and is shipped with the configurations. It contains a factory installed start-up firmware, U-Boot, which operates with those factory settings. See Chapter 3, *U-Boot Firmware Overview* for more details. You can configure most options on the ATCA-C110/1G via the U-Boot. Configuration changes are made by setting bits in control registers after the board is installed in a system.

The user control configuration details are described in Chapter 6, *Memory Map and Registers*. For more details refer to the datasheets of the devices as listed in *Manufacturers' Documents* on page 100.

# **Software Support**

Refer to the current ATCA-C110/1G Software Release Notes, as listed in Appendix B, *Specifications*, for a complete list of supported features and known limitations. All features described in this guide may not be supported in early released (proto) versions.

# Hardware Upgrades and Accessories

Hardware upgrades and accessories allow an easy and cost-efficient way to adapt the system board to your application needs.

The following hardware upgrades and accessories are available:

- Fabric Interface Module refer Installing the FIM on ATCA-C110/1G Board on page 7

- SO-DIMM Memory Modules refer Installing SO-DIMM on page 9

- AMC Modules refer Installing an AMC Module in a Powered System on page 12

The installation procedure for each hardware upgrade and accessory is described in the sections below.

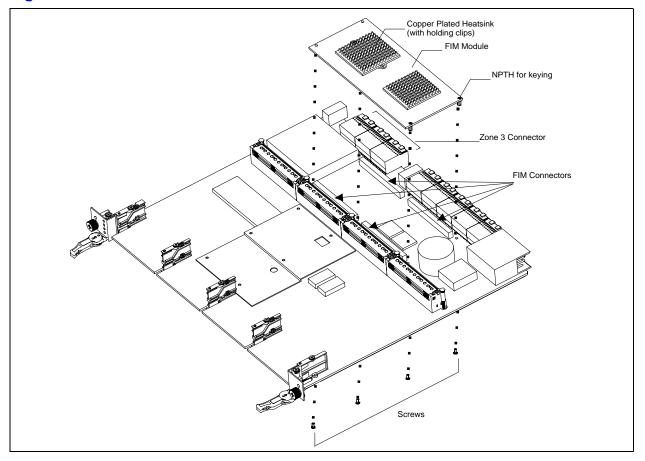

### Installing the FIM on ATCA-C110/1G Board

To install the FIM on the ATCA-C110/1G board, refer to Figure 1-3 on page 8, read all cautions and warnings and perform the following steps.

**Note** Since the FIM is not hot-swappable always install the ATCA-C110/1G when power is turned off. The FIM is assembled on the delivered board. The following steps detail the procedures to replace the FIM onboard the ATCA-C110/1G, in case of any FIM failure.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing and adjusting.

Electrostatic discharge and incorrect board installation and removal can damage circuits or shorten their life.

Therefore, before touching boards or electronic components, make sure that you are working in an ESD-safe environment.

Damage to Board or electronic components Avoid touching areas of integrated circuitry; static discharge can damage the circuits. Therefore, before touching boards or electronic components, make sure that you are

working in an ESD-safe environment.

Damage of Circuits

Step 1:Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure

**Step 2**:Remove the ATCA-C110/1G board from the chassis - refer to *Removing the ATCA-C110/1G from a Powered Chassis* on page 21.

7

#### Figure 1-3. Fabric Interface Module Installation

- **Step 3:**After removing the carrier board from its card slot, place it on a clean and adequately protected working surface (preferably an ESD mat) with the bottom side of the board facing up.

- Step 4:Remove the screws from the holes in the carrier board that fasten the FIM to the carrier board.

- **Step 5:**Carefully turn the carrier board over to the top side and place it on your working surface. Gently separate the FIM from the FIM connectors on the carrier board. Do not damage or bend connector pins.

- Step 6:Identify the FIM connectors on the carrier card as shown in the figure above.

- Step 7:Align the FIM over the FIM connectors making sure that the larger heatsink (with holding clips) is oriented towards the Zone 3 connector. Ensure that the NPTH of the FIM is aligned with the NPTH of the ATCA-C110/1G carrier board.

- **Step 8:**Carefully press the FIM into the FIM connectors. Ensure that the standoffs of the module are seated into the mounting holes of the carrier board.

- **Step 9:**Turn the carrier board over and on the bottom side of the carrier board, fasten the screws through the holes in the carrier board and the spacers. Tighten the screws.

The FIM is now fully installed on the carrier board. Install the ATCA-C110/1G in its proper card slot by following the procedures given in *Installing the ATCA-C110/1G in a Powered Chassis* on page 19.

### **SO-DIMM Installation in a Non-Powered System**

#### Note

- The SO-DIMM onboard the ATCA-C110/1G can be installed only when the module is removed from the carrier board.

- It is recommended to use the SODIMM that is factory-shipped along with the ATCA-C110/1G, since it has already been verified and validated.

If using SO-DIMM other than the standard supplied SO-DIMM, ensure that the following requirements are met when power is turned off.

- Is unbuffered

- Is 2.5V, PC166 SDRAM module compliant to the JEDEC Specification

- Has size of either 128 MB, 256 MB or 512 MB or 1 GB. (The MPC8540 will configure memory maps automatically on boot)

- Supports ECC

#### Installing SO-DIMM

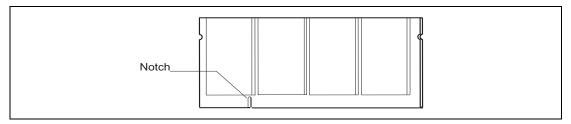

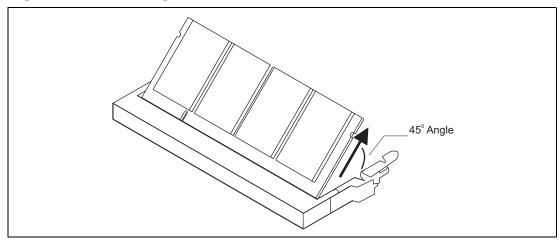

To install the SO-DIMM into the SO-DIMM socket on the ATCA-C110/1G follow these steps:

Step 1:Identify the SO-DIMM socket located onboard the ATCA-C110/1G. Locate the notch on the SO-DIMM socket as shown in Figure 1-4.

#### Figure 1-4. SO-DIMM with Notch

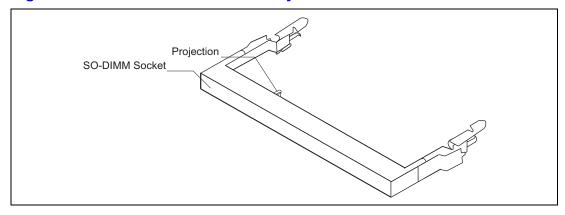

Step 2:Locate the projection on the SO-DIMM socket as shown in Figure 1-5.

#### Figure 1-5. SO-DIMM Socket and Projection

9

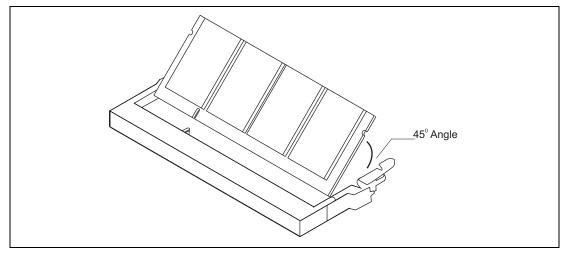

Step 3:Firmly insert the SO-DIMM into the socket at a 45° angle in the direction as indicated in Figure 1-6. Push the SO-DIMM down until the retaining clip of the socket locks the SO-DIMM into position.

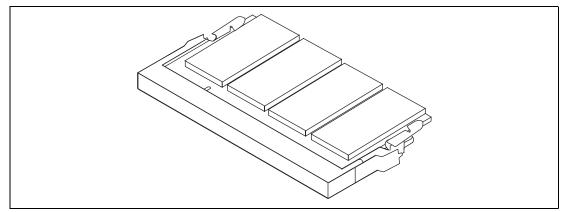

Step 4: The fully installed SO-DIMM in its socket is shown in Figure 1-7.

### **Removing SO-DIMM**

To remove the SO-DIMM from the SO-DIMM socket on the ATCA-C110/1G follow these steps:

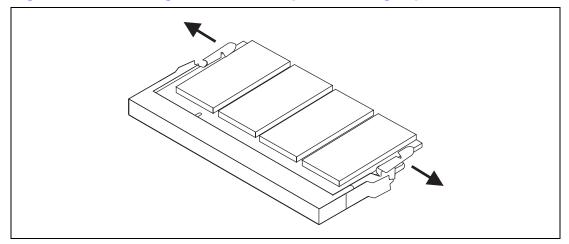

**Step 1:**Pull the two retaining clips of the SO-DIMM socket in an outward direction, parallel to the surface of the board, as shown by arrows in Figure 1-8.

#### Figure 1-8. Removing the SO-DIMM - pull retaining clips outward

Step 2: The SO-DIMM will no longer be locked in position, but will be at an angle of 45°, shown in *Removing the SO-DIMM - slide module out* on page 11. Pull the SO-DIMM outwards in the direction of the arrow as shown below.

#### Figure 1-9. Removing the SO-DIMM - slide module out

Step 3: The SO-DIMM is now removed from ATCA-C110/1G.

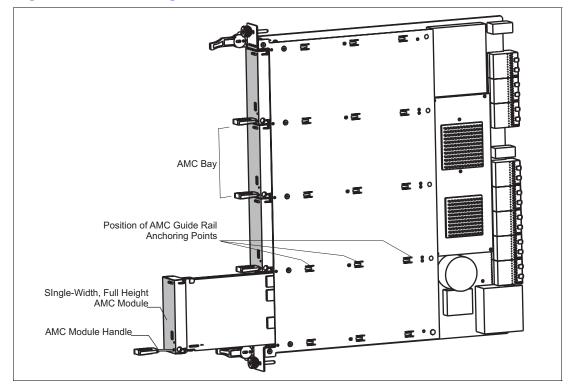

## Installing an AMC Module in a Powered System

To install an AMC Module on a AdvancedTCA host board, refer to the Figure 1-10 on page 13, read all cautions and warnings and perform the following steps. This figure is for reference only and may not represent the exact host board you are using.

#### Note

- ATCA-C110/1G can accommodate up to four single-width, full-height, B+ Connector Type, Advanced Mezzanine Cards. Refer to AMC Bay Locations on page 4 for the locations of the AMC Bays onboard the ATCA-C110/1G.

- The AMC installation procedure assumes that the ATCA-C110/1G is already installed in its host chassis - see Installing the ATCA-C110/1G in a Powered Chassis on page 19.

- The installation procedure assumes that the AMC module is being hot-inserted into a live carrier. The procedure for a cold insertion (when the carrier is not powered) is the same, except that you need not wait for the blue LED indications to proceed. For more details about hot swap, refer to Understand Hot Swap on page 18.

- Figure 1-10 on page 13 is for reference only and may not represent the exact carrier board you are using.

- Refer to the PrAMC-7201 Installation and Use manual as mentioned in Appendix D, Related Documentation for more details.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing and adjusting.

#### Damage of Circuits

Electrostatic discharge and incorrect board installation and removal can damage circuits or shorten their life.

Therefore, before touching boards or electronic components, make sure that you are working in an ESD-safe environment.

#### Module damage

Only mount permitted combinations of AMC variants. Otherwise, damage to AMC module, carrier card and equipment attached to the rear transition board may occur. Therefore, only install and use the AMC module together with the Embedded Communications Computing's carrier card.

Step 1: Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

### Figure 1-10. Installing AMC Module in ATCA-C110/1G

Step 2:Identify the AMC bay to be used for installation. Please note the following possibilities:

- If the required AMC bay is occupied by the AMC filler panel, you will need to remove the filler panel before proceeding with the installation procedure. The handles' latch mechanisms for the filler panel and the AMC module are similar, follow the steps listed in *Removing an AMC Module from a Powered System* on page 14 to remove the filler panel. The blue LED on the filler panel is irrelevant.

- If the identified bay is already filled by another AMC module, remove this module from the bay (follow the steps listed in *Removing an AMC Module from a Powered System* on page 14).

- **Step 3:**Ensure that board handles are in the extracted position: pulled outward, away from the faceplate.

- **Step 4:**Using your thumb, apply equal and steady pressure on the faceplate as necessary to carefully slide the AMC module into the guides rails.

- **Step 5:**Continue to gently push the module along the guide rails till the module is fully engaged with the connector. Avoid using excessive force during this operation.

- **Step 6:**Wait for the blue LED to glow. The blue LED glows when the AMC module is completely engaged with the connector.

- Step 7: Press board handles inwards towards the faceplate to lock the AMC module on AMC bay.

- **Step 8:**Wait for the blue LED to perform a series of long blinks. The blue LED blinks when the handles are locked in position indicating module detection and activation by the carrier board.

- Step 9: Observe blue LED status/activity. The module is fully installed when the blue LED stops blinking.

### Removing an AMC Module from a Powered System

To remove an AMC Module from the ATCA-C110/1G, read all cautions and warnings and perform the following steps.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing and adjusting.

Warning

Damage to module components

Inserting or removing modules with power applied may result in damage to module components.

Therefore, ensure that you power down before inserting or removing the AMC-7201 module.

**Unpredictable System behavior**

Avoid sudden module extractions from the carrier, without waiting for the blue LED status change as indicated in the steps below. A surprise hot extraction, which does not allow the MMC (Module Management Controller) time to react and initiate a graceful extraction sequence, is liable to cause a system software crash, especially if there are no recovery mechanisms built into the system software.

Step 1: Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure.

Step 2: If multiple AMC modules are installed on the carrier, identify the AMC module to be extracted.

Step 3:Remove any cables that are fastened to front panel connectors, if any.

Step 4:Gently pull the module latch outwards approximately 3 mm from its locked position.

Step 5: Wait for the blue LED to first perform short blinks, and then glow persistently.

**Note** Please wait for the blue LED to glow persistently before proceeding to the next step.

- Step 6: Once the blue LED glows, gently pull handles outwards to disconnect the module from the AMC connectors. Continue to gently slide the module outwards along the guide rails.

- Step 7: After module removal is complete, place the module on a clean and adequately protected working surface (preferably an ESD mat) with the top side of the board facing up.

Note Empty or unused AMC Bays need to be covered with a filler panel, in order to satisfy environmental and EMC compliance.

## **Rear Transition Modules**

At the time of writing this manual the ACC/ARTM-C110 Rear Transition Module was available for the blade. For further information, refer to the ACC/ARTM-C110 Installation and Use manual.

The RTM provides the following interfaces:

- Debug Serial port for the IPMI Controllers onboard the ATCA-C110/1G

- Debug Serial port from the Control Processor

- Ethernet port for the 10/100 port from the Control Processor

- Four Gigabit Ethernet ports from the FIM

- CX4 connector for XAUI interface from Ethernet Switch on the FIM

- Debug USB connector for the interface from AMC Bay 4

- RJ45 connector for Telecom clock interface

- JTAG header for programming

- SPI Programming Interface for IPMI Programming

- IPMI Interface

#### Note

- You must install the ARTM-C110 before the ATCA-C110/1G carrier board is installed.

- Refer to the ARTM-C110 Installation and Use manual for the RTM installation procedure.

- Check the documentation of the system where you operate the blade and the RTM for any restrictions that may apply to the blade or the RTM.

- No hot-swap is supported for the RTMs.

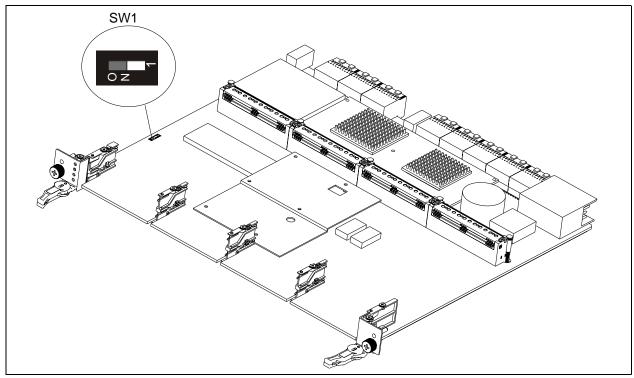

## **Switch Settings**

The blade provides the configuration switch SW1. The switch provides AMC bay selection in the JTAG chain. The board is delivered with the white switch set to the default OFF position. Refer to Table 1-2 on page 16 for default switch settings of SW1.

### Figure 1-11. Switch Settings

### Table 1-2. Default Switch Settings for SW1

| SW0 | SW1 | Description                 |

|-----|-----|-----------------------------|

| On  | On  | AMC Bay 1 on the JTAG chain |

| Off | On  | AMC Bay 2 on the JTAG chain |

| On  | Off | AMC Bay 3 on the JTAG chain |

| Off | Off | AMC Bay 4 on the JTAG chain |

## Before You Install or Remove an AdvancedTCA Blade

Blades may be damaged if improperly installed or handled. Please read and follow the guidelines in this section to protect your equipment.

## **Observe ESD Precautions**

Wrist Strap

Motorola strongly recommends that you use an antistatic wrist strap and a conductive foam pad when installing or upgrading a system. Electronic components, such as disk drives, computer boards, and memory modules, can be extremely sensitive to electrostatic discharge (ESD). After removing the component from its protective wrapper or from the system, place the component flat on a grounded, static-free surface (and, in the case of a board, component side up). Do not slide the component over any surface.

If an ESD station is not available, you can avoid damage resulting from ESD by wearing an antistatic wrist strap (available at electronics stores) that is attached to an active electrical ground. Note that a system chassis may not be grounded if it is unplugged.

### Watch for Bent Pins or Other Damage

Bent pins or loose components can cause damage to the blade, the backplane, or other system components. Carefully inspect your blade and the backplane for both pin and component integrity before installation.

Motorola and our suppliers take significant steps to ensure there are no bent pins on the backplane or connector damage to the boards prior to leaving our factory. Bent pins caused by improper installation or by boards with damaged connectors could void the Motorola warranty for the backplane or blades.

If a system contains one or more crushed pins, power off the system and contact your local sales representative to schedule delivery of a replacement chassis assembly.

### **Use Caution When Installing or Removing Blades**

When first installing blades in an empty shelf, we recommend that you start at the left of the card cage and work to the right when cards are vertically aligned; in horizontally aligned cages, work from bottom to top.

When inserting or removing a board in a slot adjacent to other boards, use extra caution to avoid damage to the pins and components located on the top or bottom sides of the blades.

## **Preserve EMI Compliance**

To preserve compliance with applicable standards and regulations for electromagnetic interference (EMI), during operation all front and rear openings on the shelf or blade face plates must be filled with an appropriate card or covered with a filler panel. If the EMI barrier is open, devices may cause or be susceptible to excessive interference.

## **Understand Hot Swap**

**Board/Component Damage**

Inserting or removing non-hot swap cards or transition modules with power applied may result in damage to module components. Make sure that your blade manufacturer identifies your module as hot swap ready.

The *PICMG 3.0 Specification* defines varying levels of hot swap. A blade that is compliant with the specification can be inserted and removed safely with system power on without damage to onboard circuitry. *If a module is not hot swap compliant, you should remove power to the slot or system before inserting or removing the module.*

To facilitate hot swap, PICMG 3.0 specifies a blue LED on the face plate and board handles' latch mechanism. This LED is under the control of System Management Firmware (IPMI). The IPMI firmware will illuminate the blue hot-swap LED on the face plate, when it has powered down the board, thus indicating that it is safe to remove the board.

**Corruption of Data or File System**

Powering down or removing a blade before the operating system or other software running on the blade has been properly shut down may cause corruption of data or file systems.

Therefore, ensure that the board has been properly shut down. You should ensure that the blue hot swap LED on the faceplate is illuminated before extracting the module.

Refer to the Management chapter of the *PICMG 3.0 Specification* for more information about hot swap

#### **Control Elements**

The ATCA-C110/1G provides the following elements as man-machine interface:

- Injector/Ejector Lever and Hot Swap Switch Mechanism on page 18

- Blue hot-swap LED (see Face plate and LEDs on page 51)

#### Injector/Ejector Lever and Hot Swap Switch Mechanism

The Hot Swap micro-switch is activated by the ATCA-C110/1G board ejector handles' mechanism during the board insertion and extraction. This switch is used to confirm insertion or to indicate a request for extraction to the IPMC.

The following illustrations show the typical blade ejector handles used with the ATCA-C110/1G payload cards. All handles are compliant with the AdvancedTCA specification and are designed to meet the IEEE1101.10 standards. The handles facilitate insertion, locking and extraction of the board. It includes the hot-swap micro-switch mounted on the board PCB. The board handles are used to activate the micro-switch, which is the Hot Swap Switch, and to extract the board by pulling it out of the ATCA slot from the chassis.

**Note** The hot-swap switch contacts should be in the OFF position (high-resistance) when the board handles are fully inserted.

### Figure 1-12. Injector/Ejector Lever Types for ATCA-C110/1G

## **Verify Slot Usage**

Prevent possible damage to module components by verifying the proper slot usage for your configuration.

In most cases, connector keying will prevent insertion of a board into an incompatible slot. However, as an extra precaution, you should be familiar with colored card rails used to indicate slot purpose.

Table 1-3 lists the colors and glyphs common to the Embedded Communications Computing chassis.

#### Table 1-3. Slot Usage Indicators

| Card Rail Color | Usage                            |  |

|-----------------|----------------------------------|--|

| Black           | AXP: Shelf Manager slot (slot 0) |  |

| Black           | AXP: Payload Card slot           |  |

| Red             | AXP: Controller Switch Card slot |  |

## Installing the ATCA-C110/1G in a Powered Chassis

This section describes a recommended procedure for installing the ATCA-C110/1G blade into the platform. Before you install your board, please read all cautions, warnings, and instructions presented in this section and the guidelines explained in Before You Install or Remove an AdvancedTCA Blade on page 16. Refer to Figure 1-13 on page 20 and perform these steps when installing the board. Note that this illustration is for general reference only and may not accurately depict the connectors and handles on the board you are installing.

**Note** The ATCA-C110/1G is designed to operate as an AdvancedTCA node board. Refer to *Verify Slot Usage* on page 19 for more details. The installation procedure assumes that the board is being hot-inserted into a live chassis. The procedure for a cold insertion (when the chassis is not powered) is the same, except that you need not wait for the blue LED indications to proceed.

Handling modules and peripherals can result in static damage. Use a grounded wrist strap, static-dissipating work surface, and antistatic containers when handling and storing components.

Wrist Strap

Insert the blade by holding the injector levers—do not exert unnecessary pressure on the face plate.

### Figure 1-13. ATCA-C110/1G Installation

Step 1:Open the injector levers of your board (Stage 1 in Figure 1-13).

- **Step 2:**Verify the proper slot for the carrier board you are inserting (see *Verify Slot Usage* on page 19). Align the edges of the carrier board with the card cage rail guides in the appropriate slot.

- Step 3:Using your thumbs, apply equal and steady pressure as necessary to carefully slide the carrier board into the card cage rail guides (Stage 2 in Figure 1-13). Continue to gently push until the blade connectors engage with the backplane connector. DO NOT FORCE THE BOARD INTO THE BACKPLANE SLOT.

**Note** If a Rear Transition Module (RTM) is already installed in the same slot, be careful not to bend any pins of the RTM connectors.

- **Step 4:**Wait until the blue LED is illuminated. The blue LED indicates that the blade announces its presence to the Shelf Management Controller.

- **Step 5:** If the levers do not completely latch, remove the carrier board from the shelf and visually inspect the slot to ensure there are no bent pins.

- Step 6:When the carrier board you are installing is completely seated, release the handles to activate the switch (Stage 3 in Figure 1-13). Wait for the blue LED to switch off. This indicates the board is active. Secure it by tightening the captive screws at both ends of the face plate.

**Note** If a (RTM) is connected to the front blade, make sure that the handles of both the RTM and the front blade are closed in order to power up the blade's payload.

Step 7:Connect cables to face plate, if applicable.

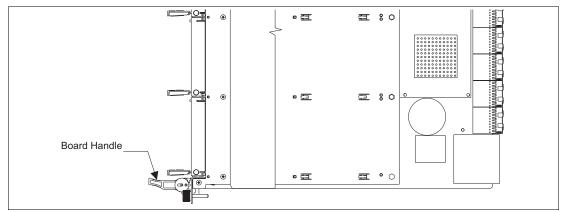

## **Removing the ATCA-C110/1G from a Powered Chassis**

Before you remove your carrier board, please read all cautions, warnings, and instructions presented in this section and the guidelines explained in *Before You Install or Remove an AdvancedTCA Blade* on page 16. Refer to the following illustration and perform these steps when removing the carrier board.

Hot swap compliant boards may be installed while the system is powered on. If a board is not hot swap compliant, you should remove power to the slot or system before installing the board. See *Understand Hot Swap* on page 18 for more information.

**Note** The removal procedure assumes that the board is being removed from a live chassis. The procedure for removing the board when the chassis is not powered is the same, except that you need not wait for the blue LED indications to proceed.

#### Data loss

Removing the blade with the blue LED still blinking causes data loss. Wait until the blue LED is permanently illuminated, before removing the blade.

Figure 1-14. ATCA-C110/1G Removal

Step 1:Remove face plate cables and cables from the AMC, if applicable.

Step 2:Loosen the board's captive screws.

- Step 3:Gently pull the top and bottom ejector handles outward from its locked position (Stage 2 of Figure 1-14).

- **Step 4:**Do not remove the board immediately. Wait for the blue LED first perform short blinks, and then glow persistently. If the blue LED fails to respond refer to Appendix A, *Troubleshooting*.

**Note** Please wait for the blue LED to glow persistently before proceeding to the next step. Unlatching this ejector lever will start the shutdown process on the blade. Software will illuminate the blue hot swap LED on the faceplate when it is safe to remove the blade.

- **Step 5:**Once the blue LED glows, gently pull handles outwards to disconnect the board from the baokplane connectors. Continue to gently slide the board outwards along the guide rails.

- **Step 6:**After board removal is complete, place the board on a clean and adequately protected working surface (preferably an ESD mat) with the top side of the board facing up.

## **Connecting to Peripherals**

When the ATCA-C110/1G is installed in a shelf, you are ready to connect peripherals.

Figure 1-1 on page 3 depicts the location of the different connectors onboard the ATCA-C110/1G and Table 1-4 on page 23 lists the different connectors onboard the ATCA-C110/1G. Refer to Chapter 5, *Controls, Indicators and Connector Pin Assignments*, for the pin assignments of the connectors.

### Table 1-4. ATCA-C110/1G Onboard Connectors

| Connector             | Function          |

|-----------------------|-------------------|

| J1                    | Zone 1 Connectors |

| J20, J21, J22 and J23 | Zone 2 Connectors |

| J30, J31 and J32      | Zone 3 Connectors |

| J1, J2, J3, J4        | FIM Connectors    |

| J38, J39, J40, J41    | AMC Connectors    |

You may access the standard serial console port via the ARTM-C110. This serial port serves as the U-Boot and operating system (OS) console port. Refer to Chapter 3, *U-Boot Firmware Overview*, for information on configuring the U-Boot. The console should be set up as follows:

### Table 1-5. Serial Port Configuration Parameters for MPC8540

| Parameter    | Setting   |

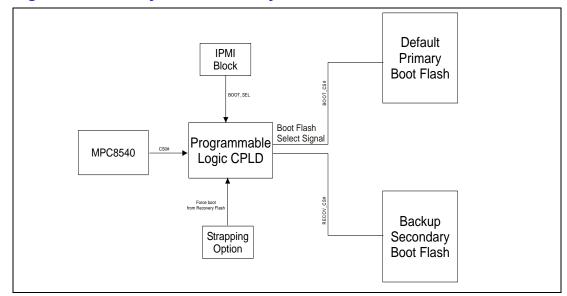

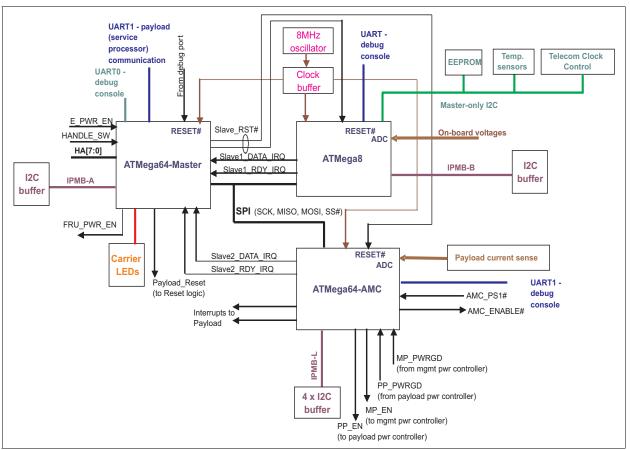

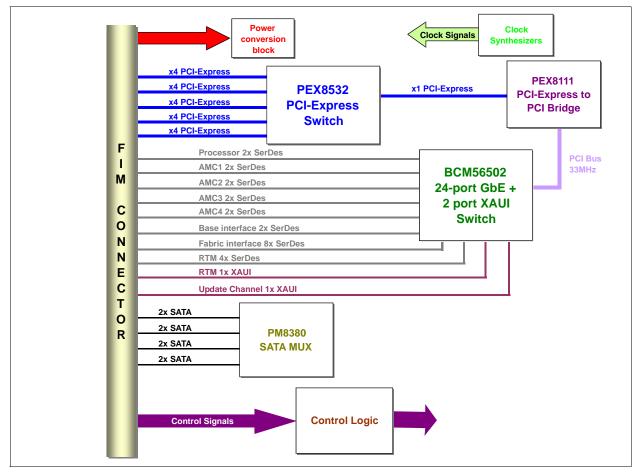

|--------------|-----------|