## SpW-10X SpaceWire Router

User Manual

Ref.: **UoD\_SpW-10X\_**

**UserManual**

Issue: 3.4

Date: 11<sup>th</sup> July 2008

# SpW-10X SpaceWire Router User Manual

Ref: UoD\_SpW-10X\_UserManual

Atmel Part No.: AT7910E

Document Revision: Issue 3.4

Date: 11<sup>th</sup> July 2008

Prepared by - Chris McClements, University of Dundee

Steve Parkes, University of Dundee Gerald Kempf, Austrian Aerospace

Checked by - Steve Parkes, University of Dundee

ESA Manager - Pierre Fabry, ESTEC

## **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

UserManual Issue: 3.4

Date: 11<sup>th</sup> July 2008

**Document Change log**

| Date                            | Issue     | Comments                                                                                                                                                    | Author                            |

|---------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 19 <sup>th</sup> -March-2004    | Issue 1.0 | Initial draft version                                                                                                                                       | Chris McClements                  |

| 26 <sup>th</sup> -August-2004   | Issue 1.2 | Timing for FPGA model added                                                                                                                                 | Chris McClements                  |

| 16 November 2004                | Issue 1.3 | Register Definitions Updated                                                                                                                                | Chris McClements                  |

| 27 April 2004                   | Issue 1.4 | Latency and Jitter Specifications added                                                                                                                     | Chris McClements                  |

| 2 May 2005                      | Issue 1.5 | Footer indicates "Preliminary."  Section 8.6 subject to change                                                                                              | Steve Parkes                      |

|                                 |           | notice added to front page.                                                                                                                                 |                                   |

| 21 December 2005                | Issue 1.6 | RMAP section added                                                                                                                                          | Chris McClements                  |

| 19 <sup>th</sup> July 2006      | Issue 1.7 | Corrections and clarifications                                                                                                                              | Chris McClements                  |

| 18 <sup>th</sup> August 2006    | Issue 2.0 | Editorial changes and clarifications                                                                                                                        | Steve Parkes                      |

| 3 <sup>rd</sup> July 2007       | Issue 2.1 | Added sections on ASIC pin placement, ASIC power consumption, bias resistors, phase locked loop and anomalies.                                              | Chris McClements Steve Parkes     |

| 28 <sup>th</sup> September 2007 | Issue 2.2 | Modifications before handed to Atmel                                                                                                                        | Chris McClements,<br>Gerald Kempf |

| 4 <sup>th</sup> October 2007    | Issue 2.3 | Modifications to SpaceWire signal names (Map pin 1 to 0)                                                                                                    | Chris McClements,<br>Gerald Kempf |

| 3 <sup>rd</sup> December 2007   | Issue 2.4 | Updates as user manual. Changed document name to UoD_SpW_10X_UserManual.doc                                                                                 | Chris McClements,<br>Gerald Kempf |

| 11 <sup>th</sup> December 2007  | Issue 2.5 | Redistribute with PLL settings                                                                                                                              | Chris McClements<br>Gerald Kempf  |

| 18 <sup>th</sup> January 2008   | Issue 3.0 | Major edit providing clarifications and additional application details throughout document.  Section added on Application Guidelines giving example circuit | Steve Parkes                      |

|                                 |           | diagram and PCB layout                                                                                                                                      |                                   |

## **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

UserManual

Issue: 3.4

|                               |           | guidelines.                                         |              |

|-------------------------------|-----------|-----------------------------------------------------|--------------|

|                               |           | Section added on anomalies and warnings.            |              |

|                               |           | Section added on Technical Support.                 |              |

| 20 <sup>th</sup> January 2008 | Issue 3.1 | Corrections and example schematic improved.         | Steve Parkes |

| 18 <sup>th</sup> April 2008   | Issue 3.2 | Explanation of non-blocking cross bar switch added. | Steve Parkes |

|                               |           | Cold sparing information added.                     |              |

|                               |           | VCO bias resistor value corrected (Section 5.7.4).  |              |

|                               |           | Tri-state mode changed to deactivate mode.          |              |

|                               |           | Description for 'time-code flag mode bit' added.    |              |

|                               |           | Reliability information added.                      |              |

|                               |           | Anomaly 2 resolved.                                 |              |

|                               |           | Details and workarounds for reset anomaly provided. |              |

| 30 <sup>th</sup> April 2008   | Issue 3.3 | RD 3 changed.                                       | Steve Parkes |

|                               |           | Editorial corrections.                              |              |

|                               |           | Correction to reset value of GAR table entry.       |              |

|                               |           | Correction to support email address.                |              |

| 11 <sup>th</sup> July         | Issue 3.4 | Data after parity error anomaly added.              | Steve Parkes |

|                               |           | Detailed timing information added.                  | Gerald Kempf |

|                               |           | DC characteristics updated.                         |              |

# SpW-10X SpaceWire Router

**User Manual**

Ref.: **UoD\_SpW-10X\_ UserManual**

Issue: 3.4

Date: 11<sup>th</sup> July 2008

### **CONTENTS**

| CO         | ONTENTS                              | 4  |

|------------|--------------------------------------|----|

| ı          | LIST OF FIGURES                      | 10 |

| II         | LIST OF TABLES                       | 12 |

| 1.         | INTRODUCTION                         | 14 |

| 1.1        | TERMS, ACRONYMS AND ABBREVIATIONS    | 14 |

| 1.2        | 2 DOCUMENTS                          | 15 |

| 2.         | USER APPLICATIONS                    | 16 |

| 2.1        | STAND-ALONE ROUTER                   | 16 |

| 2.2        | NODE INTERFACE                       | 17 |

| 2.3        | B EMBEDDED ROUTER                    | 17 |

| 2.4        | EXPANDING THE NUMBER OF ROUTER PORTS | 18 |

| 3.         | FUNCTIONAL OVERVIEW                  | 21 |

| 3.1        | SPACEWIRE PORTS                      | 22 |

| 3.2        | 2 EXTERNAL PORTS                     | 22 |

| 3.3        | CONFIGURATION PORT                   | 23 |

| 3.4        | ROUTING TABLE                        | 23 |

| 3.5        | ROUTING CONTROL LOGIC AND CROSSBAR   | 23 |

| 3.6        | TIME-CODE PROCESSING                 | 24 |

| 3.7        | CONTROL/STATUS REGISTERS             | 24 |

| 4.         | PIN LOCATIONS                        | 25 |

| 5.         | DEVICE INTERFACE                     | 31 |

| 5.1        | GLOBAL SIGNALS                       | 31 |

| 5.2        |                                      |    |

| 5.2        | , , ,                                |    |

| 5.2<br>5.2 | ·                                    |    |

## **SpaceWire Router**

### **User Manual**

Ref.: **UoD\_SpW-10X\_ UserManual**

Issue: **3.4**

| 5.3       | EXTERNAL PORT DATA SIGNALS              | . 37 |

|-----------|-----------------------------------------|------|

| 5.4       | TIME-CODE SIGNALS                       | . 39 |

| 5.5       | STATUS INTERFACE SIGNALS                | . 41 |

| 5.6       | RESET CONFIGURATION SIGNALS             | . 42 |

| 5.7       | POWER, GROUND, PLL AND LVDS SIGNALS     | . 45 |

| 5.7.1     | General                                 | . 45 |

| 5.7.2     |                                         |      |

| 5.7.3     | LVDS Reference                          | . 45 |

| 5.7.4     | PLL External Components                 | . 45 |

| <b>6.</b> | INTERFACE OPERATIONS                    | . 47 |

| 6.1       | EXTERNAL PORT INTERFACE OPERATION       | . 47 |

| 6.2       | TIME-CODE INTERFACE OPERATION           | . 48 |

| 6.3       | STATUS INTERFACE OPERATION              | . 49 |

| 6.4       | RESET CONFIGURATION INTERFACE OPERATION | . 51 |

| 7.        | SPACEWIRE ROUTER PACKET TYPES           | . 52 |

| 7.1       | PACKET ADDRESSES                        | . 52 |

| 7.2       | PACKET PRIORITY                         | . 53 |

| 7.3       | PACKET HEADER DELETION                  | . 53 |

| 7.4       | INVALID ADDRESSES                       | . 54 |

| 7.5       | DATA PACKETS                            | . 55 |

| 7.6       | COMMAND PACKETS                         | . 55 |

| 7.6.1     | Supported Commands                      | . 55 |

| 7.6.2     | Read Command                            | 56   |

| 7.6.3     | Read Incrementing Command               | . 60 |

| 7.6.4     | ,                                       |      |

| 7.6.5     |                                         |      |

| 7.6.6     | Command Error Response                  | . 74 |

| 7.6.7     | ,                                       |      |

| 7.6.8     |                                         |      |

| 7.6.9     |                                         |      |

| 7.6.1     | 0 Command Packet Fill Bytes             | . 78 |

| 8.        | CONTROL LOGIC AND OPERATIONAL MODES     | . 79 |

| 8.1       | SPACEWIRE LINK CONTROL                  |      |

| 8.1.1     | Default operating mode                  | . 79 |

## **SpaceWire Router**

### **User Manual**

Ref.: **UoD\_SpW-10X\_ UserManual**

Issue: **3.4**

| 8.1.2 Auto-Start                                           | 79  |

|------------------------------------------------------------|-----|

| 8.1.3 Link-Start                                           | 79  |

| 8.1.4 Link-Disable                                         | 80  |

| 8.1.5 Automatic deactivate driver mode                     | 80  |

| 8.1.6 Setting the SpaceWire port transmit data rate        | 82  |

| 8.2 GLOBAL SPACEWIRE LINK CONTROL                          | 84  |

| 8.2.1 Start on request mode                                | 85  |

| 8.2.2 Disable on Silence mode                              | 85  |

| 8.3 CONTROL LOGIC AND ROUTING                              | 86  |

| 8.3.1 Packet address error                                 | 86  |

| 8.3.2 Arbitration                                          | 86  |

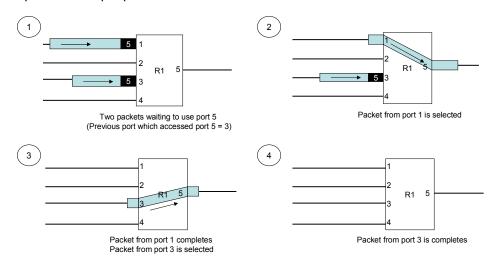

| 8.3.2.1 Arbitration of packets with matching priority (1)  | 87  |

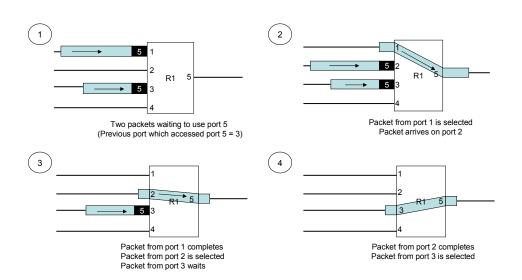

| 8.3.2.2 Arbitration of packets with matching priority (2)  | 88  |

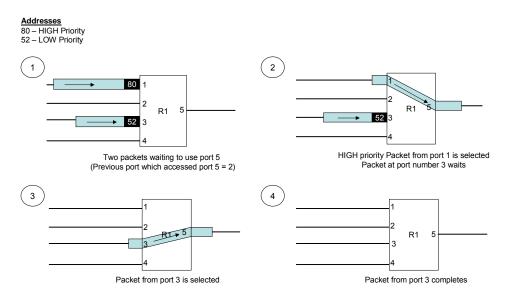

| 8.3.2.3 Arbitration of packets with different priority (1) | 89  |

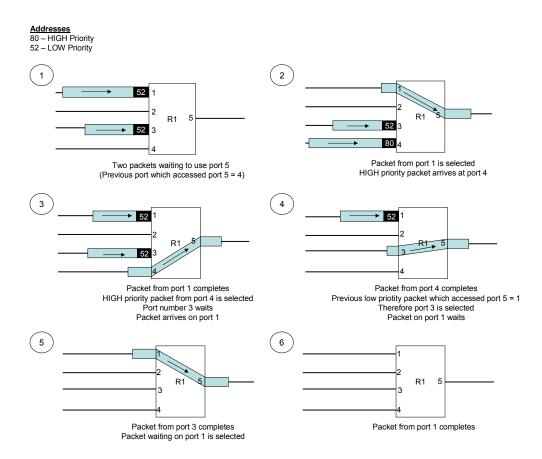

| 8.3.2.4 Arbitration of packets with different priority (2) | 90  |

| 8.3.3 Group Adaptive Routing                               | 92  |

| 8.3.3.1 Normal Group adaptive routing                      | 92  |

| 8.3.3.2 Group adaptive routing when busy                   | 92  |

| 8.3.3.3 Group adaptive routing when ports not ready        | 93  |

| 8.3.4 Loop-back with Self-Addressing                       | 93  |

| 8.3.5 Packet Blocking                                      | 95  |

| 8.3.5.1 Blocked destination                                | 95  |

| 8.3.5.2 Stalled source                                     | 98  |

| 8.3.5.3 Waiting for an output port                         | 101 |

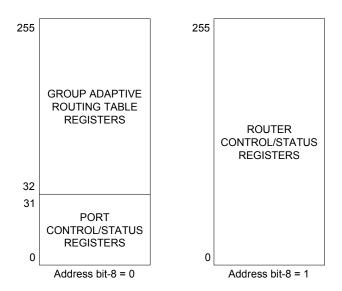

| 9. REGISTER DEFINITIONS                                    | 103 |

| 9.1 INTERNAL MEMORY MAP                                    | 103 |

| 9.2 REGISTER ADDRESSES SUMMARY                             | 104 |

| 9.3 GROUP ADAPTIVE ROUTING TABLE REGISTERS                 | 105 |

| 9.4 PORT CONTROL/STATUS REGISTERS                          | 108 |

| 9.4.1 Generic port control/status register fields.         |     |

| 9.4.2 Configuration port control/status register fields.   |     |

| 9.4.3 SpaceWire port control/status register bits.         |     |

| 9.4.4 External port control/status register bits           |     |

| 9.5 ROUTER CONTROL/STATUS REGISTERS                        |     |

| 9.5.1 Network Discovery Register                           |     |

| 9.5.2 Router Identity Register                             |     |

| 9.5.3 Router Control Register                              |     |

| 9.5.4 Error active Register                                |     |

| = =                                                        | 120 |

## **SpaceWire Router**

### **User Manual**

Ref.: UoD\_SpW-10X\_

UserManual

Issue: **3.4**

| 9.5.5 Time-Code Register                              | 121      |

|-------------------------------------------------------|----------|

| 9.5.6 Device Manufacturer and Chip ID Register        |          |

| 9.5.7 General Purpose Register                        | 123      |

| 9.5.8 Time-Code Enable Register                       | 123      |

| 9.5.9 Transmit Clock Control Register                 | 124      |

| 9.5.10 Destination Key Register                       | 127      |

| 9.5.11 Unused Registers and Register Bits             |          |

| 9.5.12 Empty packets                                  |          |

| 9.6 WRITING TO A READ-ONLY REGISTER                   | 127      |

| 10. SWITCHING CHARACTERISTICS                         | 128      |

| 10.1 CLOCK AND RESET TIMING PARAMETERS                |          |

| 10.2 SERIAL SIGNALS TIMING PARAMETERS                 | 128      |

| 10.3 EXTERNAL PORT TIMING PARAMETERS                  |          |

| 10.4 TIME-CODE INTERFACE TIMING PARAMETERS            | S 130    |

| 10.5 ERROR/STATUS INTERFACE TIMING PARAME             | TERS 131 |

| 10.6 LATENCY AND JITTER                               | 133      |

| 10.6.1 Clock Periods                                  | 133      |

| 10.6.2 Switching Latency                              |          |

| 10.6.3 Router Latency                                 |          |

| 10.6.4 Time-code Latency                              |          |

| 10.6.5 Time-code Jitter                               |          |

| 10.6.6 200M bits/s Input and Output Bit Rate Example. |          |

| 11. ELECTRICAL CHARACTERISTICS                        | 136      |

| 11.1 DC CHARACTERISTICS                               | 136      |

| 11.2 ABSOLUTE MAXIMUM RATINGS                         |          |

| 11.3 RELIABILITY INFORMATION                          |          |

| 12. APPLICATION GUIDELINES                            | 138      |

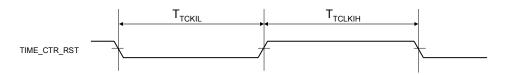

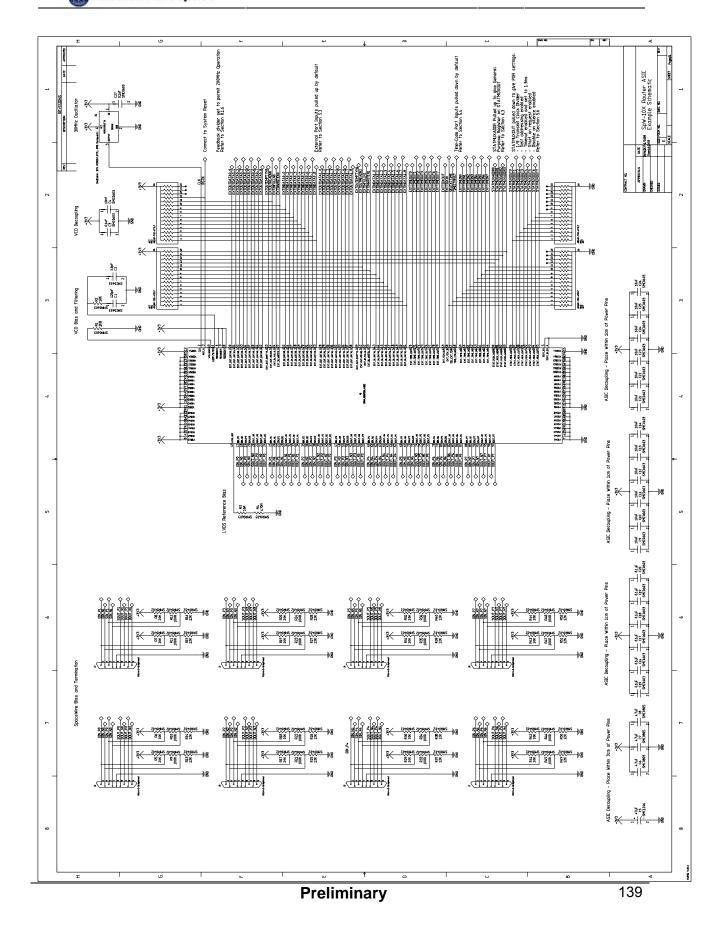

| 12.1 EXAMPLE CIRCUIT DIAGRAM                          | 138      |

| 12.2 PCB DESIGN AND LAYOUT GUIDELINES                 |          |

| 12.2.1 CLK                                            |          |

| 12.2.2 RST_N                                          |          |

| 12.2.3 Chip Test Signals                              |          |

| 12.2.4 Power and Decoupling                           |          |

| 12.2.5 Ground                                         |          |

| 12.2.6 SpaceWire                                      | 140      |

15.5

15.6

15.7

15.8

15.9

15.10

15.11

15.12

15.13

15.14

15.15

# SpW-10X

### **SpaceWire Router**

#### **User Manual**

Ref.: UoD\_SpW-10X\_ UserManual

Issue: 3.4

Date: 11th July 2008

ISSUE 1.3 TO ISSUE 1.4...... 154

### **SpaceWire Router**

### **User Manual**

Ref.: UoD\_SpW-10X\_

UserManual

Issue: **3.4**

| 15.16 | ISSUE 1.2 TO ISSUE 1.3 | 154 |

|-------|------------------------|-----|

| 15.17 | ISSUE 1.1 TO ISSUE 1.2 | 155 |

| 15.18 | ISSUE 1.0 TO ISSUE 1.1 | 155 |

## **SpaceWire Router**

### **User Manual**

Ref.: **UoD\_SpW-10X\_ UserManual**

Issue: **3.4**

Date: 11<sup>th</sup> July 2008

### I LIST OF FIGURES

| FIGURE 2-1 STAND-ALONE ROUTER                                                               | 16 |

|---------------------------------------------------------------------------------------------|----|

| Figure 2-2 Node Interface                                                                   | 17 |

| Figure 2-3 Embedded Router                                                                  | 18 |

| FIGURE 2-4 EXPANDING THE NUMBER OF SPACEWIRE PORTS (1)                                      | 19 |

| FIGURE 2-5 EXPANDING THE NUMBER OF SPACEWIRE PORTS (2)                                      | 20 |

| FIGURE 3-1 SPACEWIRE ROUTER BLOCK DIAGRAM                                                   | 22 |

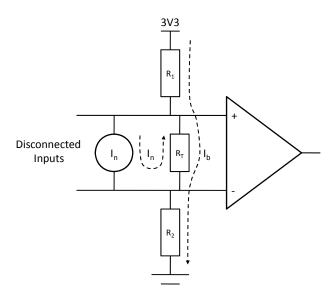

| Figure 5-1 LVDS Receiver Fail-Safe Resistors                                                | 35 |

| FIGURE 5-2 CONFIGURATION INTERFACE TIMING SPECIFICATION                                     | 42 |

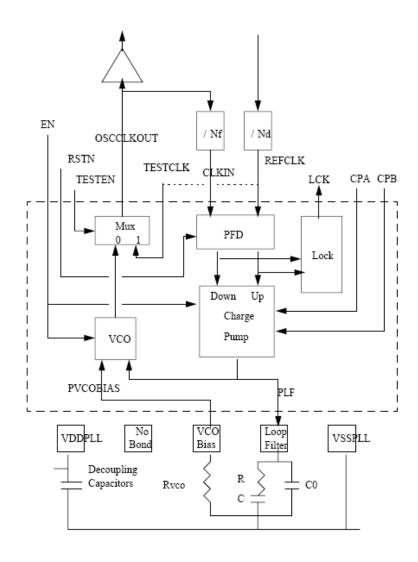

| FIGURE 5-3 PLL WITH EXTERNAL COMPONENTS                                                     | 46 |

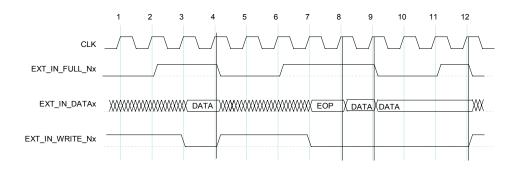

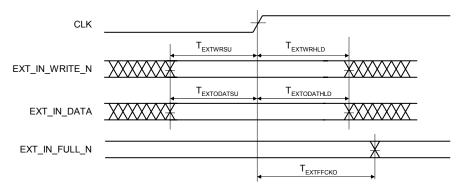

| FIGURE 6-1 EXTERNAL PORT WRITE TIMING SPECIFICATION                                         | 47 |

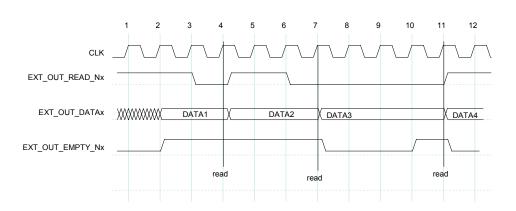

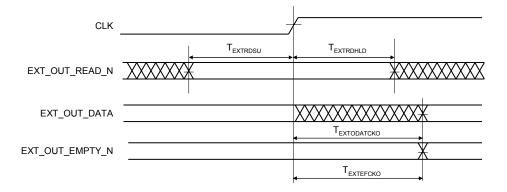

| FIGURE 6-2 EXTERNAL PORT READ TIMING SPECIFICATION                                          | 48 |

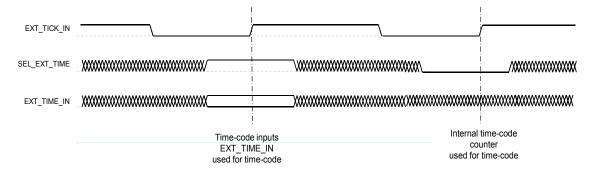

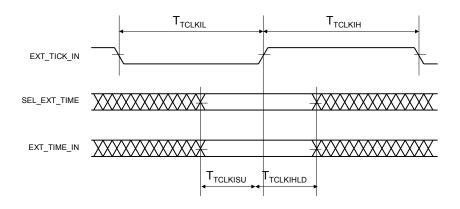

| FIGURE 6-3 TIME-CODE INPUT INTERFACE                                                        | 48 |

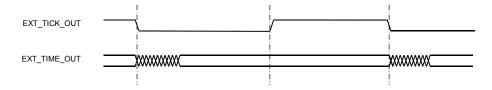

| FIGURE 6-4 TIME-CODE OUTPUT INTERFACE                                                       | 49 |

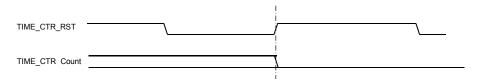

| FIGURE 6-5 TIME-CODE RESET INTERFACE                                                        | 49 |

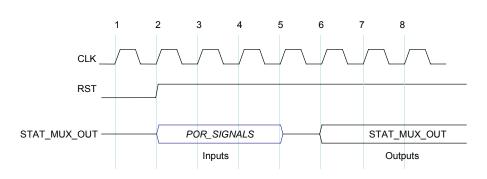

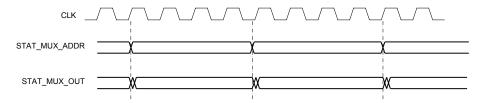

| FIGURE 6-6 STATUS MULTIPLEXER OUTPUT INTERFACE                                              | 49 |

| FIGURE 6-7 RESET CONFIGURATION INTERFACE TIMING SPECIFICATION                               | 51 |

| Figure 7-1 Normal router data packets                                                       | 55 |

| FIGURE 7-2 COMMAND PACKET FORMAT                                                            | 55 |

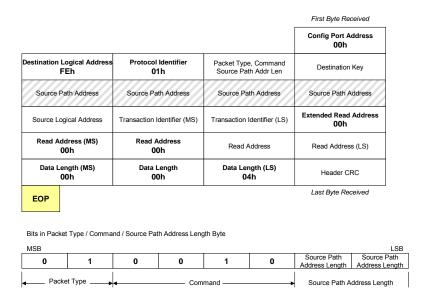

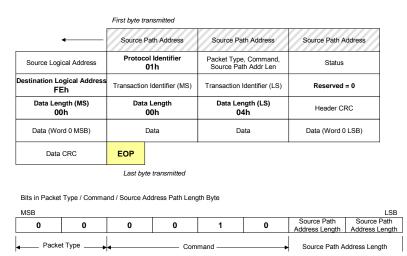

| FIGURE 7-3 READ SINGLE ADDRESS COMMAND FORMAT                                               | 57 |

| FIGURE 7-4 READ SINGLE ADDRESS REPLY PACKET FORMAT                                          | 59 |

| FIGURE 7-5 READ INCREMENTING ADDRESS COMMAND FORMAT                                         | 62 |

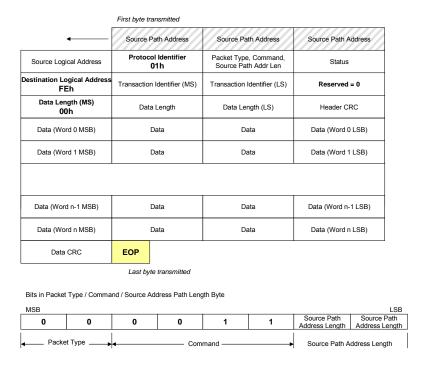

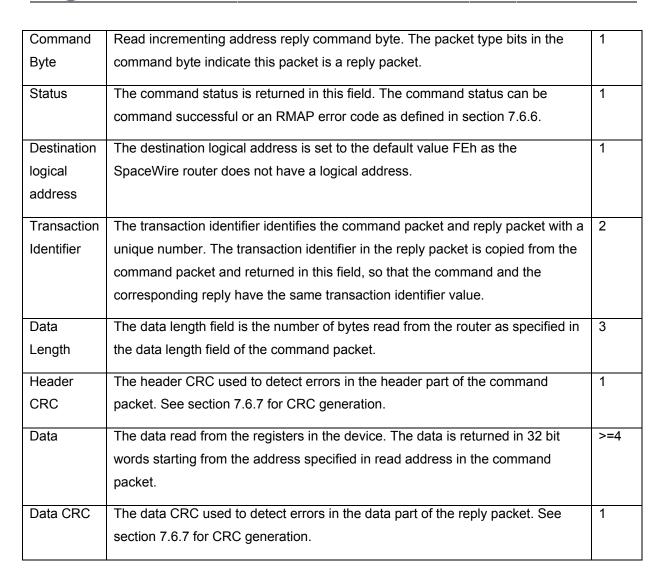

| FIGURE 7-6 READ INCREMENTING ADDRESS REPLY PACKET FORMAT                                    | 64 |

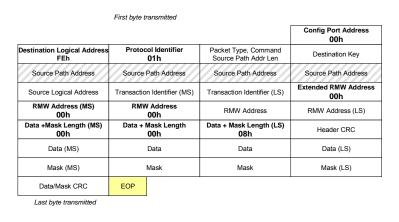

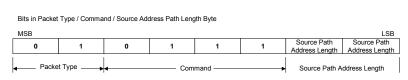

| FIGURE 7-7 READ-MODIFY-WRITE COMMAND PACKET FORMAT                                          | 66 |

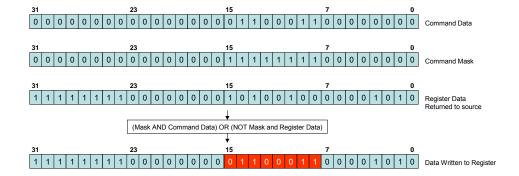

| FIGURE 7-8 READ-MODIFY-WRITE EXAMPLE OPERATION                                              | 68 |

| FIGURE 7-9 READ-MODIFY-WRITE REPLY PACKET FORMAT                                            | 69 |

| FIGURE 7-10 WRITE SINGLE ADDRESS COMMAND PACKET                                             | 71 |

| FIGURE 7-11 WRITE SINGLE ADDRESS REPLY PACKET                                               | 73 |

| Figure 7-12 Source Path Address field decoding                                              | 78 |

| FIGURE 7-13 SOURCE PATH ADDRESSES IN REPLY PACKET                                           | 78 |

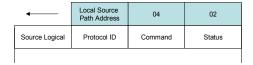

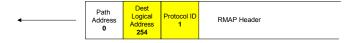

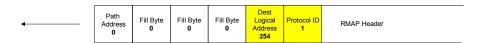

| FIGURE 7-14 NORMAL CONFIGURATION PACKET HEADER STRUCTURE                                    | 78 |

| FIGURE 7-15 FILL BYTES CONFIGURATION HEADER STRUCTURE                                       | 78 |

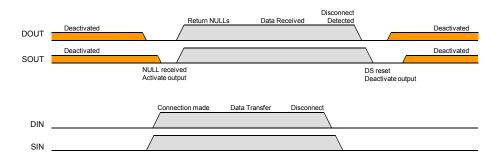

| FIGURE 8-1 DEACTIVATE DRIVER OPERATING MODE                                                 | 81 |

| FIGURE 8-2 DEACTIVATED LDVS DRIVER OUTPUT                                                   | 81 |

| FIGURE 8-3 DEACTIVATED LDVS DRIVER OUTPUT CONNECTED TO EXTERNAL BIAS NETWORK ON LVDS INPUT. | 82 |

| Figure 8-4 Start on Request mode                                                            | 85 |

| FIGURE 8-5 DISABLE ON SILENCE MODE                                                          | 86 |

| FIGURE 8-6 ARBITRATION OF TWO PACKETS WITH MATCHING PRIORITY.                               | 87 |

| FIGURE 8-7 ARBITRATION OF THREE PACKETS WITH MATCHING PRIORITY                              | 88 |

|                                                                                             |    |

## **SpaceWire Router**

### **User Manual**

Ref.: **UoD\_SpW-10X\_ UserManual**

Issue: **3.4**

| FIGURE 8-8 ARBITRATION OF TWO PACKETS WITH DIFFERENT PRIORITY (1)   | 89  |

|---------------------------------------------------------------------|-----|

| FIGURE 8-9 ARBITRATION OF TWO PACKETS WITH DIFFERENT PRIORITY (2)   | 91  |

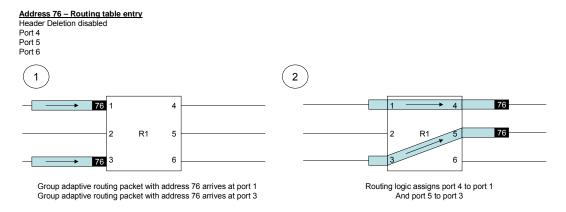

| FIGURE 8-10 NORMAL GROUP ADAPTIVE ROUTING                           | 92  |

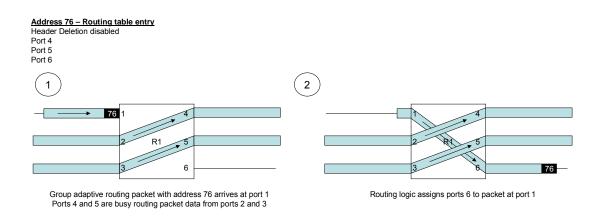

| FIGURE 8-11 GROUP ADAPTIVE ROUTING WHEN OTHER PORTS BUSY            | 93  |

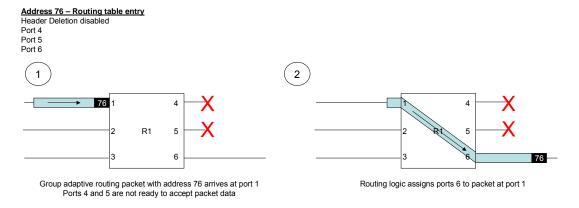

| FIGURE 8-12 GROUP ADAPTIVE ROUTING WHEN PORTS NOT READY             | 93  |

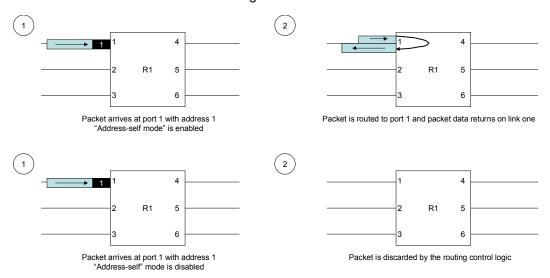

| FIGURE 8-13 PACKET SELF-ADDRESSING MODE                             | 94  |

| FIGURE 8-14 DESTINATION NODE BLOCKED (A)                            | 96  |

| FIGURE 8-15 DESTINATION NODE BLOCKED (B)                            | 96  |

| FIGURE 8-16 DESTINATION NODE BLOCKED (C)                            | 97  |

| FIGURE 8-17 DESTINATION NODE BLOCKED: WATCHDOG MODE (A)             | 97  |

| FIGURE 8-18 DESTINATION NODE BLOCKED: WATCHDOG MODE (B)             | 97  |

| FIGURE 8-19 DESTINATION NODE BLOCKED: WATCHDOG MODE (C)             | 98  |

| FIGURE 8-20 DESTINATION NODE BLOCKED: WATCHDOG MODE (D)             | 98  |

| FIGURE 8-21 SOURCE NODE STALLED (A)                                 | 99  |

| FIGURE 8-22 SOURCE NODE STALLED (B)                                 | 99  |

| FIGURE 8-23 SOURCE NODE STALLED (C)                                 | 99  |

| FIGURE 8-24 SOURCE NODE STALLED (D)                                 | 99  |

| FIGURE 8-25 SOURCE NODE STALLED: WATCHDOG MODE (A)                  | 100 |

| FIGURE 8-26 SOURCE NODE STALLED: WATCHDOG MODE (B)                  | 100 |

| FIGURE 8-27 SOURCE NODE STALLED: WATCHDOG MODE (C)                  | 100 |

| FIGURE 8-28 SOURCE NODE STALLED: WATCHDOG MODE (D)                  | 100 |

| FIGURE 9-1 ROUTER INTERNAL MEMORY MAP                               | 103 |

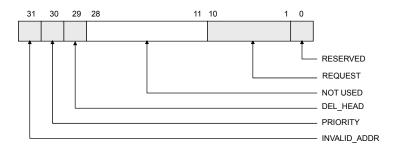

| FIGURE 9-2 GAR REGISTER FIELDS                                      | 105 |

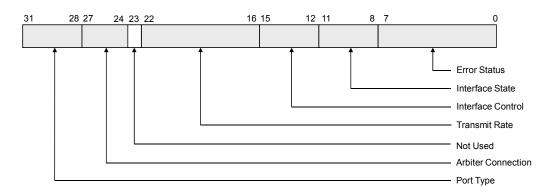

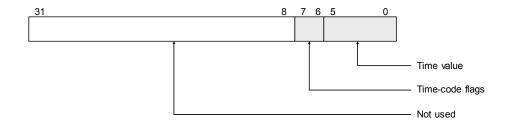

| FIGURE 9-3 SPACEWIRE PORT CONTROL/STATUS REGISTER FIELDS            | 112 |

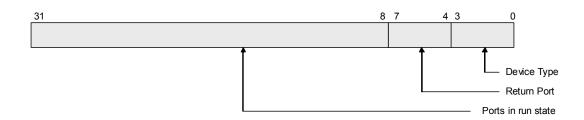

| FIGURE 9-4 NETWORK DISCOVERY REGISTER FIELDS                        | 116 |

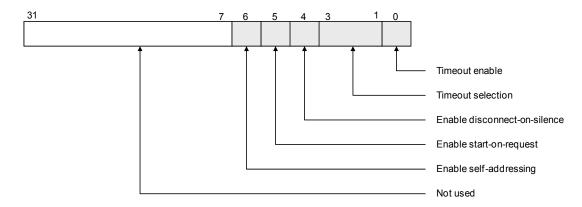

| FIGURE 9-5 ROUTER CONTROL REGISTER FIELDS                           | 117 |

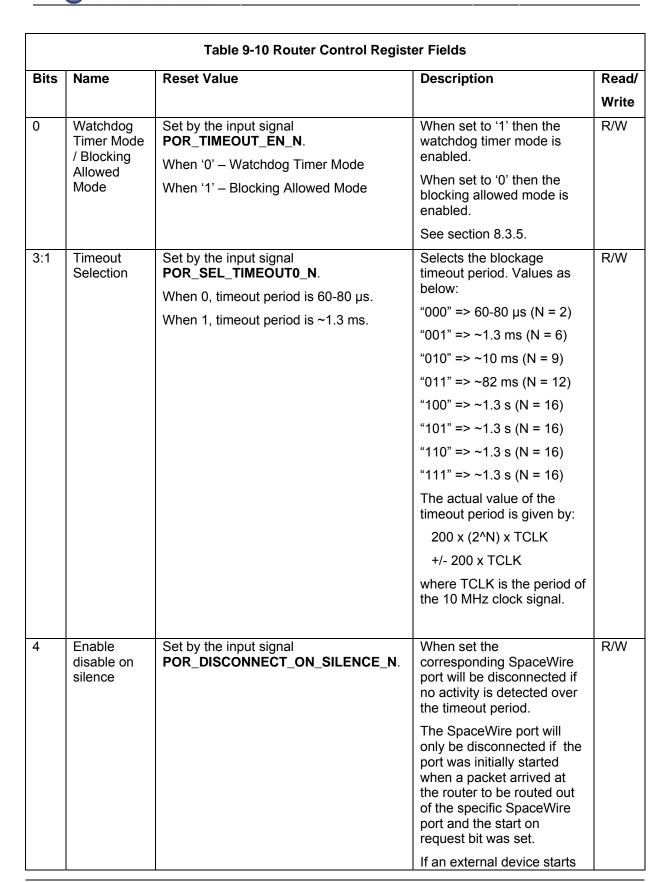

| FIGURE 9-6 ERROR ACTIVE REGISTER FIELDS                             | 120 |

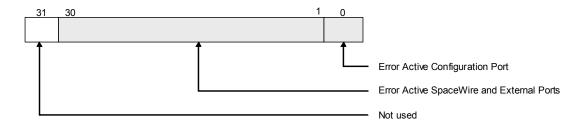

| FIGURE 9-7 TIME-CODE REGISTER FIELDS                                | 121 |

| FIGURE 9-8 DEVICE MANUFACTURER AND CHIP ID REGISTER FIELDS          | 122 |

| FIGURE 9-9 TIME-CODE ENABLE REGISTER FIELDS                         | 123 |

| FIGURE 9-10 TRANSMIT CLOCK CONTROL REGISTER                         | 125 |

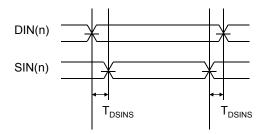

| FIGURE 10-1 DS MINIMUM CONSECUTIVE EDGE SEPARATION                  | 128 |

| FIGURE 10-2 EXTERNAL PORT INPUT FIFO TIMING PARAMETERS              | 129 |

| FIGURE 10-3 EXTERNAL PORT OUTPUT FIFO TIMING PARAMETERS             | 129 |

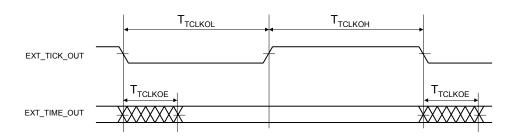

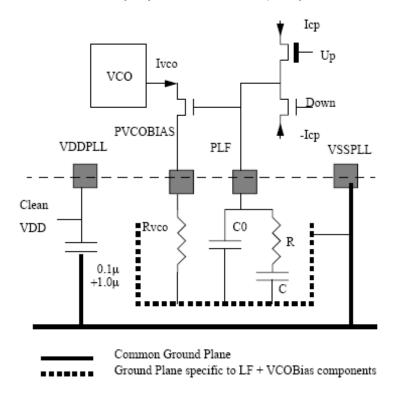

| FIGURE 10-4 TIME-CODE INPUT INTERFACE                               | 130 |

| FIGURE 10-5 TIME-CODE OUTPUT INTERFACE                              |     |

| FIGURE 10-6 TIME_CODE TIME_CTR_RST INTERFACE                        |     |

| FIGURE 12-1 PLL LAYOUT RECOMMENDATIONS.                             | 142 |

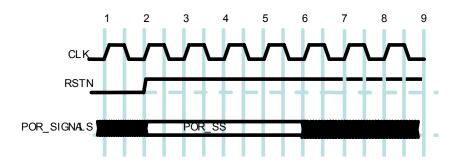

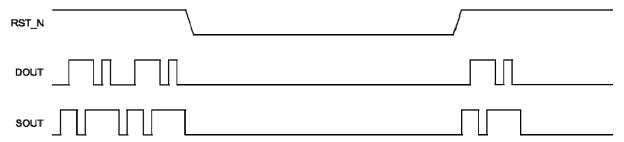

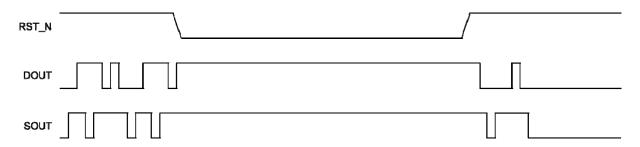

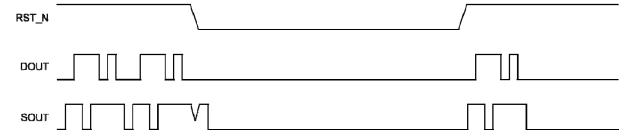

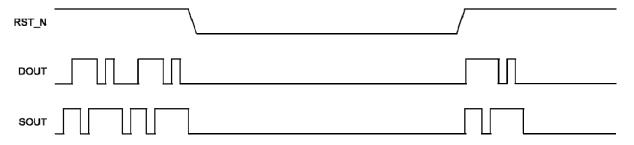

| FIGURE 13-1 RESET WAVEFORM                                          | 146 |

| FIGURE 13-2 RESET WAVEFORM WITH DATA AND STROBE BOTH HIGH           | 146 |

| FIGURE 13-3 GLITCHES ON DATA OR STROBE DURING RESET                 | 146 |

| FIGURE 13-4 SIMULTANEOUS TRANSITION OF DATA AND STROBE DURING RESET | 146 |

# SpW-10X SpaceWire Router

### User Manual

Ref.: **UoD\_SpW-10X\_ UserManual**

Issue: 3.4

Date: 11<sup>th</sup> July 2008

| FIGURE 13-5 LINK DISCONNECT WAVEFORMS                          | 147 |

|----------------------------------------------------------------|-----|

| FIGURE 13-6 DATA AFTER PARITY ERROR ANOMALY                    | 148 |

| FIGURE 13-7 NO ERROR END OF PACKET INSERTED AFTER PARITY ERROR | 149 |

### **II LIST OF TABLES**

| TABLE 1-1 APPLICABLE DOCUMENTS                              |     |

|-------------------------------------------------------------|-----|

| Table 1-2 Reference Documents                               |     |

| Table 5-1 Global Signals                                    |     |

| TABLE 5-2 DATA AND STROBE SPACEWIRE SIGNALS                 |     |

| Table 5-3 External Port Interface Signals                   |     |

| Table 5-4 Time-Code Signals                                 | 39  |

| TABLE 5-5 LINK ERROR INDICATION SIGNALS                     | 41  |

| Table 5-6 Reset Configuration Signals                       | 43  |

| Table 5-7 Power, Ground and Special Signals                 | 45  |

| TABLE 6-1 MULTIPLEXED STATUS PINS BIT ASSIGNMENT            | 50  |

| TABLE 7-1 PACKET ADDRESS MAPPING                            | 52  |

| TABLE 7-2 PACKET PRIORITY MAPPING                           | 53  |

| TABLE 7-3 PACKET HEADER DELETION MAPPING                    | 54  |

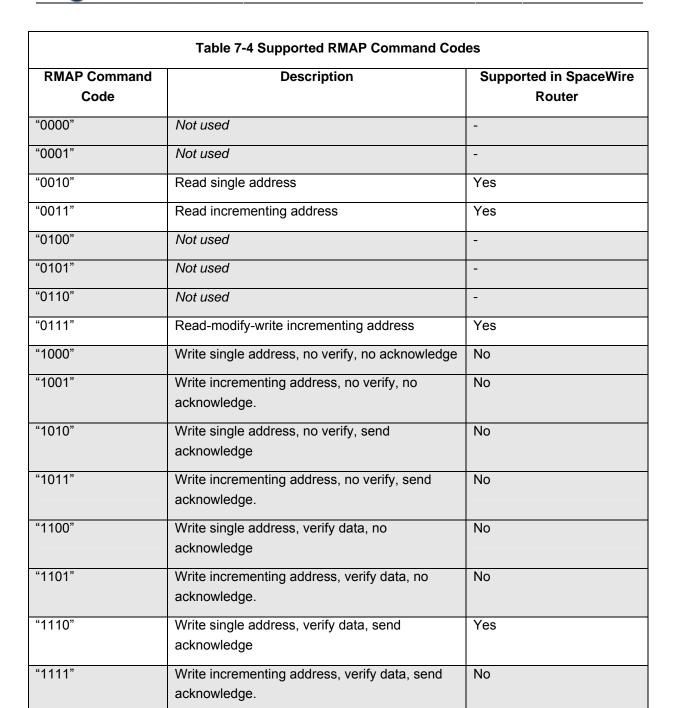

| TABLE 7-4 SUPPORTED RMAP COMMAND CODES                      | 56  |

| Table 7-5 Read Single Address Characteristics               | 57  |

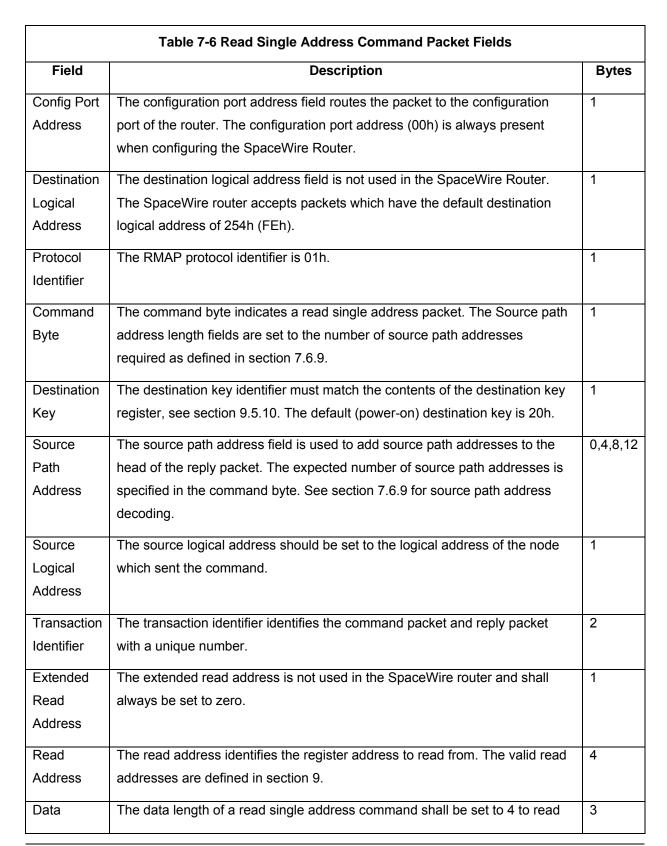

| Table 7-6 Read Single Address Command Packet Fields         | 58  |

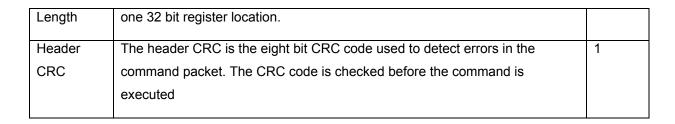

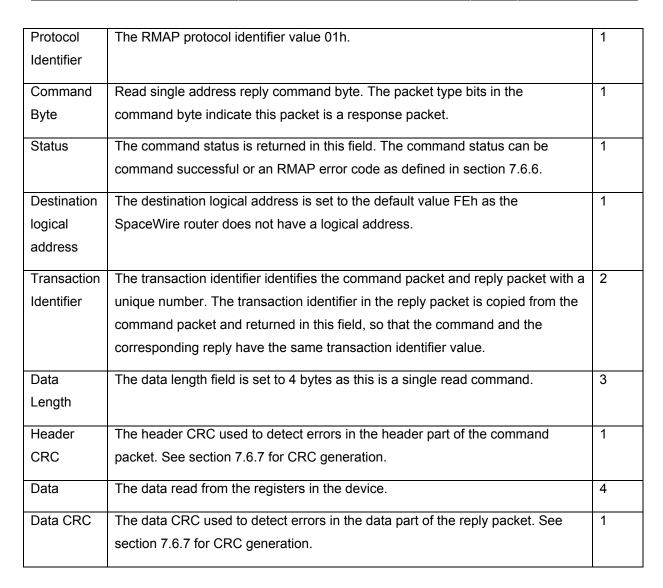

| Table 7-7 Read Single Address Reply Packet Fields           | 59  |

| Table 7-8 Read Incrementing Address Characteristics         | 61  |

| Table 7-9 Read Incrementing Address Command Packet Fields   | 62  |

| Table 7-10 Read Incrementing Address Reply Packet Fields    | 64  |

| Table 7-11 Read-Modify-Write Command Characteristics        | 65  |

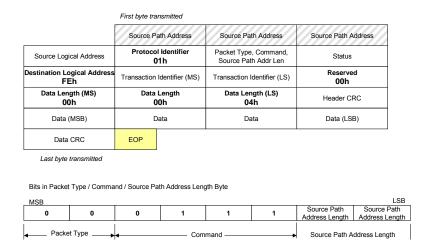

| Table 7-12 Read-Modify-Write Command Packet Fields          | 67  |

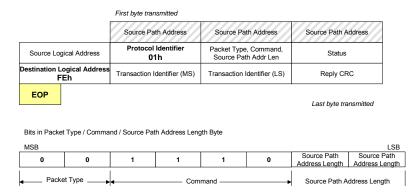

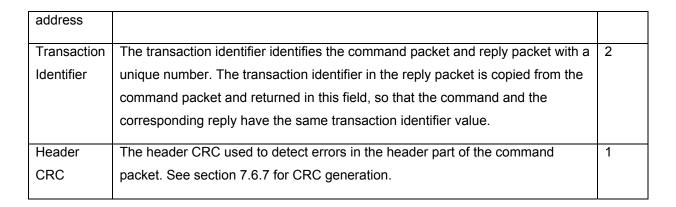

| TABLE 7-13 READ-MODIFY-WRITE REPLY PACKET FIELDS            | 69  |

| Table 7-14 Write Command Characteristics                    | 70  |

| TABLE 7-15 WRITE SINGLE ADDRESS COMMAND PACKET FIELDS       | 71  |

| TABLE 7-16 WRITE SINGLE ADDRESS REPLY PACKET FIELDS         |     |

| Table 7-17 Configuration Port Errors Summary                |     |

| TABLE 7-18 SOURCE PATH ADDRESS REFERENCE TABLE              |     |

| TABLE 8-1 SETTING SPACEWIRE TRANSMIT DATA RATE              |     |

| Table 9-1 Types of Register within Configuration Port       | 104 |

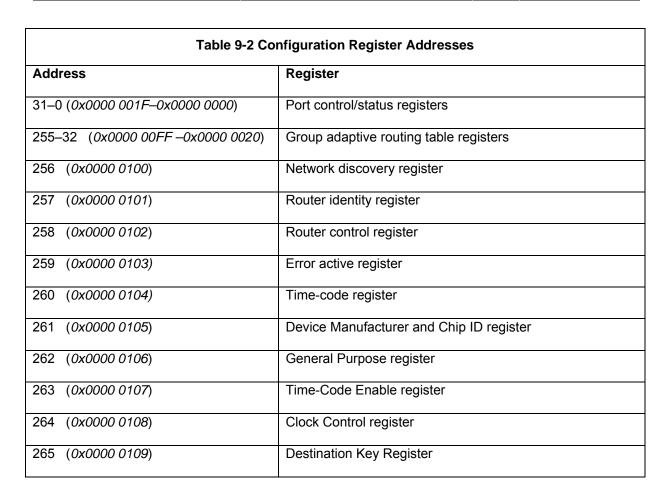

| Table 9-2 Configuration Register Addresses                  |     |

| TABLE 9-3 GAR TABLE REGISTER DESCRIPTION                    |     |

| Table 9-4 Configuration Port Control/Status Register Fields |     |

| Table 9-5 Configuration Port Control/Status Register Fields | 110 |

|                                                             |     |

## **SpaceWire Router**

### **User Manual**

Ref.: **UoD\_SpW-10X\_ UserManual**

Issue: **3.4**

| TABLE 9-6 SPACEWIRE PORT CONTROL/STATUS REGISTER FIELDS.                           | 113 |

|------------------------------------------------------------------------------------|-----|

| Table 9-7 External Port Control/Status Fields                                      | 115 |

| Table 9-8 Network Discovery Register Fields                                        | 116 |

| Table 9-9 Router Identity Register Field                                           | 117 |

| Table 9-10 Router Control Register Fields                                          | 118 |

| Table 9-11 Error Active Register Fields                                            | 121 |

| Table 9-12 Time-Code Register Fields                                               | 122 |

| TABLE 9-13 DEVICE MANUFACTURER AND CHIP ID REGISTER FIELDS                         | 122 |

| Table 9-14 Time-Code Enable Register Fields                                        | 124 |

| Table 9-15 Transmit Clock Control Register Bits                                    | 126 |

| Table 9-16 Destination Key Register                                                | 127 |

| TABLE 10-1 CLOCK AND RESET TIMING PARAMETERS                                       | 128 |

| TABLE 10-2 SERIAL SIGNAL TIMING PARAMETERS                                         | 129 |

| TABLE 10-3 EXTERNAL PORT TIMING PARAMETERS                                         | 130 |

| TABLE 10-4 TIME-CODE INTERFACE TIMING PARAMETERS                                   | 131 |

| TABLE 10-5 STATUS MULTIPLEXER TIMING PARAMETERS                                    | 132 |

| TABLE 10-6 SPACEWIRE ROUTER LATENCY AND JITTER MEASUREMENTS (BIT RATE = 200MBITS/S | 135 |

| TABLE 11-1 OPERATING CONDITIONS                                                    | 136 |

| TABLE 11-2 ABSOLUTE MAXIMUM RATINGS                                                | 137 |

| Table 11-3 Reliability Information                                                 | 137 |

### **SpaceWire Router**

**User Manual**

Ref.: **UoD\_SpW-10X\_**

**UserManual**

Issue: **3.4**

Date: 11<sup>th</sup> July 2008

#### 1. INTRODUCTION

This document is a technical reference for the implementation and operation of the SpW-10X SpaceWire Router device (Atmel part number AT7910E).

Note: Detailed timing information for the ASIC implementation will be available in 1Q08.

#### 1.1 TERMS, ACRONYMS AND ABBREVIATIONS

3V3 3.3 volt interface levels.

AAe Austrian Aerospace GmbH

ACK Acknowledge

AD Applicable Document

CLK Clock (Input clock to the SpaceWire router)

CRC Cyclic Redundancy Check

DC Direct Current

ECSS European Cooperation for Space Standarization

EEP Error end of packet, used to denote an error occurred during packet transfer

EOP End of packet used to denote a normal end of packet in SpaceWire

FIFO First in - First out buffer used to transfer data between logic

FPGA Field Programmable Gate Array

GND Ground

LVDS Low voltage differential signalling

NACK Negative acknowledge (error acknowledge)

PLL Phase Locked Loop

RD Read

RMAP Remote Memory Access Protocol

RST Asynchronous reset to the SpaceWire router

SpW SpaceWire

TBA To be advised

TBC To be confirmed

UoD University of Dundee

### **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_ UserManual

Issue: 3.4

Date: 11<sup>th</sup> July 2008

VCO Voltage Controlled Oscillator

VDD Drain Voltage (power pin of SpW-10X device)

VSS Source Voltage (ground pin of SpW-10X device)

WR Write

### 1.2 DOCUMENTS

In this section the documents referenced in this document are listed.

|     | Table 1-1 Applicable Documents |                                                 |  |  |  |  |

|-----|--------------------------------|-------------------------------------------------|--|--|--|--|

| REF | Document Number                | Document Title                                  |  |  |  |  |

| AD1 | ECSS-E5O-12A                   | SpaceWire - links, nodes, routers and networks. |  |  |  |  |

| AD2 | ECSS-E50-11A                   | SpaceWire Remote Memory Access Protocol         |  |  |  |  |

| AD3 | TBD                            | SpW_10X Standard Microcircuit Drawing           |  |  |  |  |

|     | Table 1-2 Reference Documents |                                                                                                                                                                                                                                                                        |  |  |  |  |

|-----|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| REF | Document Number               | Document Title                                                                                                                                                                                                                                                         |  |  |  |  |

| RD1 |                               | LVDS Owner's Manual, National Semiconductor.  Downloadable from: <a href="http://www.national.com/appinfo/lvds/files/National_LVDS_Owners_Manual_4th_Edition_2008.pdf">http://www.national.com/appinfo/lvds/files/National_LVDS_Owners_Manual_4th_Edition_2008.pdf</a> |  |  |  |  |

| RD2 | AN-1194                       | Application Note AN-1194, Failsafe Biasing of LVDS Interfaces,  Downloadable from: <a href="http://www.national.com/an/AN/AN-1194.pdf#page=1">http://www.national.com/an/AN/AN-1194.pdf#page=1</a>                                                                     |  |  |  |  |

| RD3 |                               | MH1RT Rad Hard 1.6M Used Gates 0.35 Micron CMOS Sea of Gates / Embedded Gates ASIC families.  Downloadable from: <a href="http://www.atmel.com/dyn/resources/prod documents/doc4110.pdf">http://www.atmel.com/dyn/resources/prod documents/doc4110.pdf</a>             |  |  |  |  |

### SpaceWire Router

**User Manual**

Ref.: UoD\_SpW-10X\_

UserManual

Issue: **3.4**

Date: 11<sup>th</sup> July 2008

#### 2. USER APPLICATIONS

The SpW-10X SpaceWire router device may be used in several different ways as described in the following sub-sections.

Note: SpW-10X is pronounced "SpaceWire Ten X". This name derives from the abbreviation for SpaceWire (SpW), the fact that the router has eight SpaceWire ports and two external ports giving ten ports in total, and the used of "X" to represent a cross-bar switch.

#### 2.1 STAND-ALONE ROUTER

The SpaceWire Router may be used as a stand-alone router with up to eight SpaceWire links connected to it. Configuration of the routing tables etc. may be done by sending SpaceWire packets containing configuration commands to the router.

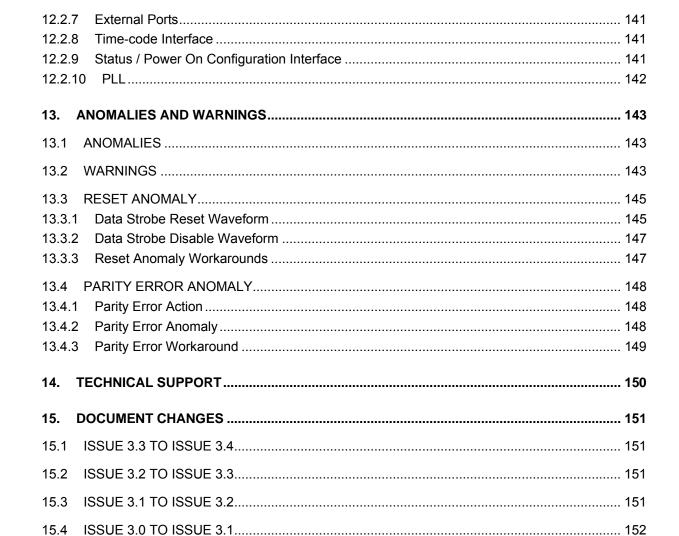

Figure 2-1 Stand-Alone Router

In Figure 2-1 an example of use of the SpW-10X device as a stand-alone router is illustrated. There are four instruments connected to the SpW-10X device along with a memory unit and processor. The processor can communicate with all the instruments and memory unit to control them and is also able to configure the SpW-10X device. The instruments can send data to the memory unit for storage or to the processor for immediate processing. The processor can also read data from the memory for later processing, writing the processed data back into memory. A pair of SpW-10X devices can be used to provide a redundant configuration.

### **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

**UserManual**

Issue: **3.4**

Date: 11<sup>th</sup> July 2008

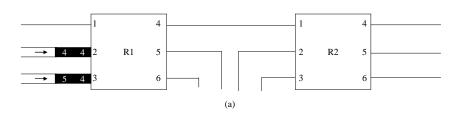

#### 2.2 NODE INTERFACE

The SpaceWire Router has two external ports which enable the device to be used as a node interface. The equipment to be connected to the SpaceWire network is attached to one or both external ports. One or more SpaceWire ports are used to provide the connection into the SpaceWire network. Unused SpaceWire ports may be disabled and their outputs deactivated to save power. In this arrangement configuration of the routing tables and other parameters may be done by sending configuration packets from the local host via an external port or from a remote network manager via a SpaceWire port.

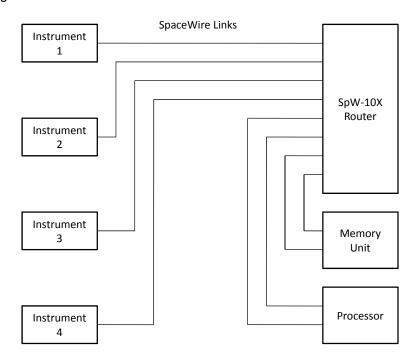

Figure 2-2 Node Interface

In Figure 2-2 a SpW-10X router is used as an interface to a user FPGA or processor, which may be part of a SpaceWire enabled instrument, control processor or other sub-system. The interface to the user FPGA or processor is via the external FIFO ports of the SpW-10X router. Only three SpaceWire links are needed for this SpaceWire node so the other five links are disabled to save power.

#### 2.3 EMBEDDED ROUTER

The SpaceWire Router device can also be used to provide a node with an embedded router. In this case the external ports are used to provide the local connections to the node and the SpaceWire ports are used to make connections to other ports in the network. The difference between this configuration and that of section 2.2 is just a conceptual one with the Node interface configuration normally using fewer SpaceWire ports than the Embedded Router configuration.

### **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

**UserManual**

Issue: 3.4

Date: 11<sup>th</sup> July 2008

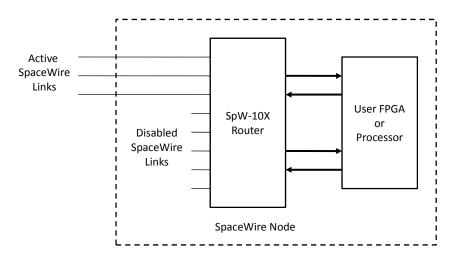

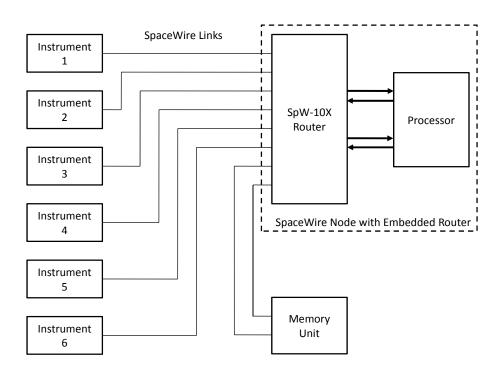

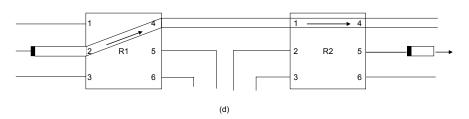

Figure 2-3 Embedded Router

In Figure 2-3 a SpaceWire system similar to that shown in Figure 2-1 is shown with the SpW-10X router embedded in a SpaceWire node along with a processor. The processor interfaces can interface to the SpW-10X router using the external FIFO ports saving some SpaceWire ports for connecting to additional instruments. For redundancy a pair of the SpaceWire nodes with embedded routers may be used.

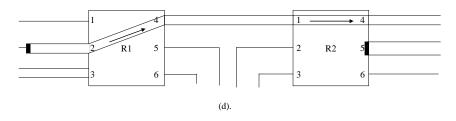

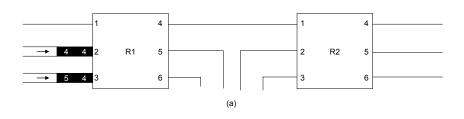

#### 2.4 EXPANDING THE NUMBER OF ROUTER PORTS

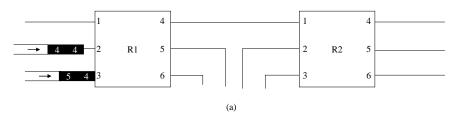

If a routing switch with a larger number of SpaceWire (or external) ports is required then this can be accomplished by joining together two or more routers using some of the SpaceWire links. For example using two SpaceWire links to join together two router devices would create an effective router with twelve SpaceWire ports and four external ports. Note, however, that an extra path addressing byte is needed to route packets between the two routers and that there is additional routing delay.

### **SpaceWire Router**

**User Manual**

Ref.: **UoD\_SpW-10X\_**

**UserManual**

Issue: 3.4

Date: 11th July 2008

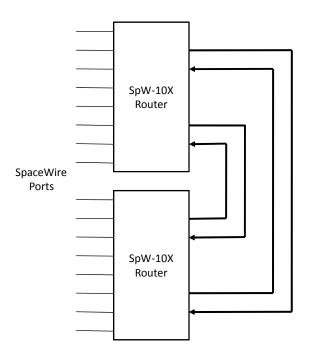

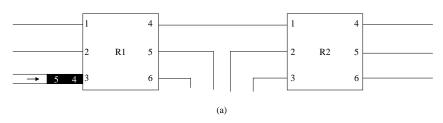

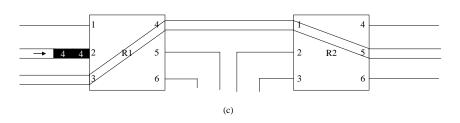

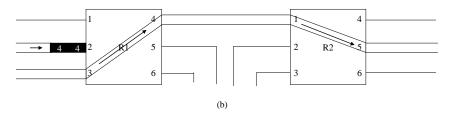

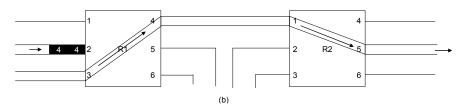

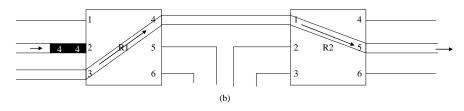

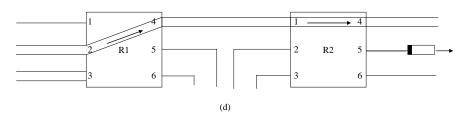

Figure 2-4 Expanding the number of SpaceWire Ports (1)

Figure 2-4 shows a pair of SpW-10X routers connected together using the external FIFO ports to provide a 16 port router. A small amount of external logic is required to connect the external FIFO ports in this way. Note that the bandwidth between the two SpW-10X devices is limited by the two external FIFO ports used to interconnect them. Each FIFO port can handle one SpaceWire packet at a time in each direction.

# SpW-10X SpaceWire Router

**User Manual**

Ref.: **UoD\_SpW-10X\_**

UserManual

Issue: 3.4

Date: 11<sup>th</sup> July 2008

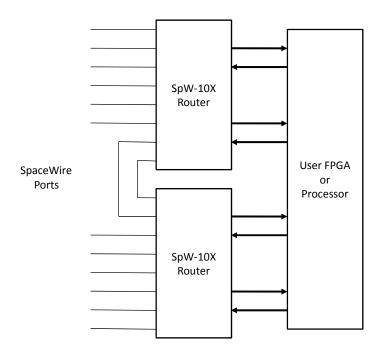

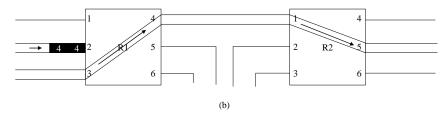

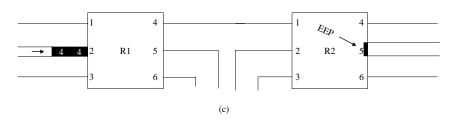

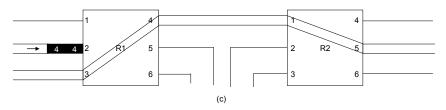

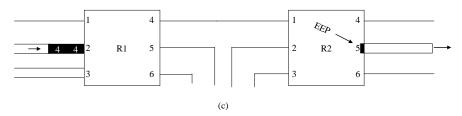

### Figure 2-5 Expanding the number of SpaceWire Ports (2)

Figure 2-5 shows two SpW-10X router devices interconnected using two of the SpaceWire ports on each router. This leaves twelve SpaceWire ports for connection to other SpaceWire nodes. The External FIFO ports of each router are used to connect to user logic in an FPGA or to a processing device.

# SpW-10X SpaceWire Router

User Manual

Ref.: **UoD\_SpW-10X\_**

**UserManual**

Issue: 3.4

Date: 11<sup>th</sup> July 2008

#### 3. FUNCTIONAL OVERVIEW

A SpaceWire routing switch comprises a number of SpaceWire ports and a routing matrix. The routing matrix enables packets arriving at one SpaceWire port to be transferred to and sent out of another port on the routing switch. A SpaceWire routing switch is thus able to connect together many SpaceWire nodes, providing a means of routing packets between the nodes connected to it.

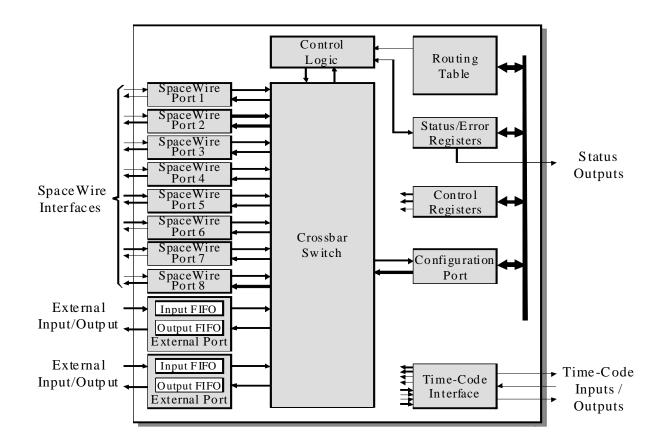

The SpW-10X SpaceWire router comprises the following functional logic blocks:

- Eight SpaceWire bi-directional serial ports.

- Two external parallel input/output ports each comprising an input FIFO and an output FIFO.

- A crossbar switch connecting any input port to any output port.

- An internal configuration port accessible via the crossbar switch from the external parallel input/output port or the SpaceWire input/output ports.

- A routing table accessible via the configuration port which holds the logical address to output port mapping.

- Control logic to control the operation of the switch, performing arbitration and group adaptive routing.

- Control registers than can be written and read by the configuration port and which hold control information e.g. link operating speed.

- An external time-code interface comprising tick\_in, tick\_out and current tick count value.

- Internal status/error registers accessible via the configuration port.

- · Watchdog timers on all ports.

- Internal status/error registers accessible via the configuration port using the RMAP protocol [2].

- External status/error signals.

A block diagram of the routing switch is given in Figure 3-1.

### **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

UserManual

Issue: **3.4**

Date: 11<sup>th</sup> July 2008

Figure 3-1 SpaceWire router block diagram

The following paragraphs define the SpaceWire router functional logic blocks in more detail.

#### 3.1 SPACEWIRE PORTS

The SpaceWire router has eight bi-directional SpaceWire links each conformant with the SpaceWire standard. Each SpaceWire link is controlled by an associated link register and routing control logic. Network level error recovery is performed when an error is detected on the SpaceWire link as defined in the SpaceWire standard. Packets received on SpaceWire links are routed by the routing control logic to the configuration port, other SpaceWire link ports or the external FIFO ports. Packets with invalid addresses are discarded by the SpaceWire router dependent on the packet address. The SpaceWire link status is recorded in the associated link register and error status is held by the router until cleared by a configuration command.

#### 3.2 EXTERNAL PORTS

The SpaceWire router has two bi-directional parallel FIFO interfaces that can be used to connect the router to an external host system. The external port FIFO is two data characters deep. Each FIFO is

# SpW-10X SpaceWire Router

**User Manual**

Ref.: UoD\_SpW-10X\_ UserManual

Issue: 3.4

Date: 11<sup>th</sup> July 2008

written to or read from synchronously with the 30MHz system clock. An eight-bit data interface and an extra control bit for end of packet markers are provided by each external port FIFO. Packets received by the external port are routed by the routing control logic to the configuration port, SpaceWire link ports or the other external port dependent on the packet address. Packets with invalid addresses are discarded by the SpaceWire router.

#### 3.3 CONFIGURATION PORT

The SpaceWire router has one configuration port which performs read and write operations to internal router registers. Packets are routed to the configuration port when a packet with a leading address byte of zero is received. The Remote Memory Access Protocol (RMAP) [AD2] to access the configuration port. A detailed description of the RMAP command packet format is provided in section 7.6. If an invalid command packet is received then the error is flagged to an associated status register and the packet is discarded. The internal router registers are described in section 9.

#### 3.4 ROUTING TABLE

The SpaceWire router routing table is set by the router command packets to assign logical addresses to physical destination ports on the router. A group of destination ports can be set, in each routing table location, to enable group adaptive routing. In group adaptive routing a packet can be routed to its destination through one of a set of output ports dependent on which ports in the set are free to use. When a packet is received with a logical address the routing table is checked by the routing control logic and the packet is routed to the destination port when the port is ready.

Routing table locations are set to invalid at power on or at reset. An invalid routing address will cause the packet to be spilled by the control logic. The routing table logical addresses can also be set to support high priority and header deletion. High priority packets are routed before low priority packets and header deletion of logical addresses can be used to support regional logical addressing (see AD1).

#### 3.5 ROUTING CONTROL LOGIC AND CROSSBAR

The routing control logic is responsible for arbitration of output ports, group adaptive routing and the crossbar switching. Arbitration is performed when two or more source ports are requesting to use the same destination port. A priority based arbitration scheme with two priority levels, high and low, is used where high priority packets are routed before low priority packets. Fair arbitration is performed on packets which have the same priority levels to ensure each packet gets equal access to the output port.

Group adaptive routing control selects one of a number of output ports for sending out the source packet.

# SpW-10X SpaceWire Router

**User Manual**

Ref.: UoD\_SpW-10X\_

UserManual

Issue: **3.4**

Date: 11<sup>th</sup> July 2008

The crossbar switch connects an input port to an output port allowing data to flow from the input port to the output port. Several input ports may be connected simultaneously to several output ports all passing data. Two or more input ports may not be connected to a single output port. The crossbar switch is a "non-blocking" type because the connection of one input port to an output port does not prevent another input port being connected to another output port at the same time. It is possible for all eight input ports to be each connected to an output port so that all input ports and output ports are being used.

#### 3.6 TIME-CODE PROCESSING

An internal time-code register is used in the router to allow the router to be a time-code master or a time-code slave.

In master mode the time-code interface is used to provide a tick-in to the SpaceWire routing causing time-codes to be propagated through the network. Two modes of time master operation are supported, an automatic mode where a time-code is propagated on each external tick-in and a normal mode where the time-code is propagated dependent on the external time-in signal.

In time-code slave mode a valid received time-code, one plus the value of the router time-code register, causes a tick-out to be sent to the SpaceWire links and the external time-code interface. The time-code is propagated to all time-code ports except the port on which the time-code was received. If the time-code received is not one plus the value of the time-code register then the time-code register is updated but the tick-out is not performed. In this way circular network paths do not cause a constant stream of time-codes to be sent in a loop.

#### 3.7 CONTROL/STATUS REGISTERS

The control and status registers in the SpaceWire router provide the means to control the operation of the router, set the router configuration and parameters or monitor the status of the device. The registers are accessed using RMAP [AD2] command packets received by the configuration port.

### **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

UserManual

3.4

Issue:

Date: 11<sup>th</sup> July 2008

### 4. PIN LOCATIONS

The SpaceWire router package is a 196 pin MQFPF package.

Type definition:

- GND.....Ground

- PIC...... CMOS input

- PRD4...... pull-down resistor (min.16kΩ, max. 80kΩ)

- PLL ..... PLL pins

- PFILVDSZP.....LVDS cold sparing input

- PFILVDSZPB ......LVDS cold sparing input, negative input

- PFOLVDS33ZP ..... LVDS output 3.3V

- PFOLVDS33ZPB...... LVDS output 3.3V, negative output

- PFOLVDSREFZ ..... LVDS reference

- PO44F ...... 4x driving strength output (fast, minimum slew rate control)

- PO22F-tri......2x driving strength output with tristate (fast, minimum slew rate control)

| Pin | Signal      | Туре      | Description             |

|-----|-------------|-----------|-------------------------|

| 1   | VDDB        | 3V3       | Power                   |

| 2   | CLK         | PIC       | System clock            |

| 3   | RSTN        | PIC       | Reset                   |

| 4   | TestlOEn    | PIC PRD4  | Chip test pin           |

| 5   | TestEn      | PIC PRD4  | Chip test pin           |

| 6   | FEEDBDIV(0) | PIC PRD4  | PLL divider bit 0 (LS)  |

| 7   | VSSA1       | GND       | Ground                  |

| 8   | VDDA1       | 3V3       | Power                   |

| 9   | FEEDBDIV(1) | PIC PRD4  | PLL divider bit 1       |

| 10  | FEEDBDIV(2) | PIC PRD4  | PLL divider bit 2 (MS)  |

| 11  | VSSB        | GND       | Ground                  |

| 12  | VDDPLL      | PLL       | PLL power               |

| 13  | VCOBias     | PLL       | PLL VCO bias            |

| 14  | LoopFilter  | PLL       | PLL loop filter         |

| 15  | VSSPLL      | PLL       | PLL ground              |

| 16  | VDDB        | 3V3       | Power                   |

| 17  | DINPlus(1)  | PFILVDSZP | SpW port 1 input data + |

## **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

UserManual

Issue: **3.4**

| 18 | DINMinus(1)  | PFILVDSZPB   | SpW port 1 input data -    |

|----|--------------|--------------|----------------------------|

| 19 | SINPlus(1)   | PFILVDSZP    | SpW port 1 input strobe +  |

| 20 | SINMinus(1)  | PFILVDSZPB   | SpW port 1 input strobe -  |

| 21 | SOUTMinus(1) | PFOLVDS33ZPB | SpW port 1 output strobe - |

| 22 | SOUTPlus(1)  | PFOLVDS33ZP  | SpW port 1 output strobe + |

| 23 | DOUTMinus(1) | PFOLVDS33ZPB | SpW port 1 output data -   |

| 24 | DOUTPlus(1)  | PFOLVDS33ZP  | SpW port 1 output data +   |

| 25 | DINPlus(2)   | PFILVDSZP    | SpW port 2 input data +    |

| 26 | DINMinus(2)  | PFILVDSZPB   | SpW port 2 input data -    |

| 27 | SINPlus(2)   | PFILVDSZP    | SpW port 2 input strobe +  |

| 28 | SINMinus(2)  | PFILVDSZPB   | SpW port 2 input strobe -  |

| 29 | VSSB         | GND          | Ground                     |

| 30 | VDDB         | 3V3          | Power                      |

| 31 | SOUTMinus(2) | PFOLVDS33ZPB | SpW port 2 output strobe - |

| 32 | SOUTPlus(2)  | PFOLVDS33ZP  | SpW port 2 output strobe + |

| 33 | DOUTMinus(2) | PFOLVDS33ZPB | SpW port 2 output data -   |

| 34 | DOUTPlus(2)  | PFOLVDS33ZP  | SpW port 2 output data +   |

| 35 | DINPlus(3)   | PFILVDSZP    | SpW port 3 input data +    |

| 36 | DINMinus(3)  | PFILVDSZPB   | SpW port 3 input data -    |

| 37 | SINPlus(3)   | PFILVDSZP    | SpW port 3 input strobe +  |

| 38 | SINMinus(3)  | PFILVDSZPB   | SpW port 3 input strobe -  |

| 39 | SOUTMinus(3) | PFOLVDS33ZPB | SpW port 3 output strobe - |

| 40 | SOUTPlus(3)  | PFOLVDS33ZP  | SpW port 3 output strobe + |

| 41 | VSSB         | GND          | Ground                     |

| 42 | VSSA2        | GND          | Ground                     |

| 43 | VDDA2        | 3V3          | Power                      |

| 44 | VDDB         | 3V3          | Power                      |

| 45 | DOUTMinus(3) | PFOLVDS33ZPB | SpW port 3 output data -   |

| 46 | DOUTPlus(3)  | PFOLVDS33ZP  | SpW port 3 output data +   |

| 47 | DINPlus(4)   | PFILVDSZP    | SpW port 4 input data +    |

| 48 | DINMinus(4)  | PFILVDSZPB   | SpW port 4 input data -    |

| 49 | LVDSRef      | PFOLVDSREFZ  | LVDS reference             |

| 50 | SINPlus(4)   | PFILVDSZP    | SpW port 4 input strobe +  |

| 51 | SINMinus(4)  | PFILVDSZPB   | SpW port 4 input strobe -  |

| 52 | SOUTMinus(4) | PFOLVDS33ZPB | SpW port 4 output strobe - |

| 53 | SOUTPlus(4)  | PFOLVDS33ZP  | SpW port 4 output strobe + |

| 54 | DOUTMinus(4) | PFOLVDS33ZPB | SpW port 4 output data -   |

| 55 | DOUTPlus(4)  | PFOLVDS33ZP  | SpW port 4 output data +   |

| 56 | VSSA3        | GND          | Ground                     |

| 57 | VDDA3        | 3V3          | Power                      |

## **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

UserManual

Issue: **3.4**

| 58 | VSSB         | GND          | Ground                     |

|----|--------------|--------------|----------------------------|

| 59 | VDDB         | 3V3          | Power                      |

| 60 | DINPlus(5)   | PFILVDSZP    | SpW port 5 input data +    |

| 61 | DINMinus(5)  | PFILVDSZPB   | SpW port 5 input data -    |

| 62 | SINPlus(5)   | PFILVDSZP    | SpW port 5 input strobe +  |

| 63 | SINMinus(5)  | PFILVDSZPB   | SpW port 5 input strobe -  |

| 64 | SOUTMinus(5) | PFOLVDS33ZPB | SpW port 5 output strobe - |

| 65 | SOUTPlus(5)  | PFOLVDS33ZP  | SpW port 5 output strobe + |

| 66 | DOUTMinus(5) | PFOLVDS33ZPB | SpW port 5 output data -   |

| 67 | DOUTPlus(5)  | PFOLVDS33ZP  | SpW port 5 output data +   |

| 68 | DINPlus(6)   | PFILVDSZP    | SpW port 6 input data +    |

| 69 | DINMinus(6)  | PFILVDSZPB   | SpW port 6 input data -    |

| 70 | SINPlus(6)   | PFILVDSZP    | SpW port 6 input strobe +  |

| 71 | SINMinus(6)  | PFILVDSZPB   | SpW port 6 input strobe -  |

| 72 | VSSB         | GND          | Ground                     |

| 73 | VDDB         | 3V3          | Power                      |

| 74 | SOUTMinus(6) | PFOLVDS33ZPB | SpW port 6 output strobe - |

| 75 | SOUTPlus(6)  | PFOLVDS33ZP  | SpW port 6 output strobe + |

| 76 | DOUTMinus(6) | PFOLVDS33ZPB | SpW port 6 output data -   |

| 77 | DOUTPlus(6)  | PFOLVDS33ZP  | SpW port 6 output data +   |

| 78 | DINPlus(7)   | PFILVDSZP    | SpW port 7 input data +    |

| 79 | DINMinus(7)  | PFILVDSZPB   | SpW port 7 input data -    |

| 80 | SINPlus(7)   | PFILVDSZP    | SpW port 7 input strobe +  |

| 81 | SINMinus(7)  | PFILVDSZPB   | SpW port 7 input strobe -  |

| 82 | SOUTMinus(7) | PFOLVDS33ZPB | SpW port 7 output strobe - |

| 83 | SOUTPlus(7)  | PFOLVDS33Z   | SpW port 7 output strobe + |

| 84 | VSSB         | GND          | Ground                     |

| 85 | VDDB         | 3V3          | Power                      |

| 86 | DOUTMinus(7) | PFOLVDS33ZPB | SpW port 7 output data -   |

| 87 | DOUTPlus(7)  | PFOLVDS33ZP  | SpW port 7 output data +   |

| 88 | DINPlus(8)   | PFILVDSZP    | SpW port 8 input data +    |

| 89 | DINMinus(8)  | PFILVDSZPB   | SpW port 8 input data -    |

| 90 | SINPlus(8)   | PFILVDSZP    | SpW port 8 input strobe +  |

| 91 | VSSA4        | GND          | Ground                     |

| 92 | VDDA4        | 3V3          | Power                      |

| 93 | SINMinus(8)  | PFILVDSZPB   | SpW port 8 input strobe -  |

| 94 | SOUTMinus(8) | PFOLVDS33ZPB | SpW port 8 output strobe - |

| 95 | SOUTPlus(8)  | PFOLVDS33ZP  | SpW port 8 output strobe + |

| 96 | DOUTMinus(8) | PFOLVDS33ZPB | SpW port 8 output data -   |

| 97 | DOUTPlus(8)  | PFOLVDS33ZP  | SpW port 8 output data +   |

## **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

**UserManual**

Issue: 3.4

| 98  | VSSB            | GND   | Ground                            |

|-----|-----------------|-------|-----------------------------------|

| 99  | VDDB            | 3V3   | Power                             |

| 100 | EXTOUTDATA9(0)  | PO44F | External FIFO port 9 output data  |

| 101 | EXTOUTDATA9(1)  | PO44F | External FIFO port 9 output data  |

| 102 | EXTOUTDATA9(2)  | PO44F | External FIFO port 9 output data  |

| 103 | EXTOUTDATA9(3)  | PO44F | External FIFO port 9 output data  |

| 104 | EXTOUTDATA9(4)  | PO44F | External FIFO port 9 output data  |

| 105 | VSSA5           | GND   | Ground                            |

| 106 | VDDA5           | 3V3   | Power                             |

| 107 | EXTOUTDATA9(5)  | PO44F | External FIFO port 9 output data  |

| 108 | VSSB            | GND   | Ground                            |

| 109 | VDDB            | 3V3   | Power                             |

| 110 | EXTOUTDATA9(6)  | PO44F | External FIFO port 9 output data  |

| 111 | EXTOUTDATA9(7)  | PO44F | External FIFO port 9 output data  |

| 112 | EXTOUTDATA9(8)  | PO44F | External FIFO port 9 output data  |

| 113 | EXTOUTEMPTYN9   | PO44F | External FIFO port 9 output empty |

| 114 | EXTOUTREADN9    | PIC   | External FIFO port 9 output read  |

| 115 | EXTINDATA9(0)   | PIC   | External FIFO port 9 input data   |

| 116 | EXTINDATA9(1)   | PIC   | External FIFO port 9 input data   |

| 117 | EXTINDATA9(2)   | PIC   | External FIFO port 9 input data   |

| 118 | EXTINDATA9(3)   | PIC   | External FIFO port 9 input data   |

| 119 | EXTINDATA9(4)   | PIC   | External FIFO port 9 input data   |

| 120 | EXTINDATA9(5)   | PIC   | External FIFO port 9 input data   |

| 121 | EXTINDATA9(6)   | PIC   | External FIFO port 9 input data   |

| 122 | EXTINDATA9(7)   | PIC   | External FIFO port 9 input data   |

| 123 | EXTINDATA9(8)   | PIC   | External FIFO port 9 input data   |

| 124 | EXTINFULLN9     | PO44F | External FIFO port 9 input full   |

| 125 | VSSB            | GND   | Ground                            |

| 126 | VDDB            | 3V3   | Power                             |

| 127 | EXTINWRITEN9    | PIC   | External FIFO port 9 input write  |

| 128 | EXTOUTDATA10(0) | PO44F | External FIFO port 10 output data |

| 129 | EXTOUTDATA10(1) | PO44F | External FIFO port 10 output data |

| 130 | EXTOUTDATA10(2) | PO44F | External FIFO port 10 output data |

| 131 | EXTOUTDATA10(3) | PO44F | External FIFO port 10 output data |

| 132 | EXTOUTDATA10(4) | PO44F | External FIFO port 10 output data |

| 133 | EXTOUTDATA10(5) | PO44F | External FIFO port 10 output data |

| 134 | VSSB            | GND   | Ground                            |

| 135 | VDDB            | 3V3   | Power                             |

| 136 | EXTOUTDATA10(6) | PO44F | External FIFO port 10 output data |

| 137 | EXTOUTDATA10(7) | PO44F | External FIFO port 10 output data |

## **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

**UserManual**

Issue: **3.4**

| 138 | EXTOUTDATA10(8) | PO44F | External FIFO port 10 output data  |

|-----|-----------------|-------|------------------------------------|

| 139 | EXTOUTEMPTYN10  | PO44F | External FIFO port 10 output empty |

| 140 | VSSA6           | GND   | Ground                             |

| 141 | VDDA6           | 3V3   | Power                              |

| 142 | EXTOUTREADN10   | PIC   | External FIFO port 10 output read  |

| 143 | EXTINDATA10(0)  | PIC   | External FIFO port 10 input data   |

| 144 | EXTINDATA10(1)  | PIC   | External FIFO port 10 input data   |

| 145 | EXTINDATA10(2)  | PIC   | External FIFO port 10 input data   |

| 146 | EXTINDATA10(3)  | PIC   | External FIFO port 10 input data   |

| 147 | EXTINDATA10(4)  | PIC   | External FIFO port 10 input data   |

| 148 | EXTINDATA10(5)  | PIC   | External FIFO port 10 input data   |

| 149 | EXTINDATA10(6)  | PIC   | External FIFO port 10 input data   |

| 150 | EXTINDATA10(7)  | PIC   | External FIFO port 10 input data   |

| 151 | EXTINDATA10(8)  | PIC   | External FIFO port 10 input data   |

| 152 | EXTINFULLN10    | PO44F | External FIFO port 10 input full   |

| 153 | EXTINWRITEN10   | PIC   | External FIFO port 10 input wrte   |

| 154 | VSSA7           | GND   | Ground                             |

| 155 | VDDA7           | 3V3   | Power                              |

| 156 | VSSB            | GND   | Ground                             |

| 157 | VDDB            | 3V3   | Power                              |

| 158 | EXTTICKIN       | PIC   | Time-code tick in                  |

| 159 | EXTTIMEIN(0)    | PIC   | Time-code input                    |

| 160 | EXTTIMEIN(1)    | PIC   | Time-code input                    |

| 161 | EXTTIMEIN(2)    | PIC   | Time-code input                    |

| 162 | EXTTIMEIN(3)    | PIC   | Time-code input                    |

| 163 | EXTTIMEIN(4)    | PIC   | Time-code input                    |

| 164 | EXTTIMEIN(5)    | PIC   | Time-code input                    |

| 165 | EXTTIMEIN(6)    | PIC   | Time-code input                    |

| 166 | EXTTIMEIN(7)    | PIC   | Time-code input                    |

| 167 | SELEXTTIME      | PIC   | Time-code counter/input selection  |

| 168 | TIMECTRRST      | PIC   | Time-code counter reset            |

| 169 | EXTTICKOUT      | PO44F | Time-code tick out                 |

| 170 | EXTTIMEOUT(0)   | PO44F | Time-code output                   |

| 171 | EXTTIMEOUT(1)   | PO44F | Time-code output                   |

| 172 | EXTTIMEOUT(2)   | PO44F | Time-code output                   |

| 173 | EXTTIMEOUT(3)   | PO44F | Time-code output                   |

| 174 | VSSB            | GND   | Ground                             |

| 175 | VDDB            | 3V3   | Power                              |

| 176 | EXTTIMEOUT(4)   | PO44F | Time-code output                   |

| 177 | EXTTIMEOUT(5)   | PO44F | Time-code output                   |

## **SpaceWire Router**

**User Manual**

Ref.: **UoD\_SpW-10X\_**

**UserManual**

Issue: **3.4**

| 178 | EXTTIMEOUT(6)  | PO44F         | Time-code output                   |

|-----|----------------|---------------|------------------------------------|

| 179 | EXTTIMEOUT(7)  | PO44F         | Time-code output                   |

| 180 | STATMUXADDR(0) | PIC           | Status output multiplexer address  |

| 181 | STATMUXADDR(1) | PIC           | Status output multiplexer address  |

| 182 | STATMUXADDR(2) | PIC           | Status output multiplexer address  |

| 183 | STATMUXADDR(3) | PIC           | Status output multiplexer address  |

| 184 | VSSB           | GND           | Ground                             |

| 185 | VDDB           | 3V3           | Power                              |

| 186 | STATMUXOUT(0)  | PO22F-tri PIC | Status output /configuration input |

| 187 | STATMUXOUT(1)  | PO22F-tri PIC | Status output /configuration input |

| 188 | STATMUXOUT(2)  | PO22F-tri PIC | Status output /configuration input |

| 189 | VSSA8          | GND           | Ground                             |

| 190 | VDDA8          | 3V3           | Power                              |

| 191 | STATMUXOUT(3)  | PO22F-tri PIC | Status output /configuration input |

| 192 | STATMUXOUT(4)  | PO22F-tri PIC | Status output /configuration input |

| 193 | STATMUXOUT(5)  | PO22F-tri PIC | Status output /configuration input |

| 194 | STATMUXOUT(6)  | PO22F-tri PIC | Status output /configuration input |

| 195 | STATMUXOUT(7)  | PO22F-tri PIC | Status output /configuration input |

| 196 | VSSB           | GND           | Ground                             |

### **SpaceWire Router**

**User Manual**

Ref.: **UoD\_SpW-10X\_**

**UserManual**

Issue: 3.4

Date: 11th July 2008

### 5. DEVICE INTERFACE

The device pins used by each interface are described in this section. There is a table for each type of interface listing the signals in that interface. These tables have the following fields:

Pin No: The device pin number

Signal: The name of the signal

Dir: The direction of the signal; in, out or in/out

Description: An explanation of what the signal does.

Type: The type of signal

The sections below define the pin out of the SpaceWire router. Its interfaces are split into several types, separated by headings for clarity:

5.1 Global signals: clock and reset

5.2 SpaceWire interface signals

5.3 External port signals

5.4 Time-code interface signals

5.5 Configuration signals

5.6 Reset configuration signals

5.7 Power and Ground

The following signal types are used in the SpaceWire Router:

CMOS3V3 3.3 Volt CMOS logic

LVDS Low Voltage Differential Signal

3V3 3.3 Volt power

GND Ground

#### 5.1 GLOBAL SIGNALS

The global system clock and reset signals are listed in Table 5-1.

### **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

**UserManual**

Issue: 3.4

Date: 11<sup>th</sup> July 2008

|       | Table 5-1 Global Signals     |    |                                                                                                                                                           |                                |  |  |

|-------|------------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|

| PinNo | PinNo Signal Dir Description |    |                                                                                                                                                           |                                |  |  |

| 2     | CLK                          | In | System clock. Provides the reference clock for all modules except the interface receivers.                                                                | CMOS3V3                        |  |  |

| 3     | RST_N                        | In | Asynchronous system reset (active low).                                                                                                                   | CMOS3V3                        |  |  |

| 4     | TestIOEn                     | In | ASIC Test control signal; Shall be connected to logic '0' during normal operation.  Tie to ground.                                                        | CMOS3V3;<br>Internal pull-down |  |  |

| 5     | TestEn                       | In | ASIC Test control signal; Shall be connected to logic '0' during normal operation.  Tie to ground.                                                        | CMOS3V3;<br>Internal pull-down |  |  |

| 10    | FEEDBDIV(2)                  | In | Set the output clock rate of the internal PLL as                                                                                                          | CMOS3V3;                       |  |  |

| 9     | FEEDBDIV(1)<br>FEEDBDIV(0)   |    | follows: "000" → 100MHz                                                                                                                                   | Internal pull-down             |  |  |

|       |                              |    | "001" → 120MHz "010" → 140MHz "011" → 160MHz "100" → 180MHz "101" → 200MHz "110" → 200MHz "111" → 200MHz See section 8.1.6 for setting the transmit rate. |                                |  |  |

See section 10.1 for timing details.

#### **WARNING**

Simultaneous data/strobe transitions can occur during reset and power up. This is not a problem when connected to SpaceWire compliant devices but is a problem when connected to IEEE-1355 devices.

#### 5.2 SPACEWIRE SIGNALS

### 5.2.1 SpW-10X SpaceWire Signals

The SpaceWire interface signals are listed in Table 5-2. For further details about SpaceWire see the SpaceWire standard [AD1]. The LVDS inputs and outputs are cold sparing [RD3].

## **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

**UserManual**

11<sup>th</sup> July 2008 Date:

Issue: 3.4

|       | Table 5-2 Data and Strobe SpaceWire Signals |     |                                                      |                 |  |

|-------|---------------------------------------------|-----|------------------------------------------------------|-----------------|--|

| PinNo | Signal                                      | Dir | Description                                          | Туре            |  |

| 24    | DOUTPlus(1)                                 | Out | Differential output pair, data part of Data-Strobe   | LVDS+ (P Side)  |  |

| 23    | DOUTMinus(1)                                |     | SpaceWire port 1.                                    | LVDS - (N Side) |  |

| 34    | DOUTPlus(2)                                 | Out | Differential output pair, data part of Data-Strobe   | LVDS+ (P Side)  |  |

| 33    | DOUTMinus(2)                                |     | SpaceWire port 2.                                    | LVDS - (N Side) |  |

| 46    | DOUTPlus(3)                                 | Out | Differential output pair, data part of Data-Strobe   | LVDS+ (P Side)  |  |

| 45    | DOUTMinus(3)                                |     | SpaceWire port 3.                                    | LVDS - (N Side) |  |

| 55    | DOUTPlus(4)                                 | Out | Differential output pair, data part of Data-Strobe   | LVDS+ (P Side)  |  |

| 54    | DOUTMinus(4)                                |     | SpaceWire port 4.                                    | LVDS - (N Side) |  |

| 67    | DOUTPlus(5)                                 | Out | Differential output pair, data part of Data-Strobe   | LVDS+ (P Side)  |  |

| 66    | DOUTMinus(5)                                |     | SpaceWire port 5.                                    | LVDS - (N Side) |  |

| 77    | DOUTPlus(6)                                 | Out | Differential output pair, data part of Data-Strobe   | LVDS+ (P Side)  |  |

| 76    | DOUTMinus(6)                                |     | SpaceWire port 6.                                    | LVDS - (N Side) |  |

| 87    | DOUTPlus(7)                                 | Out | Differential output pair, data part of Data-Strobe   | LVDS+ (P Side)  |  |

| 86    | DOUTMinus(7)                                |     | SpaceWire port 7.                                    | LVDS - (N Side) |  |

| 97    | DOUTPlus(8)                                 | Out | Differential output pair, data part of Data-Strobe   | LVDS+ (P Side)  |  |

| 96    | DOUTMinus(8)                                |     | SpaceWire port 8.                                    | LVDS - (N Side) |  |

| 22    | SOUTPlus(1)                                 | Out | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |  |

| 21    | SOUTMinus(1)                                |     | SpaceWire port 1.                                    | LVDS - (N Side) |  |

| 32    | SOUTPlus(2)                                 | Out | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |  |

| 31    | SOUTMinus(2)                                |     | SpaceWire port 2.                                    | LVDS - (N Side) |  |

| 40    | SOUTPlus(3)                                 | Out | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |  |

| 39    | SOUTMinus(3)                                |     | SpaceWire port 3.                                    | LVDS - (N Side) |  |

| 53    | SOUTPlus(4)                                 | Out | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |  |

| 50    | SOUTMinus(4)                                |     | SpaceWire port 4.                                    | LVDS - (N Side) |  |

| 65    | SOUTPlus(5)                                 | Out | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |  |

| 64    | SOUTMinus(5)                                |     | SpaceWire port 5.                                    | LVDS - (N Side) |  |

| 75    | SOUTPlus(6)                                 | Out | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |  |

| 74    | SOUTMinus(6)                                |     | SpaceWire port 6.                                    | LVDS - (N Side) |  |

| 83    | SOUTPlus(7)                                 | Out | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |  |

| 82    | SOUTMinus(7)                                |     | SpaceWire port 7.                                    | LVDS - (N Side) |  |

| 95    | SOUTPlus(8)                                 | Out | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |  |

| 94    | SOUTMinus(8)                                |     | SpaceWire port 8.                                    | LVDS - (N Side) |  |

### **SpaceWire Router**

**User Manual**

Ref.: UoD\_SpW-10X\_

**UserManual**

Issue: **3.4**

Date: 11<sup>th</sup> July 2008

| 47 | DINDI (4)   | La | Differential investment data ment of Data Checks    | 1./DC+ (D C:4-) |

|----|-------------|----|-----------------------------------------------------|-----------------|

| 17 | DINPlus(1)  | In | Differential input pair, data part of Data-Strobe   | LVDS+ (P Side)  |

| 18 | DINMinus(1) |    | SpaceWire port 1.                                   | LVDS - (N Side) |

| 25 | DINPlus(2)  | In | Differential input pair, data part of Data-Strobe   | LVDS+ (P Side)  |

| 26 | DINMinus(2) |    | SpaceWire port 2.                                   | LVDS - (N Side) |

| 35 | DINPlus(3)  | In | Differential input pair, data part of Data-Strobe   | LVDS+ (P Side)  |

| 36 | DINMinus(3) |    | SpaceWire port 3.                                   | LVDS - (N Side) |

| 47 | DINPlus(4)  | In | Differential input pair, data part of Data-Strobe   | LVDS+ (P Side)  |

| 48 | DINMinus(4) |    | SpaceWire port 4.                                   | LVDS - (N Side) |

| 60 | DINPlus(5)  | In | Differential input pair, data part of Data-Strobe   | LVDS+ (P Side)  |

| 61 | DINMinus(5) |    | SpaceWire port 5.                                   | LVDS - (N Side) |

| 68 | DINPlus(6)  | In | Differential input pair, data part of Data-Strobe   | LVDS+ (P Side)  |

| 69 | DINMinus(6) |    | SpaceWire port 6.                                   | LVDS - (N Side) |

| 78 | DINPlus(7)  | In | Differential input pair, data part of Data-Strobe   | LVDS+ (P Side)  |

| 79 | DINMinus(7) |    | SpaceWire port 7.                                   | LVDS - (N Side) |

| 88 | DINPlus(8)  | In | Differential input pair, data part of Data-Strobe   | LVDS+ (P Side)  |

| 89 | DINMinus(8) |    | SpaceWire port 8.                                   | LVDS - (N Side) |

| 19 | SINPlus(1)  | In | Differential input pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| 20 | SINMinus(1) |    | SpaceWire port 1.                                   | LVDS - (N Side) |

| 27 | SINPlus(2)  | In | Differential input pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| 28 | SINMinus(2) |    | SpaceWire port 2.                                   | LVDS - (N Side) |

| 37 | SINPlus(3)  | In | Differential input pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| 38 | SINMinus(3) |    | SpaceWire port 3.                                   | LVDS - (N Side) |

| 50 | SINPlus(4)  | In | Differential input pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| 51 | SINMinus(4) |    | SpaceWire port 4.                                   | LVDS - (N Side) |

| 62 | SINPlus(5)  | In | Differential input pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| 63 | SINMinus(5) |    | SpaceWire port 5.                                   | LVDS - (N Side) |

| 70 | SINPlus(6)  | In | Differential input pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

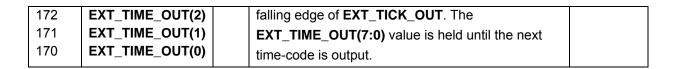

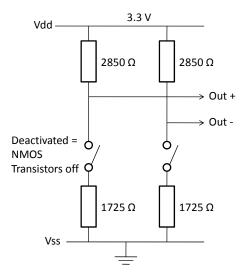

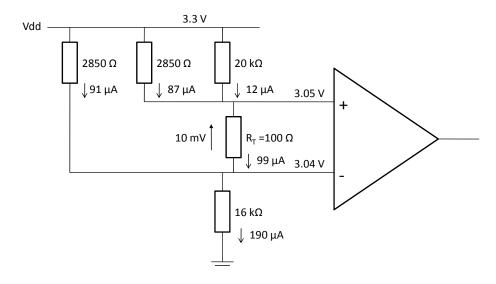

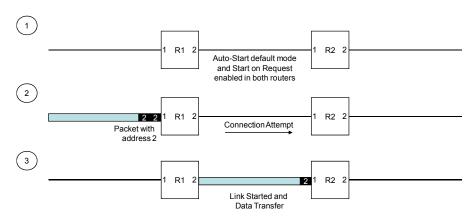

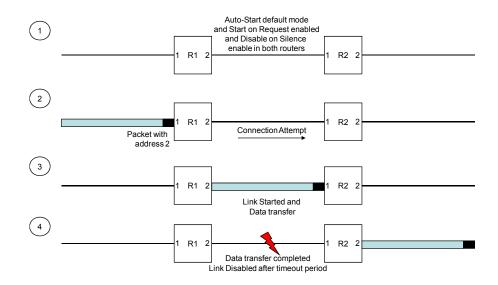

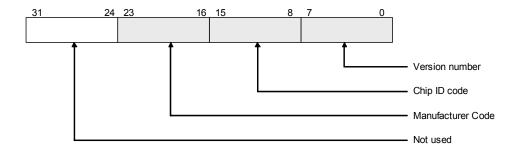

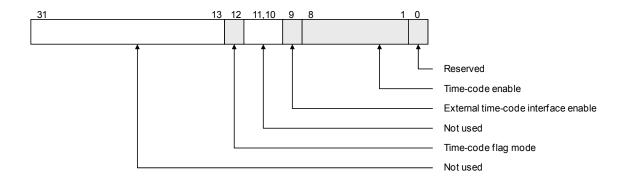

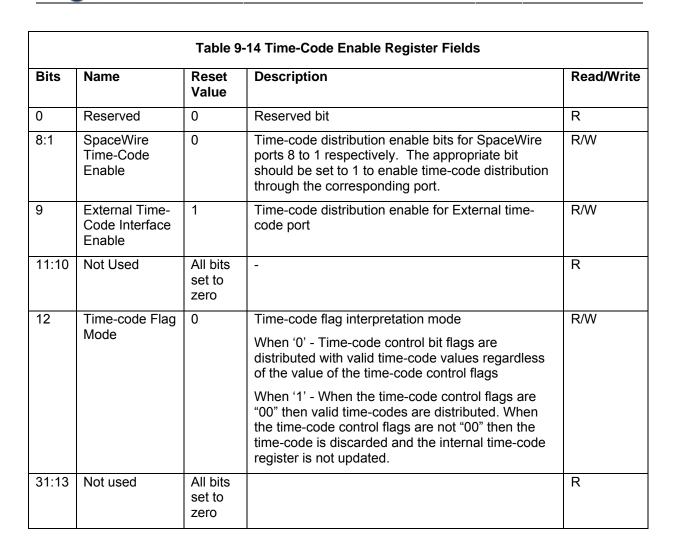

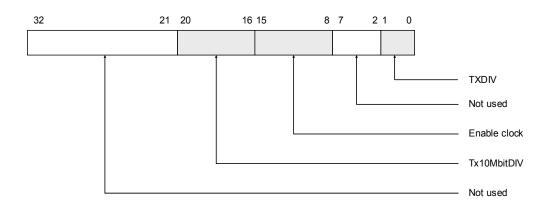

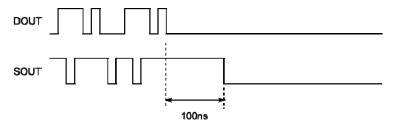

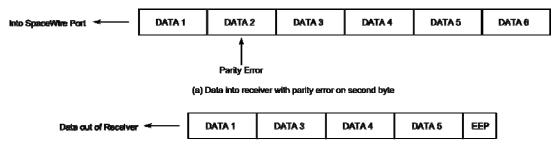

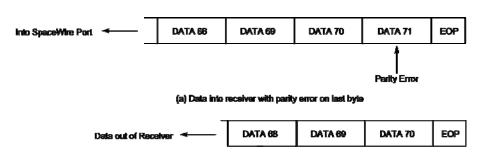

| 71 | SINMinus(6) |    | SpaceWire port 6.                                   | LVDS - (N Side) |