CY25822-2

# CK-SSC Spread Spectrum Clock Generator

#### Features

- 3.3V operation

- 48- and 66-MHz frequency support

- Selectable slew rate control

- 350-pS jitter

- I<sup>2</sup>C programmability

- 500-µA power-down current

- Spread Spectrum for best electromagnetic interference

(EMI) reduction

- 8-pin SOIC package

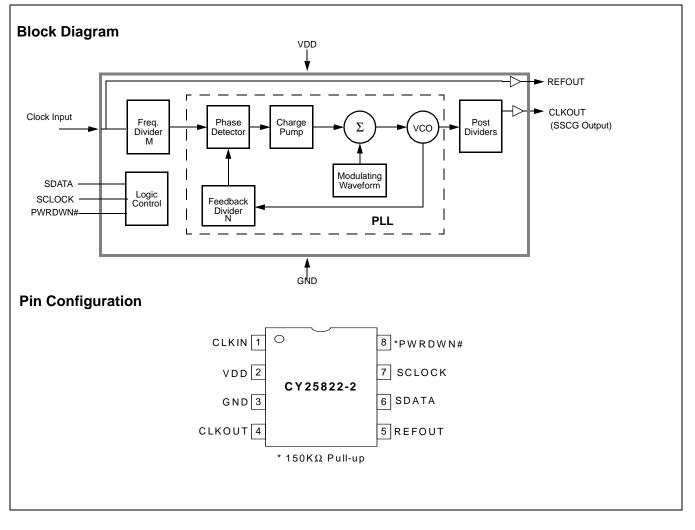

### **Pin Description**

| Pin No. | Pin Name | Pin Type | Pin Description                                |

|---------|----------|----------|------------------------------------------------|

| 1       | CLKIN    | Input    | 48-MHz or 66-MHz Clock Input.                  |

| 2       | VDD      | Power    | Power Supply for PLL and Outputs.              |

| 3       | GND      | Ground   | Ground for Outputs.                            |

| 4       | CLKOUT   | Output   | 48-MHz or 66-MHz Spread Spectrum Clock Output. |

| 5       | REFOUT   | Output   | Non-spread Spectrum Reference Clock Output.    |

| 6       | SDATA    | I/O      | I <sup>2</sup> C-compatible SDATA.             |

| 7       | SCLOCK   | Input    | I <sup>2</sup> C-compatible SCLOCK.            |

| 8       | PWRDWN#  | Output   | LVTTL Input for PowerDown# Active Low.         |

#### **Serial Data Interface**

To enhance the flexibility and function of the clock synthesizer, a two-signal serial interface is provided. Through the Serial Data Interface, various device functions such as individual clock output buffers, etc., can be individually enabled or disabled.

The registers associated with the Serial Data Interface initializes to their default setting upon power-up, and therefore use of this interface is optional. Clock device register changes are normally made upon system initialization, if any are required. The interface can also be used during system operation for power management functions.

#### **Data Protocol**

The clock driver serial protocol accepts byte write, byte read, block write, and block read operation from the controller. For block write/read operation, the bytes must be accessed in sequential order from lowest to highest byte (most significant bit first) with the ability to stop after any complete byte has been transferred. For byte write and byte read operations, the system controller can access individual indexed bytes. The offset of the indexed byte is encoded in the command code, as described in *Table 1*.

The block write and block read protocol is outlined in *Table 2* while *Table 3* outlines the corresponding byte write and byte read protocol. The slave receiver address is 11010100 (D4h).

| Bit   | Description                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 7     | 0 = Block read or block write operation<br>1 = Byte read or byte write operation                                            |

| (6:0) | Byte offset for byte read or byte write operation. For block read or block write operations, these bits should be '0000000' |

#### Table 1. Command Code Definition

#### Table 2. Block Read and Block Write Protocol

|       | Block Write Protocol                                           | Block Read Protocol |                                                                |  |  |

|-------|----------------------------------------------------------------|---------------------|----------------------------------------------------------------|--|--|

| Bit   | Description                                                    | Bit                 | Description                                                    |  |  |

| 1     | Start                                                          | 1                   | Start                                                          |  |  |

| 2:8   | Slave address – 7 bits                                         | 2:8                 | Slave address – 7 bits                                         |  |  |

| 9     | Write = 0                                                      | 9                   | Write = 0                                                      |  |  |

| 10    | Acknowledge from slave                                         | 10                  | Acknowledge from slave                                         |  |  |

| 11:18 | Command Code – 8 bits<br>'00000000' stands for block operation | 11:18               | Command Code – 8 bits<br>'00000000' stands for block operation |  |  |

| 19    | Acknowledge from slave                                         | 19                  | Acknowledge from slave                                         |  |  |

| 20:27 | Byte Count – 8 bits                                            | 20                  | Repeat start                                                   |  |  |

| 28    | Acknowledge from slave                                         | 21:27               | Slave address – 7 bits                                         |  |  |

| 29:36 | Data byte 1 – 8 bits                                           | 28                  | Read = 1                                                       |  |  |

| 37    | Acknowledge from slave                                         | 29                  | Acknowledge from slave                                         |  |  |

| 38:45 | Data byte 2 – 8 bits                                           | 30:37               | Byte count from slave – 8 bits                                 |  |  |

| 46    | Acknowledge from slave                                         | 38                  | Acknowledge                                                    |  |  |

|       |                                                                | 39:46               | Data byte from slave – 8 bits                                  |  |  |

|       | Data Byte (N–1) –8 bits                                        | 47                  | Acknowledge                                                    |  |  |

|       | Acknowledge from slave                                         | 48:55               | Data byte from slave – 8 bits                                  |  |  |

Document #: 38-07531 Rev. \*\*

#### Table 2. Block Read and Block Write Protocol (continued)

| <br>Data Byte N –8 bits    | 56 | Acknowledge                       |

|----------------------------|----|-----------------------------------|

| <br>Acknowledge from slave |    | Data bytes from slave/Acknowledge |

| <br>Stop                   |    | Data byte N from slave – 8 bits   |

|                            |    | Not Acknowledge                   |

|                            |    | Stop                              |

\_\_\_\_

#### Table 3. Byte Read and Byte Write Protocol

|       | Byte Write Protocol                                                                                                                                |       | Byte Read Protocol                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Description                                                                                                                                        | Bit   | Description                                                                                                                                        |

| 1     | Start                                                                                                                                              | 1     | Start                                                                                                                                              |

| 2:8   | Slave address – 7 bits                                                                                                                             | 2:8   | Slave address – 7 bits                                                                                                                             |

| 9     | Write = 0                                                                                                                                          | 9     | Write = 0                                                                                                                                          |

| 10    | Acknowledge from slave                                                                                                                             | 10    | Acknowledge from slave                                                                                                                             |

| 11:18 | Command Code – 8 bits<br>'1xxxxxx' stands for byte operation, bits[6:0] of<br>the command code represents the offset of the<br>byte to be accessed | 11:18 | Command Code – 8 bits<br>'1xxxxxx' stands for byte operation, bits[6:0]<br>of the command code represents the offset of<br>the byte to be accessed |

| 19    | Acknowledge from slave                                                                                                                             | 19    | Acknowledge from slave                                                                                                                             |

| 20:27 | Data byte from master – 8 bits                                                                                                                     | 20    | Repeat start                                                                                                                                       |

| 28    | Acknowledge from slave                                                                                                                             | 21:27 | Slave address – 7 bits                                                                                                                             |

| 29    | Stop                                                                                                                                               | 28    | Read = 1                                                                                                                                           |

|       |                                                                                                                                                    | 29    | Acknowledge from slave                                                                                                                             |

|       |                                                                                                                                                    | 30:37 | Data byte from slave – 8 bits                                                                                                                      |

|       |                                                                                                                                                    | 38    | Not Acknowledge                                                                                                                                    |

|       |                                                                                                                                                    | 39    | Stop                                                                                                                                               |

#### **Byte 0: Control Register**

| Bit | @Pup | Pin# | Name              | Pin Description                                                                                                       |

|-----|------|------|-------------------|-----------------------------------------------------------------------------------------------------------------------|

| 7   | 1    | 4    | SS0               | -                                                                                                                     |

| 6   | 0    | 4    | SS1               | -                                                                                                                     |

| 5   | 0    | 4    | SS2               | -                                                                                                                     |

| 4   | 0    | 4    | SS3               | -                                                                                                                     |

| 3   | 1    |      | Not Applicable    | Reserved, must be written as 1                                                                                        |

| 2   | 1    | 4, 5 | CLKOUT,<br>REFOUT | Power-down three-state enable<br>0 = three-state outputs, 1 = drive outputs low<br>(Applies only in Power Down State) |

| 1   | 1    | 4    | CLKOUT            | Spread Spectrum enable<br>0 = spread off, 1 = spread on                                                               |

| 0   | 0    |      | Not Applicable    | No Pins                                                                                                               |

#### Table 4. Spread Spectrum Select

| SS3 | SS2 | SS1 | SS0 | Spread Mode | Spread Amount% |

|-----|-----|-----|-----|-------------|----------------|

| 0   | 0   | 0   | 0   | Down        | 0.8            |

| 0   | 0   | 0   | 1   | Down        | 1.0            |

| 0   | 0   | 1   | 0   | Down        | 1.25           |

| 0   | 0   | 1   | 1   | Down        | 1.5            |

| 0   | 1   | 0   | 0   | Down        | 1.75           |

#### Table 4. Spread Spectrum Select (continued)

| SS3 | SS2 | SS1 | SS0 | Spread Mode | Spread Amount% |

|-----|-----|-----|-----|-------------|----------------|

| 0   | 1   | 0   | 1   | Down        | 2.0            |

| 0   | 1   | 1   | 0   | Down        | 2.5            |

| 0   | 1   | 1   | 1   | Down        | 3.0            |

| 1   | 0   | 0   | 0   | Center      | ±0.3           |

| 1   | 0   | 0   | 1   | Center      | ±0.4           |

| 1   | 0   | 1   | 0   | Center      | ±0.5           |

| 1   | 0   | 1   | 1   | Center      | ±0.6           |

| 1   | 1   | 0   | 0   | Center      | ±0.8           |

| 1   | 1   | 0   | 1   | Center      | ±1.0           |

| 1   | 1   | 1   | 0   | Center      | ±1.25          |

| 1   | 1   | 1   | 1   | Center      | ±1.5           |

#### Byte 1: Control Register

| Bit | @Pup | Pin# | Name           | Pin Description                                   |  |

|-----|------|------|----------------|---------------------------------------------------|--|

| 7   | 1    | 5    | REFEN          | REFOUT enable<br>0 = disabled, 1 = enabled        |  |

| 6   | 1    | 5    | REFSLEW        | REFOUT edge rate control<br>0 = slow, 1 = nominal |  |

| 5   | 0    |      | Not Applicable | Reserved.                                         |  |

| 4   | 0    |      | Not Applicable | Reserved                                          |  |

| 3   | 1    | 4    | CLKSLEW        | CLKOUT edge rate control<br>0 = slow, 1 = nominal |  |

| 2   | 1    | 4    | CLKEN          | CLKOUT enable<br>0 =disabled, 1 = enabled         |  |

| 1   | 0    |      | Not Applicable | Reserved                                          |  |

| 0   | 0    |      | Not Applicable | Reserved                                          |  |

#### Bytes 2 through 5: Reserved Registers

#### Byte 6: Vendor/Revision ID Register

| Bit | @Pup | Pin# | Name | Pin Description   |  |

|-----|------|------|------|-------------------|--|

| 7   | 0    | _    | _    | Revision ID Bit 3 |  |

| 6   | 0    | -    | -    | Revision ID Bit 2 |  |

| 5   | 0    | -    | -    | Revision ID Bit 1 |  |

| 4   | 0    | -    | -    | Revision ID Bit 0 |  |

| 3   | 1    | -    | -    | Vendor ID Bit 3   |  |

| 2   | 0    | -    | -    | Vendor ID Bit 2   |  |

| 1   | 0    | _    | _    | Vendor ID Bit 1   |  |

| 0   | 0    | -    | _    | Vendor ID Bit 0   |  |

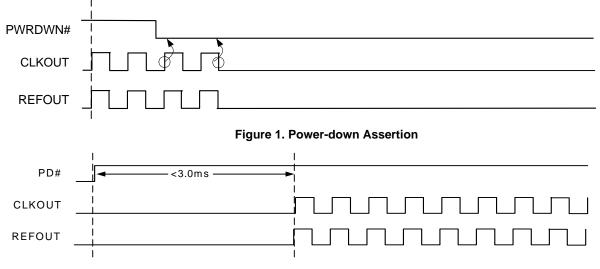

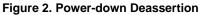

#### **PWRDWN# (Power-down) Clarification**

The PWRDWN# (Power-down) pin is used to shut off ALL clocks prior to shutting off power to the device. PWRDWN# is an asynchronous active LOW input. This signal is synchronized internally to the device powering down the clock synthesizer. PWRDWN# is an asynchronous function for powering up the system. When PWRDWN# is low, all clocks are driven to a LOW value and held there and the VCO and PLLs are also powered down. All clocks are shut down in a synchronous manner so has not to cause glitches while transitioning to the low 'stopped' state. When PWRDWN# is deasserted the clocks should remain stopped until the VCO is stable and within specification ( $t_{STABLE}$ ). A stopped clock is either tri-stated or driven low depending on the state of the tri-state enable I<sup>2</sup>C register bit. CY25822 clocks that are stopped in the driven state are driven low.

The CLKIN input must be on and within specified operating parameters before PWRDWN# is asserted and it must remain in this state while PWRDWN# is asserted.

## **CLKOUT and REFOUT Enable Clarification**

The CLKOUT enable and REFOUT enable I<sup>2</sup>C register bits are used to shot-off the CLKOUT and REFOUT clocks individually. The VCO and crystal oscillator must remain on. A shutdown clock is driven low. ALL clocks need to be stopped in a predictable manner. All clocks need to be shutdown without any glitches or other abnormal behavior while transitioning to a stopped state. Similarly when CLKOUT or REFOUT is enabled the clock must start in a predictable manner without any glitches or abnormal behavior.

#### Table 5. Absolute Maximum Ratings

| Parameter          | Description                       | Condition                   | Min. | Max.                  | Unit  |

|--------------------|-----------------------------------|-----------------------------|------|-----------------------|-------|

| V <sub>DD</sub>    | Core Supply Voltage               |                             | -0.5 | 4.6                   | V     |

| V <sub>DD_A</sub>  | Analog Supply Voltage             |                             | -0.5 | 4.6                   | V     |

| V <sub>IN</sub>    | Input Voltage                     | Relative to V <sub>SS</sub> | -0.5 | V <sub>DD</sub> + 0.5 | VDC   |

| T <sub>S</sub>     | Temperature, Storage              | Non Functional              | -65  | +150                  | °C    |

| Τ <sub>Α</sub>     | Temperature, Operating Ambient    | Functional                  | 0    | 70                    | °C    |

| Τ <sub>J</sub>     | Temperature, Junction             | Functional                  | -    | 150                   | °C    |

| ESD <sub>HBM</sub> | ESD Protection (Human Body Model) | MIL-STD-883, Method 3015    | 2000 | -                     | Volts |

| UL-94              | Flammability Rating               | @1/8 in.                    | V    | -0                    |       |

| MSL                | Moisture Sensitivity Level        |                             |      | 1                     |       |

\_\_\_\_\_

## Table 6. DC Parameters (T<sub>A</sub> = 0°C to +70°C, V<sub>DD</sub> = $3.3V \pm 5\%$ )

| Parameter        | Description               | Condition               | Min.                 | Max                   | Unit | Notes                                                                                   |

|------------------|---------------------------|-------------------------|----------------------|-----------------------|------|-----------------------------------------------------------------------------------------|

| V <sub>DD</sub>  | Supply Voltage            | -                       | 3.135                | 3.465                 | V    | $V_{DD} = 3.3 \pm 5\%$                                                                  |

| V <sub>IH</sub>  | Input High Voltage        | -                       | 2.0                  | V <sub>DD</sub> + 0.3 | V    |                                                                                         |

| V <sub>IL</sub>  | Input Low Voltage         | -                       | V <sub>SS</sub> -0.3 | 0.8                   | V    |                                                                                         |

| I <sub>IL1</sub> | Input Leakage Current     | SCLOCK<br>or SDATA      | -25                  | +25                   | μA   |                                                                                         |

| I <sub>IL2</sub> | Input Leakage Current     | PWRDWN#                 | -75                  | -15                   | μΑ   |                                                                                         |

| V <sub>OH</sub>  | Output High Voltage       | I <sub>OH</sub> = -4 mA | 2.4                  | -                     | V    | Single edge is required to<br>be monotonic when transi-<br>tioning through this region. |

| V <sub>OL</sub>  | Output Low Voltage        | I <sub>OL</sub> = 4 mA  | _                    | 0.4                   | V    | Single edge is required to be monotonic when transi-<br>tioning through this region.    |

| C <sub>IN</sub>  | Input Pin Capacitance     | -                       | _                    | 5                     | pF   |                                                                                         |

| C <sub>OUT</sub> | Output Pin Capacitance    | -                       | _                    | 6                     | pF   |                                                                                         |

| L <sub>IN</sub>  | Pin Inductance            | -                       | _                    | 7                     | nH   |                                                                                         |

| T <sub>A</sub>   | Ambient Temperature       | -                       | 0                    | 70                    | °C   | No air flow                                                                             |

| I <sub>DD1</sub> | Supply Current            | @ 66 MHz                | -                    | 50                    | mA   |                                                                                         |

| I <sub>DD2</sub> | Supply Current            | @ 48 MHz                | _                    | 40                    | mA   |                                                                                         |

| I <sub>PD</sub>  | Power Down Supply Current | _                       | -                    | 500                   | μΑ   |                                                                                         |

Table 7. AC Parameters (T<sub>A</sub> = 0°C to +70°C, V<sub>DD</sub> =  $3.3V \pm 5\%$ )

| Parameter                            | Description          | Conditions                                        | Min. | Max.  | Unit | Notes                                                     |

|--------------------------------------|----------------------|---------------------------------------------------|------|-------|------|-----------------------------------------------------------|

| t <sub>HIGH</sub>                    | CLK High Time, 48MHz | Measured @2.4V                                    | 9.45 | 10.95 | ns   | Specification applies to 48MHz output mode.               |

| t <sub>LOW</sub>                     | CLK, Low Time, 48MHz | Measured @0.4V                                    | 8.50 | 10.10 | ns   | Specification applies to 48MHz output mode.               |

| t <sub>HIGH</sub>                    | CLK High Time, 66MHz | Measured @2.4V                                    | 6.85 | 7.90  | ns   | Specification applies to 66.7MHz output mode.             |

| t <sub>LOW</sub>                     | CLK Low Time, 66MHz  | Measured @0.4V                                    | 5.95 | 6.95  | ns   | Specification applies to 66.7MHz output mode.             |

| t <sub>RISEH1</sub>                  | Rising Edge Rate     | Measured from 0.4V to 2.4V<br>REFOUT and CLOCKOUT | 2.0  | 5.0   | V/ns | High Buffer Strength<br>Refer to I <sup>2</sup> C Control |

| t <sub>FALLH1</sub>                  | Falling Edge Rate    | Measured from 2.4V to 0.4V<br>REFOUT and CLOCKOUT | 2.0  | 5.0   | V/ns | High Buffer Strength<br>Refer to I <sup>2</sup> C Control |

| t <sub>RISEL1</sub> Rising Edge Rate |                      | Measured from 0.4V to 2.4V<br>REFOUT and CLOCKOUT | 1.33 | 4.0   | V/ns | Low Buffer Strength<br>Refer to I <sup>2</sup> C Control  |

| Parameter           | Description                                                         | Conditions                                                         | Min. | Max. | Unit | Notes                                                     |

|---------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|------|------|------|-----------------------------------------------------------|

| t <sub>FALLL1</sub> | Falling Edge Rate                                                   | Measured from 2.4V to 0.4V<br>REFOUT and CLOCKOUT                  | 1.33 | 4.0  | V/ns | Low Buffer Strength<br>Refer to I <sup>2</sup> C Control  |

| t <sub>RISEH2</sub> | Rise Time                                                           | Measured from 0.4V to 2.4V<br>REFOUT and CLOCKOUT                  | 0.4  | 1.0  | ns   | High Buffer Strength<br>Refer to I <sup>2</sup> C Control |

| t <sub>FALLH2</sub> | Fall Time                                                           | Measured from 2.4V to 0.4V<br>REFOUT and CLOCKOUT                  | 0.4  | 1.0  | ns   | High Buffer Strength<br>Refer to I <sup>2</sup> C Control |

| t <sub>RISEL2</sub> | Rise Time                                                           | Measured from 0.4V to 2.4V<br>REFOUT and CLOCKOUT                  | 0.5  | 1.5  | ns   | Low Buffer Strength<br>Refer to I <sup>2</sup> C Control  |

| t <sub>FALLL2</sub> | Fall Time                                                           | Measured from 2.4V to 0.4V<br>REFOUT and CLOCKOUT                  | 0.5  | 1.5  | ns   | Low Buffer Strength<br>Refer to I <sup>2</sup> C Control  |

| T <sub>CYC1</sub>   | Cycle to Cycle Jitter                                               | REFOUT                                                             | _    | 500  | ps   | SSCG is ON                                                |

| T <sub>CYC2</sub>   | Cycle to Cycle Jitter                                               | CLOCKOUT                                                           | _    | 250  | ps   | SSCG is ON                                                |

| LTJ                 | 10µS Period Jitter<br>(100KHz, Frequency Mod-<br>ulation Amplitude) | Applies to REFOUT at all<br>times and CLOCKOUT when<br>SSCG is Off | -    | 2.0  | ns   | _                                                         |

| t <sub>START</sub>  | Start up time                                                       | From VDD = 2.0 V                                                   | _    | 3.0  | ms   | All outputs disabled                                      |

## Table 7. AC Parameters (T<sub>A</sub> = 0°C to +70°C, V<sub>DD</sub> = 3.3V ± 5%) (continued)

#### Table 8. Signal Loading Table

| Clock Name     | Max Load (pF) |  |  |

|----------------|---------------|--|--|

| CLKOUT, REFOUT | 15            |  |  |

## **Ordering Information**

| Part Number  | Package Type               | Product Flow            |

|--------------|----------------------------|-------------------------|

| CY25822SC-2  | 8-pin SOIC                 | Commercial, 0°C to 70°C |

| CY25822SC-2T | 8-pin SOIC – Tape and Reel | Commercial, 0°C to 70°C |

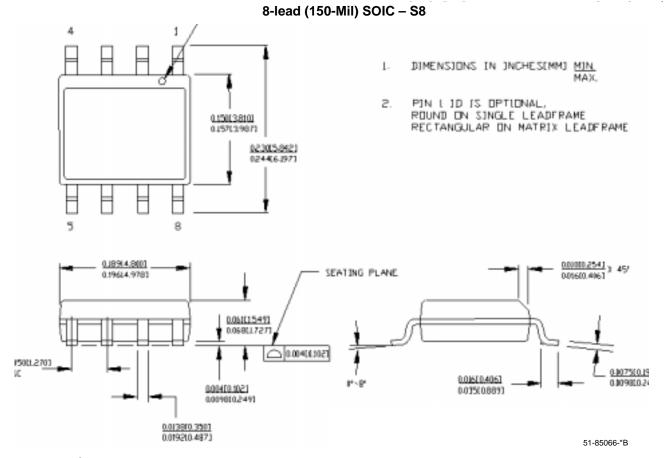

## Package Diagram

Purchase of I<sup>2</sup>C components from Cypress, or one of its sublicensed Associated Companies, conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.All product and company names mentioned in this document are trademarks of their respective holders.

© Cypress Semiconductor Corporation, 2003. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems provided from the manufacturer assumes all risk of such use and in doing of indemnifies Cypress Semiconductor against all charges.

## **Document History Page**

| Document Title: CY25822-2 CK-SSC Spread Spectrum Clock Generator<br>Document Number: 38-07531 |         |               |                    |                       |  |

|-----------------------------------------------------------------------------------------------|---------|---------------|--------------------|-----------------------|--|

| REV.                                                                                          | ECN NO. | Issue<br>Date | Orig. of<br>Change | Description of Change |  |

| **                                                                                            | 124462  | 03/19/03      | RGL                | New Data Sheet        |  |

Free Manuals Download Website <u>http://myh66.com</u> <u>http://usermanuals.us</u> <u>http://www.somanuals.com</u> <u>http://www.4manuals.cc</u> <u>http://www.4manuals.cc</u> <u>http://www.4manuals.cc</u> <u>http://www.4manuals.com</u> <u>http://www.404manual.com</u> <u>http://www.luxmanual.com</u> <u>http://aubethermostatmanual.com</u> Golf course search by state

http://golfingnear.com Email search by domain

http://emailbydomain.com Auto manuals search

http://auto.somanuals.com TV manuals search

http://tv.somanuals.com