3048 MS

# HP 8663A SYNTHESIZED SIGNAL GENERATOR

(Including Options 001, 002, & 003)

# Service Manual

volume 3

SERIAL NUMBERS

This manual applies directly to instruments with serial numbers prefixed:

$2234\mathrm{A}$  to  $2927\mathrm{A}$  and all MAJOR changes that apply to your instrument.

rev.01JUL91

For additional important information about serial numbers, refer to "INSTRUMENTS COVERED BY THIS MANUAL" in Section 1.

Third Edition

This material may be reproduced by or for the U.S. Government pursuant to the Copyright License under the clause at DFARS 52,227-7013 (APR 1988).

Copyright@HEWLETT-PACKARD COMPANY 1982

EAST 24001 MISSION AVENUE, TAF C-34, SPOKANE, WASHINGTON, U.S.A. 99220

Service Manual (Volume 1, 2, 3, 4) HP Part 08663-90071

Other Documents Available:

Operation and Calibration Manual HP Part 08663-90069

Microfiche Service Manual HP Part 08663-90072

Microfiche Operation and Calibration Manual HP Part 08663-90070

Printed in U.S.A.: November 1990

# **COPYRIGHT AND DISCLAIMER NOTICE**

Copyright – Agilent Technologies, Inc. Reproduced with the permission of Agilent Technologies Inc. Agilent Technologies, Inc. makes no warranty of any kind with regard to this material including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Agilent Technologies, Inc. is not liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material or data.

Model 8663A Volume 3 Contents

# **VOLUME 3 CONTENTS**

| Schematic<br>Service<br>Sheet<br>Number | Block<br>Diagram |                     | Assembly or Section                                                    | Theory/Trouble-<br>Shooting<br>Page<br>Number | Parts<br>List<br>Page<br>Number |

|-----------------------------------------|------------------|---------------------|------------------------------------------------------------------------|-----------------------------------------------|---------------------------------|

| SS13                                    | BD3              | A5A4                | Fractional N Loop Reference Divider                                    | 8-401                                         | 6–109                           |

| SS14                                    | BD4              | A5A3                | Fractional N Loop Phase Detector                                       | 8-407                                         | 6–103                           |

| SS15                                    | BD4              | A5A5                | Fractional N Loop VCO                                                  | 8-417                                         | 6–111                           |

| SS16                                    | BD4              | A5A2                | Fractional N Loop N Divider                                            | 8-425                                         | 6-101                           |

| SS17                                    | BD4              | A5A1                | Fractional N Loop Accumulator                                          | 8-433                                         | 6-99                            |

| SS18                                    | BD5              | A3A3                | N Loop Divider/Phase Detector                                          | 8–445                                         | 6–39                            |

| SS19                                    | BD5              | A3A3                | N Loop Divider/Phase Detector                                          | 8–455                                         | 6-39                            |

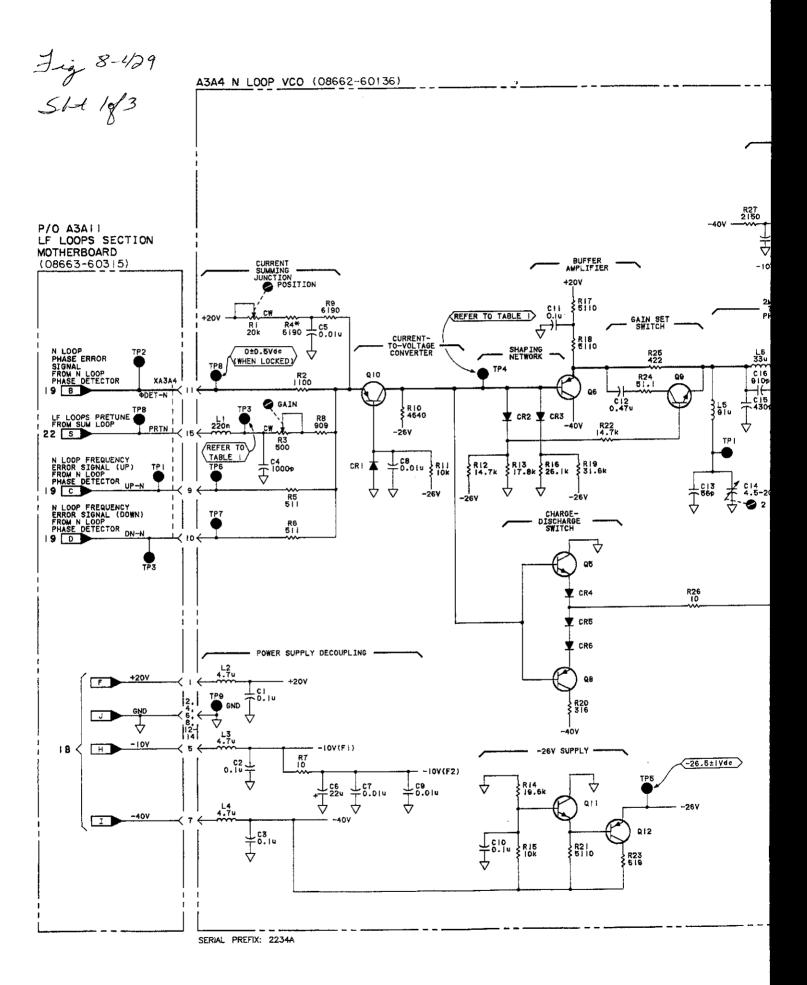

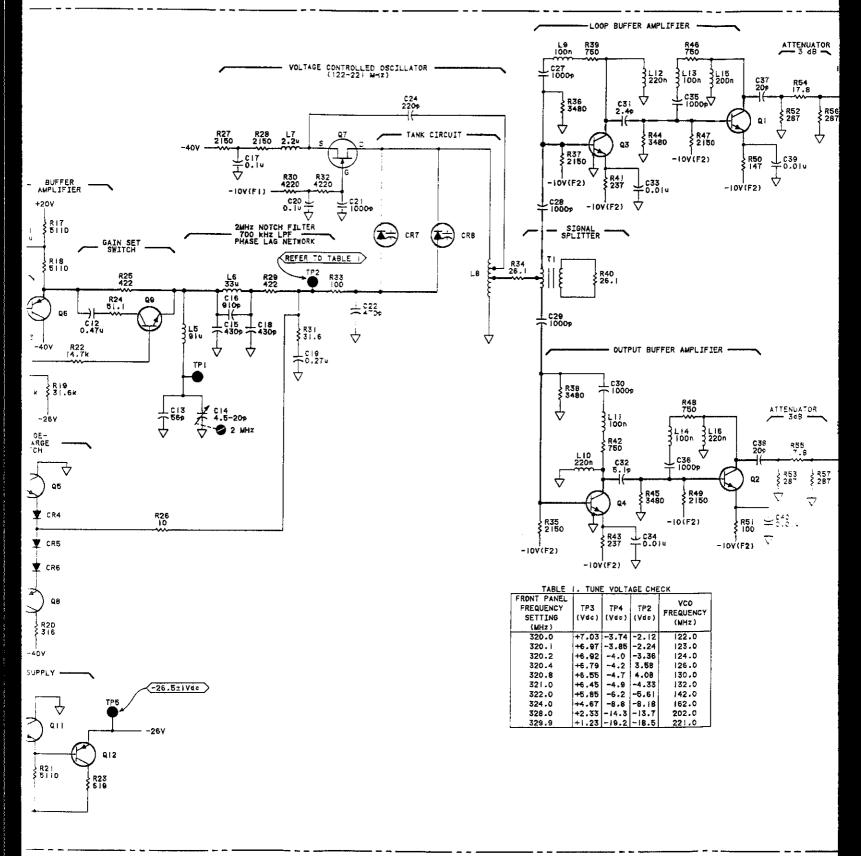

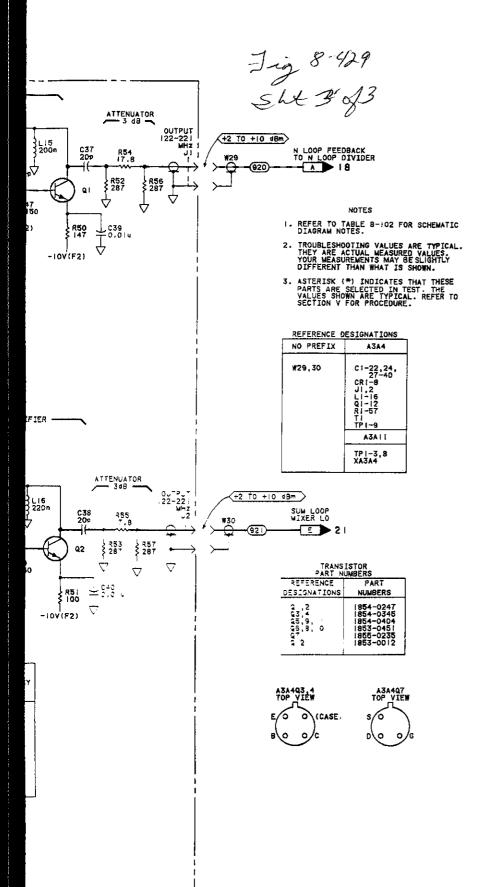

| SS20                                    | BD5              | A3A4                | N Loop VCO                                                             | 8–461                                         | 6–45                            |

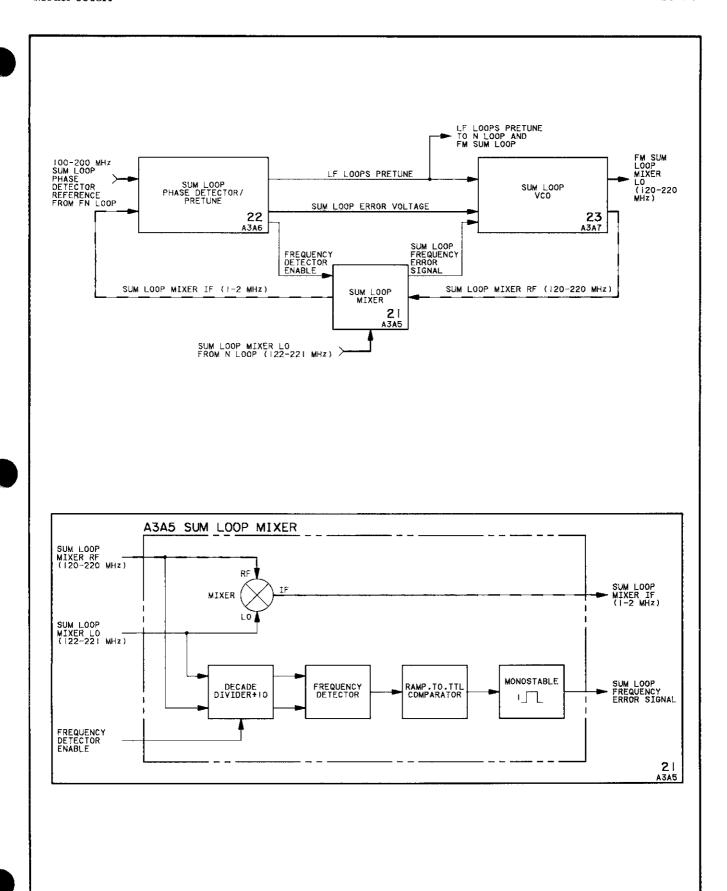

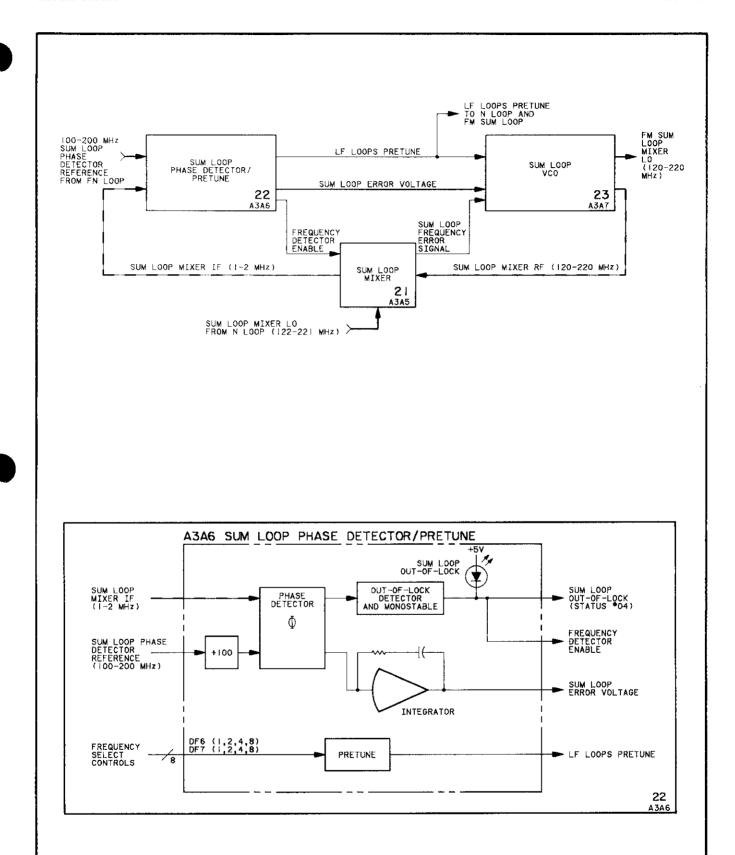

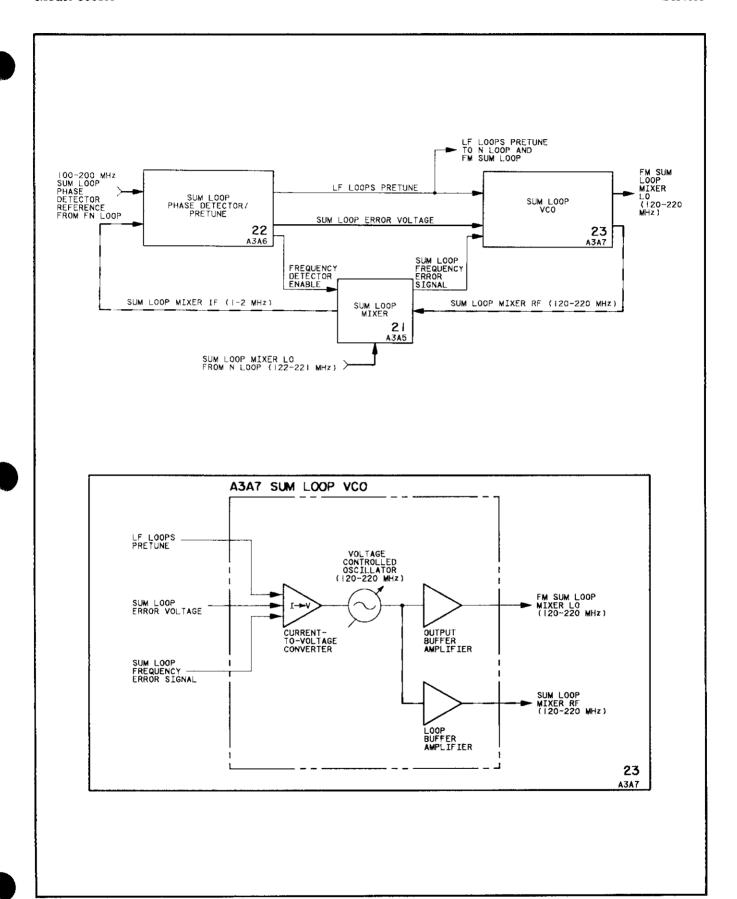

| SS21                                    | BD5              | A3A5                | Sum Loop Mixer                                                         | 8–467                                         | 6–49                            |

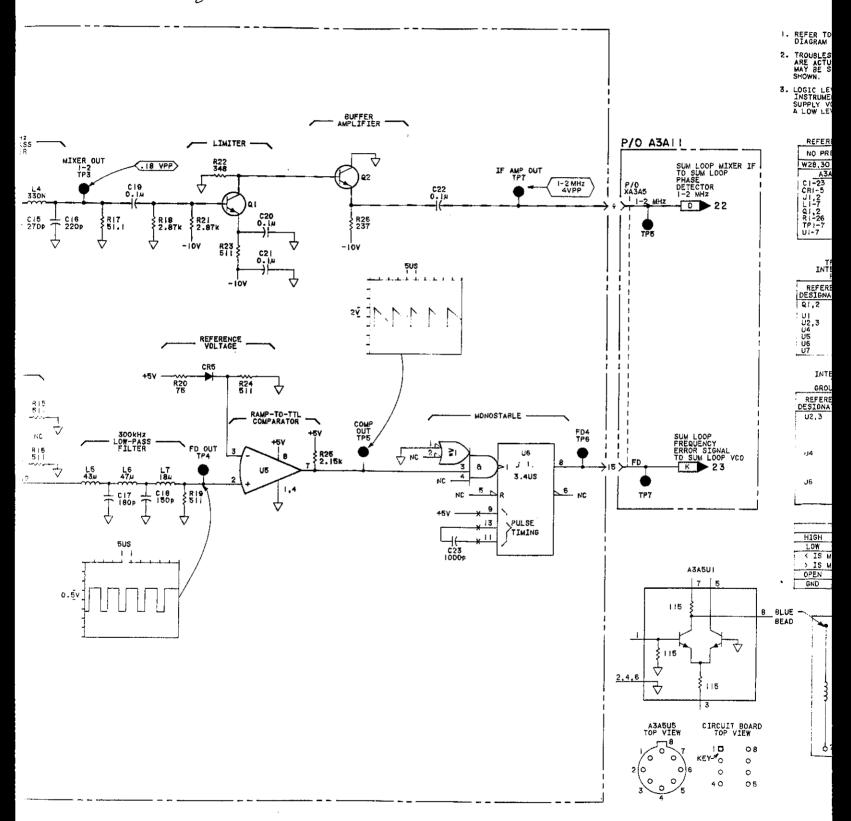

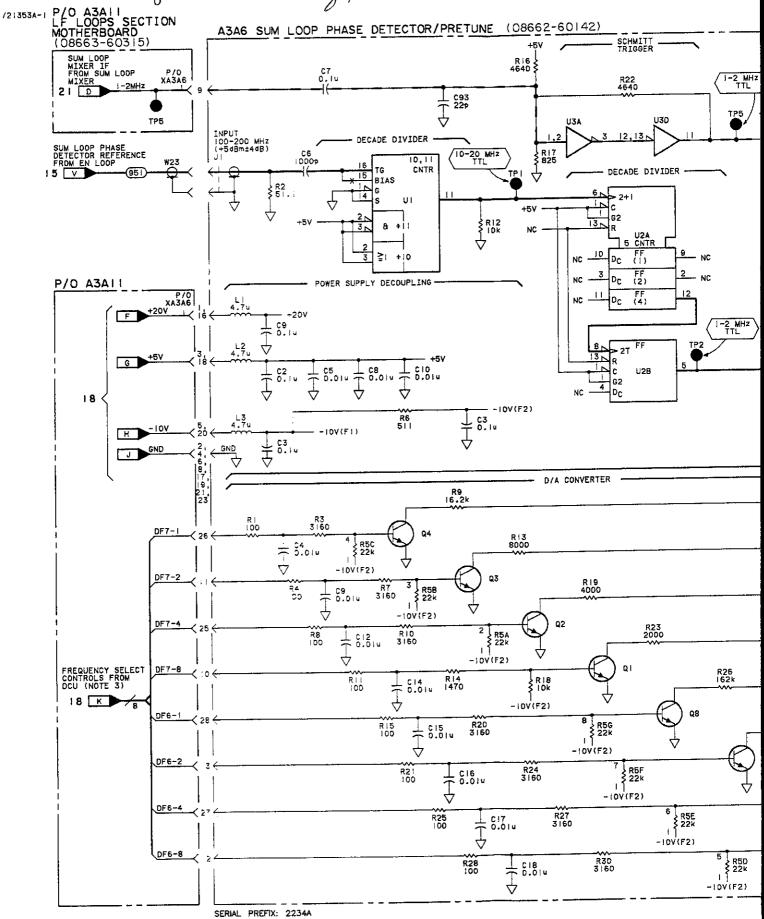

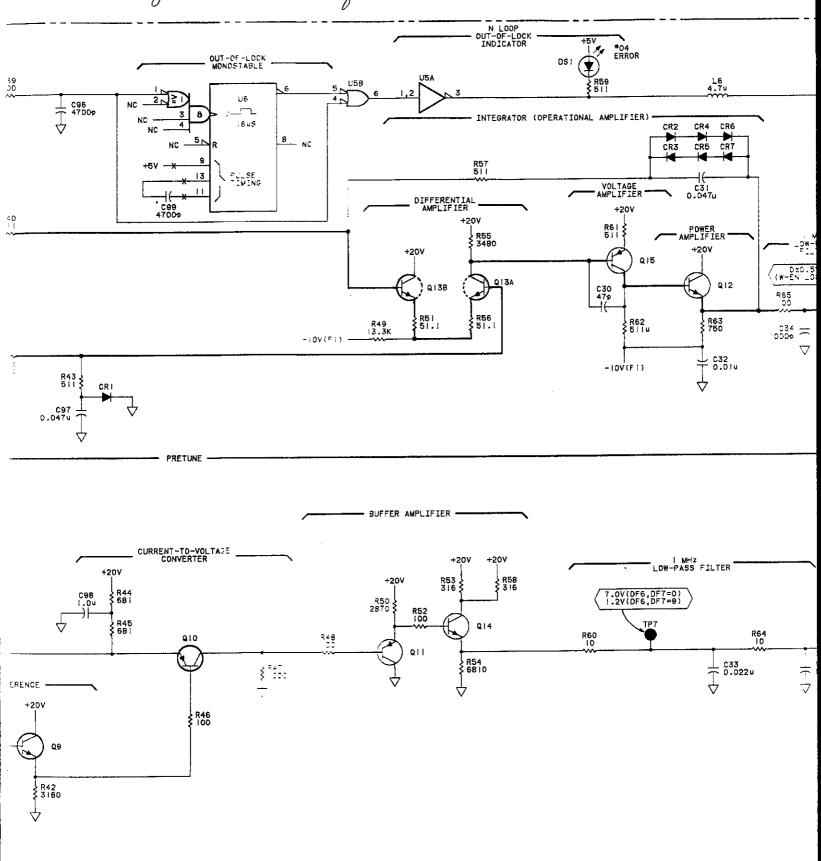

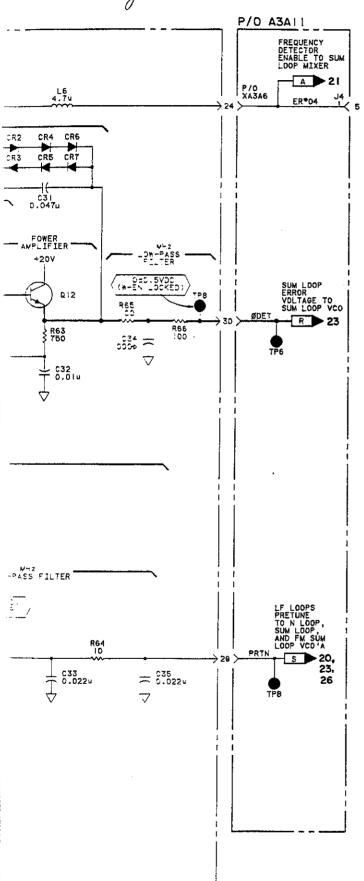

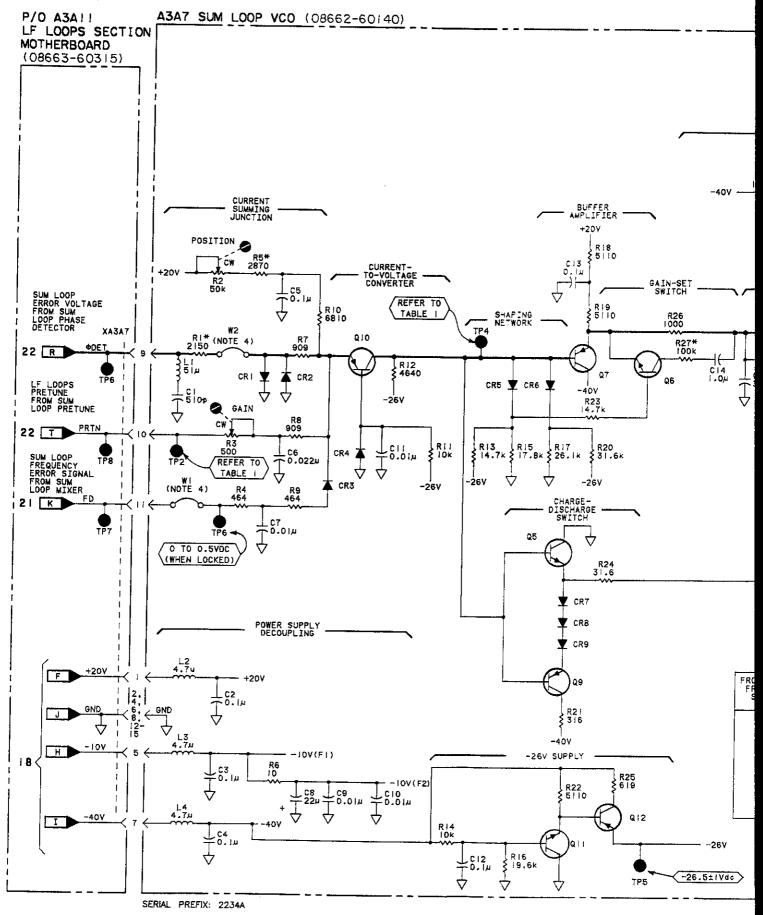

| SS22                                    | BD5              | A3A6                | Sum Loop Phase Detector and Pretune                                    | 8–473                                         | 6–51                            |

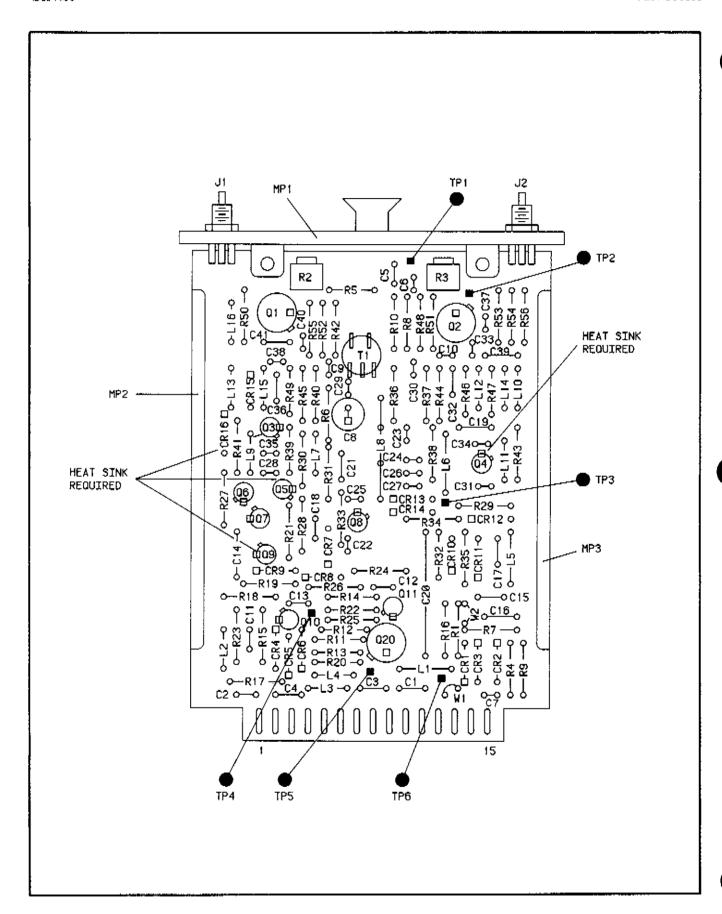

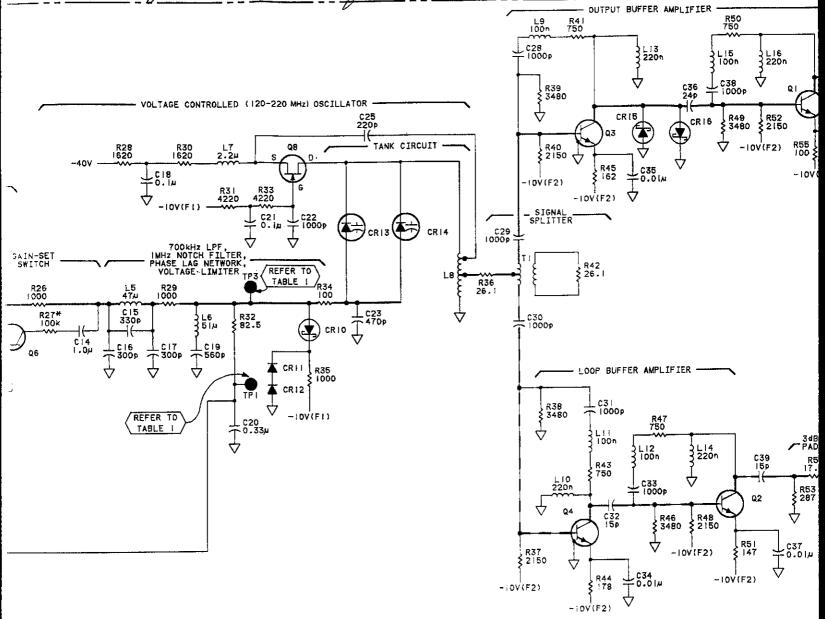

| S\$23                                   | BD5              | A3A7                | Sum Loop VCO                                                           | 8–479                                         | 6-55                            |

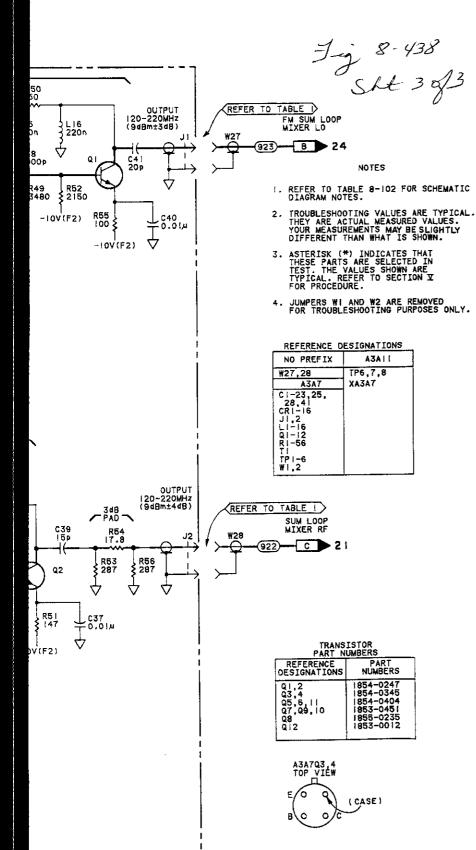

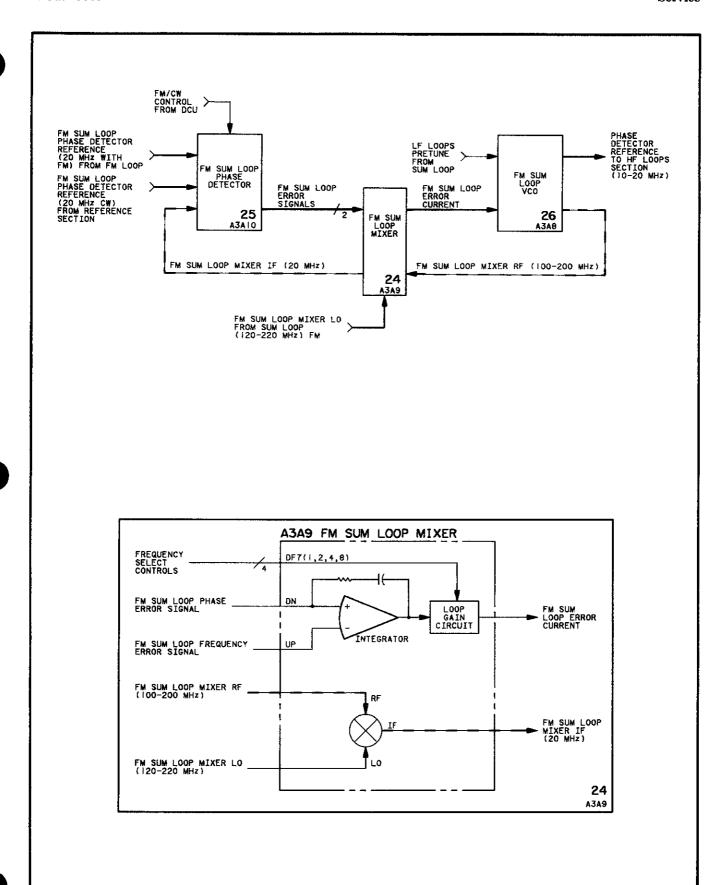

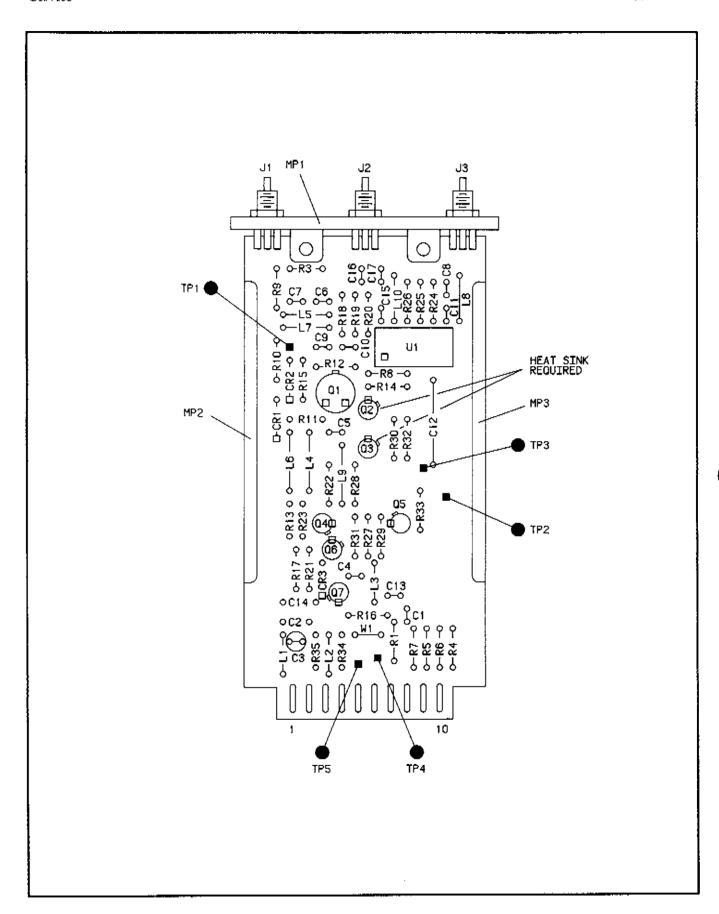

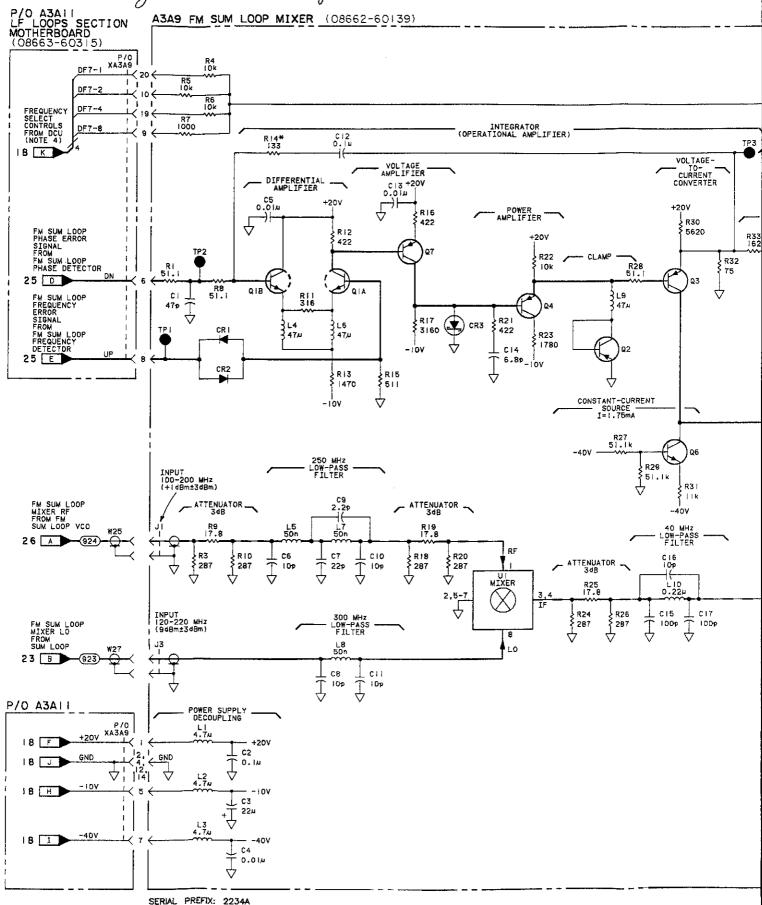

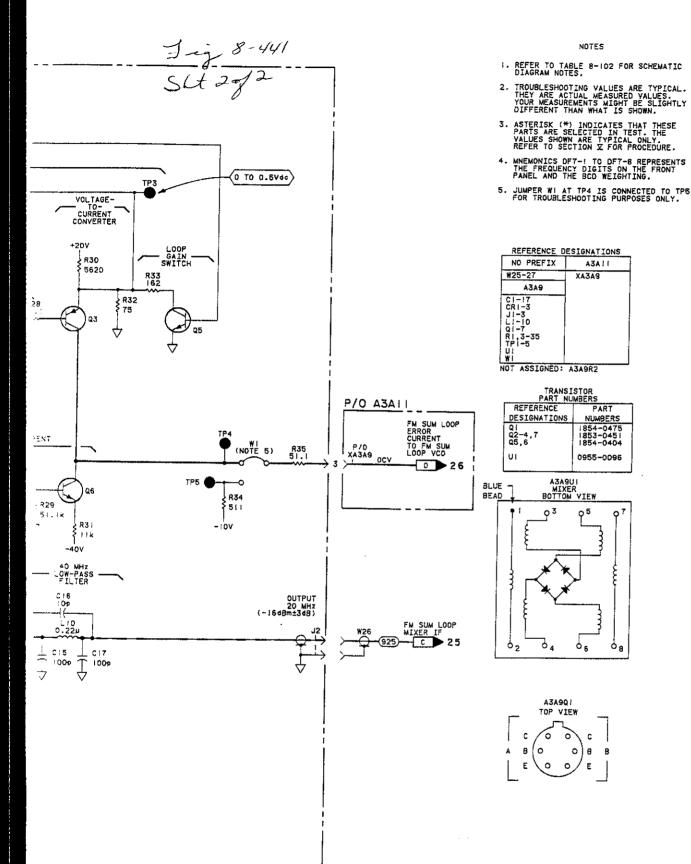

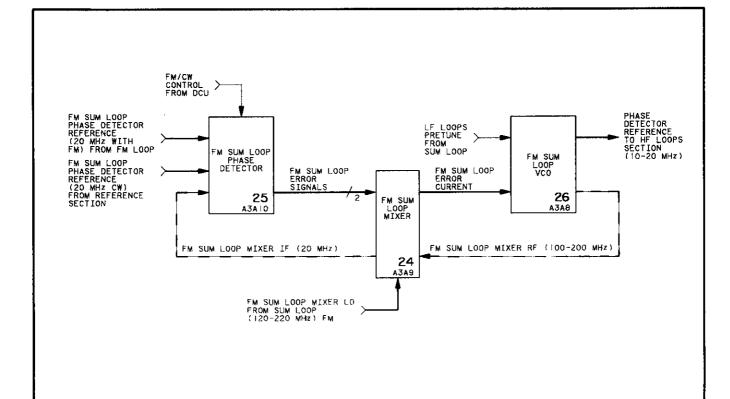

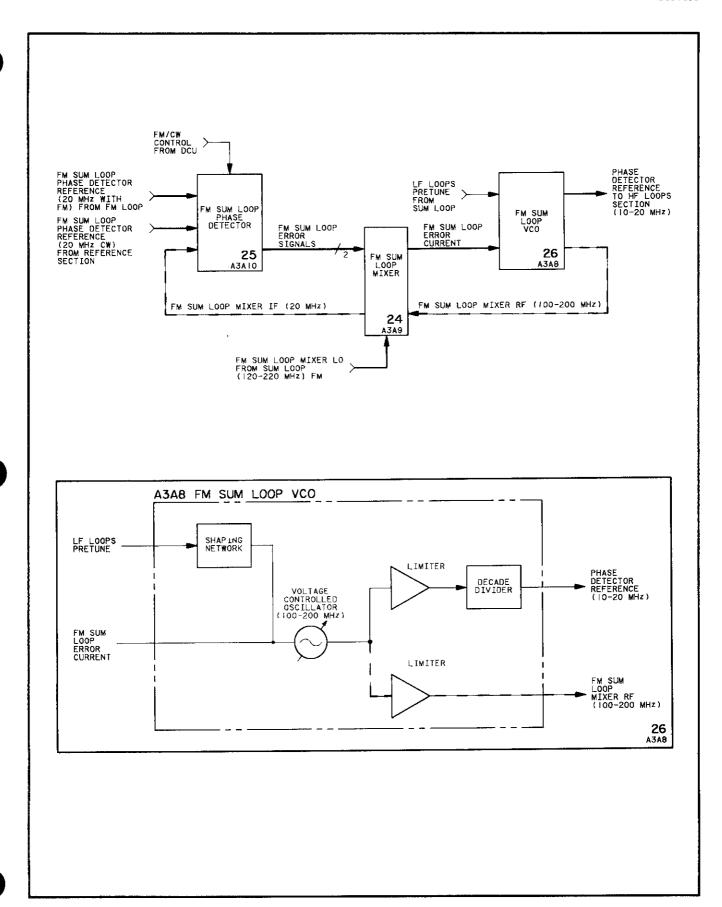

| SS24                                    | BD5              | A3A9                | FM Sum Loop Mixer                                                      | 8-485                                         | 6–63                            |

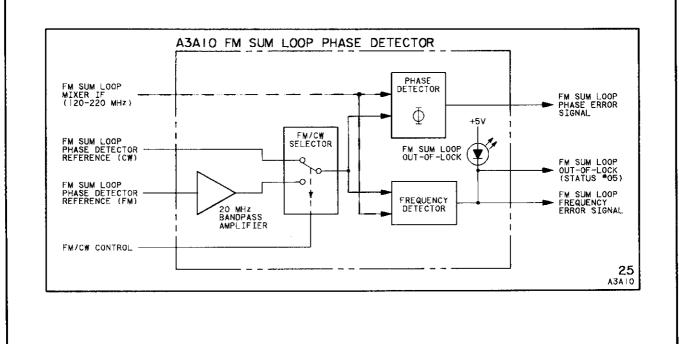

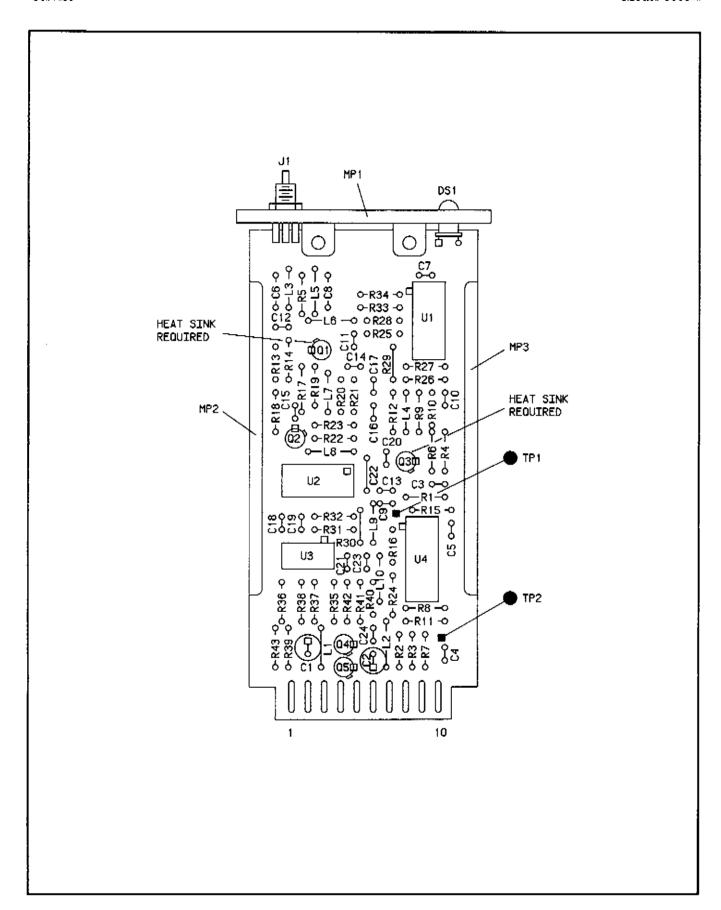

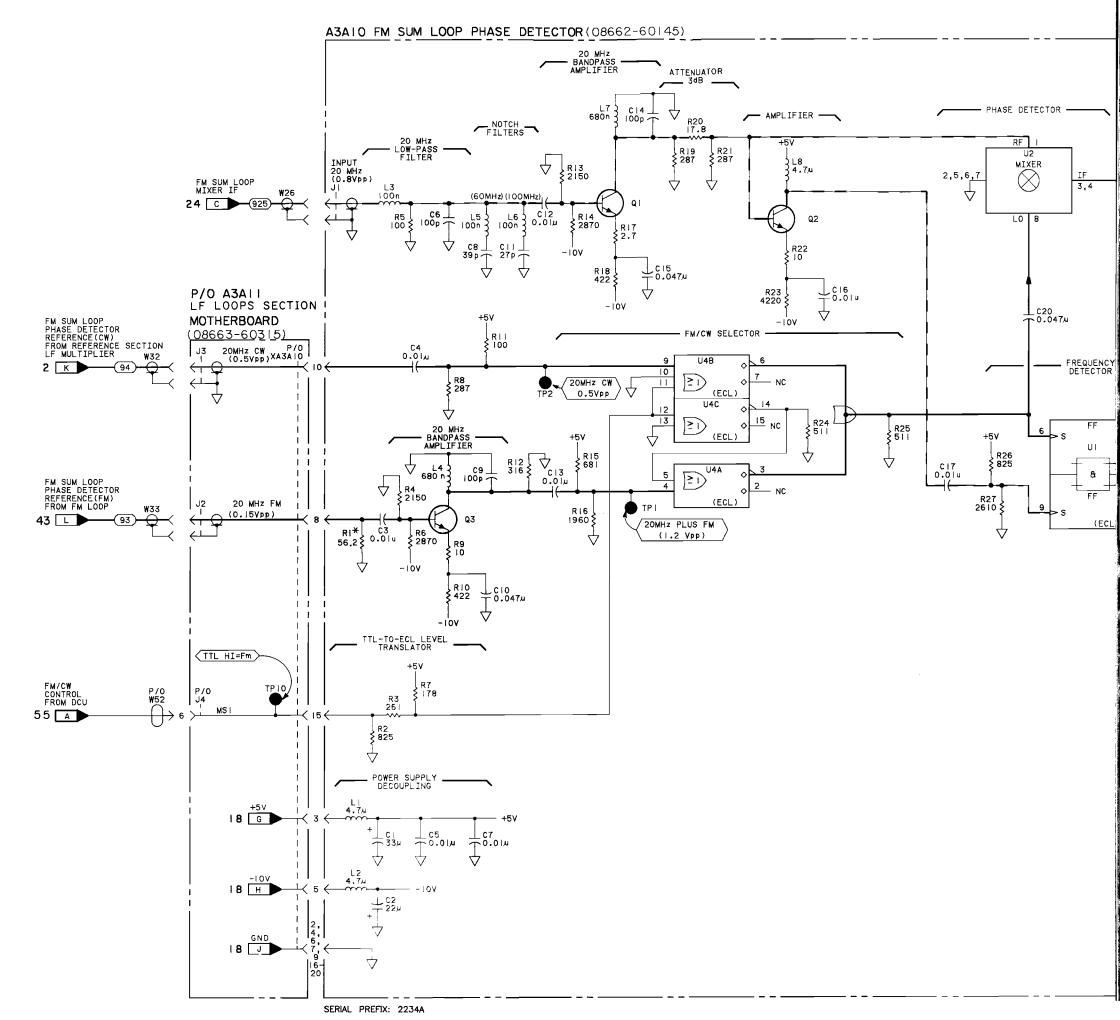

| SS25                                    | BD5              | A3A10               | FM Sum Loop Phase Detector                                             | 8-491                                         | 6-65                            |

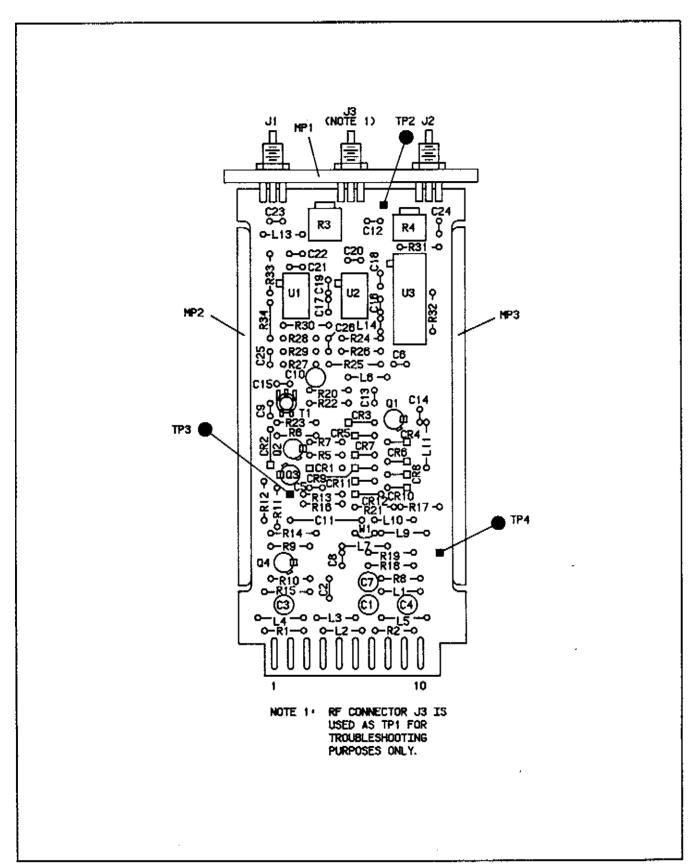

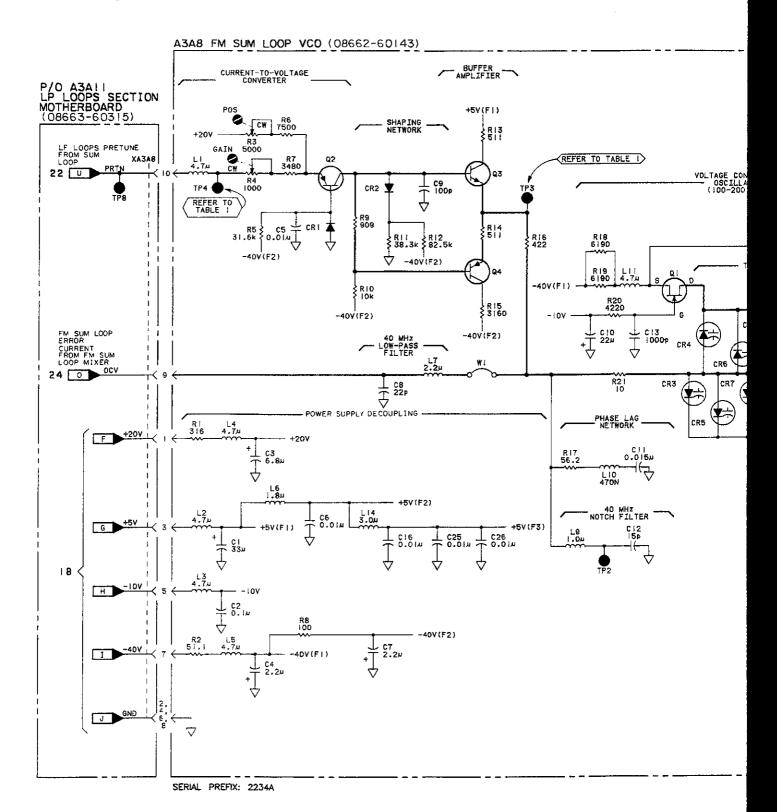

| \$\$26                                  | BD5              | A3A8                | FM Sum Loop VCO                                                        | 8–495                                         | 6-59                            |

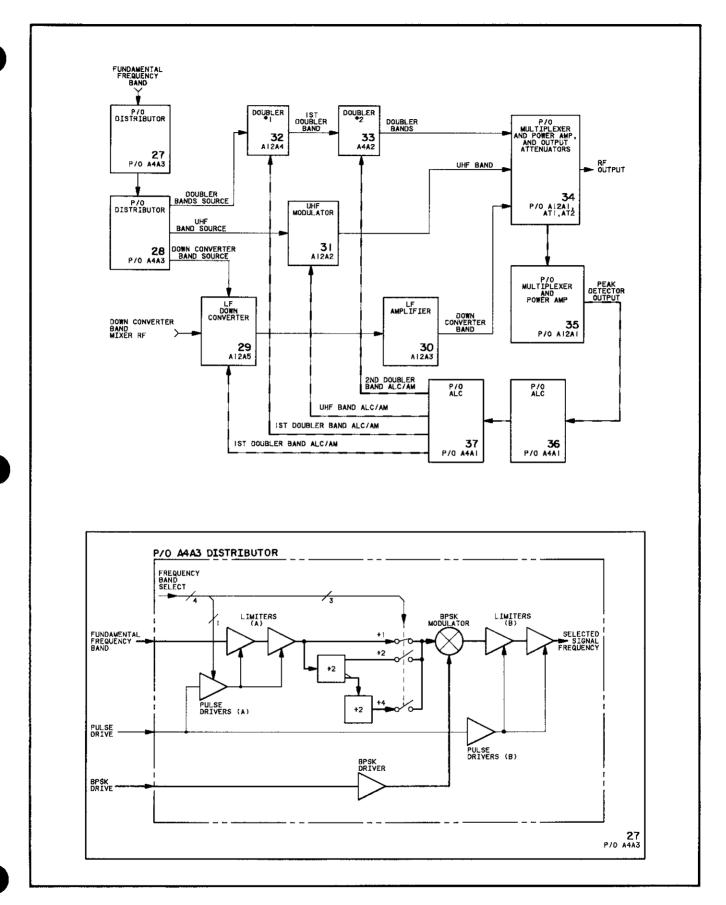

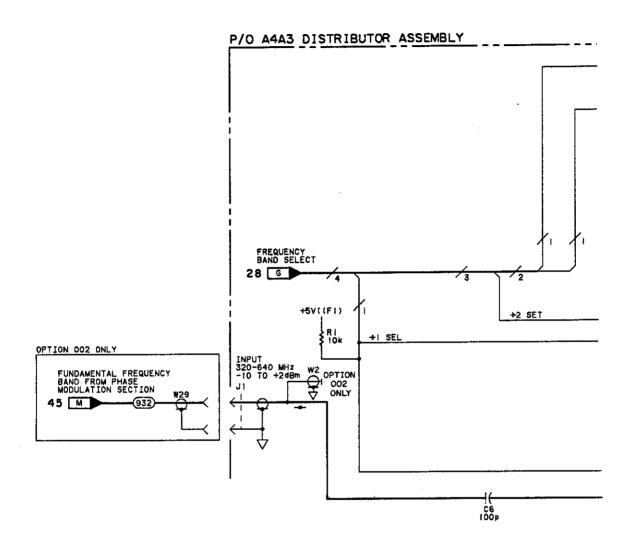

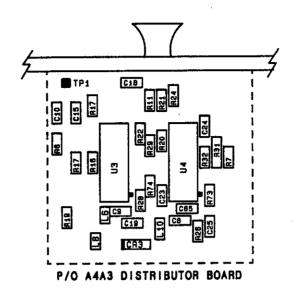

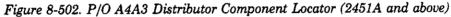

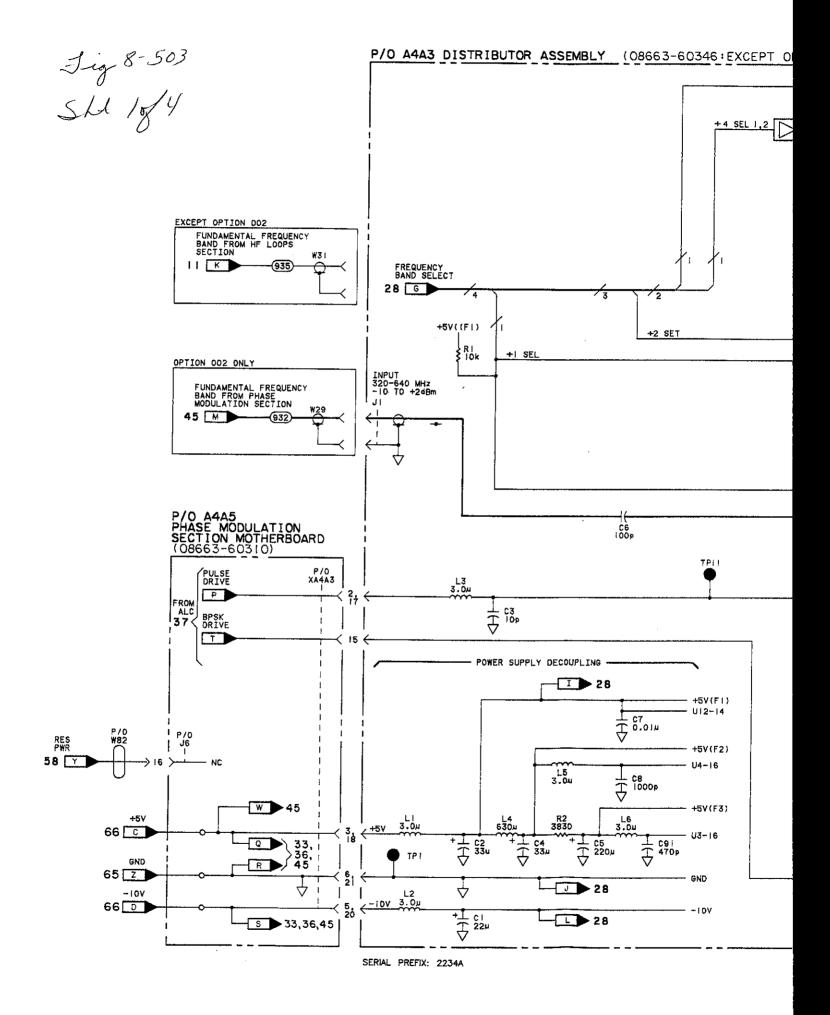

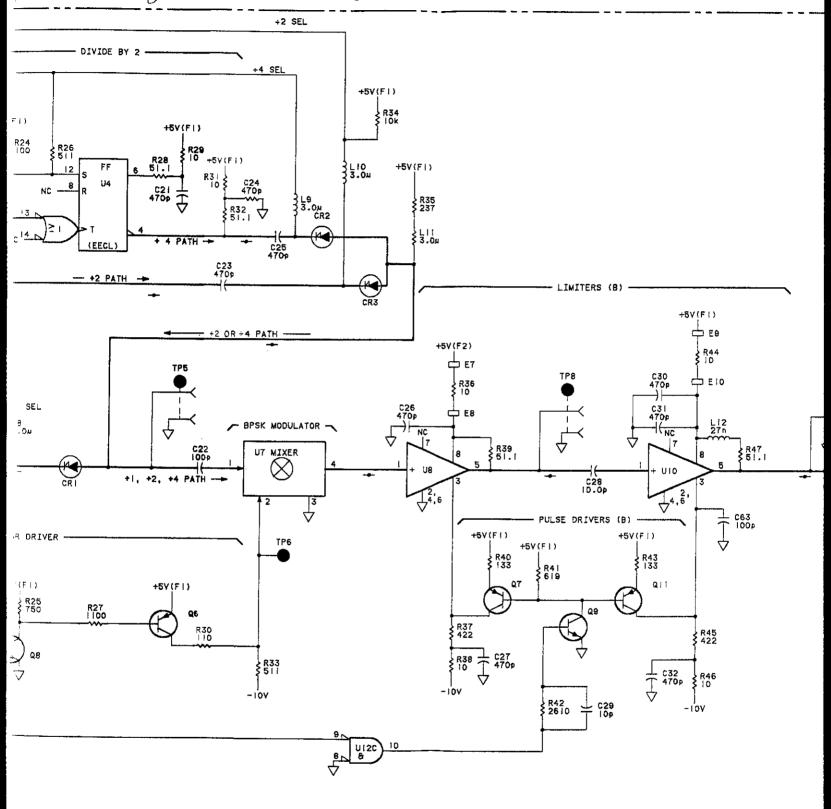

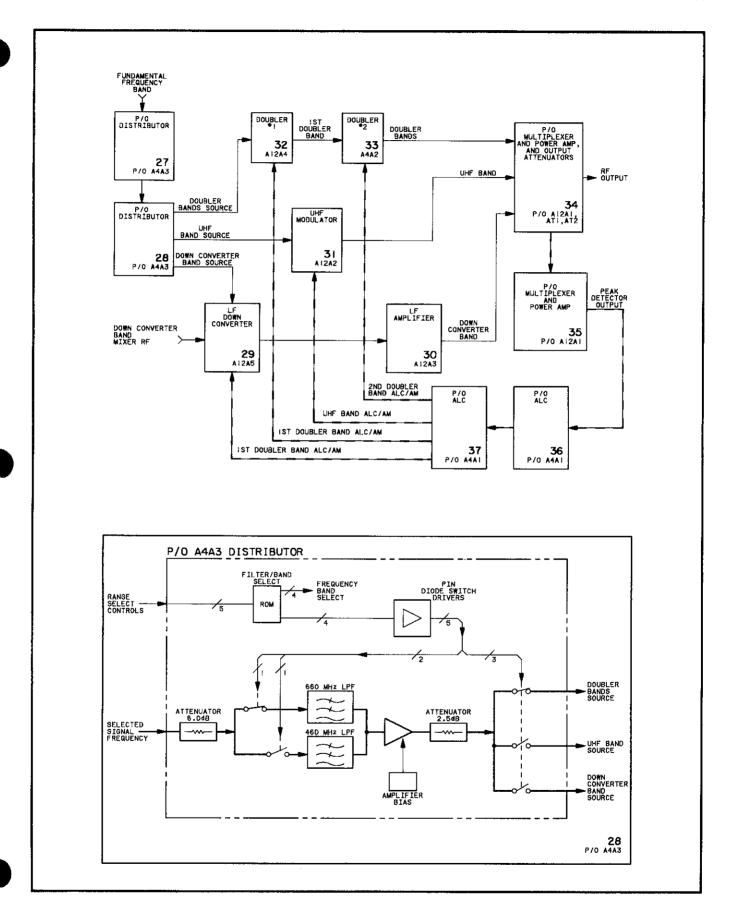

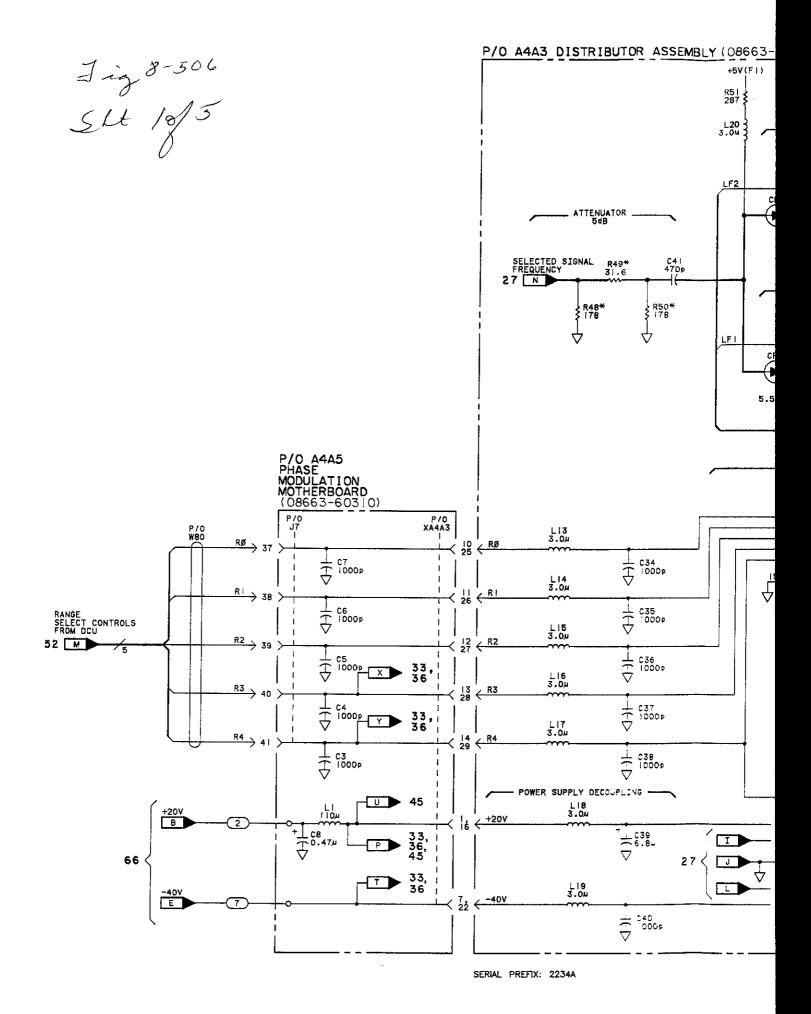

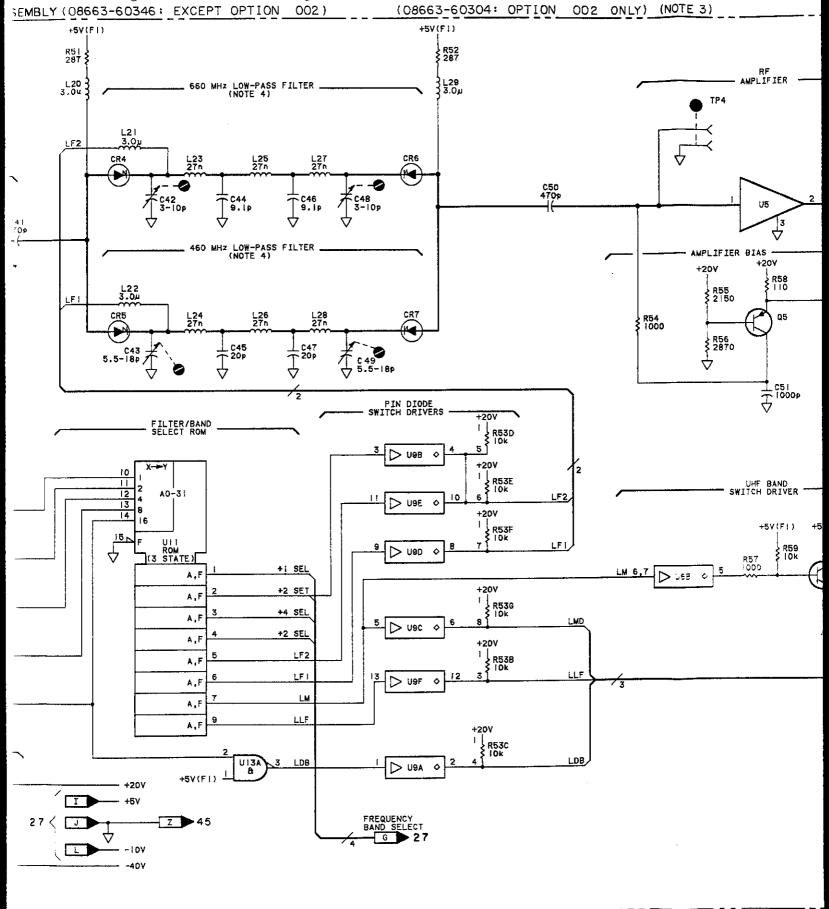

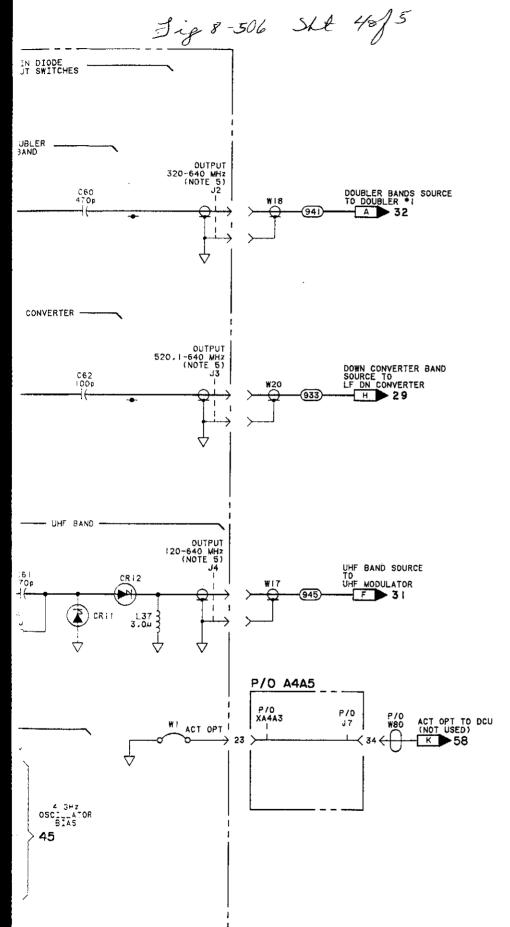

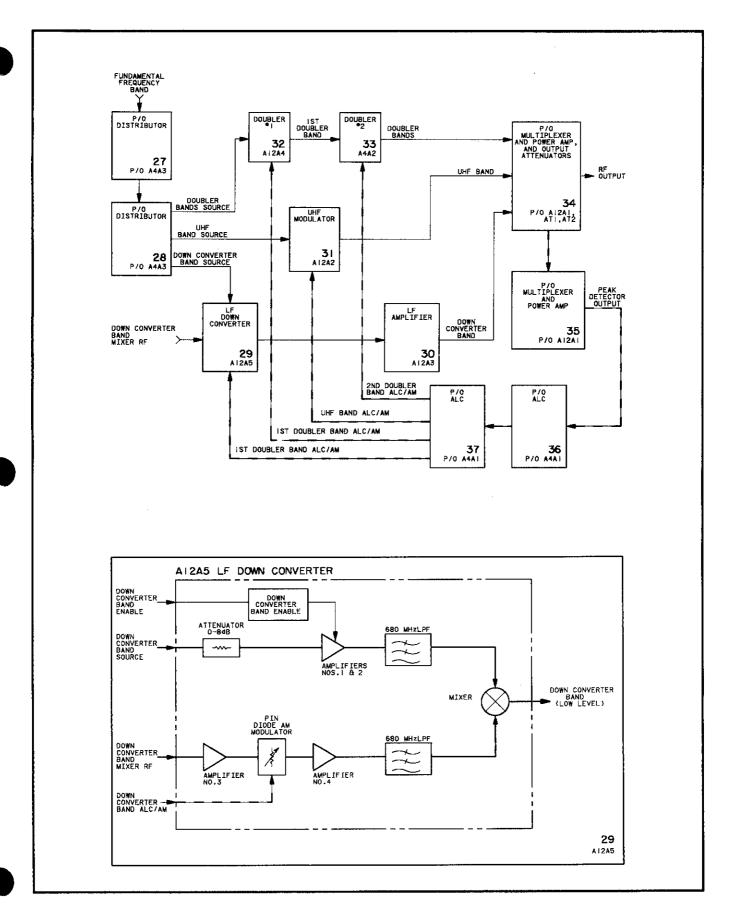

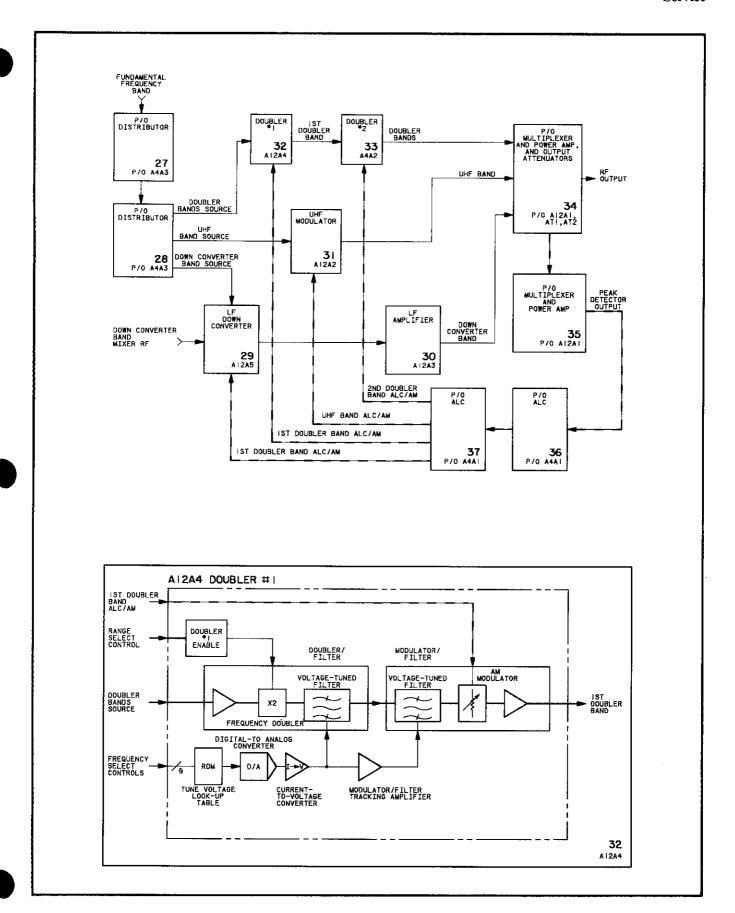

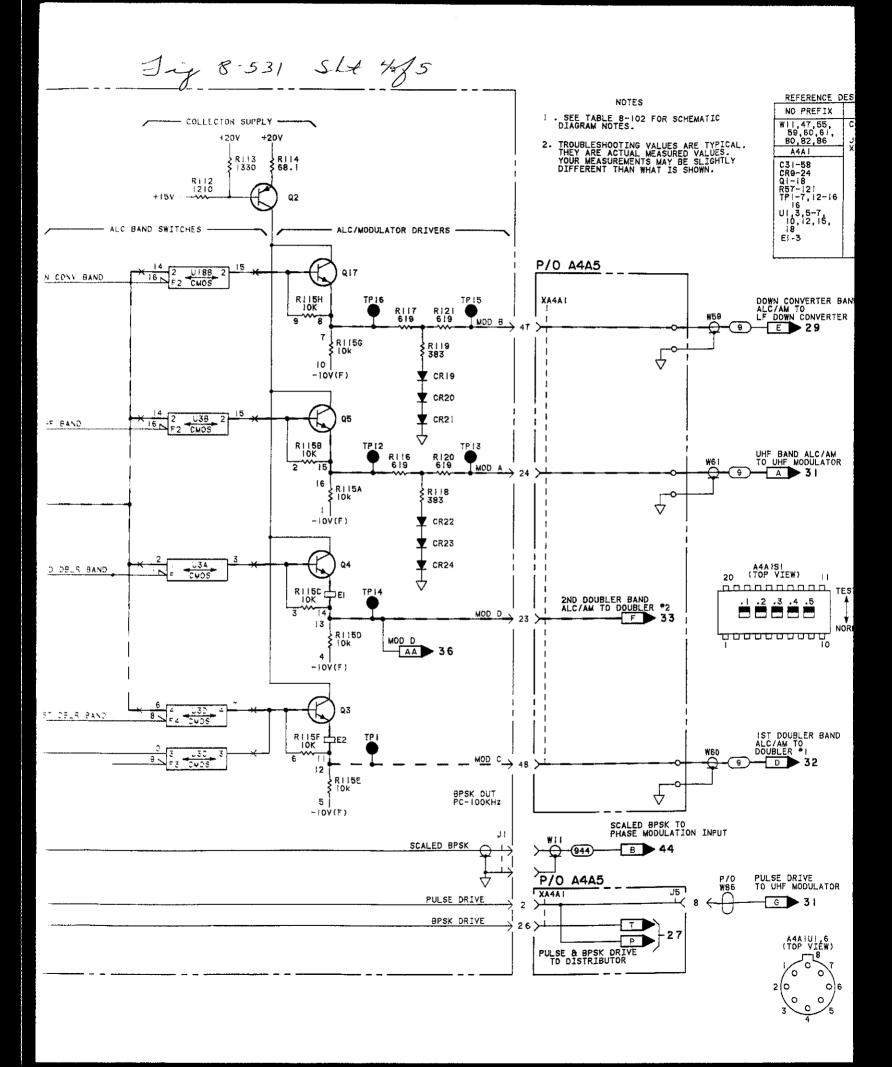

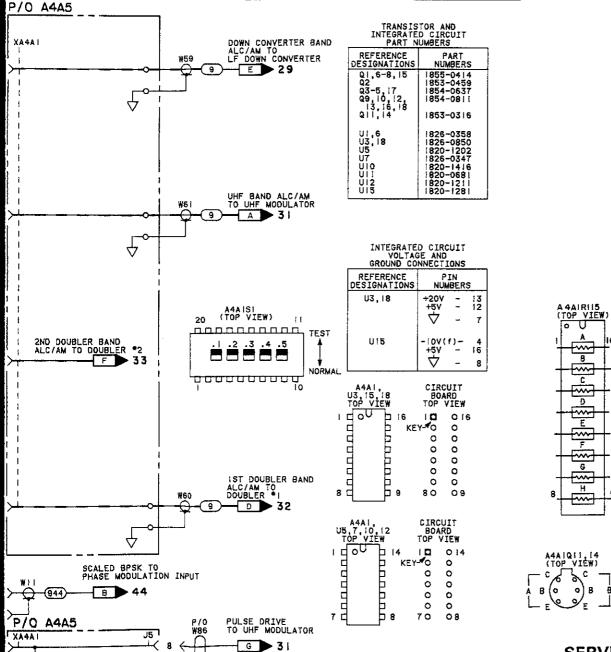

| SS27                                    | BD6              | A4A3                | Distributor                                                            | 8–501                                         | 6-79                            |

| SS28                                    | BD6              | A4A3                | Distributor                                                            | 8–505                                         | 6–79                            |

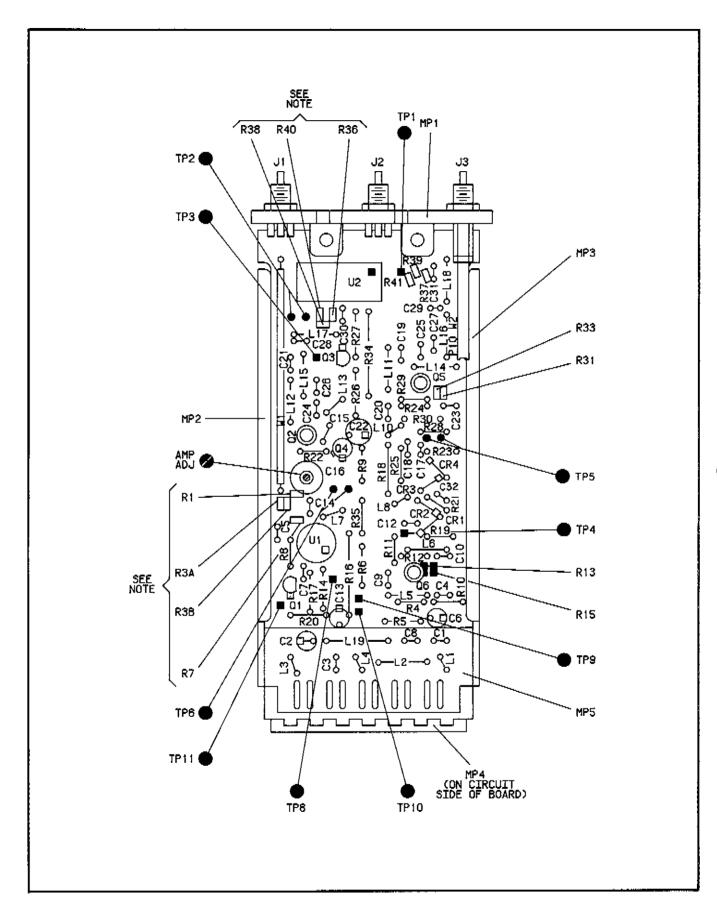

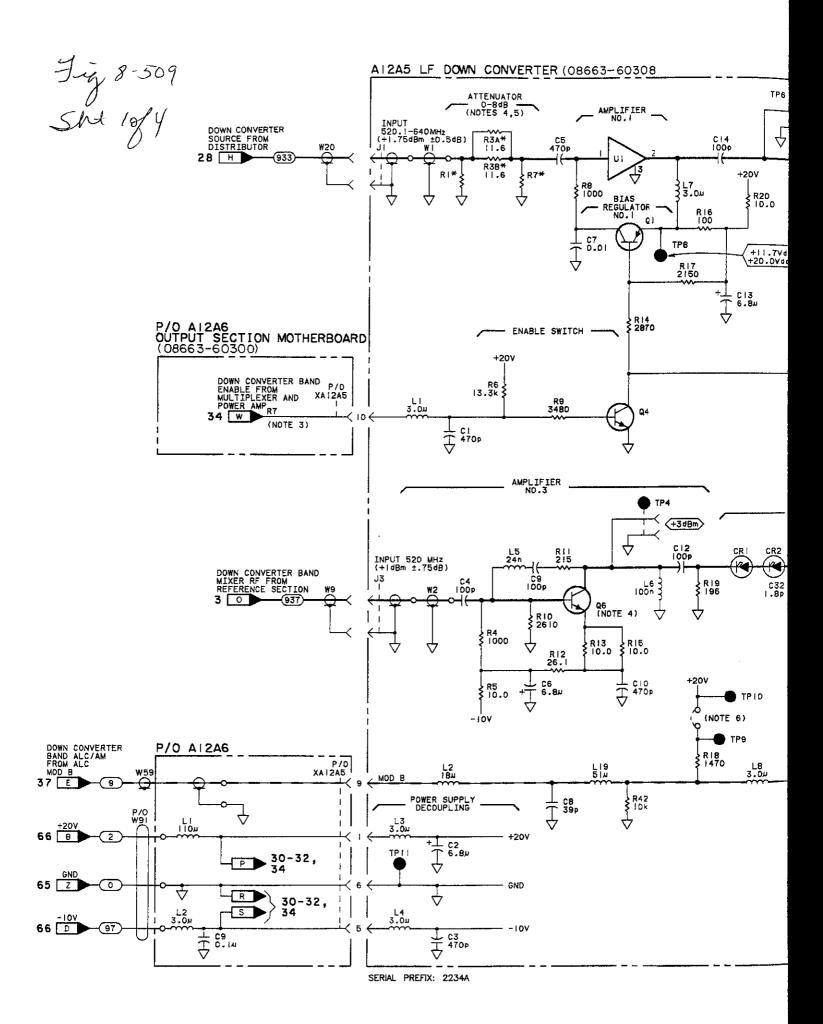

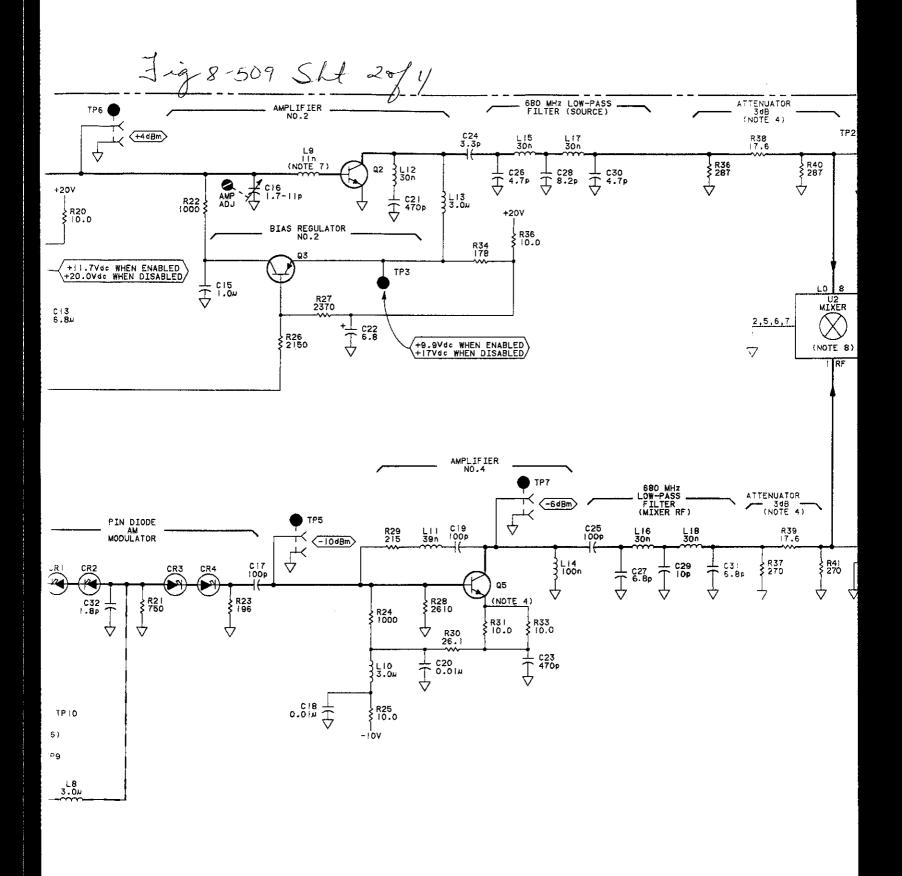

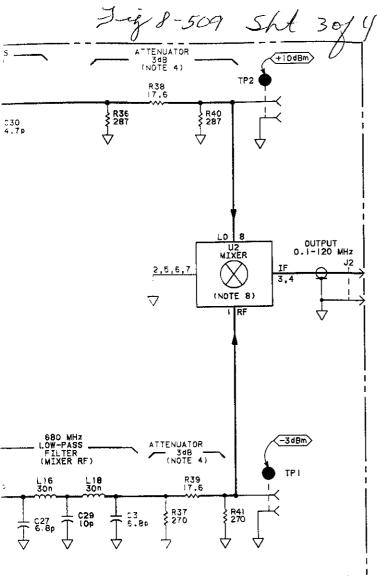

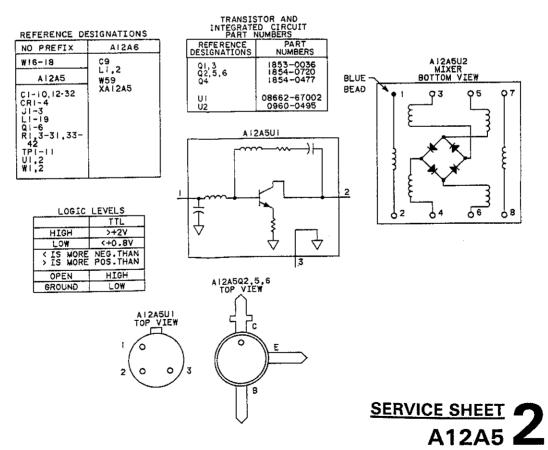

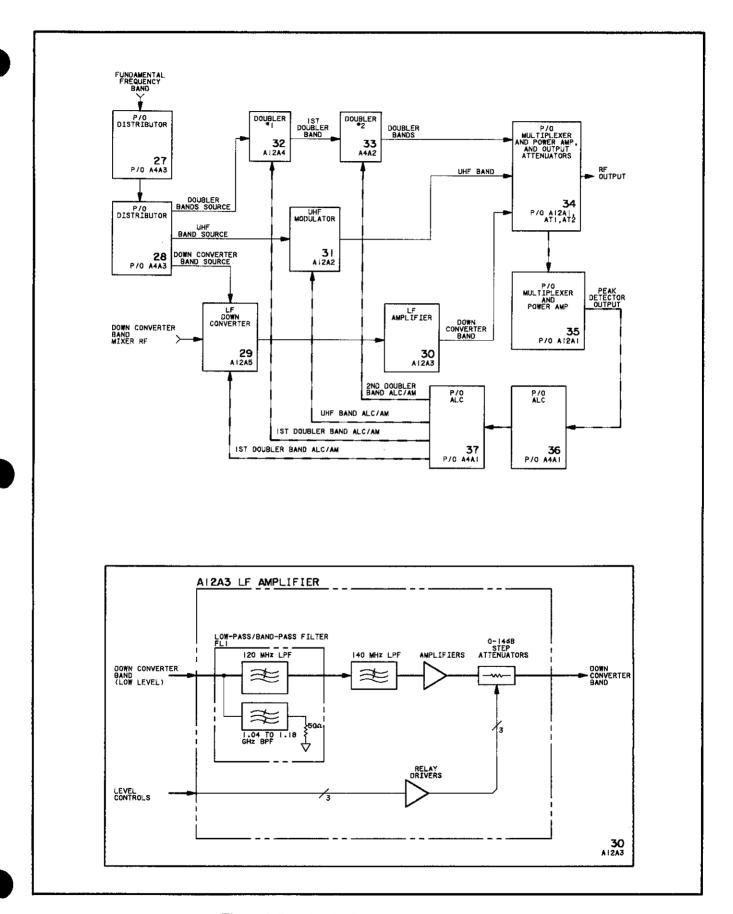

| SS29                                    | BD6              | A12A5               | Low Frequency Down Converter                                           | 8–509                                         | 6-223                           |

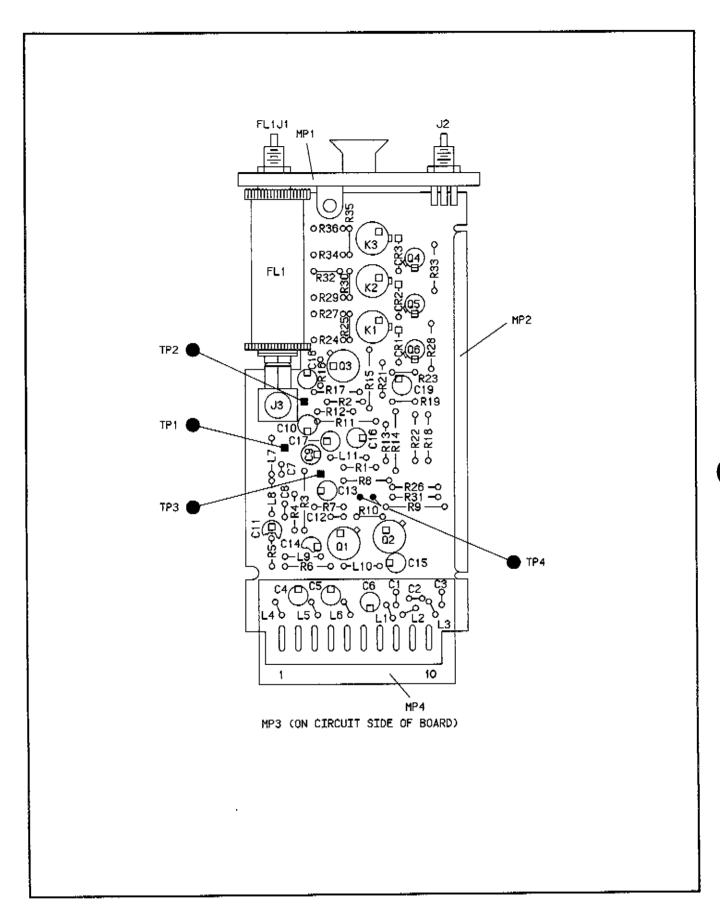

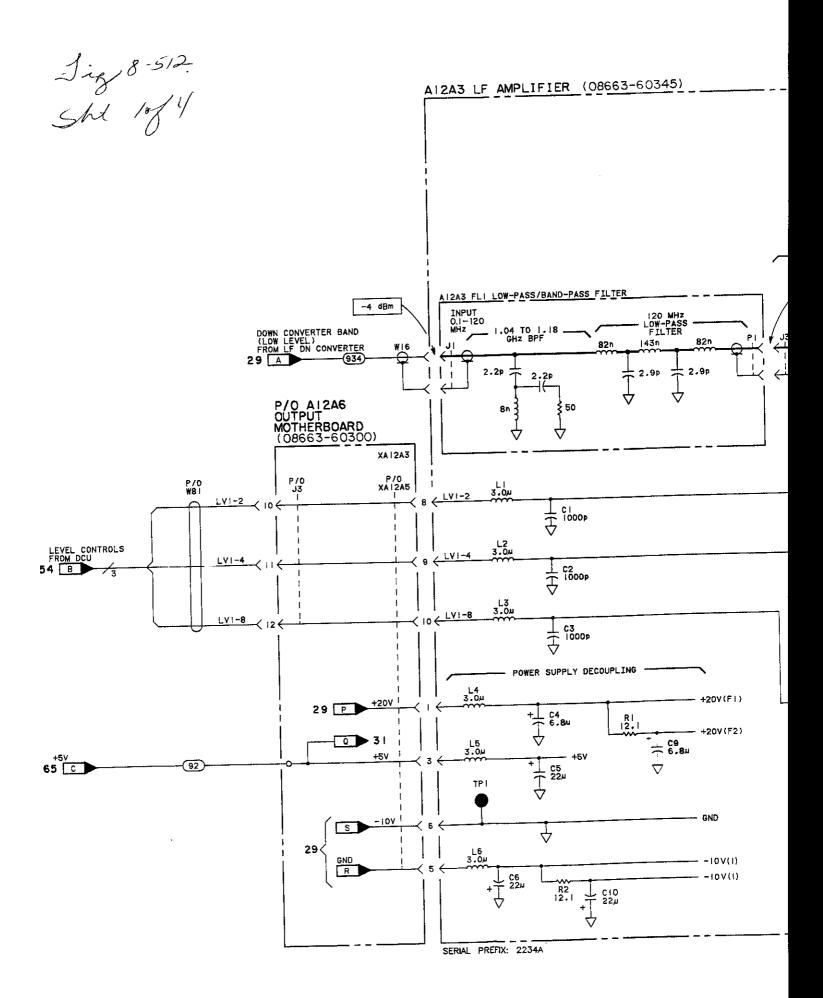

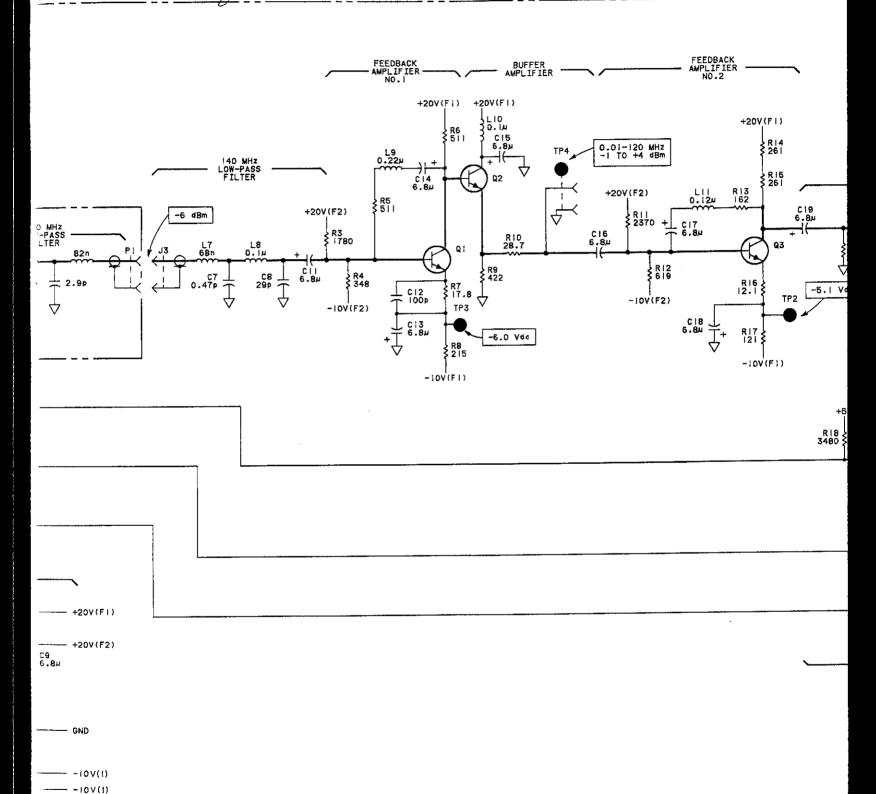

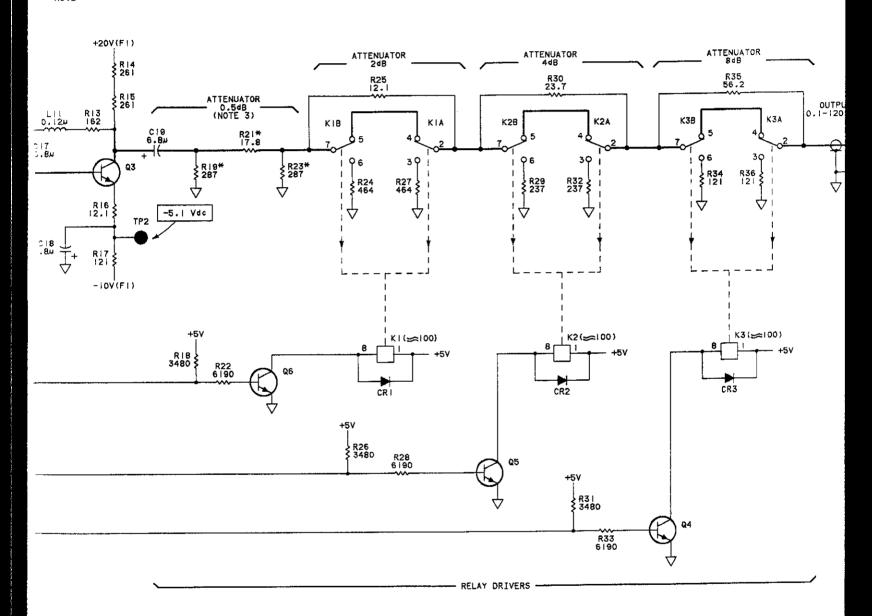

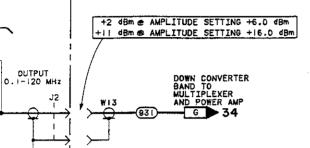

| SS30                                    | BD6              | A12A3               | Low Frequency Amplifier                                                | 8515                                          | 6-215                           |

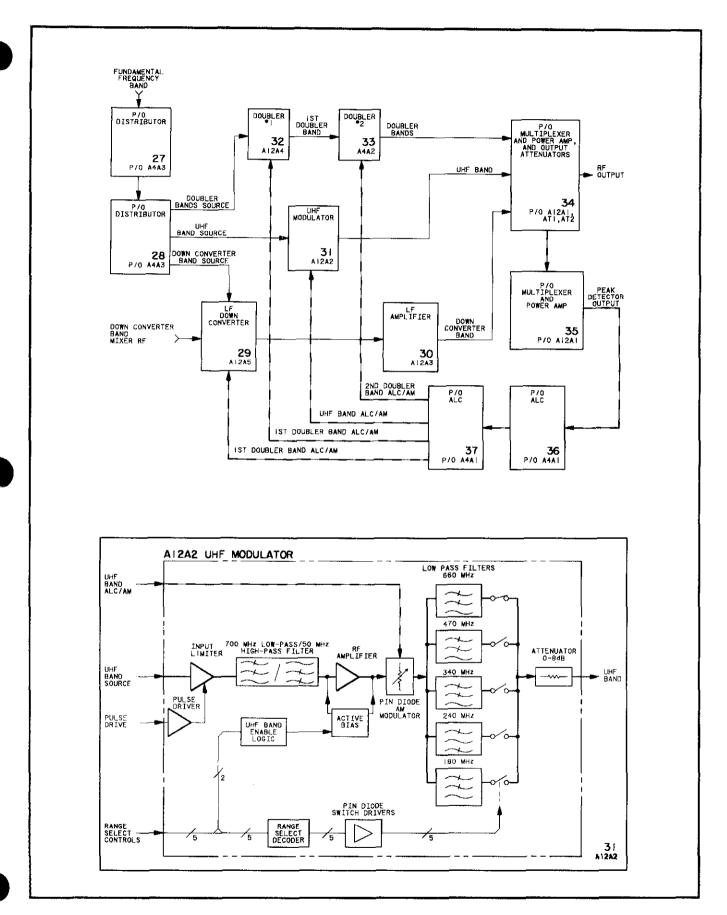

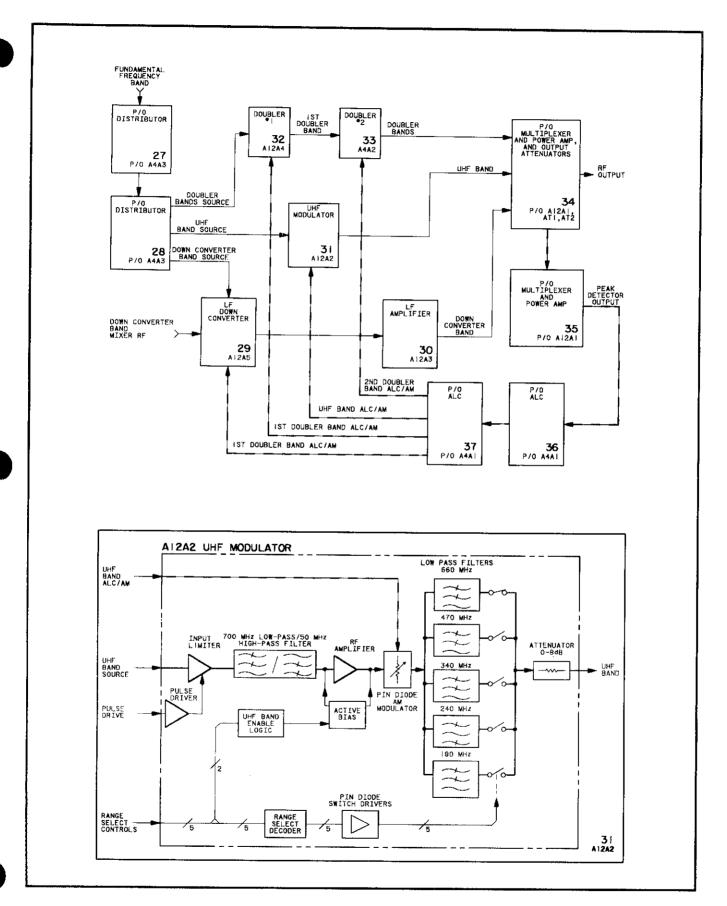

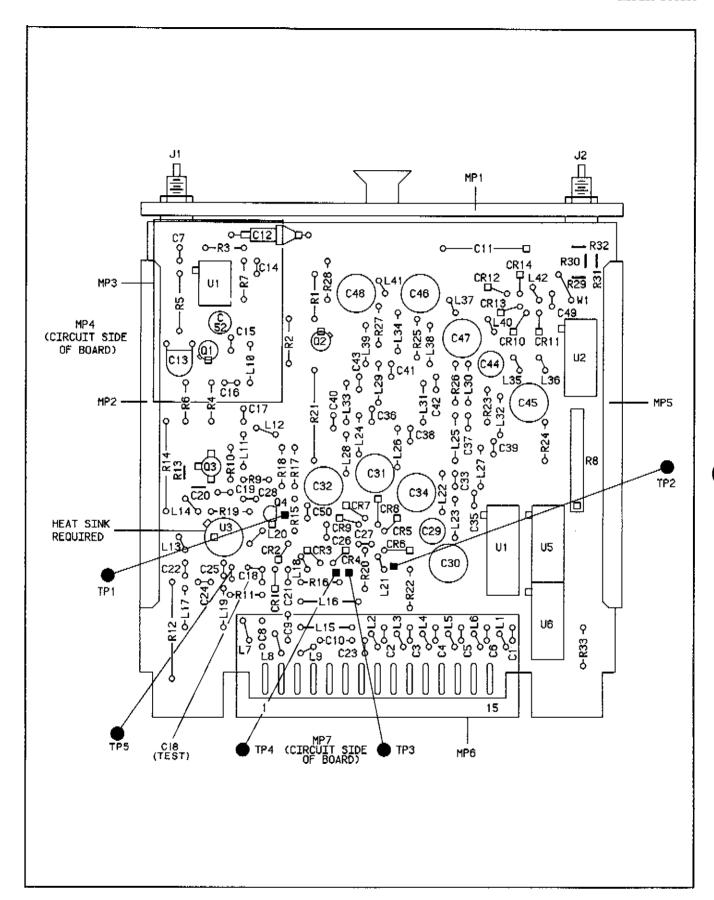

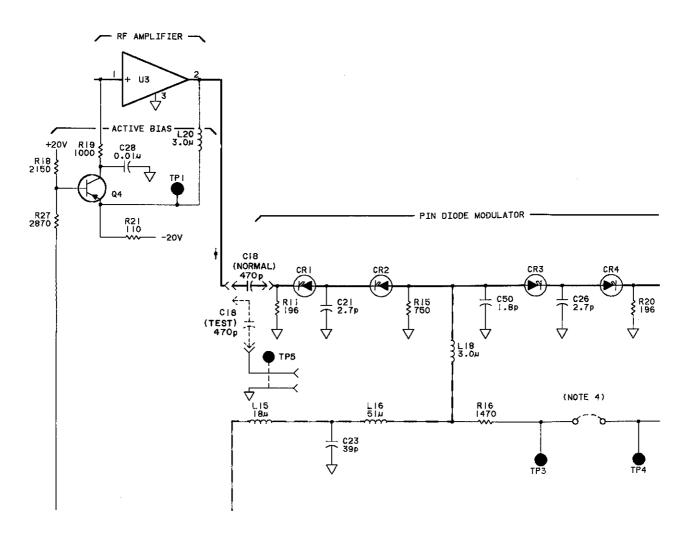

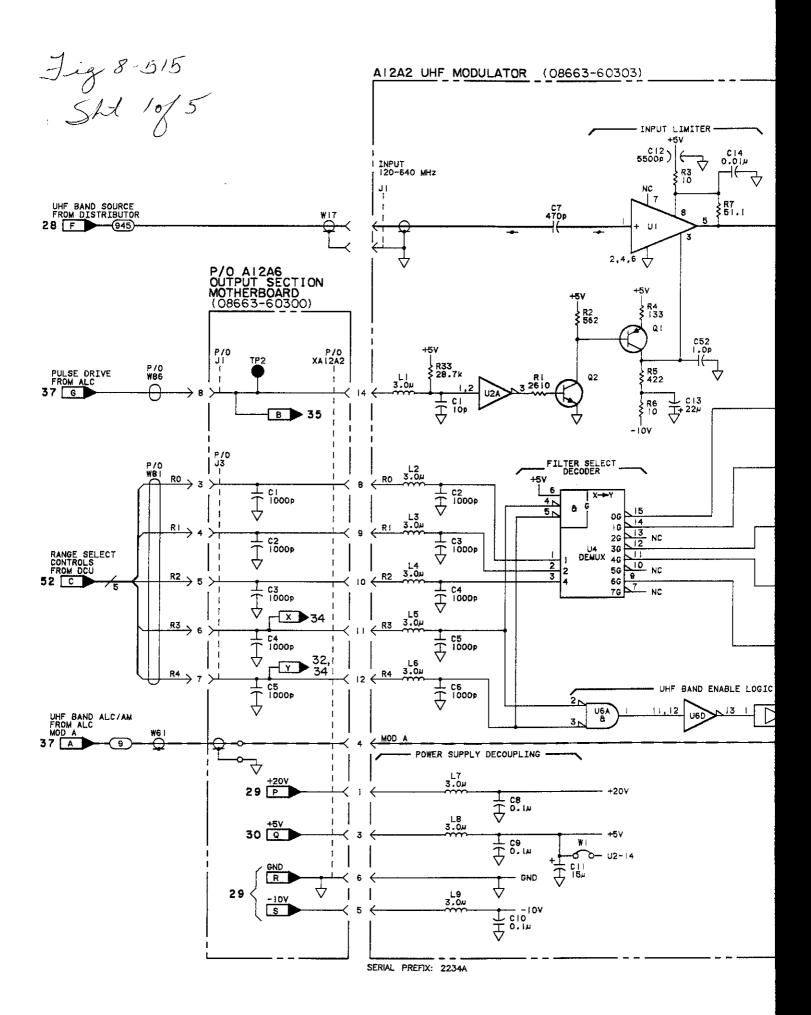

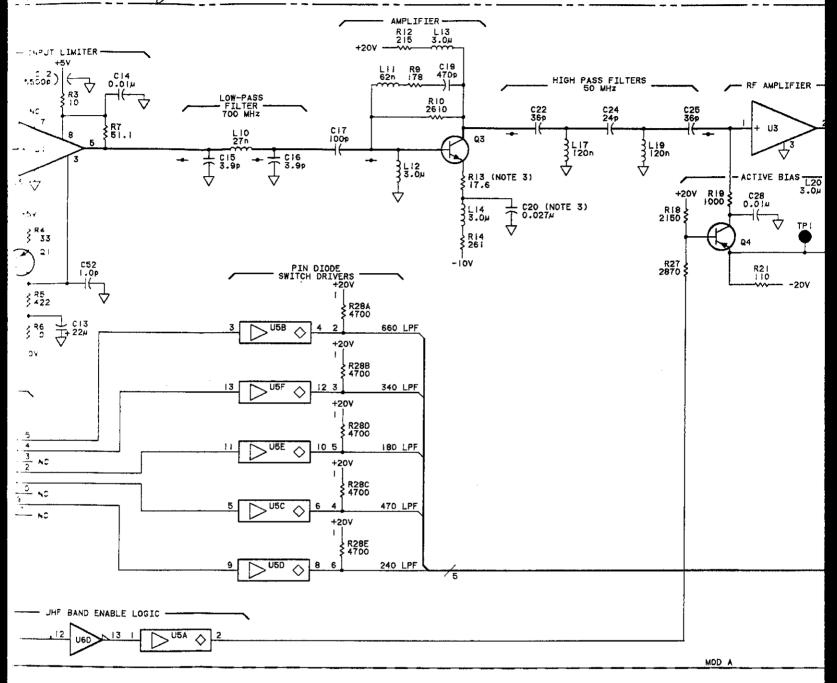

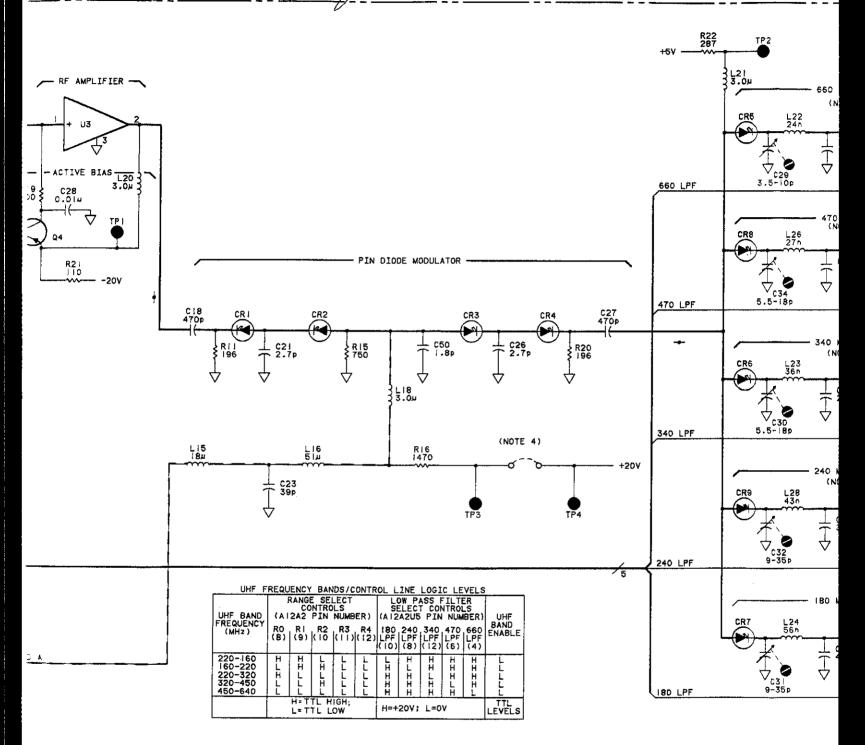

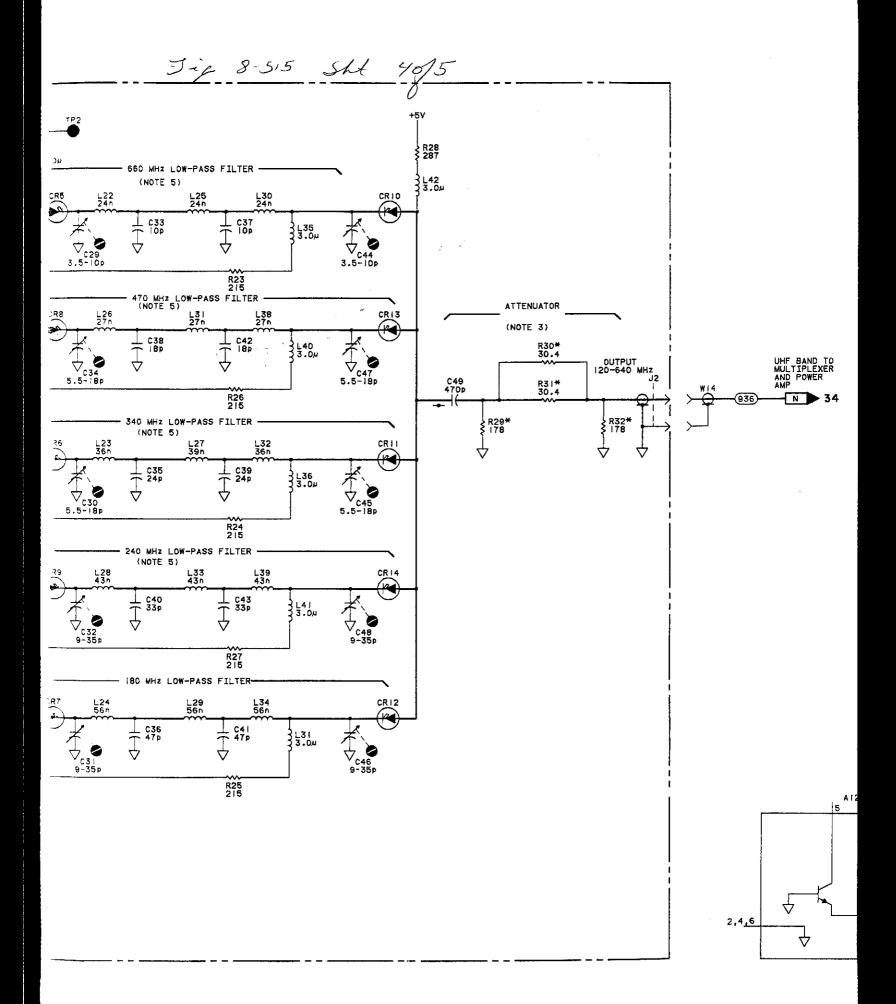

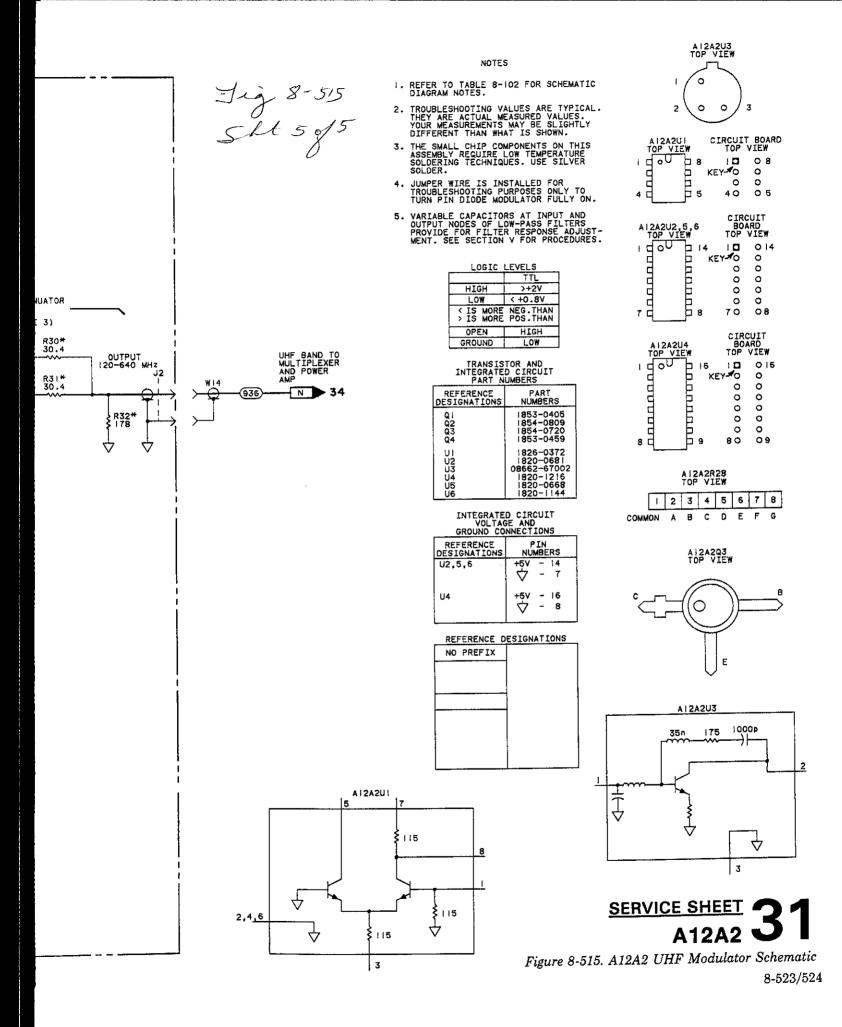

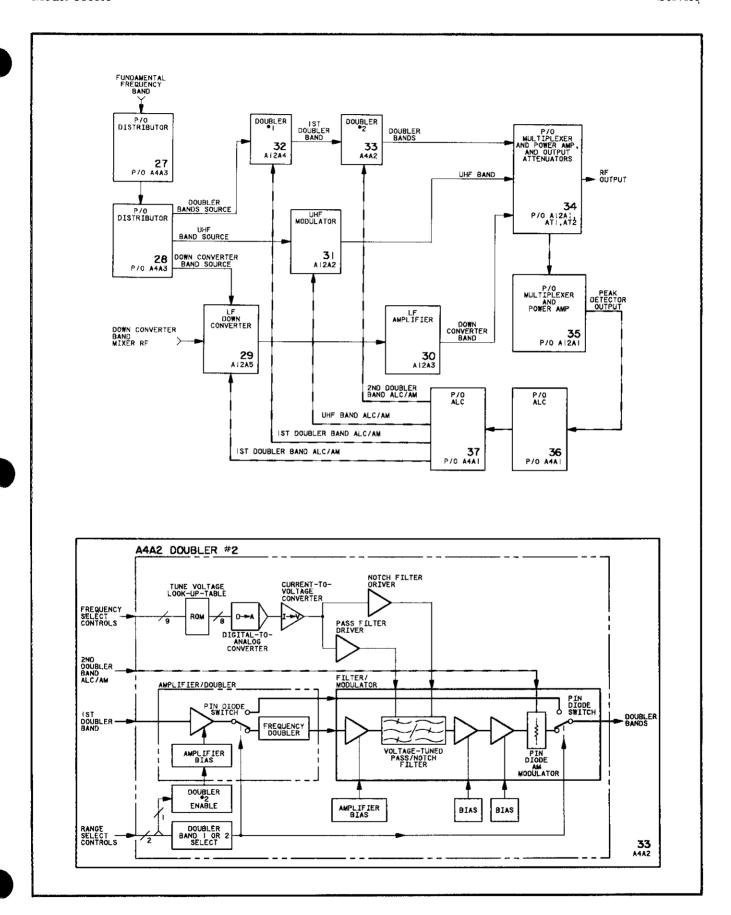

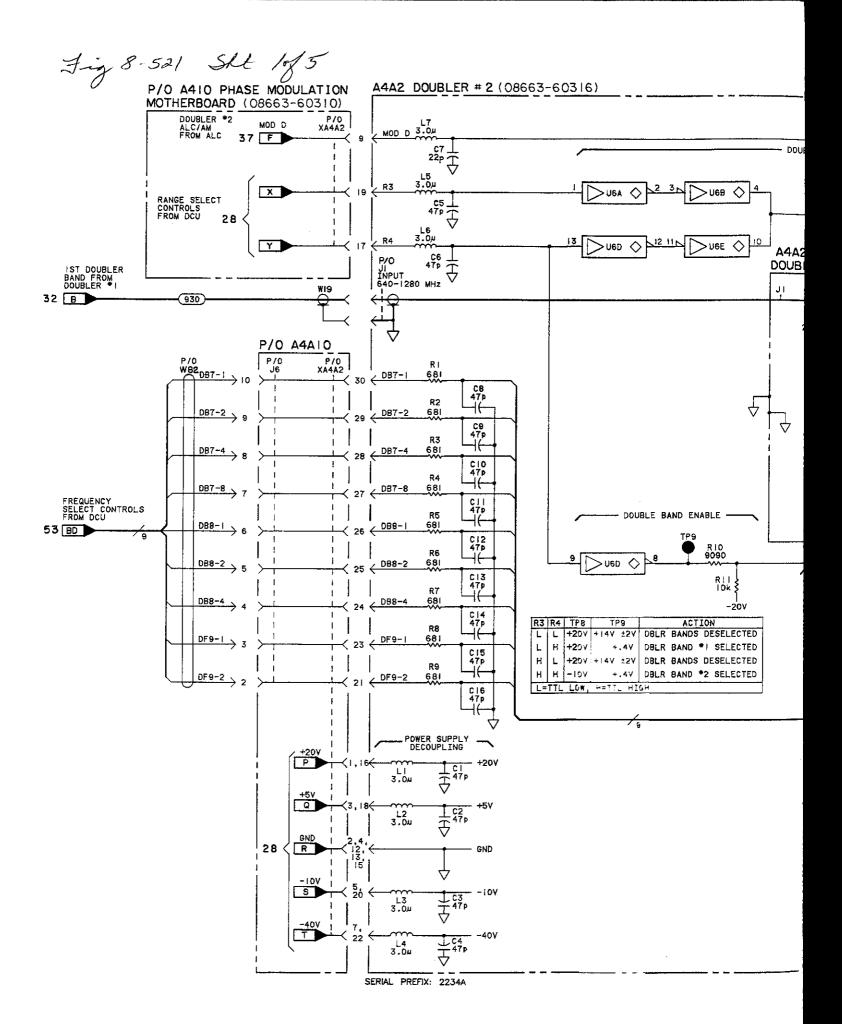

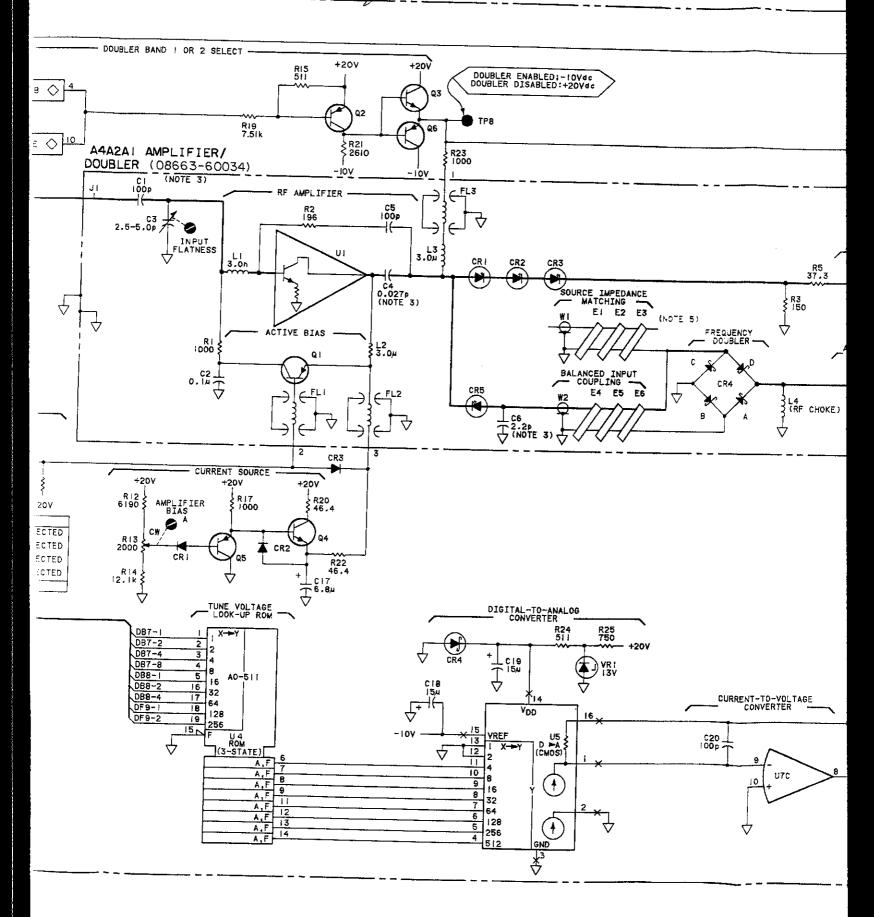

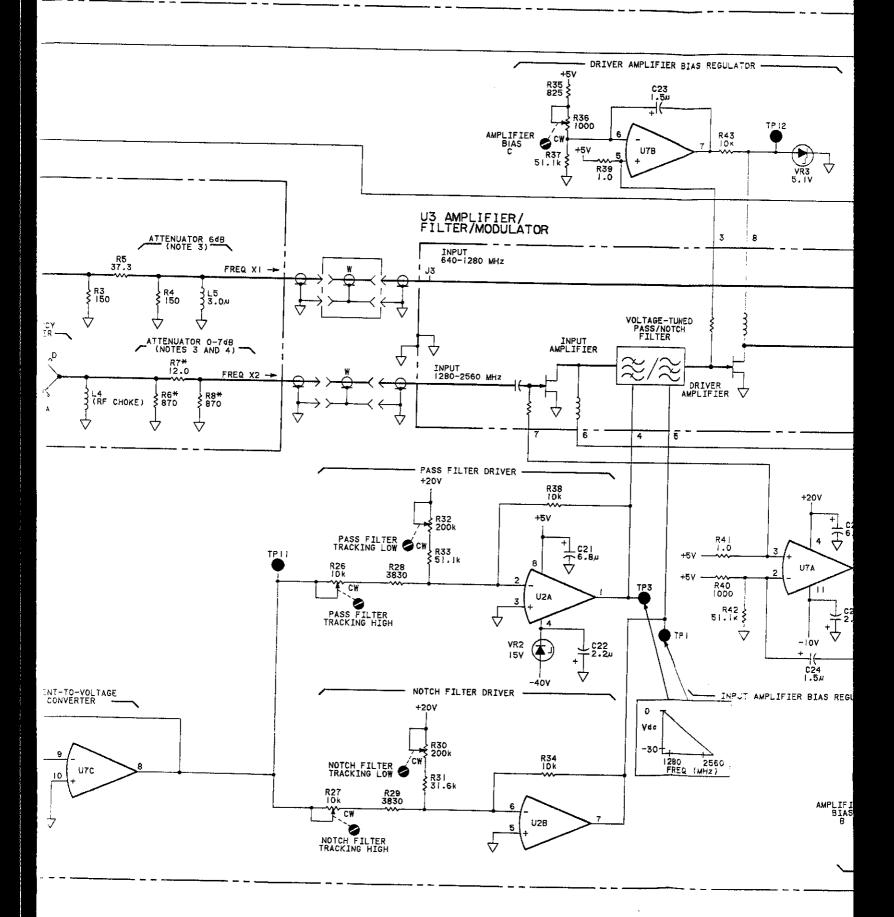

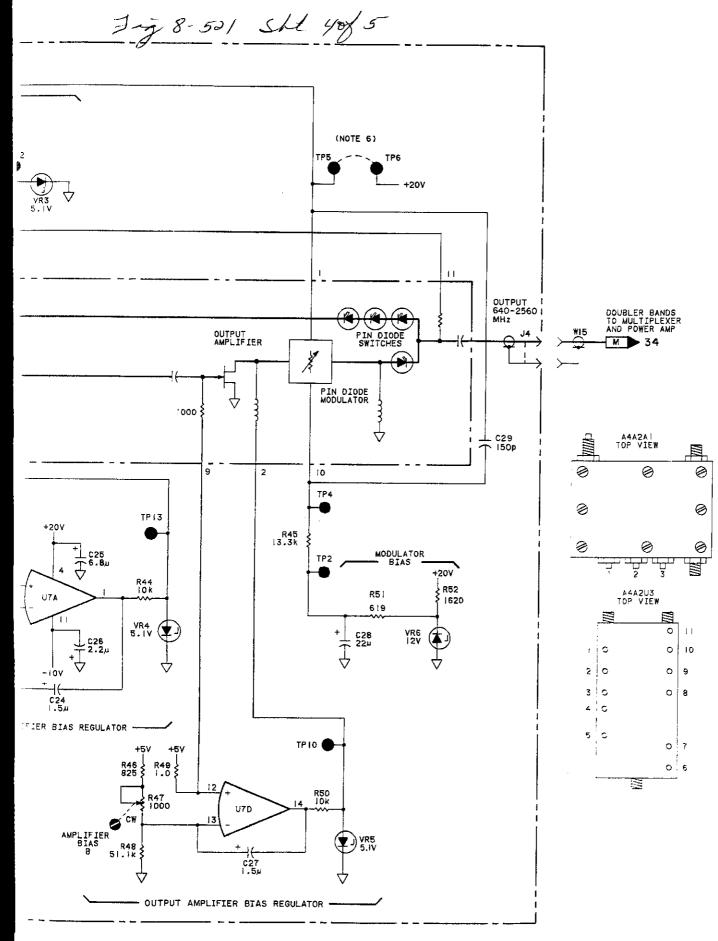

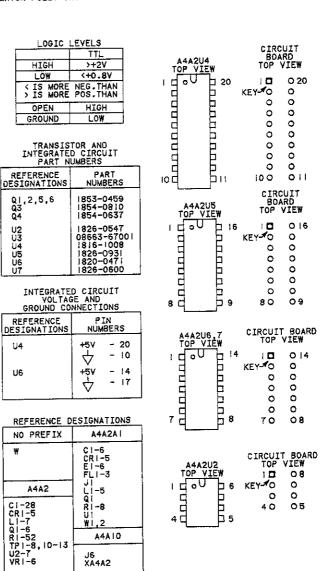

| SS31                                    | 8D6              | A12A2               | UHF Modulator                                                          | 8-521                                         | 6-211                           |

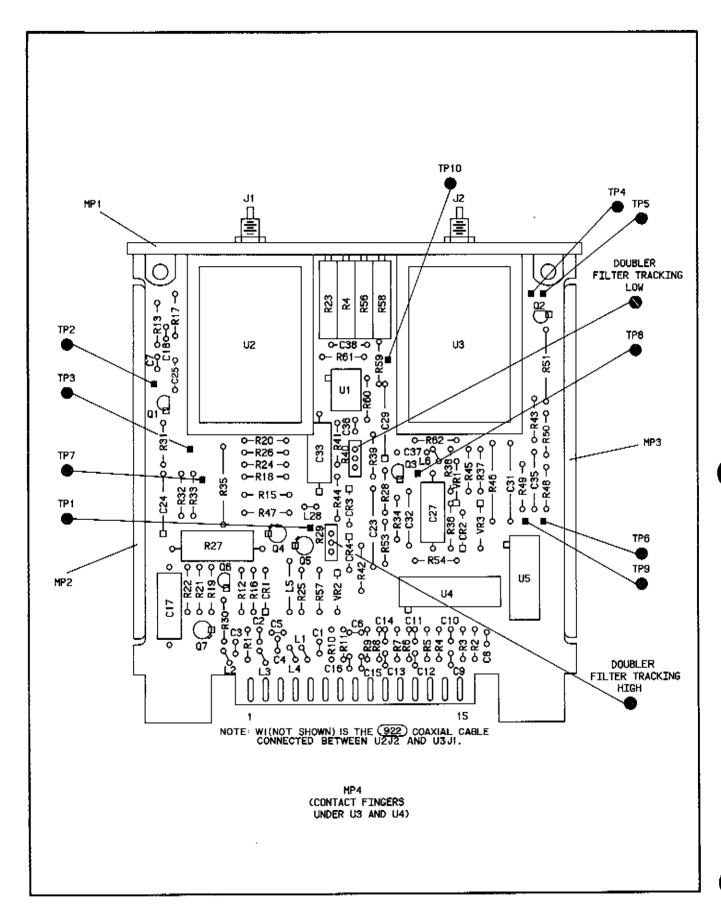

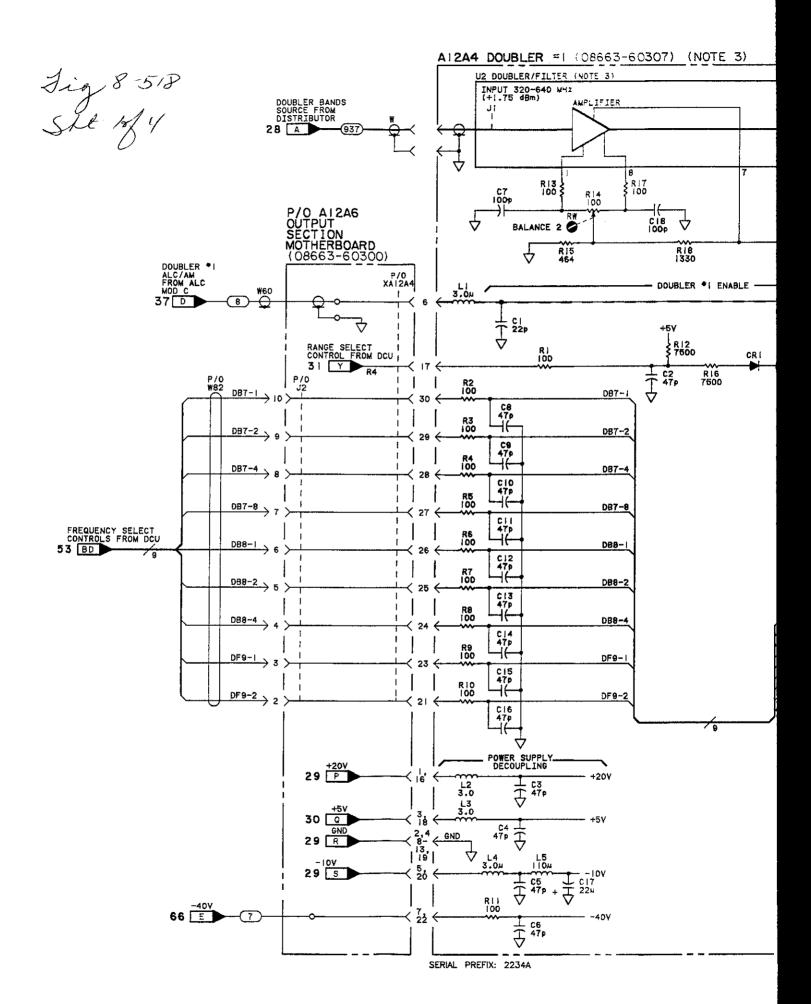

| SS32                                    | BD6              | A12A4               | Doubler #1                                                             | 8-525                                         | 6-219                           |

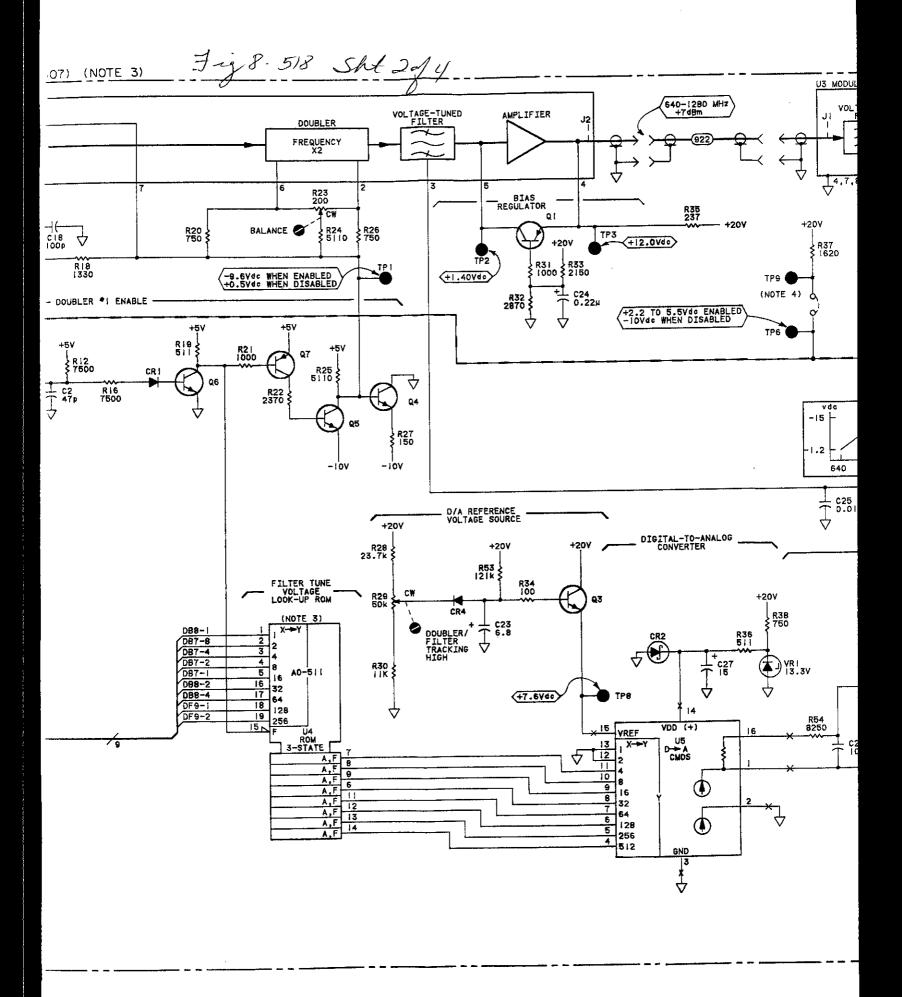

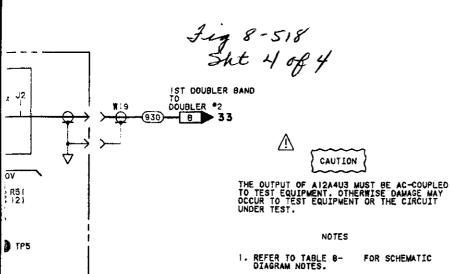

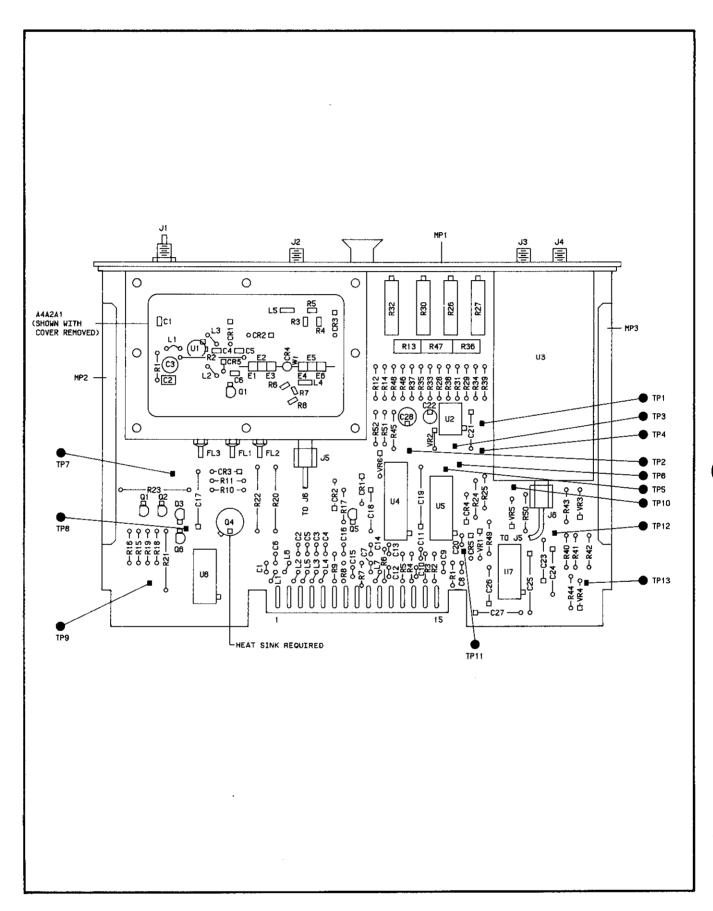

| SS33                                    | BD6              | A4A2                | Doubler #2                                                             | 8-533                                         | 6–75                            |

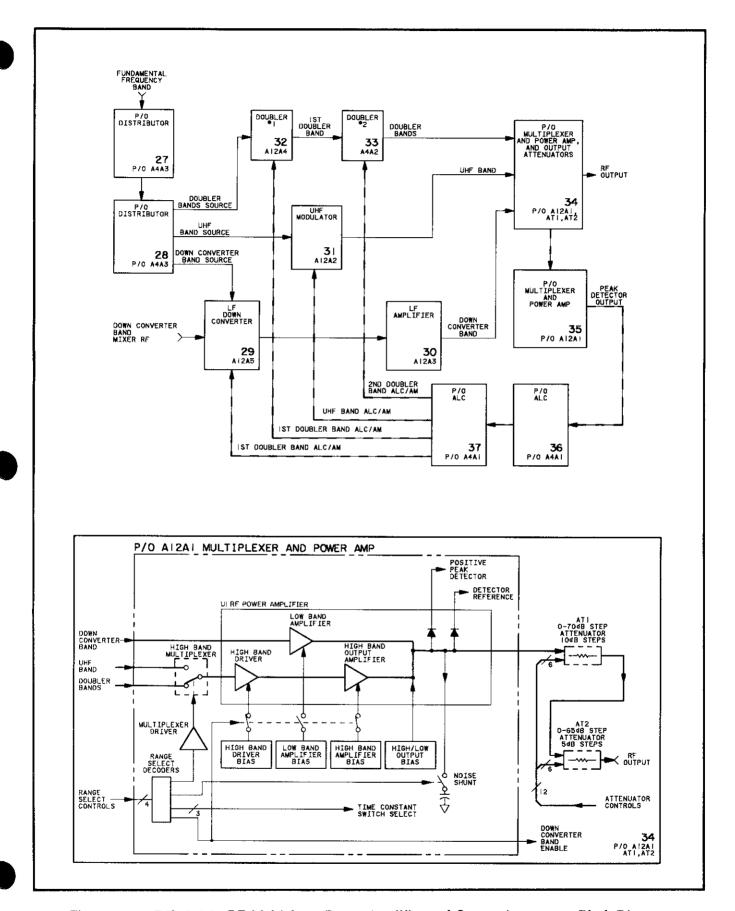

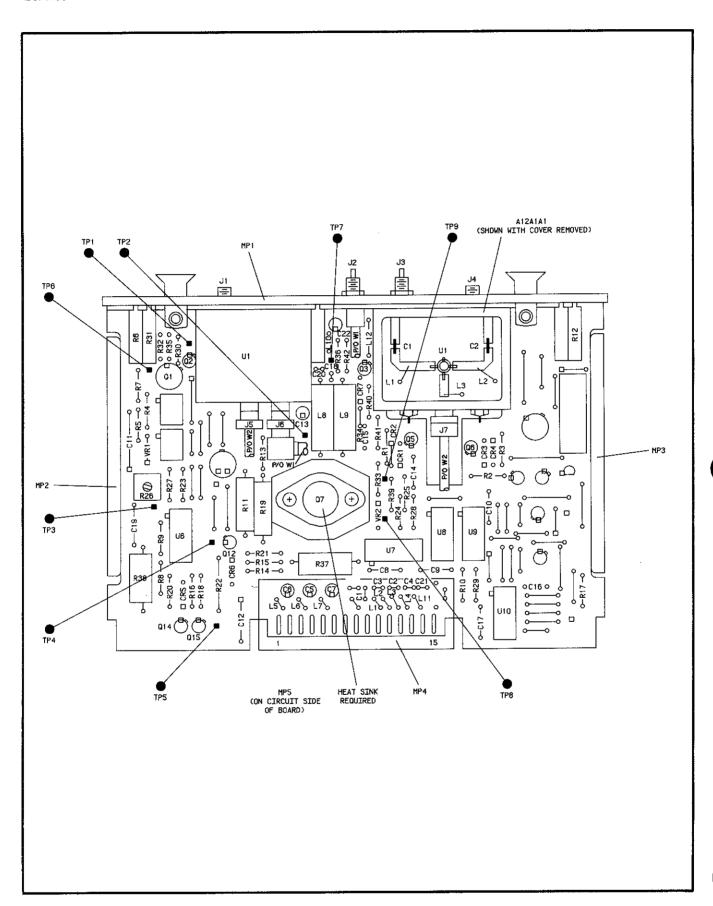

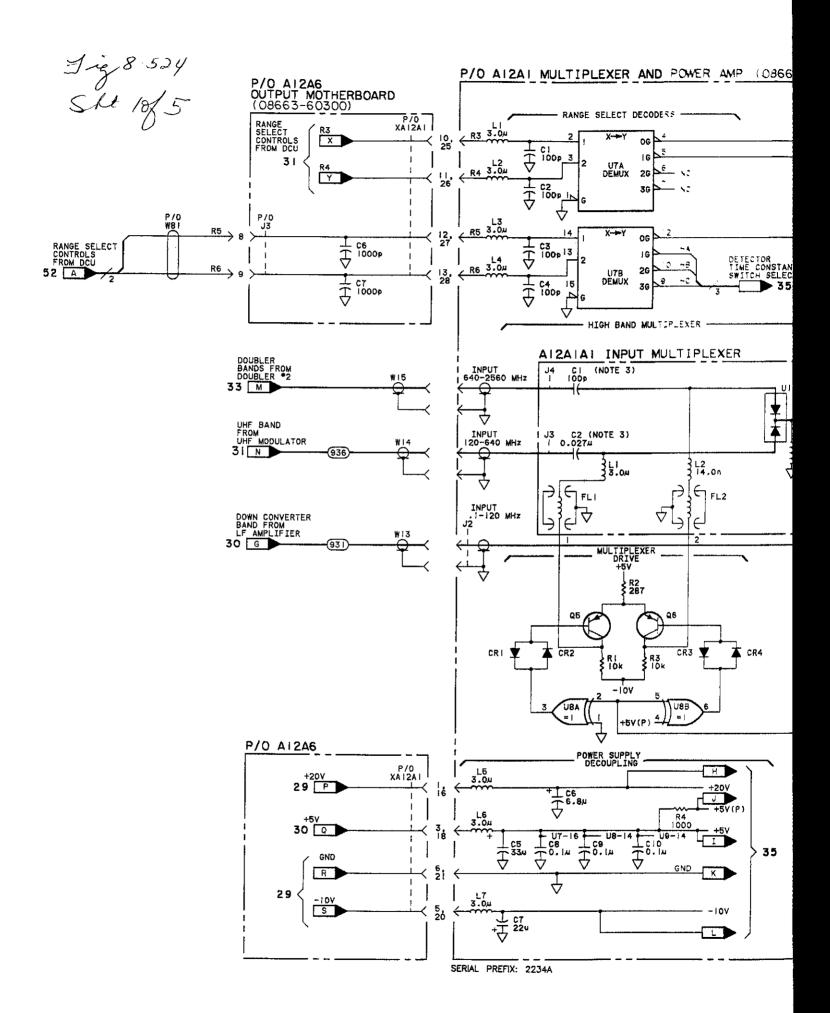

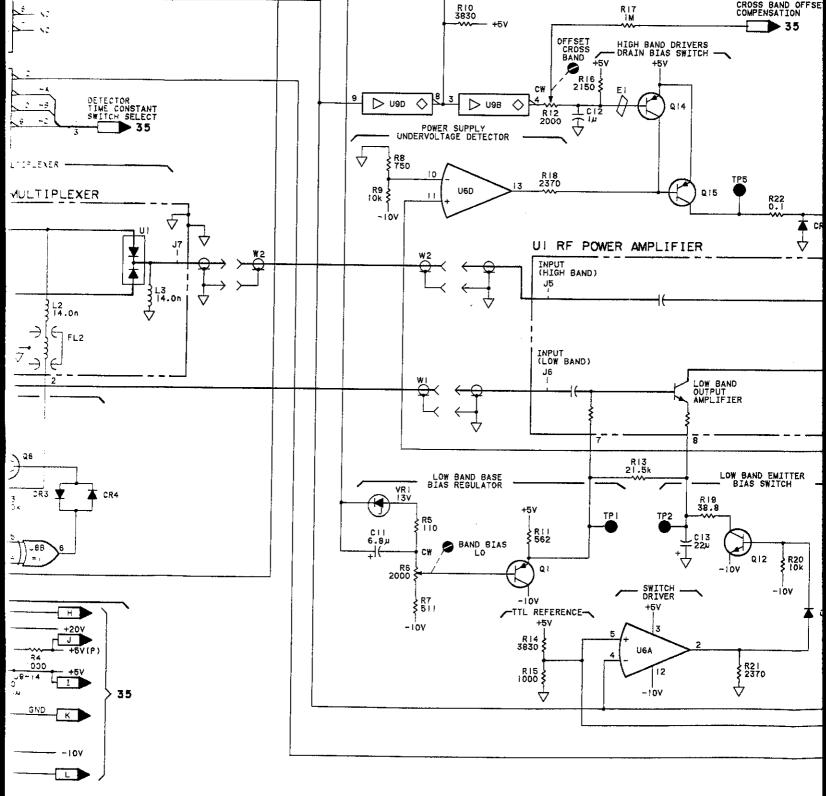

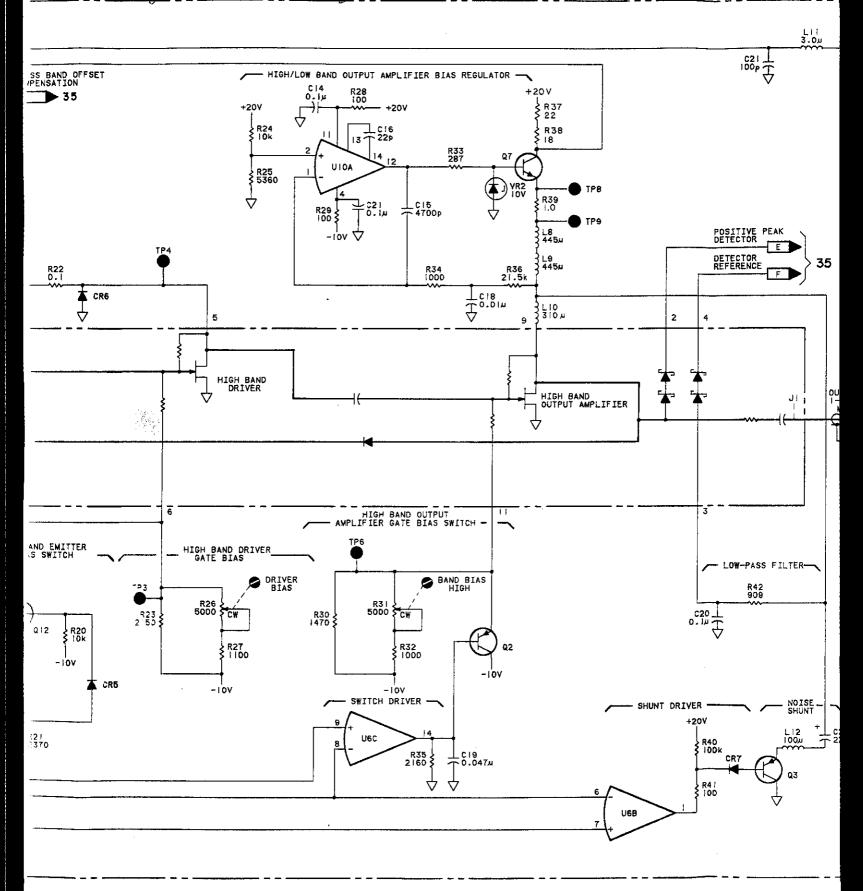

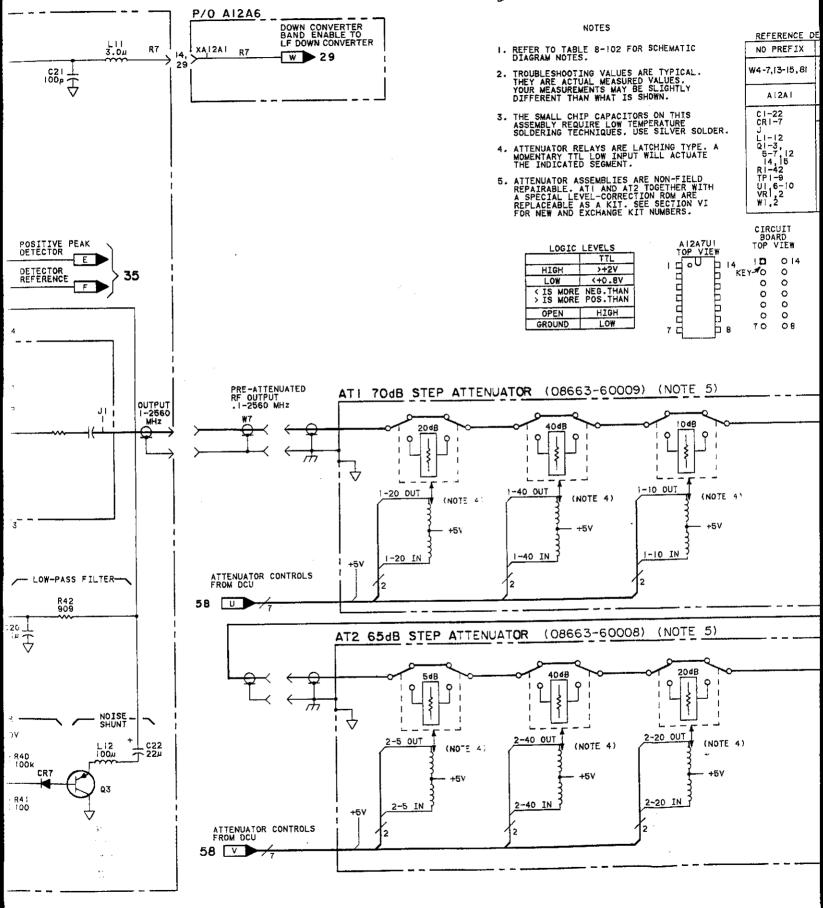

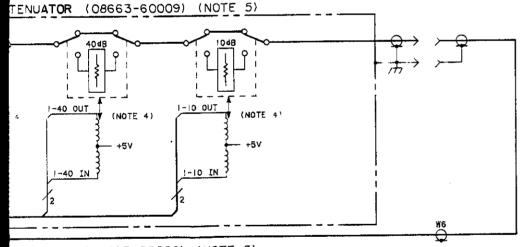

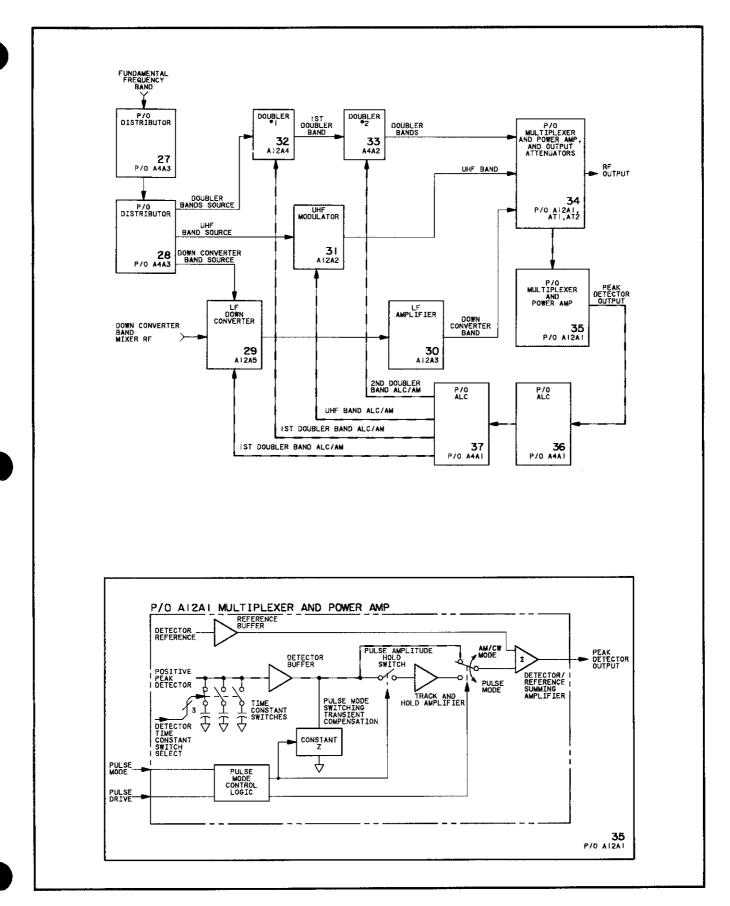

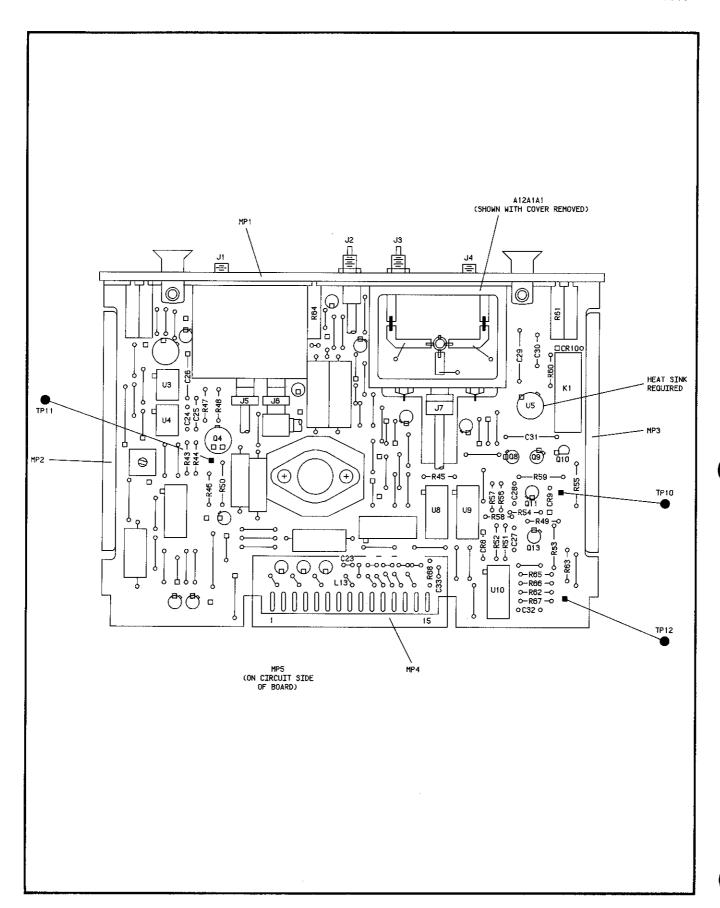

| SS34                                    | BD6              | A12A1<br>AT1<br>AT2 | RF Multiplexer and Power Amplifier Output Attenuator Output Attenuator | 8–537                                         | 6–205                           |

| SS35                                    | BD6              | A12A1               | RF Multiplexer and Power Amplifier                                     | 8-541                                         | 6–205                           |

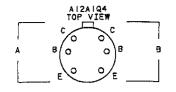

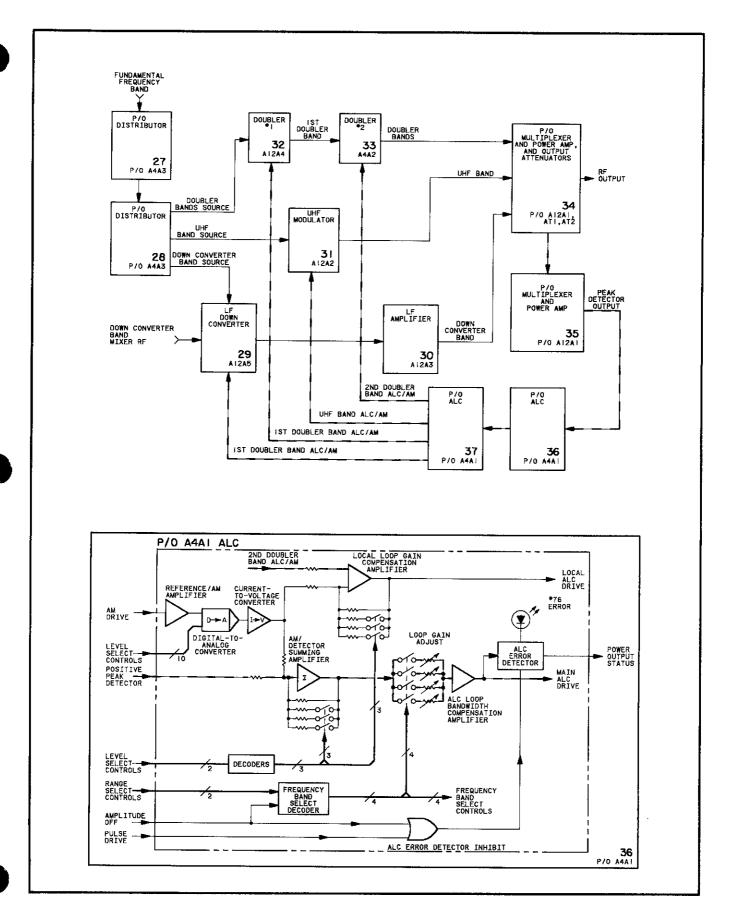

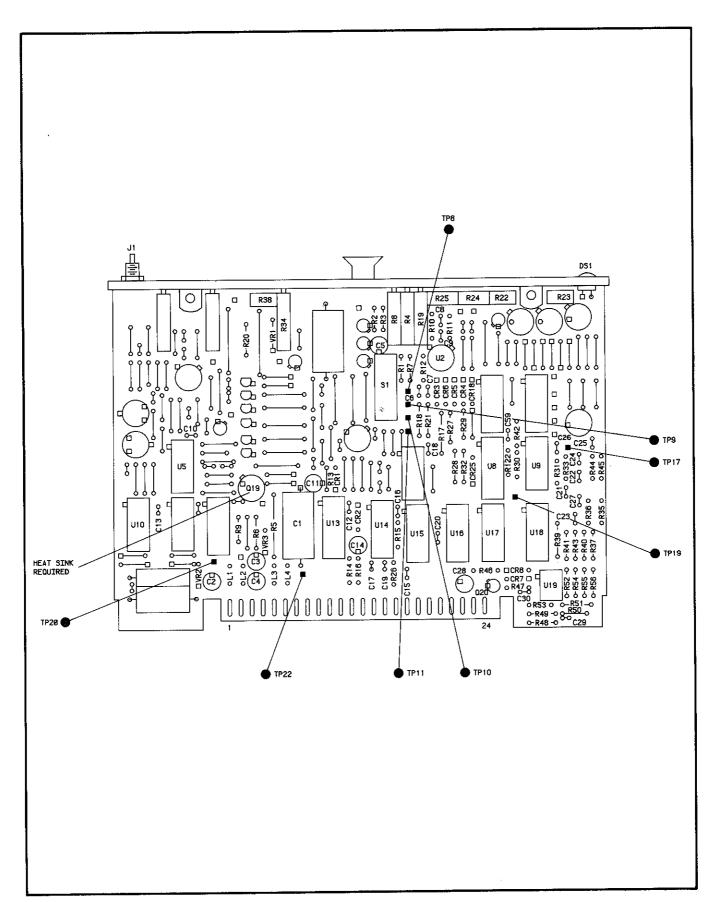

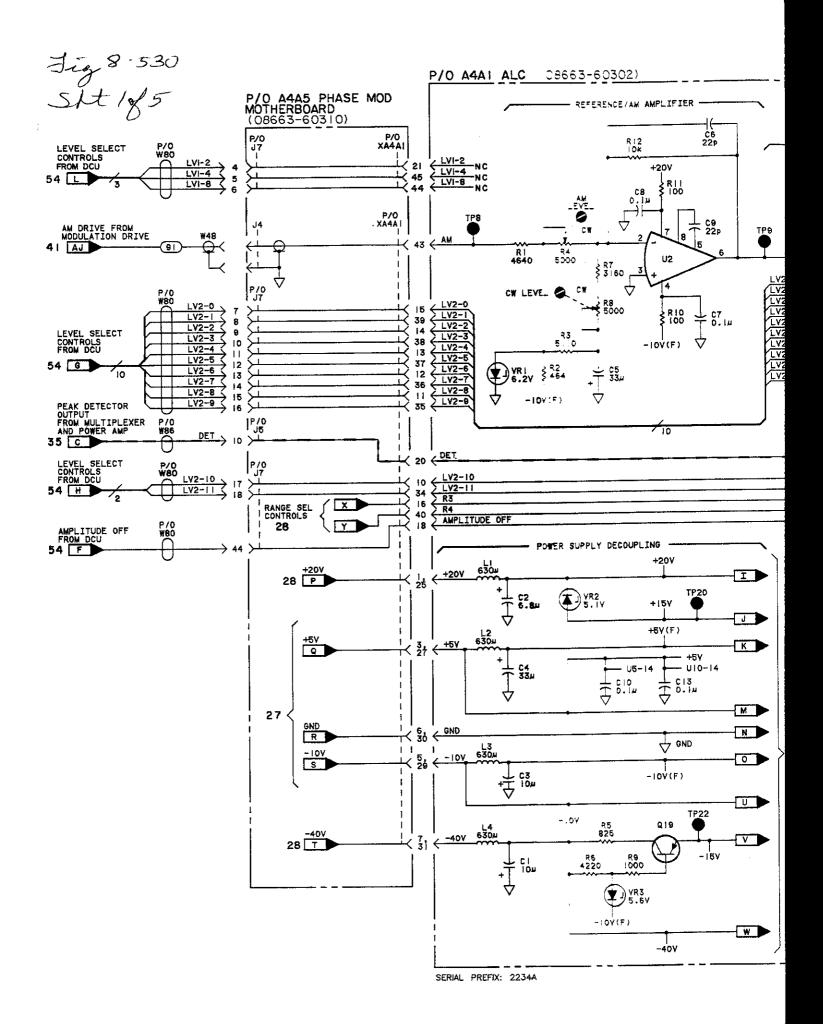

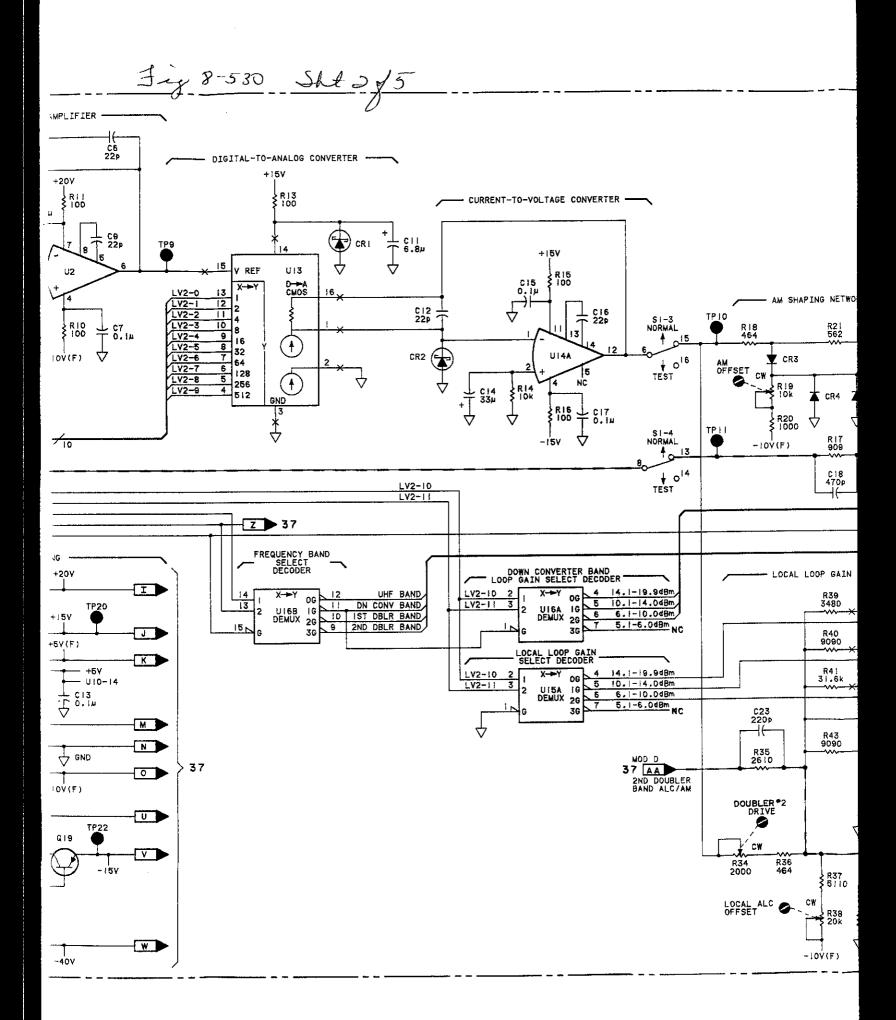

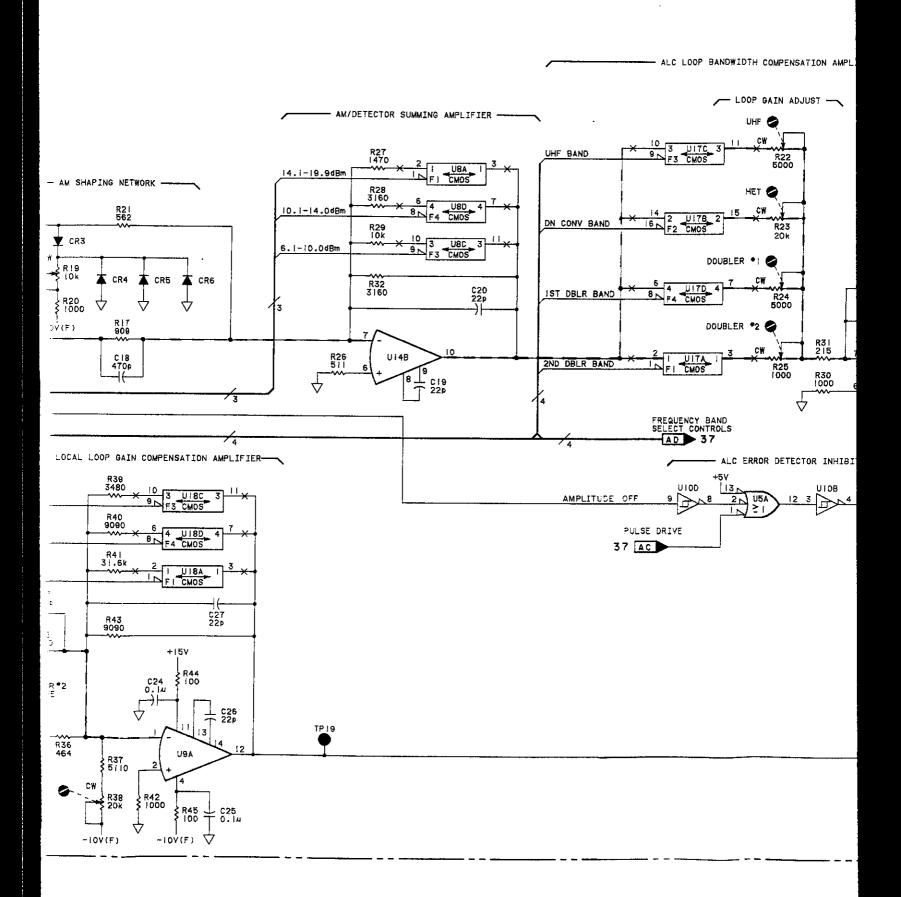

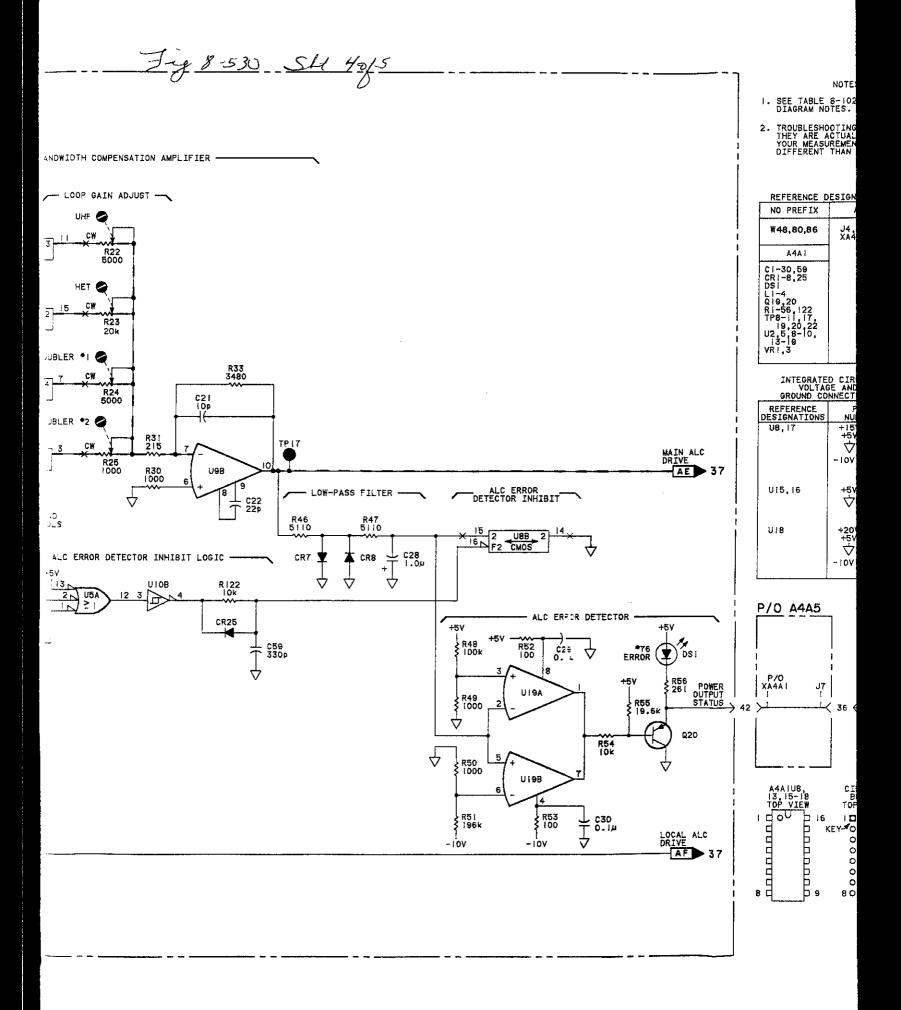

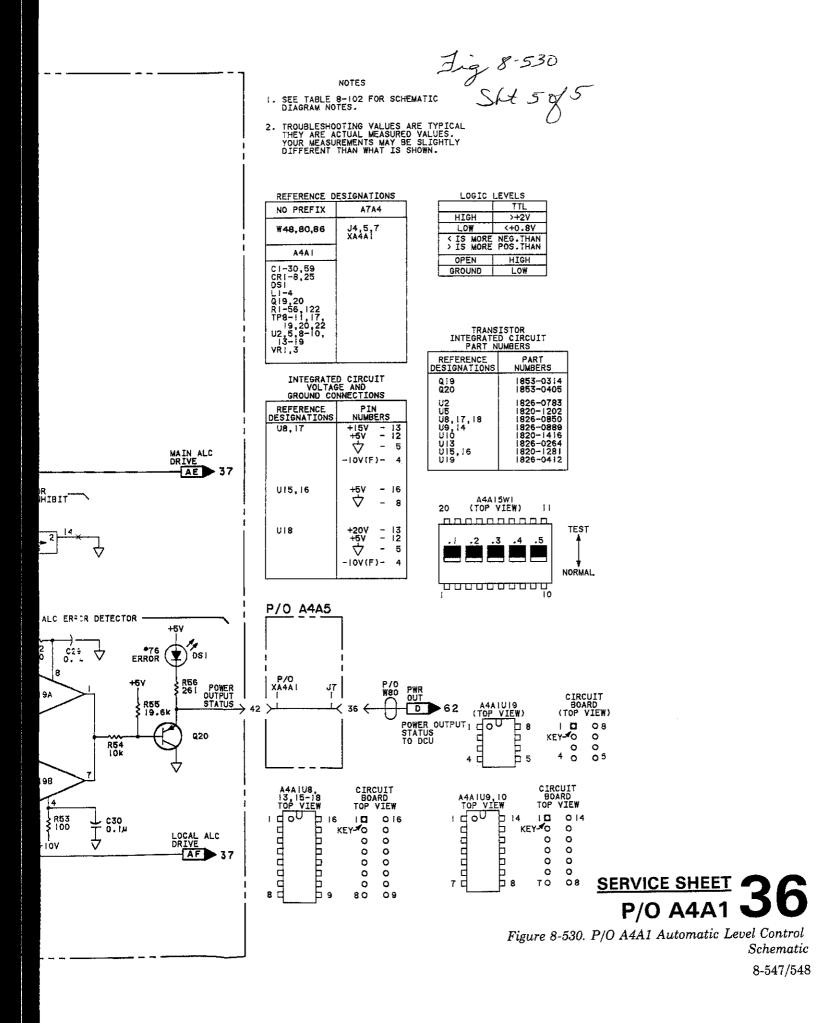

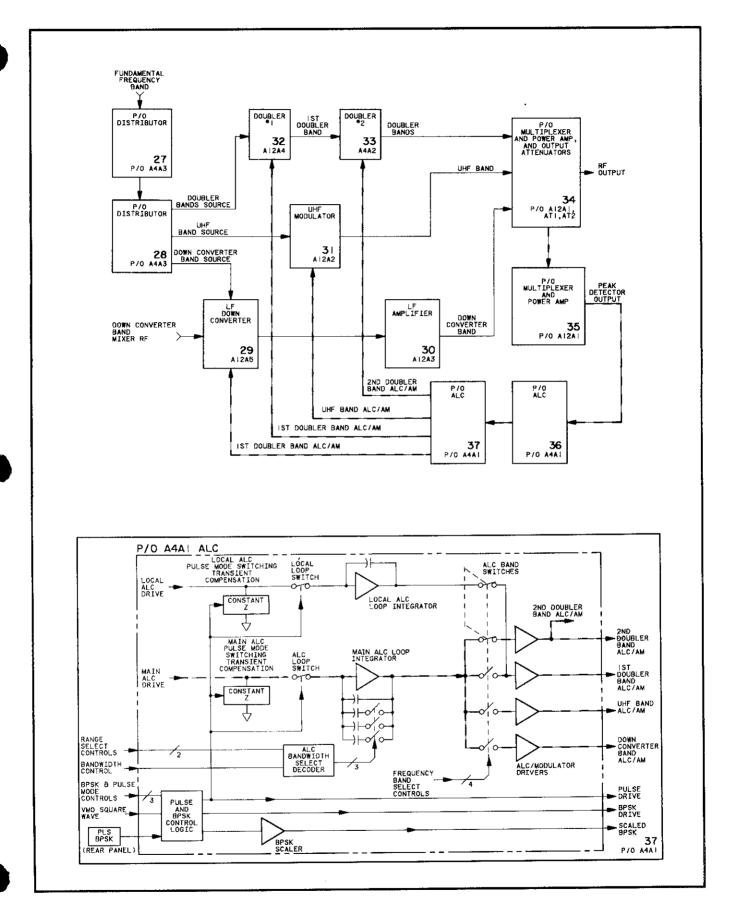

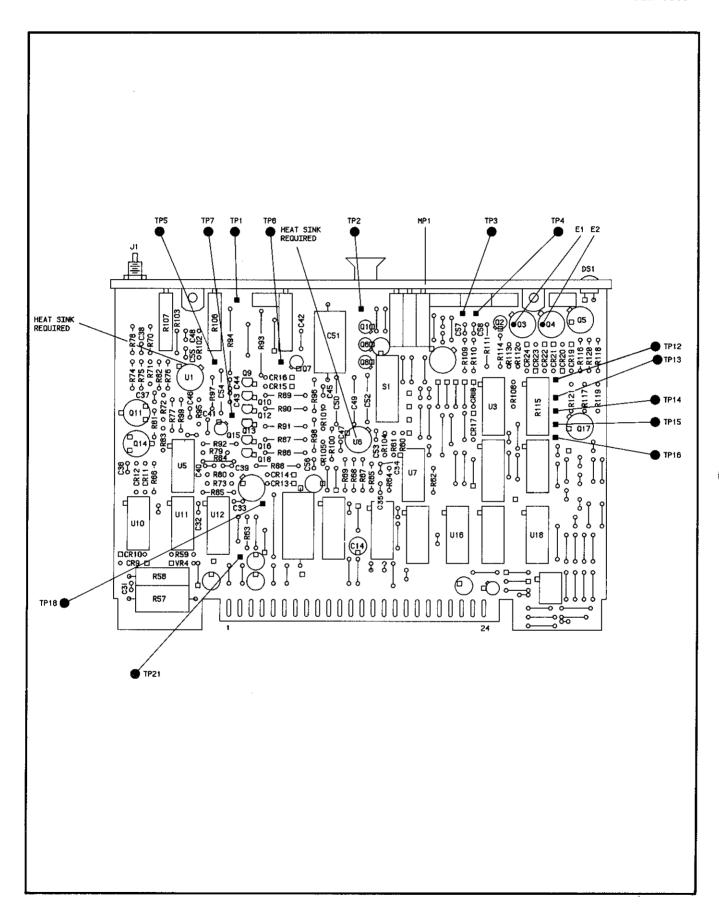

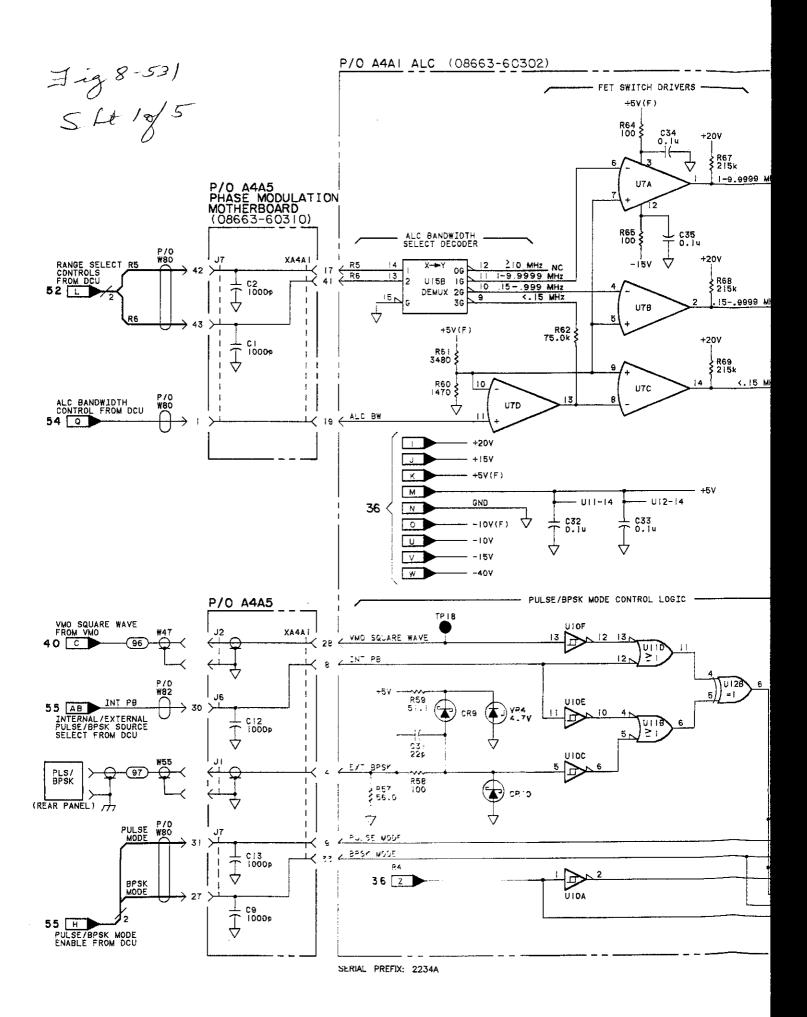

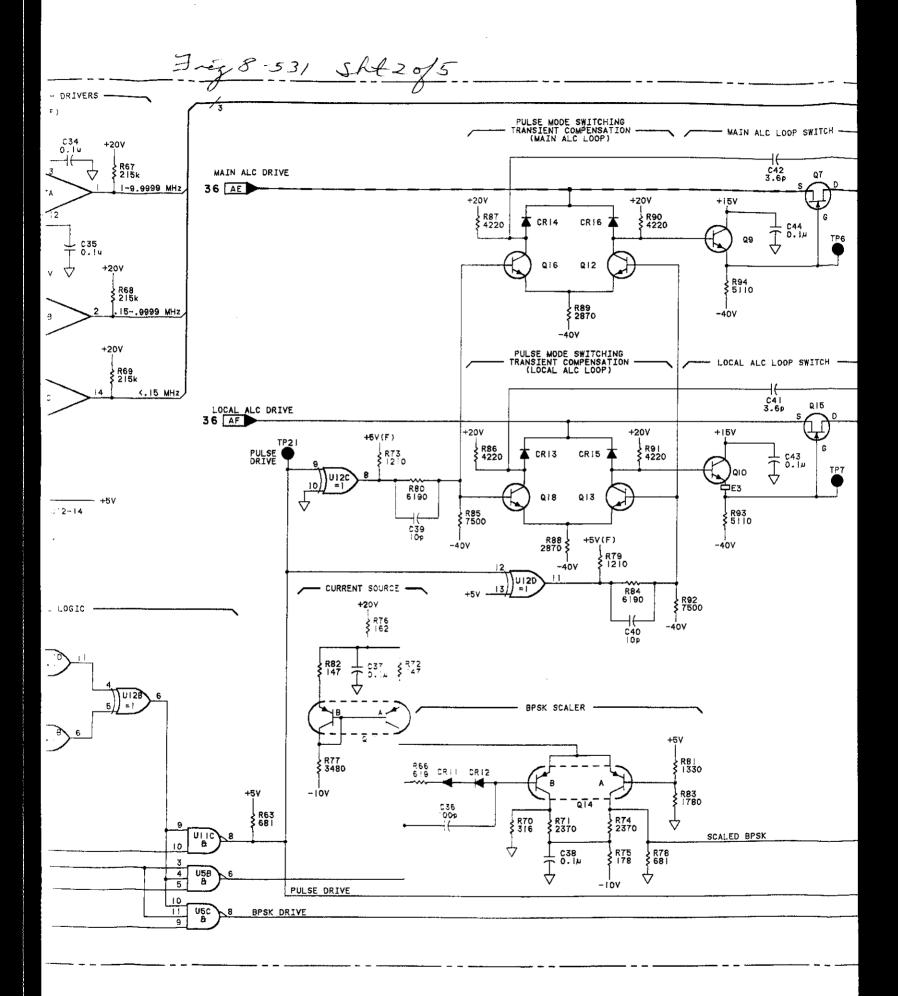

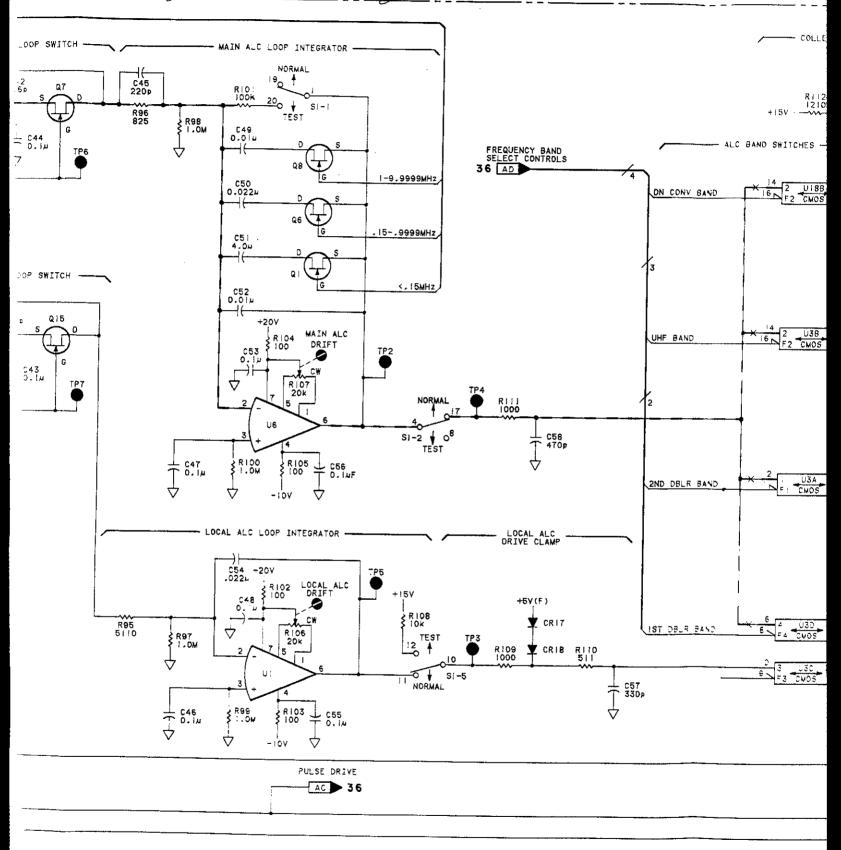

| SS36                                    | BD6              | A4A1                | Automatic Level Control (ALC)                                          | 8-545                                         | 6–69                            |

| SS37                                    | BD6              | A4A1                | Automatic Level Control (ALC)                                          | 8–549                                         | 669                             |

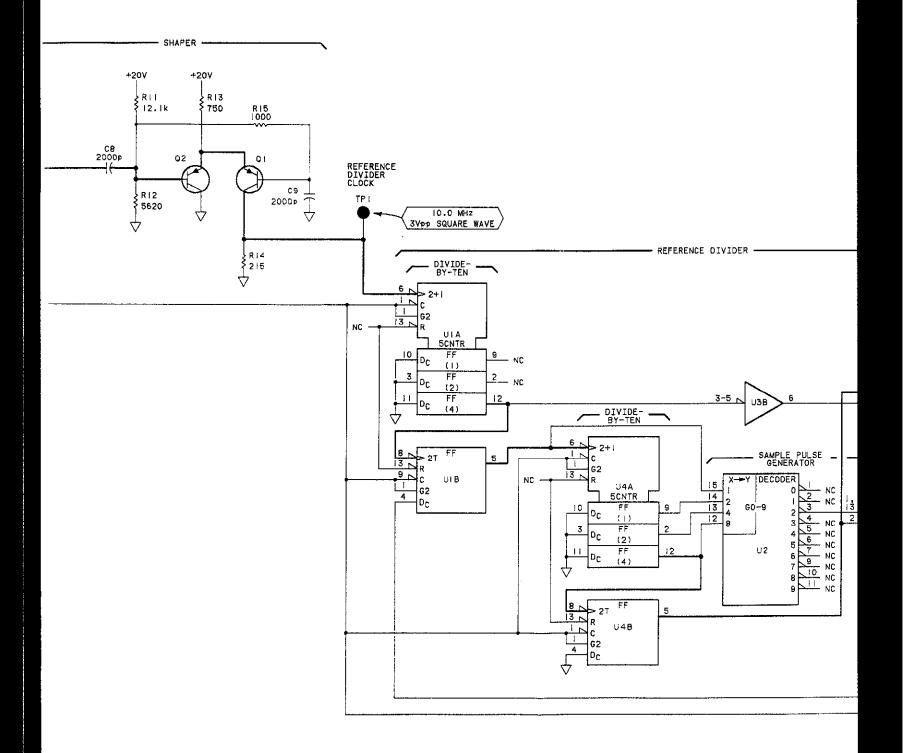

SERVICE SHEET 13 A5A4 FRACTIONAL-N LOOP

### PRINCIPLES OF OPERATION

### General

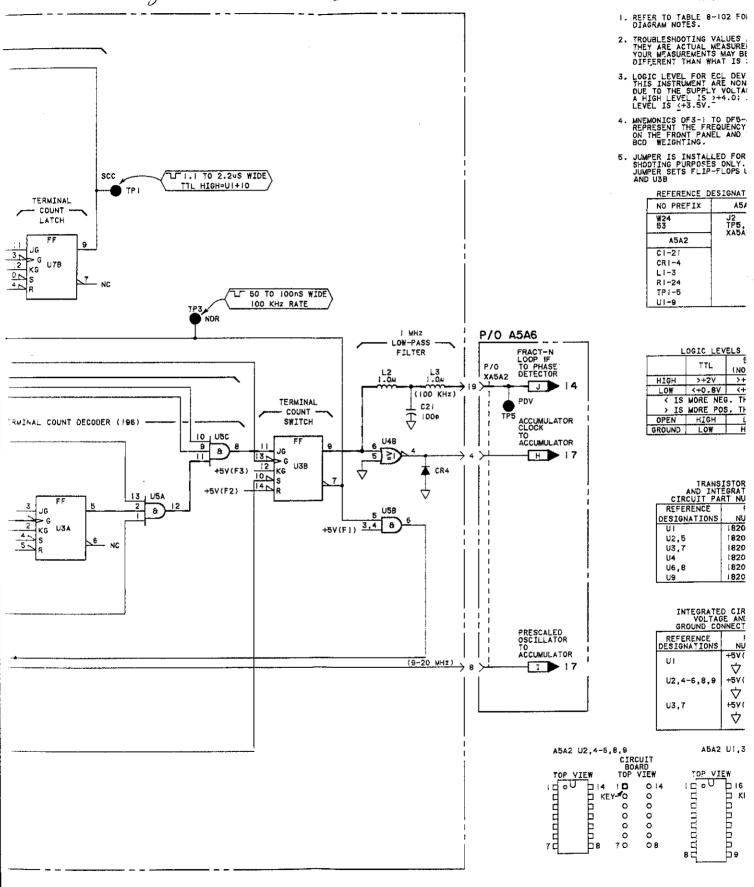

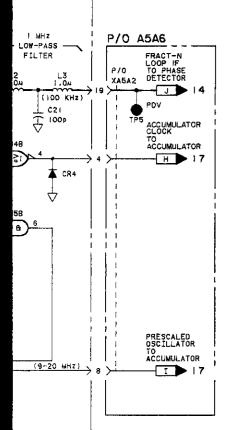

The Reference Divider divides the 10 MHz reference signal down to 100 kHz which is used as the reference signal to the phase detector. This assembly also generates the sample pulse signal that clocks the sample-hold circuit at the proper time.

## Shaper

The shaper network consists of a diode clamping network and a differential amplifier. It provides the analog-to-TTL conversion.

### Reference Divider

Ul and U4 form the divide-by-100 circuit which divides the 10 MHz input signal to produce the 100 kHz phase detector reference signal.

### Sample Pulse Generator

The function of the sample pulse generator is to produce a 500 ns pulse that is delayed by 1 microsecond from the leading edge of the phase detector reference signal. This is accomplished by detecting a state in the divide-by-100 circuit which corresponds to the desired delay time.

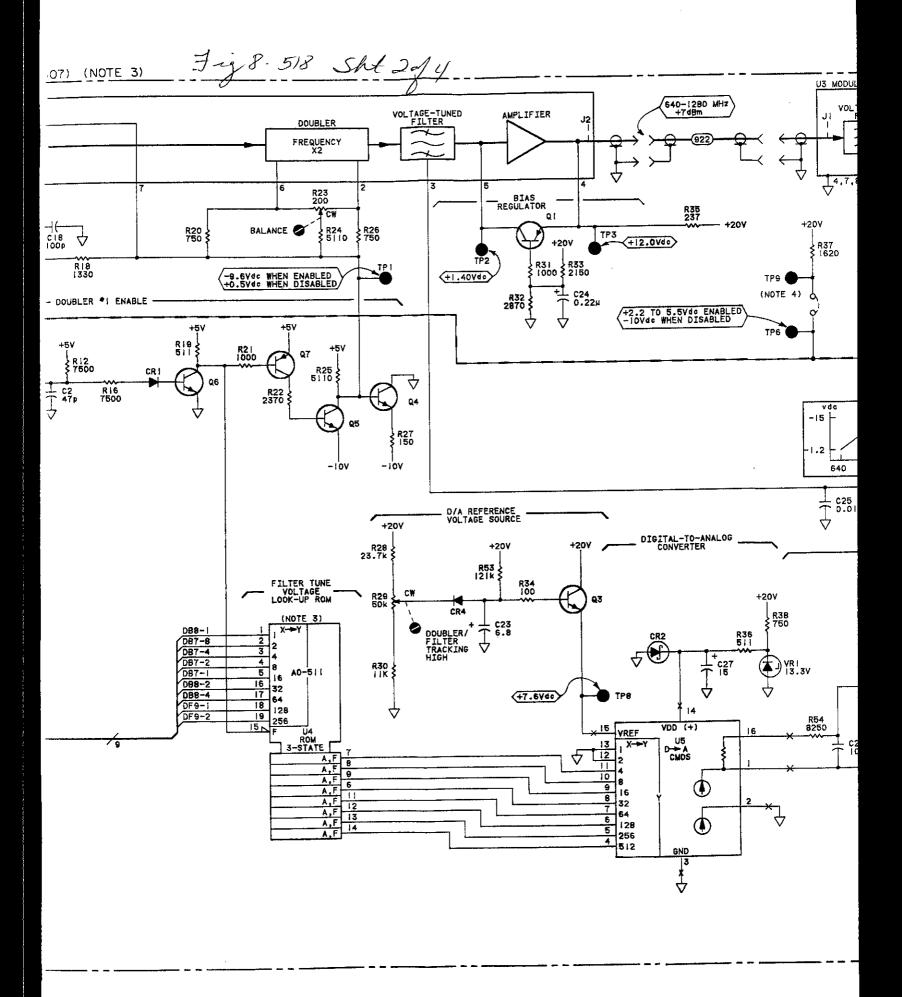

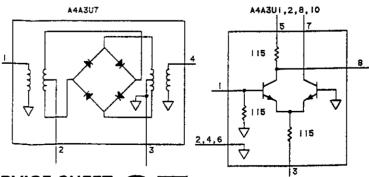

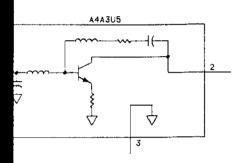

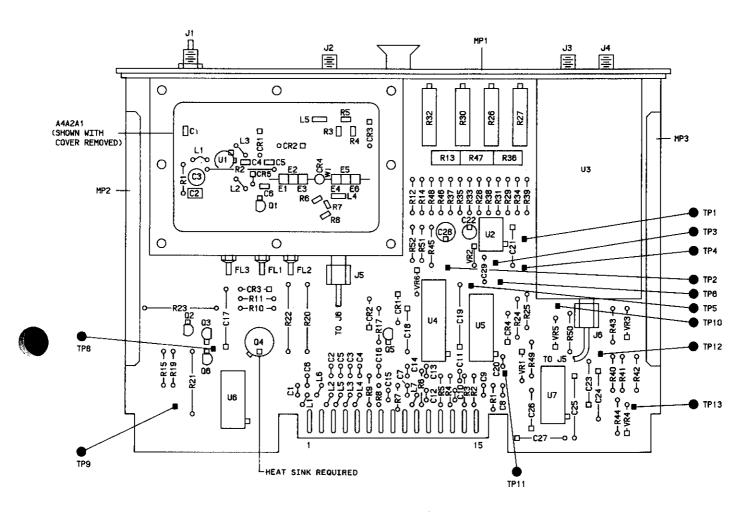

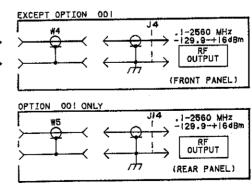

Figure 8-513. A12A2 UHF Modulator Block Diagrams

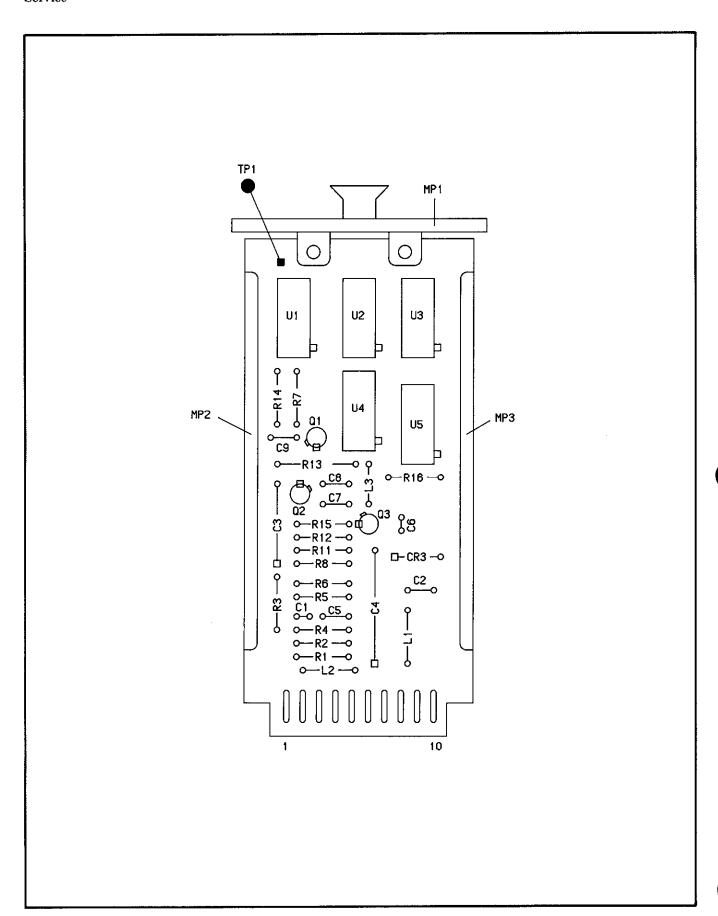

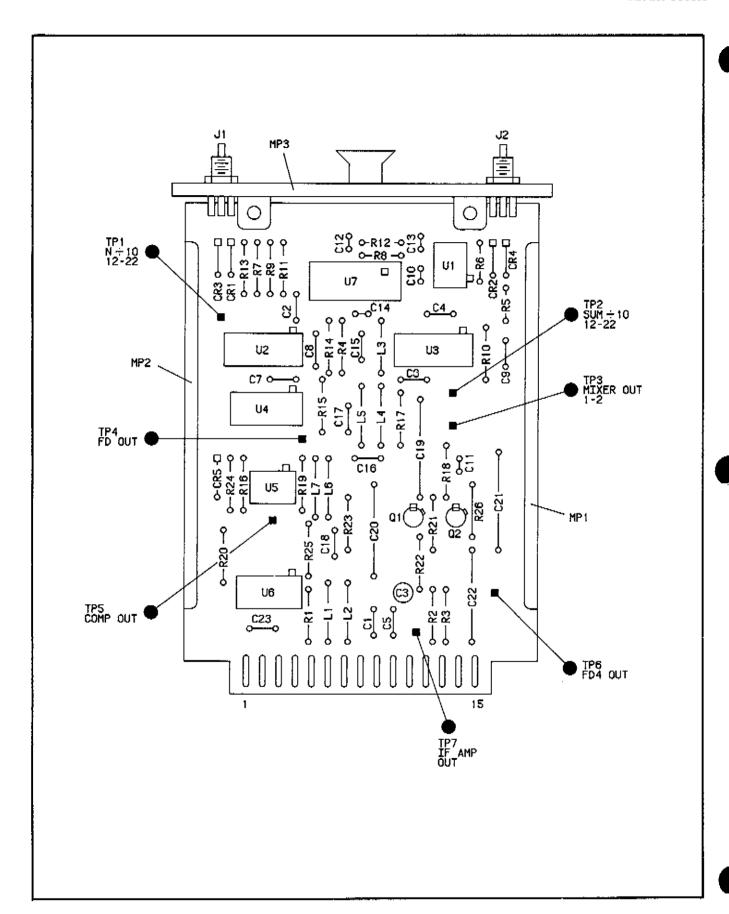

Figure~8-402.~A5A4 Fractional-N~Loop~Reference~Divider~Component~Locator

SERIAL PREFIX: 2234A

REFERENCE DIVIDER -

- 1. REFER TO TABLE 8-102 FOR SCHEMATIC DIAGRAM NOTES.

- 2. TROUBLESHOOTING VALUES ARE TYPICAL.

THEY ARE ACTUAL MEASURED VALUES.

YOUR MEASUREMENTS MAY BE SLIGHTLY

DIFFERENT THAN WHAT IS SHOWN.

#### REFERENCE DESIGNATIONS

|                    | 2020           |

|--------------------|----------------|

| NO PREFIX          | A5A6           |

| W38                | ال             |

| A5A4               | TP1-3<br>XA5A4 |

| C1-9<br>CR3        |                |

| L1-3<br>Q1-3       |                |

| RI-8, 11-16<br>TPI |                |

| TP1<br>U1-5        |                |

|                    | 1              |

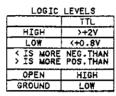

| LOGIC                 | LEVEL                |

|-----------------------|----------------------|

|                       | TTL                  |

| HIGH                  | >+2V                 |

| LOW                   | <+0.8V               |

| <pre> / IS MORE</pre> | NEG.THAN<br>POS.THAN |

# HIGH GROUND

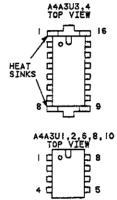

| INTEGRATED  | CIRCUIT |

|-------------|---------|

| VOLTAGE     | AND     |

| GROUND CONN | ECTIONS |

| REFERENCE<br>DESIGNATIONS | PIN<br>NUMBERS  |

|---------------------------|-----------------|

| UI,3-5                    | +5V - 14<br>- 7 |

| U2                        | +5V - 16        |

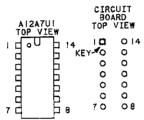

| A5A4UI<br>TOP VI | 3-5<br><u>E</u> W |         | CUIT<br>ARD<br>VIEW |

|------------------|-------------------|---------|---------------------|

| ı 🗖 o U          | 14                | 1 🗖     | 0 14                |

| d                | Þ                 | KEY 🗝 O | 0                   |

| ום ח.            | þ                 | 0       | 0                   |

|                  | Þ                 | 0       | 0                   |

|                  | Þ                 | 0       | 0                   |

|                  | Þ                 | 0       | 0                   |

| 7 🗖              | 8 🚅               | 70      | 0.8                 |

# TRANSISTOR AND INTEGRATED CIRCUIT PART NUMBERS

| I AIL INGING LIVE |           |  |

|-------------------|-----------|--|

| REFERENCE         | PART      |  |

| DESIGNATIONS      | NUMBERS   |  |

| Q1-3              | 1853-0034 |  |

| U1,4              | 1820-1251 |  |

| U2                | 1820-1418 |  |

| U3                | 1820-1206 |  |

| U5                | 1820-0693 |  |

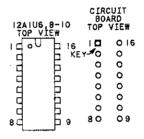

| A5A4U2<br>TOP VIEW |        | CIRCUII<br>BOARD<br>TOP VIEW |      |

|--------------------|--------|------------------------------|------|

|                    | oU ⊒16 | ΙD                           | 0.16 |

|                    |        | KEY -                        | 0    |

|                    |        | 0                            | 0    |

|                    |        | 0                            | 0    |

| ппппп              | 口口     | 0                            | 0    |

|                    | ₽      | 0                            | 0    |

|                    | P      | 0                            | 0    |

| 8 ⊏                | ₽a     | 80                           | 09   |

|                    |        |                              |      |

- Jig 8-403 Set 40/4

- 1. REFER TO TABLE 8-102 FOR SCHEMATIC DIAGRAM NOTES.

- 2. TROUBLESHOOTING VALUES ARE TYPICAL.

THEY ARE ACTUAL MEASURED VALUES.

YOUR MEASUREMENTS MAY BE SLIGHTLY

DIFFERENT THAN WHAT IS SHOWN.

#### REFERENCE DESIGNATIONS

| KELEKENCE D                                              | ESTRINA LTOMS        |

|----------------------------------------------------------|----------------------|

| NO PREFIX                                                | A5A6                 |

| W38<br>A5A4                                              | J!<br>TPI-3<br>XA5A4 |

| C -9<br>CR3<br>L -3<br>Q -3<br>R -8,  -+6<br>TP <br>U -5 |                      |

LOGIC LEVEL

| LOGIC LEVEL |              |  |

|-------------|--------------|--|

|             | TTL          |  |

| HIGH        | >+2 <b>V</b> |  |

| LOW         | <+0.8V       |  |

| <pre></pre> | NEG.THAN     |  |

| OPEN        | HIGH         |  |

| GROUND      | l.,OW        |  |

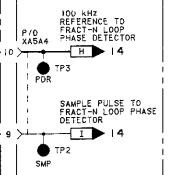

FOO KHZ REFERENCE TO FRACT-N LOOP PHASE DETECTOR

H 14

SAMPLE PULSE TO FRACT-N LOOP PHASE DETECTOR

-14

P/O A5A6

PDR TP3

TP2

P/0 XA5A4

(100 kHz) | PDR |

**▲** CR3

# INTEGRATED CIRCUIT VOLTAGE AND GROUND CONNECTIONS

| GROOMB COMMECTIVE         |                 |  |  |  |

|---------------------------|-----------------|--|--|--|

| REFERENCE<br>DESIGNATIONS | PIN<br>NUMBERS  |  |  |  |

| UI,3-5                    | +5V → 14        |  |  |  |

| U2                        | +5V - 16<br>- 8 |  |  |  |

|                           |                 |  |  |  |

| TOP VI | 3-5<br>EW<br>14 | 80  | CUIT<br>ARD<br>VIEW<br>O 14<br>O<br>O |

|--------|-----------------|-----|---------------------------------------|

| 9      | E               | •   | _                                     |

| 70     |                 | 70  | 0                                     |

| r •••  | Pr. V           | , • |                                       |

### TRANSISTOR AND INTEGRATED CIRCUIT PART NUMBERS

| REFERENCE    | PART      |

|--------------|-----------|

| DESIGNATIONS | NUMBERS   |

| Q1-3         | 1853-0034 |

| U1,4         | 1820-1251 |

| U2           | 1820-1418 |

| U3           | 1820-1206 |

| U5           | 1820-0693 |

| Ţ   | ASA4U2<br>DP VIE | ₩  |       | CIR<br>BD<br>TOP | CUIT<br>ARD<br>VIEW |

|-----|------------------|----|-------|------------------|---------------------|

| ıd  | U                | 16 |       | ΙD               | 016                 |

|     |                  |    | KEY - | 10               | 0                   |

|     |                  | ╘  |       | 0                | 0                   |

|     |                  |    |       | 0                | 0                   |

|     |                  | þ  |       | 0                | 0                   |

| П   |                  | ⊨  |       | 0                | 0                   |

|     |                  | þ  |       | ٥                | 0                   |

| 8 □ |                  | þ9 |       | 80               | 09                  |

# SERVICE SHEET A5A4 13

Figure 8-403. A5A4 Fractional-N Loop Reference Divider Schematic

SERVICE SHEET 14 A5A3 FRACTIONAL-N LOOP PHASE DETECTOR

### PRINCIPLES OF OPERATION

#### General

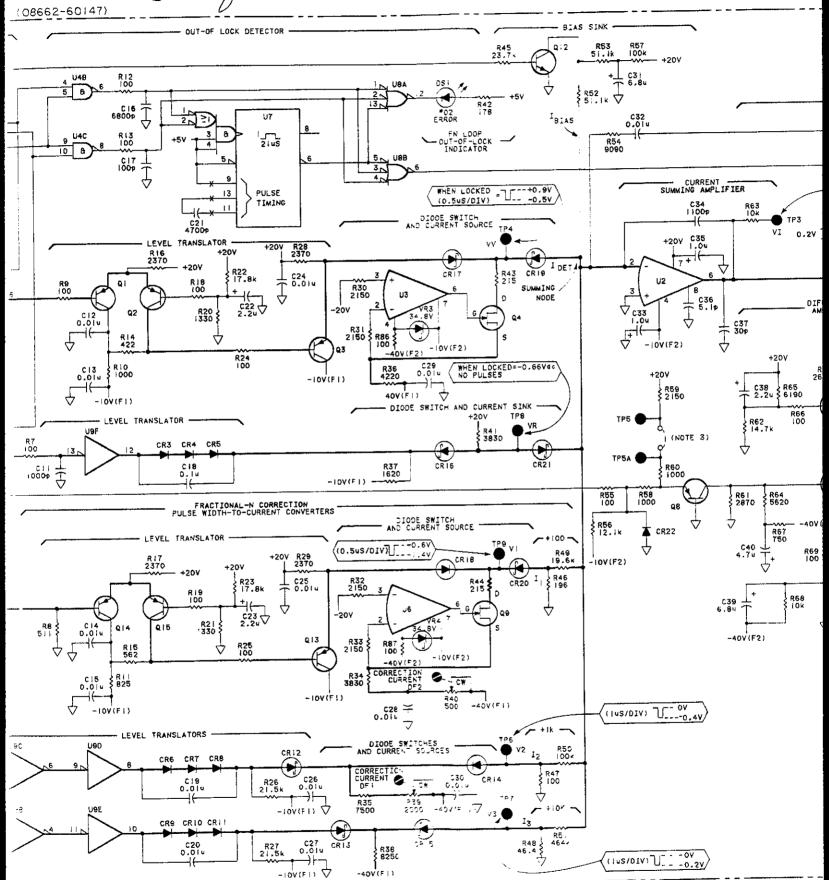

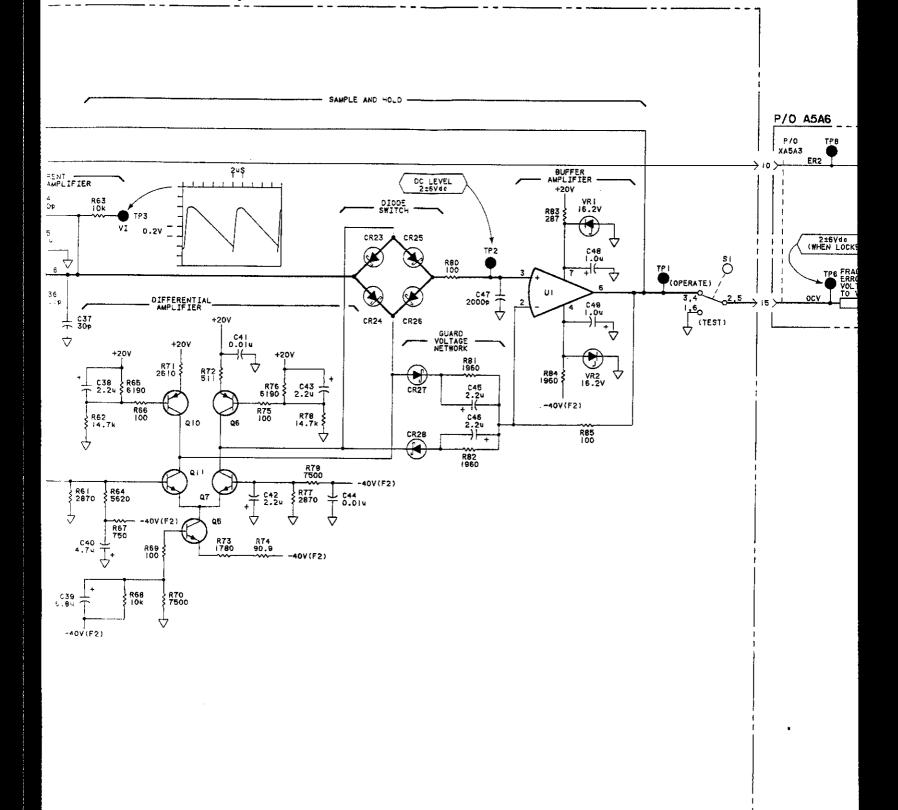

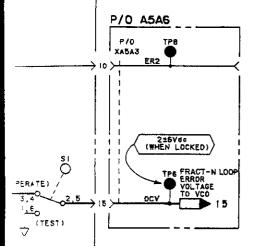

The purpose of the Fractional-N Loop Phase Detector (A5A3) is to develop the FN Loop Error Voltage which is used to tune the VCO. This FN Loop Error Voltage (tuning voltage) is developed by integrating currents from the Phase Detector circuit, the Fractional-N Correction Pulse Width to Current Converters, and the Bias Sink circuit. These currents are integrated together by the Current Summing Amplifier to develop a voltage. The Sample and Hold circuit samples the voltage output from the Current Summing Amplifier once each reference period and at the same time during each reference period. The sampled voltage becomes the FN Loop Error Voltage.

When the Fractional-N Loop (FN Loop) is phase-locked, the tune voltage must be a constant dc value. This means the voltage output from the Current Summing Amplifier must be the same at every sample period. In order to meet this condition the total of the currents being integrated must be the same each reference period. To look at it another way, the currents entering the summing node must equal the currents leaving the summing node in order for the tune voltage to remain constant. This concept, that when the FN Loop is phase-locked, the currents entering the summing node equal the currents leaving the node is true for all conditions, that is, for the condition when the loop runs without a fractional part and for the condition when it has a fractional part. The difference is that when the loop operates with no fractional part the output from the Phase Detector circuit remains constant. However, when the loop operates with a fractional part, the output from the Phase Detector circuit no longer remains constant but varies from reference period to reference period. To compensate for the changing phase detector output the outputs from the Fractional-N Correction Fulse Width to Current Converters must also change. For example, if the Phase Detector circuit supplies less current to the summing node, the Fractional-N Correction Pulse Width to Current Converters must supply more current so that the current entering the summing node is always a constant value.

### Phase Detector

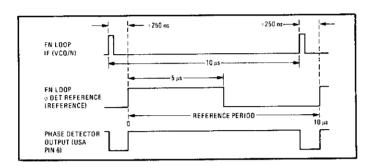

The Phase Detector consists of a pair of flip-flops, U5A and B, and gates U4D and U8C. The purpose of the Phase Detector is to generate a pulse width proportional to the phase difference between its two input signals, the FN Loop IF (VCO/N) and the FN Loop PM Det

Service Model 8663A

Reference (reference). Normally the FN Loop operates with a slight phase offset when the loop is phase-locked. This phase offset is due to the constant current being drawn from the summing node by the Bias Sink circuit. Figure 8-404 shows the phase relationship between the VCO/N signal and the reference signal when the loop is phase-locked and has no fractional part. Note that the two signals are equal in Frequency but are out of phase. This phase offset is normally about 250 ns.

Figure 8-404. Fractional-N Loop Phase Detector Input and Output Waveforms (Phase Locked and No Fractional Part)

This phase offset causes the Phase Detector (U5A) to generate a 250 ns negative-going pulse every reference period (See Figure x-xx). The other Phase Detector output (U5B) is normally only a glitch (which is filtered out) when the loop is phase-locked. U5B should only generate a pulse output during the acquisition of lock.

In a phase-locked condition the amount of current drawn from the summing node is equal to current driven into the node. When the FN Loop operates without a fractional part, the phase detector generates a constant pulse width every reference period. This results in a constant amount of current being driven into the summing node from the phase detector current source ( $I_{DET}$ ) each reference period. Currents from the Fractional-N Correction circuit ( $I_1$ ,  $I_2$ , and  $I_3$ ,) also remain constant, therefore, the total current entering into the summing node is always a constant value each reference period.

Now when the loop operates with a Fractional part, the VCO/N signal and reference signal no longer equal each other, hence the phase detector no longer generates a constant pulse width each reference period.

### NOTE

If the N-Divider (A5A2) is in the divide-by-N mode, the VCO/N signal starts to lag the reference frequency, which results in a series of decreasing pulse width signals from the phase detector. Conversely, if the N-Divider is dividing by N-1, the pulse width from the phase detector starts to increase.

For example, if the N-Divider is in the divide by N mode, the output pulses from the phase detector start to decrease in duration each reference period. This causes the phase detector current source, IDET, to be connected to the summing node for shorter periods each reference period. At the same time correction current from the Fractional-N Correction circuit is increasing (Correction Pulses duration increasing). The net result is that the decreasing phase detector current is compensated by the increasing correction currents so that the total current contributions from the Phase Detector and the Fractional-N Correction circuits to the summing node are always a constant value.

# Level Translators, Diode Switches and Current Sources

Following the Phase Detector are Level Translators, and Diode Switches and Current Sources. These circuits convert the digital outputs from the Phase Detector into currents. There are two types of Level Translators and Current Sources used. One type uses an active current source and a differential amplifier arrangement to switch the Diode Switch on and off. Q4 and U3 form an active current source while CR17 and CR19 form the Diode Switch. Q1, Q2 and Q3 make up the differential amplifier that translates the TTL levels to the appropriate levels required to drive the Diode Switch on and off. When the output from the Phase Detector goes LOW, CR17 is reverse-biased and CR19 is forward-biased, connecting the Current Source to the summing node. In the opposite state when the output is HIGH, CR17 is forward-biased and CR19 becomes reverse-biased, disconnecting the Current Source from the summing node.

The Levels Translator, Diode Switch and Current Source which follow the output of U5B word in a similar manner, as described previously. The major difference is that the active current source is replaced simply by a resistor, and that the level shifting is done with a diode string instead of a differential amplifier.

### Out-of-Lock Detector

The Out-of-Lock Detector monitors the two outputs from the Phase Detector to determine if the loop is unlocked. The Out-of-Lock Detector detects two unlock conditions. One condition is when the pulse width from U5A exceeds about 700 ns. The other condition is when the output from U5B exceeds 100 ns. Note that the Loop should never be in a phase-locked condition when U5B generates a pulse. Monostable U7 stretches either the 100 ns or 700 ns pulse to give a continuous indication that an unlocked condition exists.

Service Model 8663A

Fractional-N Correction Pulse Width To Current Converters (Fractional-N Correction)

The purpose of the Fractional-N Correction circuit is to develop the signals that counteract the changing phase detector output when the loop is operating with a fractional part. The Fractional-N Correction circuit is comprised of Level Translators, Diode Switches and Current Sources. These circuits convert the Correction Pulses (TTL levels) from the Accumulator (A4A1) into currents. The Level Translators, Diode Switches and Current Sources are the same types which follow the Phase Detector circuit. For discussion of these circuits, refer to the Section titled Level Translators, Diode Switches and Current Sources.

Each one of the Correction Current Sources  $I_1$ ,  $I_2$ , and  $I_3$ , is connected to the summing node once during each reference period. The sequence of these currents are as follows: Correction current  $I_3$ , Correction current  $I_2$ , and Correction current  $I_1$ . How long each of the Current Sources remains connected to the summing node depends on the negative pulse duration of its corresponding Correction Pulse.

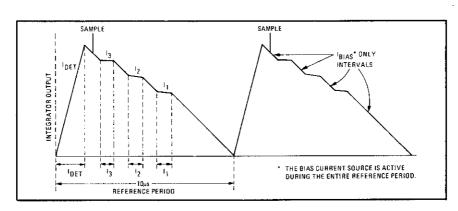

### Current Summing Amplifier

The Current Summing Amplifier is an integrator circuit. C34 is the integrating capacitor. When the loop is phase-locked the currents being integrated are:  $I_{DET}$ ;  $I_3$ ;  $I_2$ ;  $I_1$  and currents from the feedback network C32 and R54.

Due to the different magnitudes of the various current sources and the different times the current sources are connected to the summing node, the output from the Current Summing Amplifier is continuously ramping up and down. Figure 8-405 illustrates the integrator waveform showing the contribution of the different currents.

Figure 8-405. Current Summing Amplifier Output Waveform showing the contributions of the different currents

### Sample and Hold

The circuits which make up the Sample and Hold circuit are the Diode Switch, Differential Amplifier, Guard Voltage Network, and the Buffer Amplifier. During each reference period, the four diodes which comprise the Diode Switch are all forward-biased and the output of the Current Summing Amplifier is sampled. This sample voltage (VS) is stored in hold capacitor C47. During the hold period the Diode Switch is reversed-biased and the hold capacitor remains stored. The Buffer Amplifier, Ul, which follows the hold capacitor, provides isolation and a low output impedance.

The Buffer Amplifier is a unity-gain, noninverting amplifier. Feedback from this output is fed back to the summing node through C32 and R54 for loop stabilizations.

Switching of the Diode Switch is controlled by the Differential Amplifier. During the sample period, the Sample Pulse line goes high, causing the Differential Amplifier to supply current to the Diode Switch. The Differential Amplifier also provides current to the Guard Voltage Network during the hold period.

The purpose of the Guard Voltage Network is to ensure that the voltage to be sampled does not itself forward-bias the Diode Switch during the hold period. The guard voltages (the collector voltages of Q7 and Q11) are balanced and centered around the last sample voltage. About 2 ma of current flows through the Guard Voltage network during the hold of current flows through the Guard Voltage network during the hold period. This causes a voltage drop of 4V (guard voltages) across CR28 and R82 and across CR27 and R81 the guard voltages equal +6V and -2V for a sample voltage of +2 Vdc (guard voltages = Vs + 4 Vdc).

# TROUBLESHOOTING

When a Fractional-N Loop problem has been traced through the block diagram troubleshooting procedure to this assembly, use the following procedure to isolate the cause of the problem.

- 1. Mount the A5A3 assembly on an extender board from the service kit. Move the slide switch on A5A3 to the TEST position (up) which opens the loop.

- 2. Monitor TP3 with an oscilloscope. The waveform should be a dclevel with small spikes. Measure the frequency of the signal at pin 14 of the edge connector.

Turn the PRETUNE-GAIN adjustment on the top of the A5A5 VCO assembly while monitoring the frequency at pin 14. Move the frequency above and below 100 kHz and check that the voltage at TP3 goes to the values shown in the following table. If the voltages at TP3 are normal, continue troubleshooting with step 3. Otherwise, there is a problem with the basic phase detector circuitry so continue troubleshooting with step 4.

| Edge Connector  | A5A3  | A5A3  | A5A3  |

|-----------------|-------|-------|-------|

| Pin 14          | TP3   | TP2   | TP1   |

| Frequency (kHz) | (Vdc) | (Vdc) | (Vdc) |

| >100 kHz        | +18   | +16   | +15   |

| <100 kHz        | -7    | -7    | -7    |

3. Repeat the measurement made in step 2 while monitoring TP2 and then TP1. Compare the measured values to the normal values in the table above.

If the voltage at TP2 is not normal, the differential amplifier or diode switch is bad. Shorting TP5 and TP5A together holds the amplifier and diode switch in the ON condition for troubleshooting.

If the voltage at TP1 is not normal but the voltage at TP2 is normal, the problem is in U1 or associated circuitry.

4. Turn the PRETUNE-GAIN adjustment on A5A5 so the frequency at pin 14 of the A5A3 edge connector is greater than 100 kHz. Check that there are pulses on A5A3 TP4.

Change the frequency at pin 14 to less than 100 kHz. Check that there are pulses on A5A3 TP8.

5. If pulses are not present at one of the test points, troubleshoot from U5 to find the cause of the problem. If both pulses are present, the problem is with U2 or associated components.

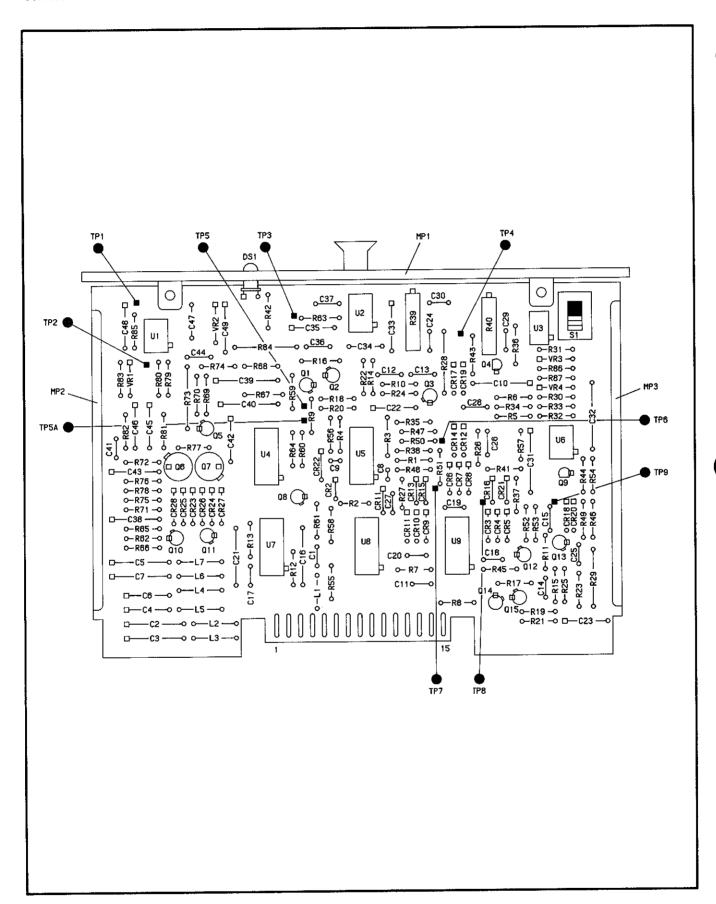

Figure 8-407. A5A3 Fractional-N Loop Phase Detector Component Locator

P/O A5A6 FRACTIONAL-N LOOP A5A3 FRACTIONAL-N LOOP PHASE DETECTOR (08662-60147) MOTHERBOARD (08662-60152) PHASE DETECTOR FROM FRACT-N LOOP VCO INHIBIT 15 F R12 100 4 U4B ┰ ± 1000° 5 a C16 6800p 8 13 C17 T LEVEL TRANSL TP5 (100kHz) R16 2370 FRACT-N LOOP IF RI +20V 16 🕡 R18 100 R3 12.1x - C8 100p  $\nabla$ -:0V(F2) R10 1000 -10V(F1) (100kHz) FRACT-N LOOP PHASE DETECTOR REFERENCE FROM REF DIVIDER LEVEL TRANSLATOR \_\_\_\_\_ 13/ CR3 CR4 SAMPLE PULSE FROM REF DIVIDER -10V(F2) (100kHz) FR# PULSE W POWER SUPPLY DECOUPLING +20V 66 B 2 **†** LEVEL TRANSLA -<u>|</u>| | 13,15 [3,15,16, 17 +57 R17 2370 65 C -(92 + Ç3 +20V TP4 R19 100  $\nabla$ 17 0 -107 Q15 66 💿 TP10 I -XX 15 GND ÷ 2.2. 65 Z R11 825 LE 7 AO 13,15, 16,17, GND -40V 66 E -10V(F1) -40V + C10 6.8u R6 4220  $\overline{\forall}$ LEVEL TRANSLATORS  $\preceq \tilde{z}_{r,i}^{\tilde{z}_{r,j}}$ U9D 4220 CORRECTION PULSE 2 FROM ACCUMULATOR CR6 CR7 7 -201 17 P CORRECTION PULSE 3 FROM ACCUMULATOR CR9 CRIO 17 0 SERIAL PREFIX: 2234A

Fig 8-408 Sht 2014

Jug 8-408 Sht 3 of 4

Jig 8-408 Sht 4014

NOTES

- 1. REFER TO TABLE 8-102 FOR SCHEMATIC DIAGRAM NOTES.

- 2. TROUBLESHOOTING VALUES ARE TYPICAL.

THEY ARE ACTUAL MEASURED VALUES.

YOUR MEASUREMENTS MAY BE SLIGHTLY

DIFFERENT THAN WHAT IS SHOWN.

- 3. SHORTING TP5 TO TP5A KEEPS THE DIODE SWITCH CLOSED SO THE OUTPUT OF U2 IS ALWAYS CONNECTED TO THE INPUT OF U1. IN THIS CONDITION, THE WAVEFORM AT TP3 SHOULD APPEAR AT TP2.

### REFERENCE DESIGNATIONS

| NO PREFIX                                                                        | <b>A5A</b> 6        |

|----------------------------------------------------------------------------------|---------------------|

| W53                                                                              | TP2-6,8,10<br>XA5A3 |

| A5A3                                                                             |                     |

| C1-49<br>CRI-28<br>DSI<br>LI-7<br>QI-15<br>RI-87<br>SI<br>TPI-9<br>UI-9<br>VRI-4 |                     |

| LOGIC                                  | LEYEL\$              |

|----------------------------------------|----------------------|

|                                        | TTL                  |

| HIGH                                   | >+2V                 |

| LOW                                    | <+0.8V               |

| <pre> &lt; IS MORE  &gt; IS MORE</pre> | NEG.THAN<br>POS.THAN |

| OPEN                                   | HIGH                 |

| GROUND                                 | LOW                  |

|                                        |                      |

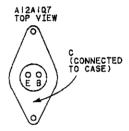

| TOP VIEW  |        |             |

|-----------|--------|-------------|

|           |        | CUIT        |

| 10001     | 10P    | ARD<br>VIEW |

| 210 06    | 10     | 0 8         |

| \ /       | KEY-*O | 0           |

| \0 \ 0 \/ | 0      | ٥           |

| 3 ~ 5     | 40     | 05          |

|           |        |             |

#### TRANSISTOR AND INTEGRATED CIRCUIT PART NUMBERS

| REFERENCE                                            | PART                                                                                                                                                     |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| DESIGNATIONS                                         | NUMBERS                                                                                                                                                  |

| 21-3.6, 10, 24.9 4.9 4.9 4.9 4.9 4.9 4.9 4.9 4.9 4.9 | 1853-0007<br>1855-0081<br>1854-0210<br>1853-0012<br>1854-0013<br>1854-0023<br>1826-0089<br>1826-0089<br>1820-0681<br>1820-0681<br>1820-0586<br>1820-0586 |

| A5A3<br>U4,5,7 <del>-</del> 9<br>TOP VIEW |        | CIRC | IRD . |

|-------------------------------------------|--------|------|-------|

| 1 400                                     | 14     |      | VIEW  |

|                                           | 1 1 44 | 10   | 014   |

| 9 5                                       | K      | EY-O | ٥     |

| 9 8                                       |        | 0    | 0     |

|                                           | !      | 0    | 0     |

|                                           |        | 0    | 0     |

| E                                         |        | 0    | 0     |

| 7 9 P                                     | 8      | 70   | 0.6   |

|                                           |        |      |       |

# INTEGRATED CIRCUIT VOLTAGE AND GROUND CONNECTIONS

| GROUND CONNECTIONS        |                |  |  |

|---------------------------|----------------|--|--|

| REFERENCE<br>DESIGNATIONS | PIN<br>NUMBERS |  |  |

| U4,5,7-9                  | +57 - 14       |  |  |

|                           |                |  |  |

# A5A3 14

Figure 8-408. A5A3 Fractional-N Loop Phase Detector Schematic

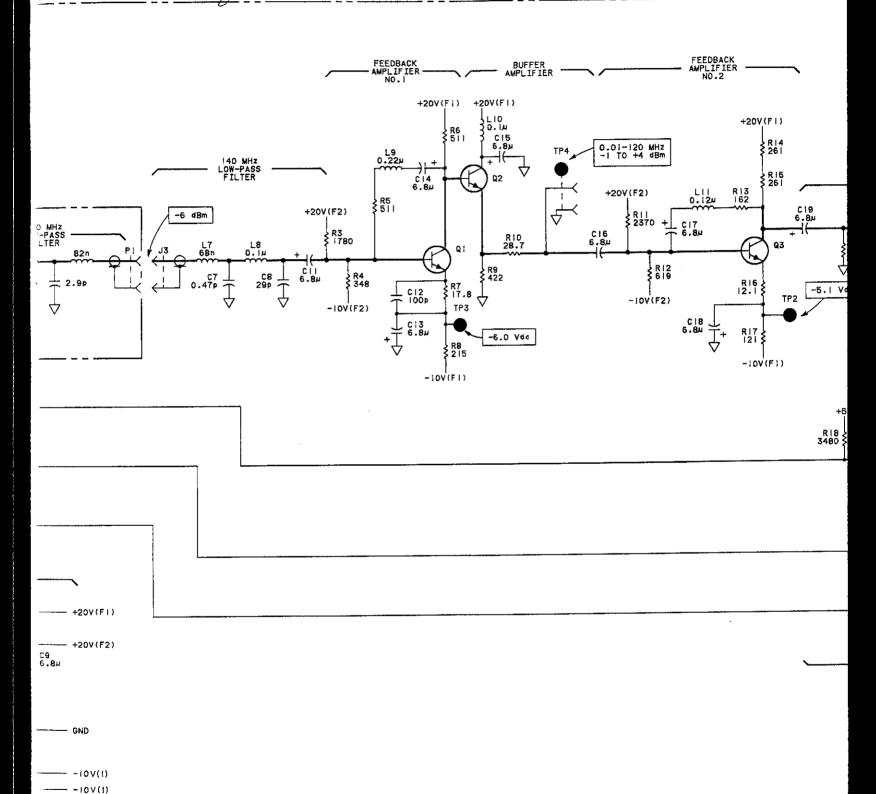

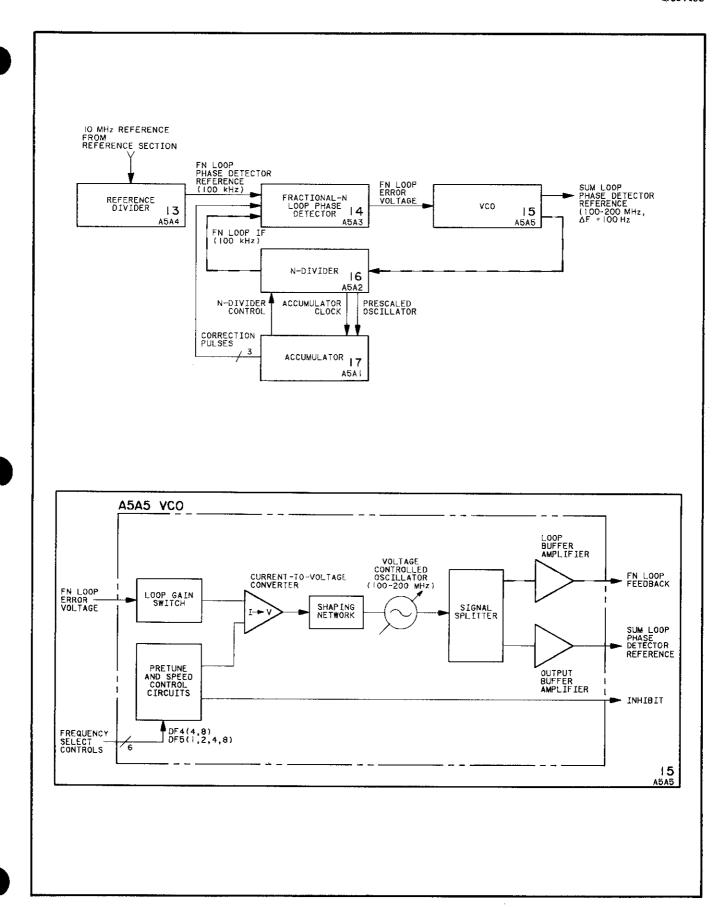

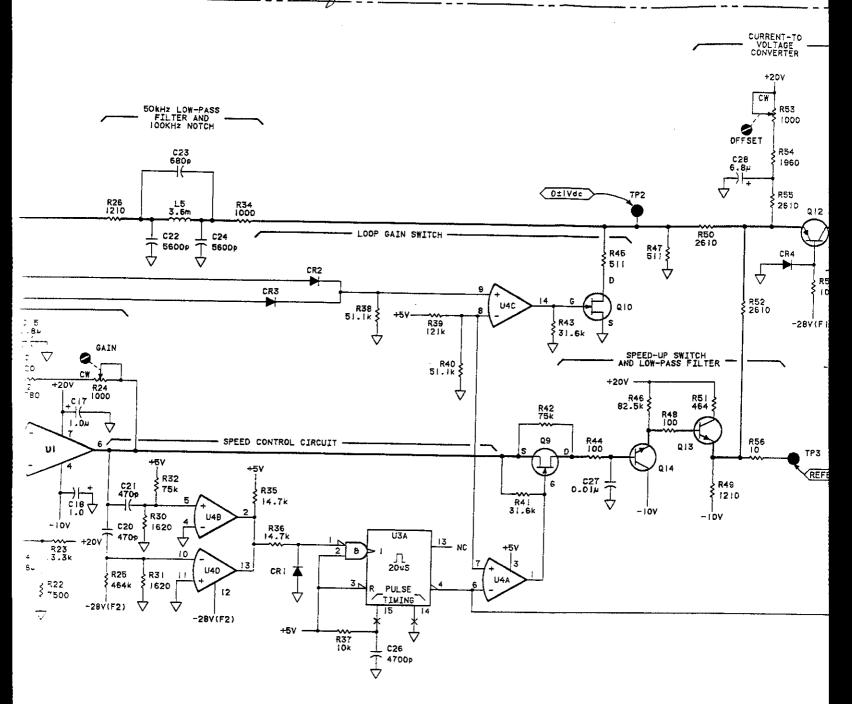

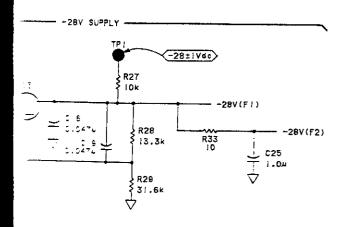

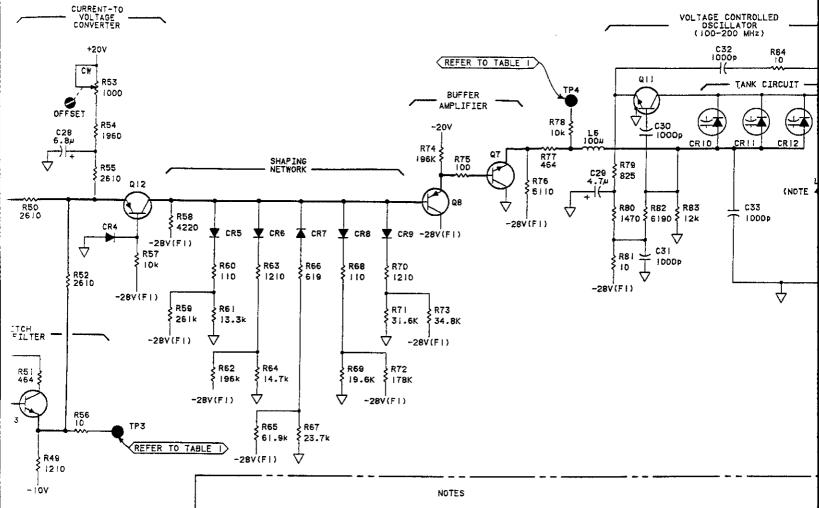

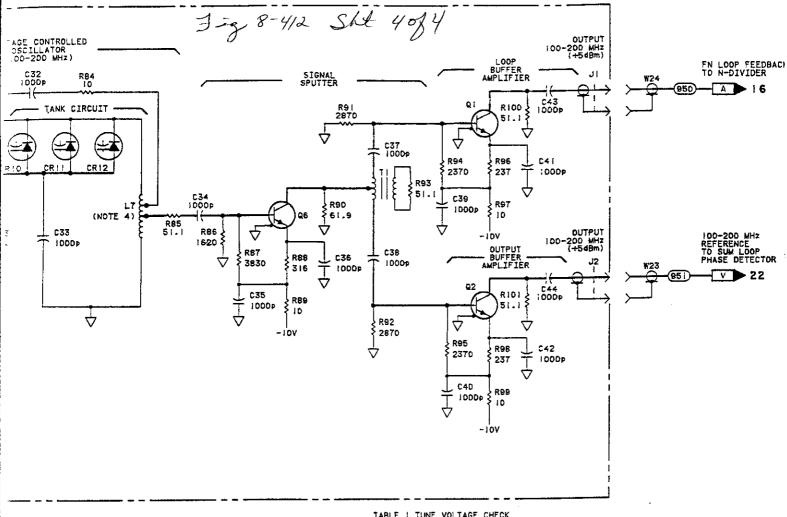

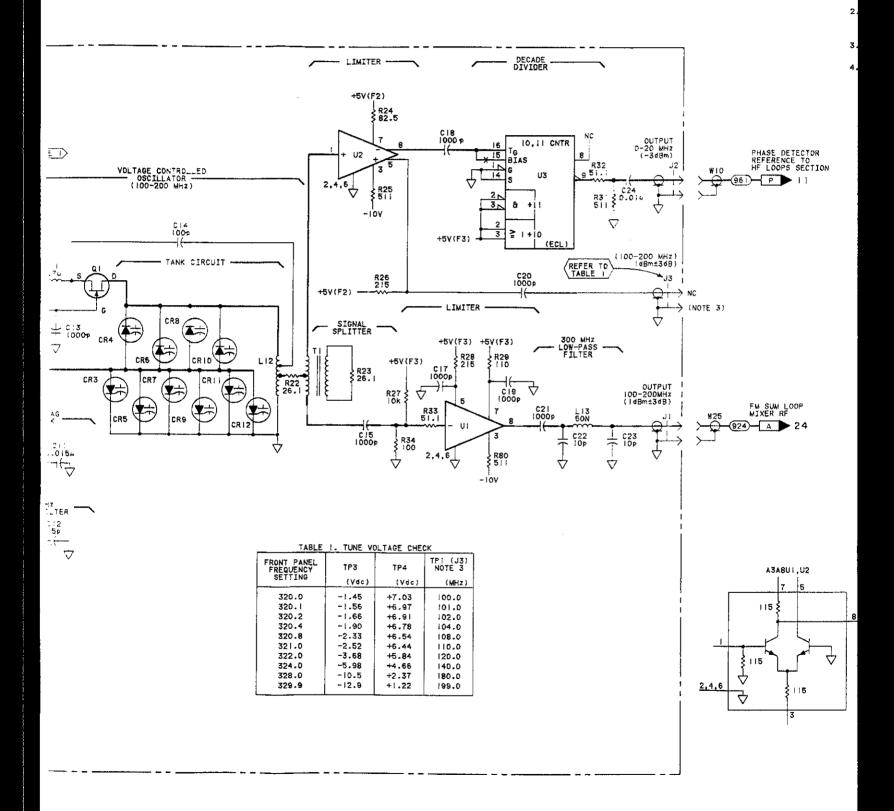

SERVICE SHEET 15 A5A5 FRACTIONAL-N LOOP VCO

REFERENCE BLOCK DIAGRAM 4

Table 4-1. Recommended Performance Tests

After Adjustments or Repair

Table 5-2. Post-Repair Adjustment Procedures

## PRINCIPLES OF OPERATION

### General

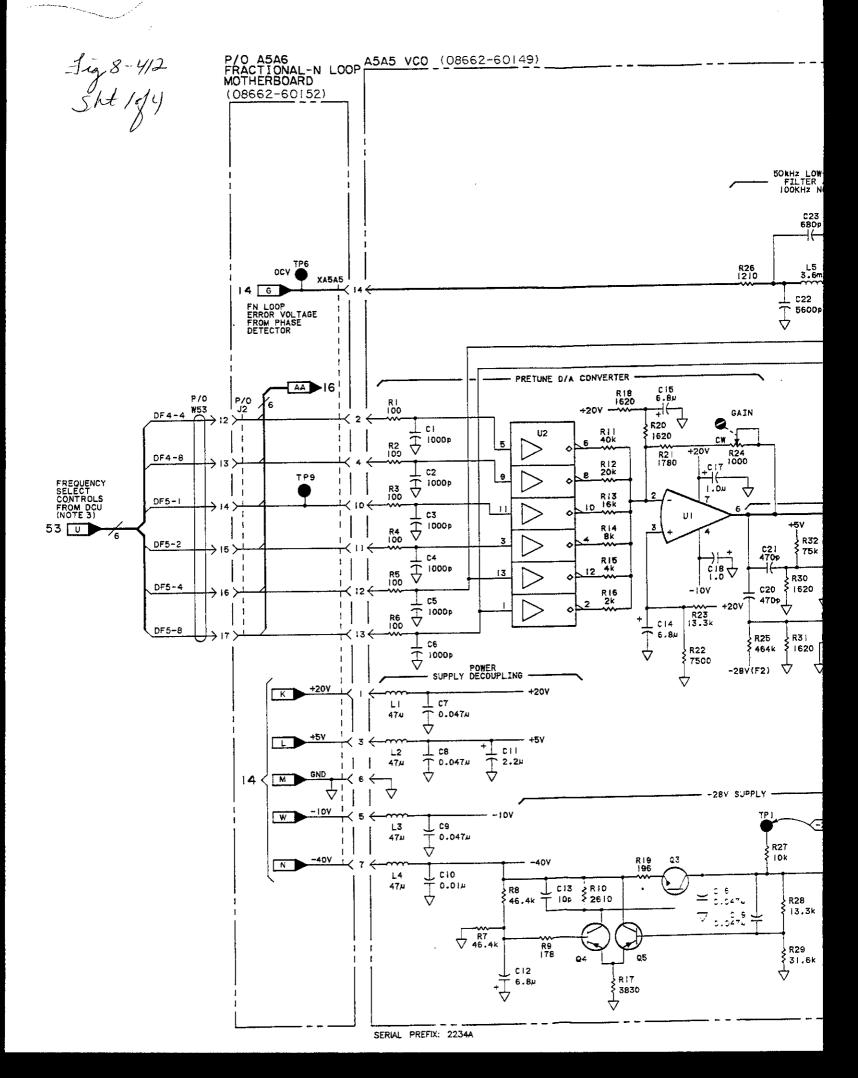

The purpose of the VCO ( $A^{4}A^{4}$ ) is to generate an output frequency between 100 MHz and 200 MHz. The primary inputs are the pretune information, Digit Frequency DF4 and DF5, and the FN Loop Error Voltage. The output from the Pretune D/A Converter is used to tune the VCO close to the desired frequency and then the FN Loop Error Voltage is used to phase lock the loop.

# Voltage-Controlled Hartley Oscillator (VCO)

Varactors CR10, CR11, and CR12, transistor Q11, and associated components comprise a voltage-controlled Hartley oscillator. Three varactors are used in parallel to provide the wide capacitance range required to tune the VCO. Feedback is obtained by tapping the inductive branch (L7) of the Tank Circuit. C32 and R84 couple the feedback signal back to the emitter of Q11 to sustain oscillation.

The VCO is both pretained and phase locked by controlling the reverse bias voltage on the varactor diodes. An increase in the reverse bias voltage causes a reduction in the junction capacitance of the varactor diodes. This reduction increases the resonant frequency of the Tank Circuit, causing the VCO to oscillate at a higher frequency.

## Signal Splitter and Buffer Amplifiers

The signal developed across the resonant Tank Circuit is coupled to Q6 by tapping inductor L7. Q6 amplifies the signal and applies the signal to the center tap winding of T1. T1 splits the power and adds isolation between the buffer amplifiers. The output from the Loop Buffer Amplifier is used to phase lock the loop. The output from the Output Buffer Amplifier goes to the Low Frequency Loop Section where it is combined with other signals.

### Shaping Network

Due to the nonlinear tuning characteristics of the varactor diodes a Shaping Network is required. The Shaping Network conditions the pretune and error signals applied to the varactor in order to ensure that the frequency change is linear with the applied tuning voltage.

Service Model 8663A

The Shaping Network consists of a ladder of diodes that are reverse-biased at successively higher voltage. As the voltage at the collector of Q12 increases, the diodes turn on consecutively and present a lower impedance to the tuning signal.

## Current to Voltage Converter

Common-base amplifier Q12 sums the output of the Pretune D/A Converter, current from the +20V source (R53) and the FN Loop Error Voltage from the phase detector. The voltage at the emitter (summing point) is always near zero volts since the base of Q12 is biased one diode drop below ground.

## Pretune D/A Converter

The output from the Pretune D/A Converter roughly tunes the VCO to a frequency within the capture range of the phase lock loop. The Pretune D/A Converter cannot, by itself, set the VCO precisely.

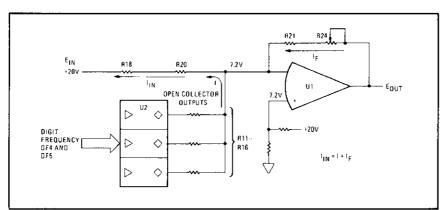

Op amp, U1, is connected in the inverting amplifier configuration. Its output voltage is programmed by Frequency Digits DF4 and DF5. Figure 8-409 is a simplified schematic of the Pretune D/A Converter Circuit.

Figure 8-409. Simplified Pretune D/A Converter Circuit

To better analyze how this circuit works, assume that the op amp (U1) is ideal. That is, its gain and bandwidth are both infinity, the input currents and offset are both zero, and there is zero potential difference between the two input terminals. The output voltage,  $E_{OUT}$ , is dependent on the feedback current,  $I_F$ , that flows through R21 and R24. In the ideal inverting amplifier configuration the feedback current must equal the input current ( $I_{IN} = I_F$ ). The magnitude of the input current  $I_{IN}$  is dependent on the potential across R18 and R20. In this circuit the magnitude of  $I_{IN}$  remains constant at all times.

If the outputs of U2 are all HIGH (open), there is no current flowing through the pull-up resistors, R11-R16. Hence, the input and feedback currents equal each other. Now, when any of the outputs of U2 goes LOW, current starts flowing into the (-) input node through the pull-up resistors.  $\rm I_{IN}$  is no longer equal to  $\rm I_F$ ,  $\rm I_{IN}$  now

equaling  $I_F$  + I. Since the value of  $I_{\rm IN}$  has to remain constant, the feedback current has to decrease so equilibrium is maintained. A decrease in  $I_F$  causes the output voltage,  $E_{\rm OUT},$  to decrease in magnitude.

# Speed Control Circuit

The Speed Control Circuit monitors the output from the Pretune D/A Converter circuit. When a change in the pretune voltage is detected, the Speed Control Circuit drives the J-FET switch (Q9) ON. U4B and U4D are comparators. U4B detects a negative going transition while U4D detects a positive going transition. When either transition is detected, the monostable U3 is triggered. This causes comparator U4A to go HIGH which then turns ON J-FET switch Q9.

## Speed-Up Switch and Low-Pass Filter

J-FET Q9 is connected in parallel with R42, so when Q9 is turned ON C27 is allowed to charge or discharge at a faster rate. Hence, voltage stored on the capacitor tracks the pretune voltage at a faster rate. Q13 and Q14 form a buffer amplifier that couples the pretune voltage to the emitter of Q12.

To maintain the J-FET switch in the ON state, the gate is biased with a positive voltage. To turn the J-FET switch OFF, the gate is biased with a negative voltage.

Figure 8-410. A5A5 Fractional-N Loop Voltage Controlled Oscillator Block Diagrams

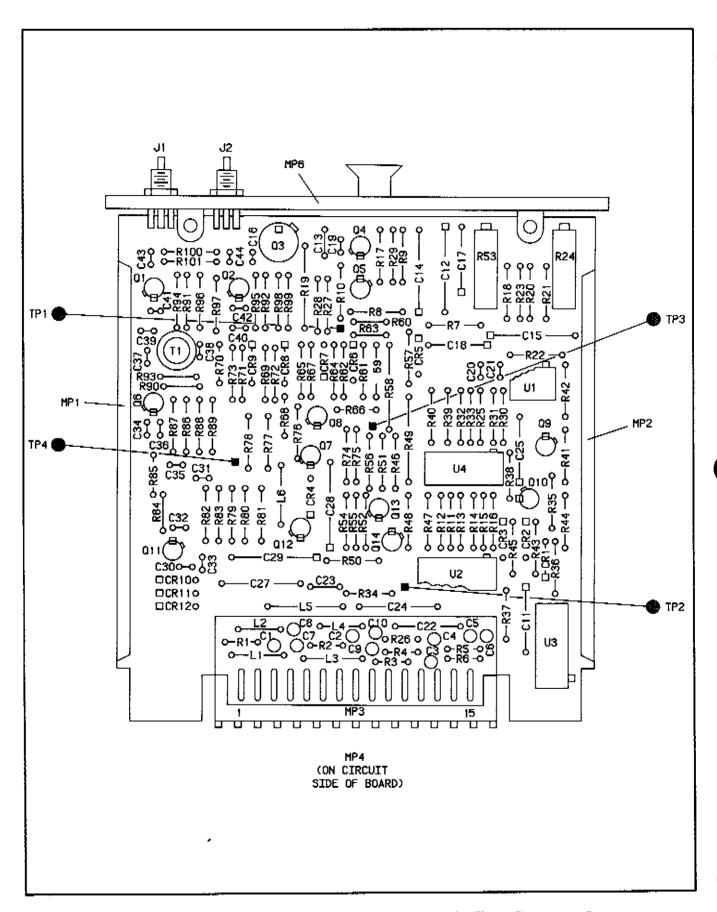

Figure 8-411. A5A5 Fractional-N Loop Voltage Controlled Oscillator Component Locator

# **CHANGES**

### All serial prefixes

### On the A5A5 schematic:

2684A and Above

• A5A5R1-R6 - Change the value of R1-R6 to 178 ohms.

On the A5A5 schematic:

• A5A5CR6-CR9 - Delete CR6-CR9.

A5A5R53, R54, R58-R61 - Change the values of these resistors to those shown below:

R53 3k R54 100 ohms R58 3.83k R59 56.2k R60 348 ohms R61 5.62k

• A5A5R62-R73 - Delete R62-R73.

P/0 A5A6

XA5A5 | | 3, | 15 | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16, | 16,

- :- REFER TO TABLE 8-102 FOR SCHEMATIC DIAGRAM NOTES.

- 2. TROUBLESHOOTING VALUES ARE TYPICAL.

THEY ARE ACTUAL MEASURED VALUES.

YOUR MEASUREMENTS MAY BE SLIGHTLY

DIFFERENT THAN WHAT IS SHOWN.

- 3. MNEMONICS DF4-4 TO DF5-8 REPRESHT THE FREQUENCY DIGITS ON THE FRONT PANEL AND THE BCD WEIGHTING

- 4. INDUCTOR LT IS A PC TRACE INDUCTOR

# TRANSISTOR AND INTEGRATED CIRCUIT PART NUMBERS

| REFERENCE    | PART      |

|--------------|-----------|

| DESIGNATIONS | NUMBERS   |

| Q1,2,6,11    | 1854-0540 |

| Q3           | 1854-0039 |

| Q4,5,8,12,14 | 1853-0451 |

| Q7,13        | 1854-0404 |

| Q9,10        | 1855-0020 |

| U1           | 1826-0377 |

| U2           | 1820-0577 |

| U3           | 1820-1423 |

| U4           | 1826-0138 |

## REFERENCE DESIGNATIONS

| NO PREFIX                                                        | A5A6                 |

|------------------------------------------------------------------|----------------------|

| W23,24<br>53                                                     | J2<br>TP6.9<br>XA5A5 |

| A5A5                                                             |                      |

| CI-44<br>CRI-12<br>J!,2<br>L!-7<br>RI-10!<br>TI<br>TPI-4<br>UI-4 |                      |

# INTEGRATED CIRCUIT VOLTAGE AND GROUND CONNECTIONS

|   | GROUND CONNECTIONS        |                |             |  |  |  |

|---|---------------------------|----------------|-------------|--|--|--|

| ĺ | REFERENCE<br>DESIGNATIONS | PIN<br>NUMBERS |             |  |  |  |

|   | U2                        | +5∨            | - 14<br>- 7 |  |  |  |

|   | กร                        | +5∨            | - 8<br>- 8  |  |  |  |

ISTOR AND ED CIRCUIT NUMBERS

| TOMBLITO |                                                               |  |

|----------|---------------------------------------------------------------|--|

| s '      | PART<br>NUMBERS                                               |  |

| 4        | 1854-0540<br>1854-0039<br>1853-0451<br>1854-0404<br>1855-0020 |  |

|          | 1826-0371<br>1820-0577<br>1820-1423<br>1826-0138              |  |

| TED DIRC<br>-GE AND<br>-ONNECTI |             |

|---------------------------------|-------------|

|                                 | IN<br>MBERS |

| +5∨                             | - 14<br>- 7 |

| +5∨<br>▽                        | - 8         |

| LOGIC LEVEL |                      |  |

|-------------|----------------------|--|

|             | ΤTL                  |  |

| HIGH        | >+2V                 |  |

| LOW         | <+0.8V               |  |

| <pre></pre> | NEG THAN<br>POS.THAN |  |

| OPEN        | HIGH                 |  |

| GROUND      | LOW                  |  |

| ASASU:<br>TOP VIEW | CIRCUIT<br>BOARD<br>TOP VIEW |    |

|--------------------|------------------------------|----|

|                    | 1,0                          | 08 |

| 2 0 5 5K           | 5.43<br>C                    | 0  |

| 100/               | 0                            | 0  |

| 3 0 5              | 40                           | 05 |

| 4                  |                              |    |

| 4545U2<br>T <u>OP</u> V | . Z<br>ĒW | BO      | CUIT<br>ARD<br>VIEW |

|-------------------------|-----------|---------|---------------------|

| 1 🛱 💇                   | Ξ !       | , 2     | 0 14                |

| 7                       |           | E Y-P O | 0                   |

| 71170                   | =         | ٥       | 0                   |

| =                       | Ξ         | 0       | O                   |

| 3                       | Ξ         | 0       | ٥                   |

| 9                       | -         | ٥       | 0                   |

| 7 🖳                     | _= ₽      | 70      | 08                  |

| TABLE I TUNE VOLTAGE CHECK          |       |       |                  |

|-------------------------------------|-------|-------|------------------|

| FRONT PANEL<br>FREQUENCY<br>SETTING | TP3   | TP4   | VCO<br>FREQUENCY |

| (MHz)                               | (Vdc) | (Vdc) | (MH2)            |

| 320.0                               | -2.1  | -13.5 | 200.0            |

| 320.004                             | -1.7  | -13.0 | 196.0            |

| 320.008                             | -1.3  | -12.4 | 192.0            |

| 320.01                              | +i.1  | -12.2 | 190.0            |

| 320.02                              | 0.0   | -11.0 | 180.0            |

| 320.04                              | +2.1  | ~B.9  | 160.0            |

| 320.08                              | +6.2  | -3.8  | 120.0            |

| 320.099                             | +8.0  | -1.5  | 101.0            |

| A5A5U3   |      | CIRCUIT<br>BOARD<br>TOP VIEW |      |  |

|----------|------|------------------------------|------|--|

| TOP VIE  | 1    | Jo                           | 0 16 |  |

| aumana   | D 16 | 70                           | 0    |  |

| 급        | þ K! | EY o                         | 0    |  |

| ΞÍ.      | Þ    | 0                            | 0    |  |

| ₫        | Þ    | 0                            | 0    |  |

| <b>=</b> | Þ    | 0                            | 0    |  |

|          | Þ    | 0                            | 0    |  |

| 8 □      | e 🖯  | 80                           | 09   |  |

# SERVICE SHEET A5A5 15

Figure 8-412. A5A5 Fractional-N Loop Voltage Controlled Oscillator Schematic

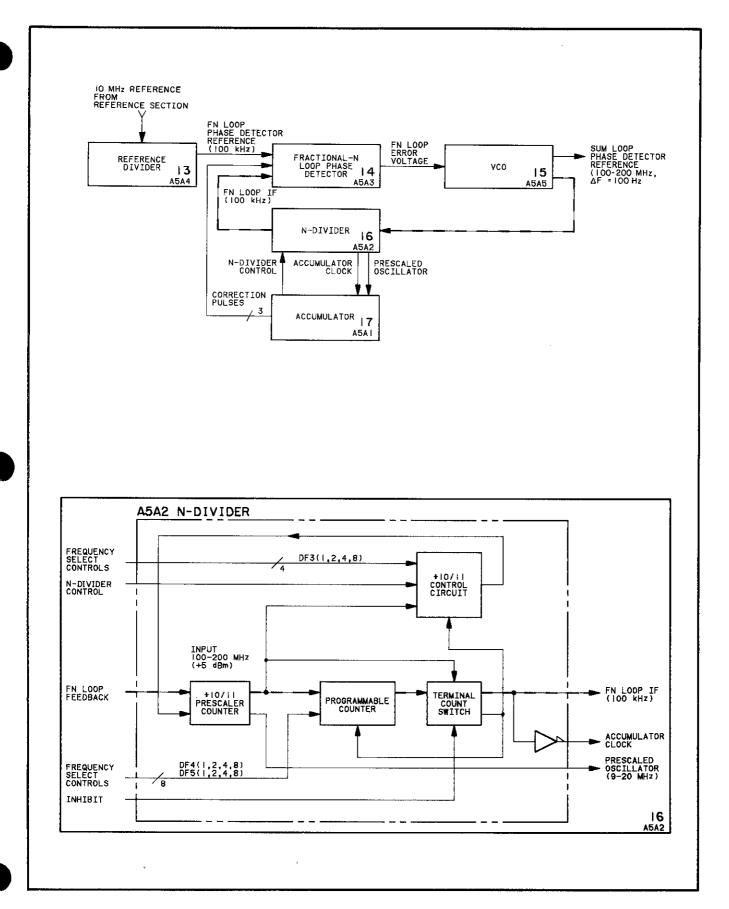

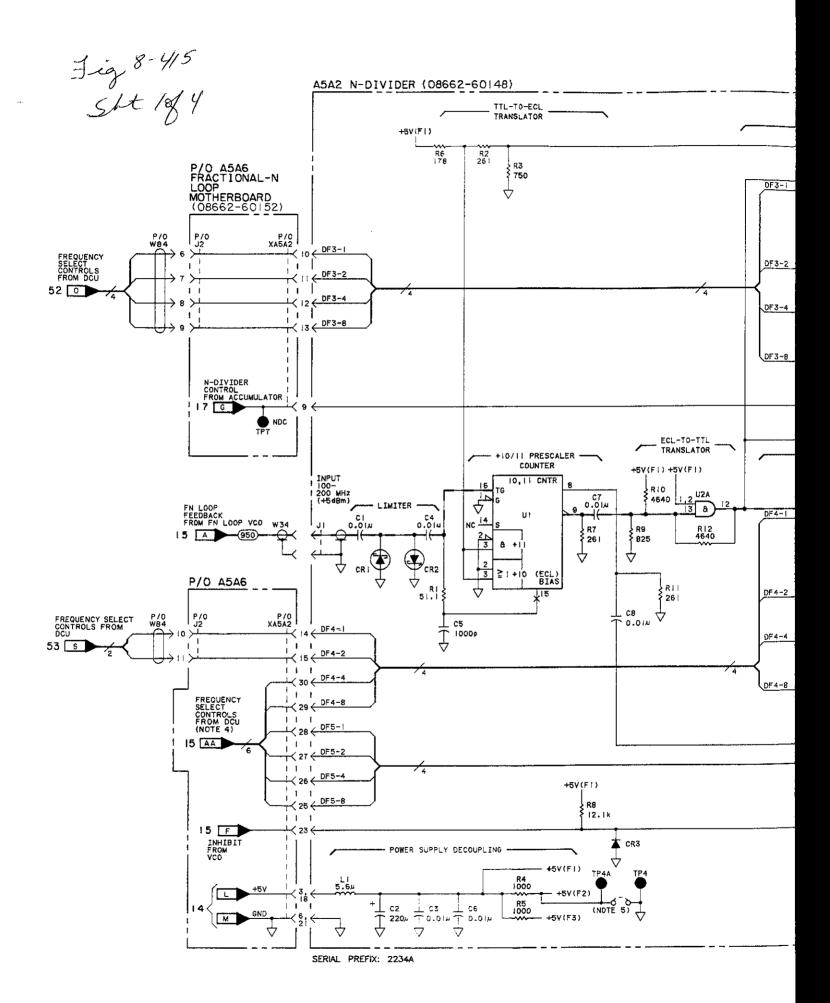

### SERVICE SHEET 16 A5A2 FRACTIONAL-N LOOP N-DIVIDER

REFERENCE BLOCK DIAGRAM 4

Table 4-1. Recommended Performance Tests

After Adjustments or Repairs

Table 5-2. Post-Repair Adjustment Procedures

### PRINCIPLES OF OPERATION

### General

The purpose of the N-Divider (A5A2) is to divide the Fractional N (FN) Loop VCO frequency (FN Loop N-Divider Drive) down to 100 kHz. The 100 kHz output signal, FN loop IF, is one input to the FN Loop's phase detector. The N-Divider consists of programmable digital dividers (counters) which divide down the VCO frequency. The N-Divider can divide by integers from 1001 through 2000. The frequency digits, DF3, DF4 and DF5, determine the divide-by-N number. In addition the divide by N number can be changed to N-1 by the N-Divider Control (NDC) signal from the Accumulator (A5A1).

Fractional division is accomplished by dividing by N for a number of times and then by N-1 for a number of times. The fractional N is then the average of N and N-1. The N-Divider can divide by a fractional part that has three significant places, for example, a fractional N of 1000.001.

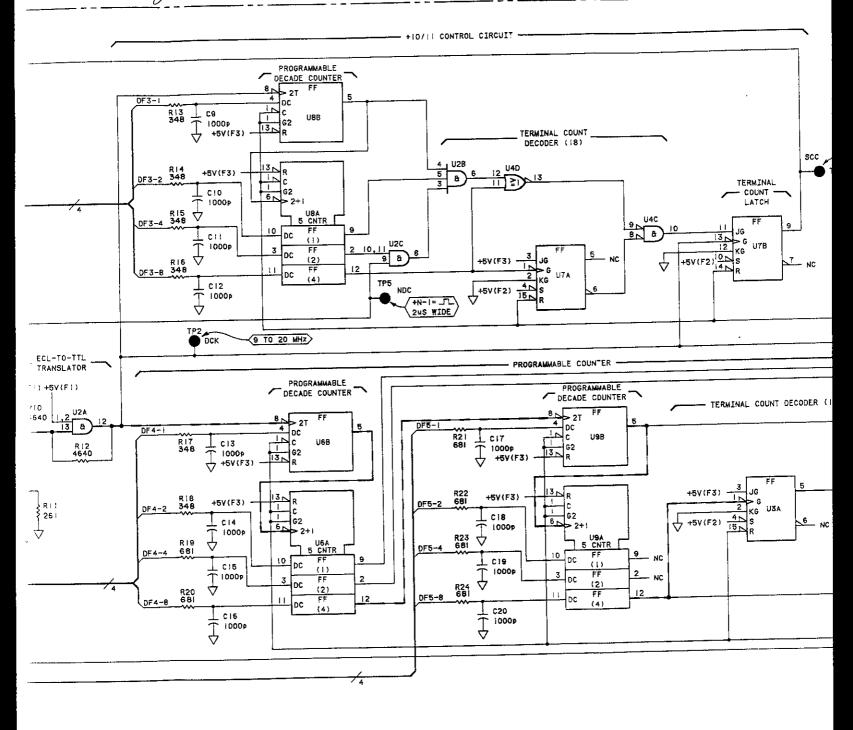

# Divide-by-10/11 Prescaler Counter

The divide-by-10/11 Prescaler Counter, U1, is an ECL device which can be programmed to divide by 11 or 10. At the beginning of each reference period the divide-by-10/11 Prescaler Counter divides by 11. It later starts dividing by 10 and remains in the divide-by-10 mode until the end of the reference period. How long it continues to divide by 11 is determined by the divide-by-10/11 Control Circuit. One output from the divide-by-10/11 Prescaler Counter, the Prescaled Oscillator signal (PSO), goes to the Accumulator (A5A1) where it is used as a clock. Note during the time when the Correction Pulses are generated this clock equals the VCO frequency divided by 10.

Service Model 8663A

# Divide-by-10/11 Control Circuit

The purpose of the divide-by-10/11 Control Circuit is to control the modulus (10 or 11) of U1. Frequency digit DF3 along with the NDC line determine how long U1 divides by 11 each reference period. Frequency digit DF3 presets the Programmable Decade Counter (U8) while the NDC line controls the terminal count of the Terminal Count Decoder (18). Normally the terminal count is 18 except when the NDC line goes high. When the NDC line goes high the terminal count changes from 18 to 17. Changing the terminal count of the Terminal Count Decoder (18) from 18 to 17 effectively causes the N-Divider to divide by N-1.

U8 starts to count up from its preset value to the terminal count. When counter U8 reaches the terminal count the Terminal Count Latch (U7B) is set and on the next clock the Terminal Count Latch output goes high. This causes counter U1 to start dividing by 10.

### Programmable Counters

The Programmable Counter counts all the pulses out of the divide-by-10/11 Prescaler Counter. Frequency digits DF4 and DF5 preset the Programmable Decade Counters U6 and U9 respectively. These counters count from the preset count to the count of 196. The count of 196 is determined by the Terminal Count Decoder (196). When the count reaches 196 the Terminal Count Switch is set up to change state on the next pulse from U1. The output from the Terminal Count Switch (U3B) is fed back to reset both the Programmable Counter and the divide-by-10/11 Control Circuit.

When the loop is phase-locked the output from the Terminal Count Switch is a 50 to 100 ns pulse with an average pulse repetition rate of 100 kHz.

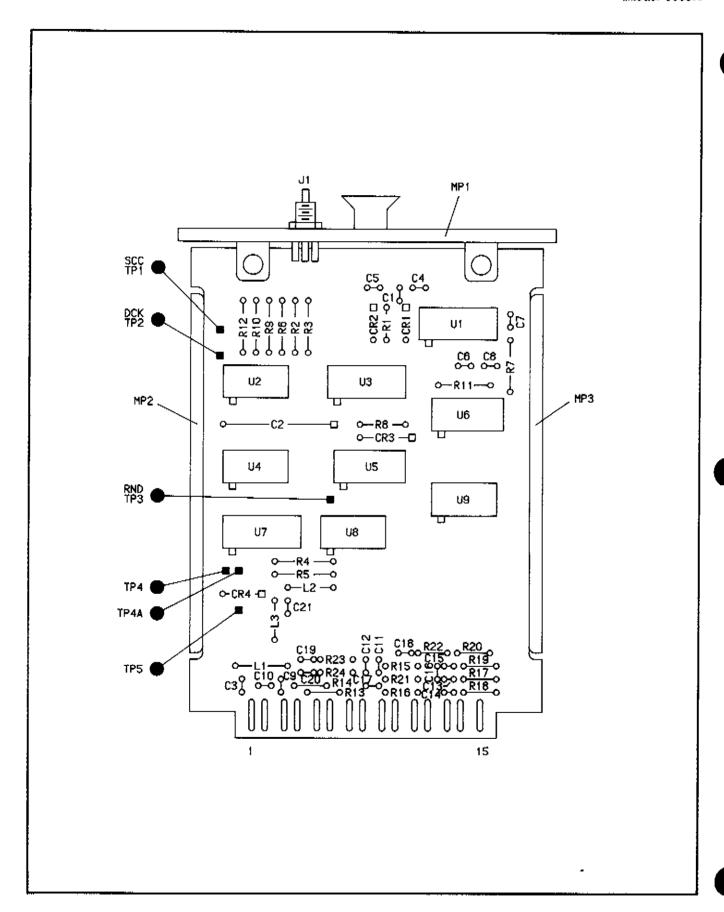

# TROUBLESHOOTING

When a Fractional-N Loop problem has been traced through the block diagram troubleshooting procedure to this assembly, use the following procedure to isolate the cause of the problem.

There are two types of procedures covered by this procedure.

- 1. No output pulses produced by A5A2 assembly. Begin troubleshooting with section I of the procedure.

- 2. Output pulses produced by A5A2 assembly are at the wrong frequency. Begin troubleshooting with section II of the procedure.

No output pulses.

1. Mount the A5A2 assembly on its extender board.

2. Use a logic probe and check for pulses at the outputs of U3B (pins 9 and 7). If pulses are present, the problem is between U3B and the edge connector. If no pulses are present, continue with step 3.

- 3. Check the output of U2A pin 12 (TP2). This signal should be a TTL pulse train. Check that the signal assumes valid high and low TTL logic levels. If this signal is not normal, the problem is in the prescaler (U1) or translator (U2A), or one of the counters (U6B, U8B, U3B) is pulling down the output of U2A. If this signal is normal, continue with step 4.

- 4. Connect a jumper between TP4 and TP4A which will allow counters U6 and U9 to free-run. Check that these counters are counting by touching a logic probe to the outputs. Flip-flop U3A should be set. The outputs of U5A (pin 12) and U5C (pin 8) should be normally low but go high when the counters reach the value they are decoding so a logic probe touched to these pins should blink.

If the counter circuitry is normal, the problem is with the terminal counter switch.

Output pulses of wrong frequency.

- 1. Mount the A5A2 assembly on its extender board.

- 2. Connect an extender cable from the service kit between A5A2J1 and A3A4J2. This cable routes the output of the LF N-loop to the input of the A5A2 N-divider assembly.

- 3. Set the 8663A front panel frequency to 327.8 MHz. This sets the LF N-loop output to 200.0 MHz.

- 4. Short test points TP4 and TP4A together. This holds flip-flop U7B in the set condition (TP1 high) which keeps counter U1 in the divide-by-10 mode. Measure the frequency at TP2 with the high impedance input of a frequency counter. The frequency should be exactly 20.0 MHz. If it is not, the problem is with flip-flop U7B, counter U1 or associated components.

- 5. Remove the short between TP4 and TP4A. Connect a jumper between TP3 and ground. This holds flip-flop U7B in the clear condition (TP1 low) which keeps counter U1 in the divide-by-11 mode. Measure the frequency at TP2. The frequency should be 18.181818 MHz (200 divided by 11). If it is not, the problem is with flip-flop U7B, counter U1 or associated components.

- 6. Remove the jumper from TP3. View the signal at TP1 on an oscilloscope. The waveform should be a TTL negative-going pulse approximately 1.1 microsec wide. Set the frequency increment to 100 Hz. Pushing the INCREMENT (up) key should decrease the pulse width in 55 microsec steps.

If there are no pulses on TP1, the problem could be the pulses coming from flip-flop U3B. Check TP3 for TTL negative going pulses (approximately 50 microseconds wide). The normal period

Service Model 8663A

of these pulses is approximately 10 microseconds, but any period greater than 1.5 microseconds should allow the pulses on TP1, described above, to be produced. If the TP3 pulses are not normal, continue troubleshooting with step 7.

7. Remove the jumper from TP3. Short test points TP4 and TP4A together which makes the output of U2A (pin 12) exactly 20.0 MHz and puts counters U6 and U9 into a free-run mode. The output of U6 (pin 12) should be a 2.0 MHz signal and the output of U9 (pin 12) should be a 200.0 kHz signal.

Figure 8-413. A5A2 Fractional-N Divider Block Diagrams

Figure 8-414. A5A2 Fractional-N Divider Component Locator

- 1. REFER TO TABLE 8-102 FOR SCHEMATIC DIAGRAM NOTES.

- 2. TROUBLESHOOTING VALUES ARE TYPICAL. THEY ARE ACTUAL MEASURED VALUES. YOUR MEASUREMENTS MAY BE SLIGHTLY DIFFERENT THAN WHAT IS SHOWN.

- 3, LOGIC LEYEL FOR ECL DEVICES IN THIS INSTRUMENT ARE NONSTANDARD DUE TO THE SUPPLY VOLTAGE USED. A HIGH LEVEL IS >+4.0; A LOW LEVEL IS <+3.5V.

- 4. MNEMONICS 0F3-; TO 0F5-8 REPRESENT THE FREQUENCY DIGITS ON THE FRONT PANEL AND THE BCD WEIGHTING.

- 5. JUMPER IS INSTALLED FOR TROUBLE-SHOOTING PURPOSES ONLY. INSTALLING JUMPER SETS FLIP-FLOPS UTA, UTB, U3A AND U3B

| REFERENCE | DESIGNATIONS |

|-----------|--------------|

| THE CITCHES | LOZUIM I ZUIIQ       |

|-------------|----------------------|

| NO PREFIX   | A5A6                 |

| ₩24<br>53   | J2<br>TP5,7<br>XA5A2 |

| A5A2        | 1 14542              |

| C1-21       | 1                    |

| CR1-4       |                      |

| L1-3        | 1 1                  |

| R1-24       | l i                  |

| TP!-5       |                      |

| U!-9        | ]                    |

| L      | LOGIC LEVELS |          |  |  |  |  |  |

|--------|--------------|----------|--|--|--|--|--|

|        | TTL.         | ECL      |  |  |  |  |  |

|        | ,            | (NOTE 3) |  |  |  |  |  |

| HIGH   | >+2V         | >+4.0V   |  |  |  |  |  |

| LOW    | <+0.8V       | <+3.5V   |  |  |  |  |  |

| < IS   | MORE NEG     | . THAN   |  |  |  |  |  |

| > IS   | MORE POS     | . THAN   |  |  |  |  |  |

| OPEN   | HIGH         | LOW      |  |  |  |  |  |

| GROUND | FOM          | HIGH     |  |  |  |  |  |

TRANSISTOR AND INTEGRATED

| CIRCUIT PART NUMBERS |           |  |  |  |  |  |

|----------------------|-----------|--|--|--|--|--|

| REFERENCE            | PART      |  |  |  |  |  |

| DESIGNATIONS         | NUMBERS   |  |  |  |  |  |

| VI I                 | 1820-1780 |  |  |  |  |  |

| U2,5                 | 1820-0686 |  |  |  |  |  |

| U3,7                 | 1820-0629 |  |  |  |  |  |

| U4                   | 1820-1322 |  |  |  |  |  |

| U6,8                 | 1820-2049 |  |  |  |  |  |

| U9                   | 1820-1251 |  |  |  |  |  |

### INTEGRATED CIRCUIT VOLTAGE AND GROUND CONNECTIONS

| GROUND CO                 | NNECTIONS      |

|---------------------------|----------------|

| REFERENCE<br>DESIGNATIONS | PIN<br>NUMBERS |

| UI                        | +5V(FI)-4,5    |

| U2,4-6,8,9                | +5V(F1)- 14    |

| U3,7                      | +5V(FI) - 16   |

|                           | <b>♦ - 8</b>   |

| A5  | A2 U2 | 4-6,     | CIR          | CUIT<br>ARD | A5  | A2 UI,3, | CIRC | CUIT |

|-----|-------|----------|--------------|-------------|-----|----------|------|------|

| TO  | P VIE | W        | TOP          | VIEW        | TOP | VIEW     |      | VIEW |

| ıď  | •U    | 14       | ΙØ           | 0.14        | 140 | ) j 16   | ıμ   | 0.16 |

| □   |       | KE.      | <b>1 1</b> 0 | ٥           | ₽   | j⊒ KE    | Y 10 | o    |

| d   |       | Þ        | 0            | 0           | □   | Þ        | 0    | Q    |

| d   |       | <b>5</b> | 0            | ٥           | ₫   | Þ        | 0    | ٥    |

| d   |       | <b>b</b> | 0            | 0           | ₫   | Þ        | 0    | 0    |

| ᆸ   |       | <b>3</b> | 0            | 0           | d   | Þ        | 0    | ٥    |

| 7 d |       | 38       | 70           | 0.8         | ₫   | Þ        | 0    | ٥    |

| L.  |       | ı        |              |             | 8 🗆 | Þ9       | 80   | 09   |

Fig 8-415 Sht 40/4

# SERVICE SHEET A5A2 16

Figure 8-415. A5A2 Fractional-N Divider Schematic

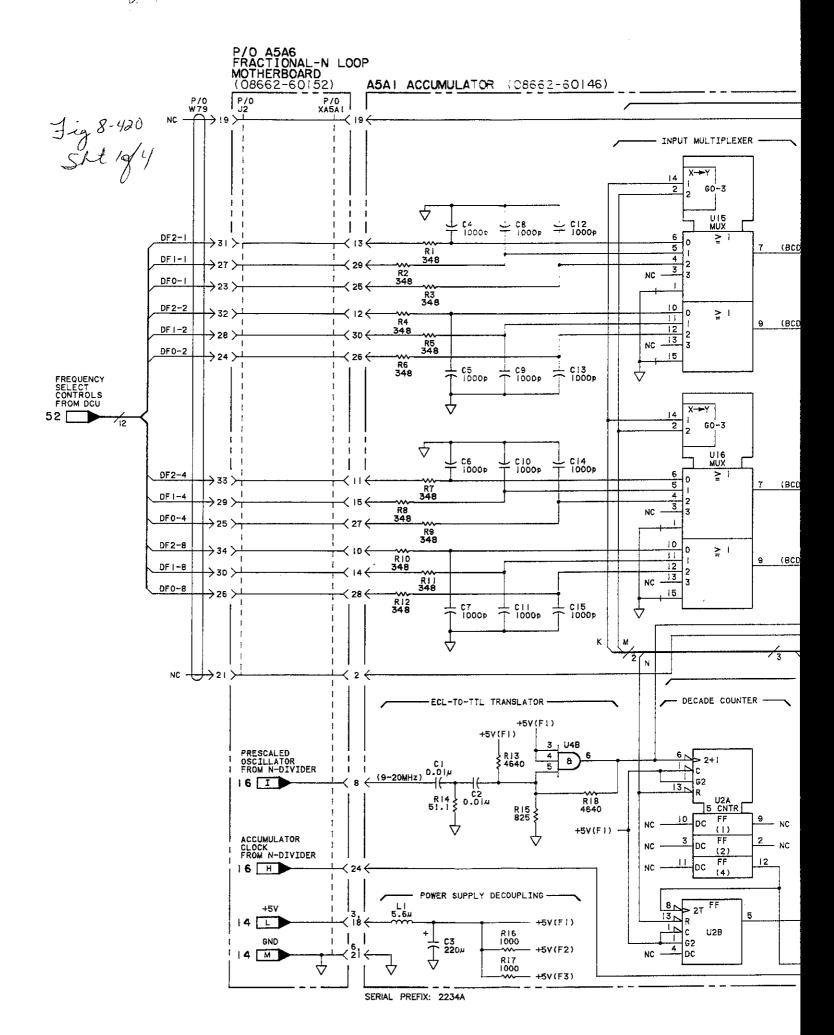

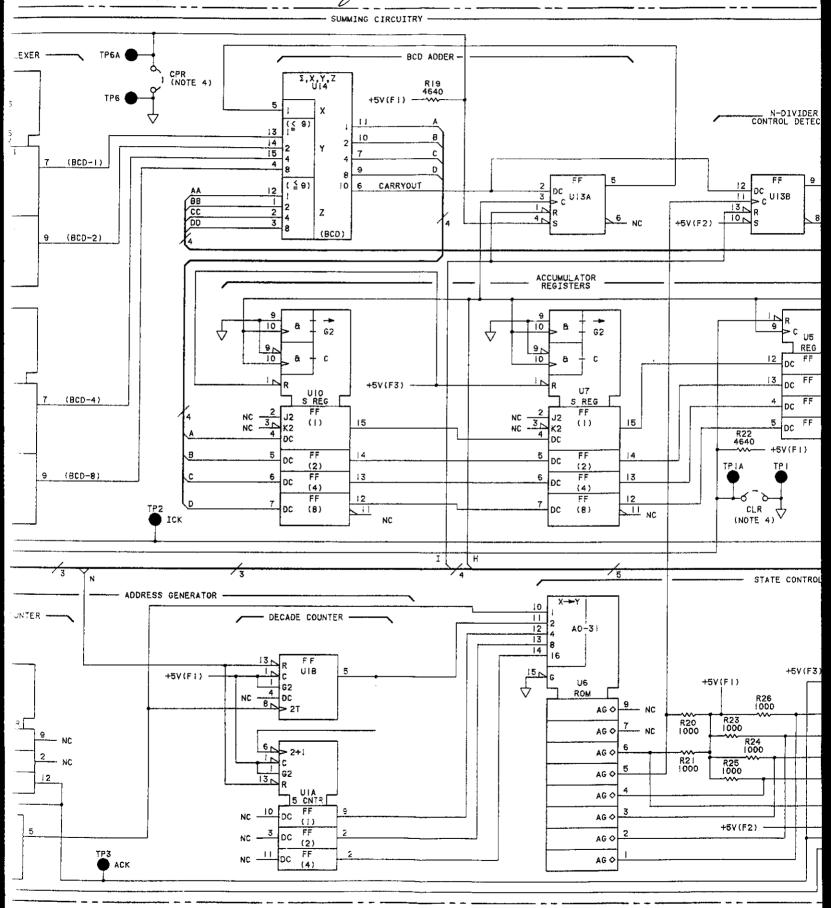

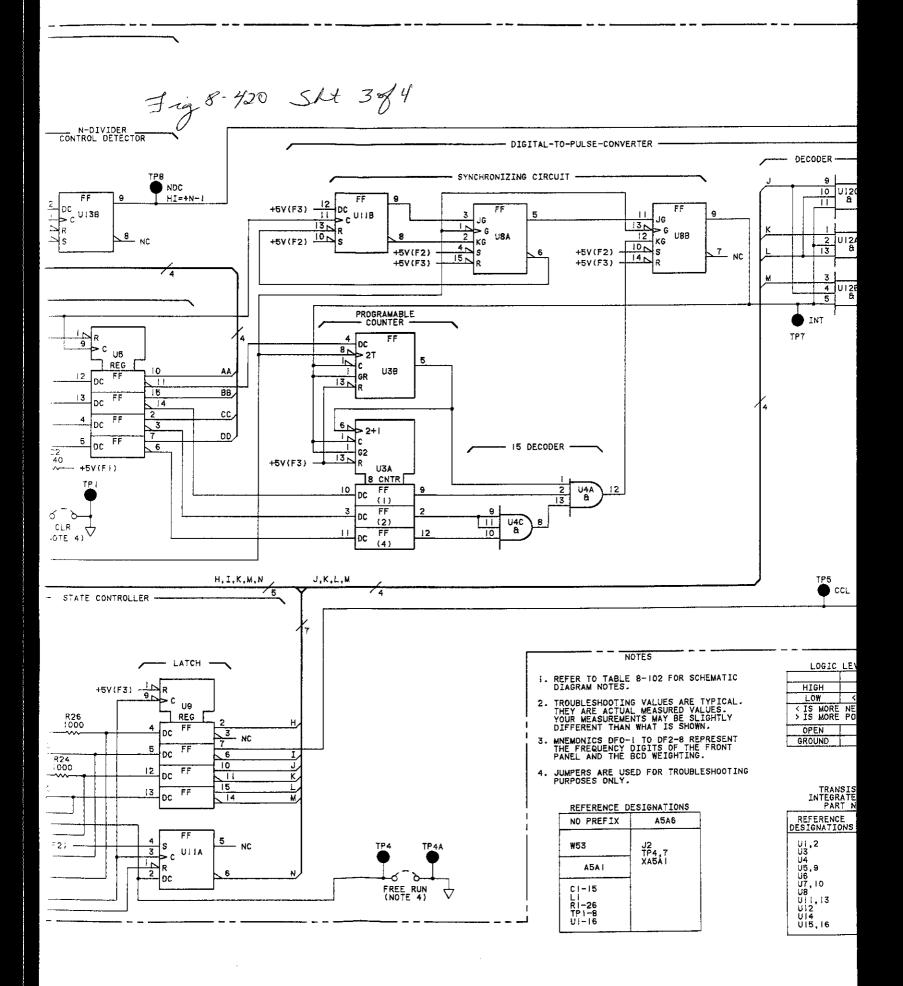

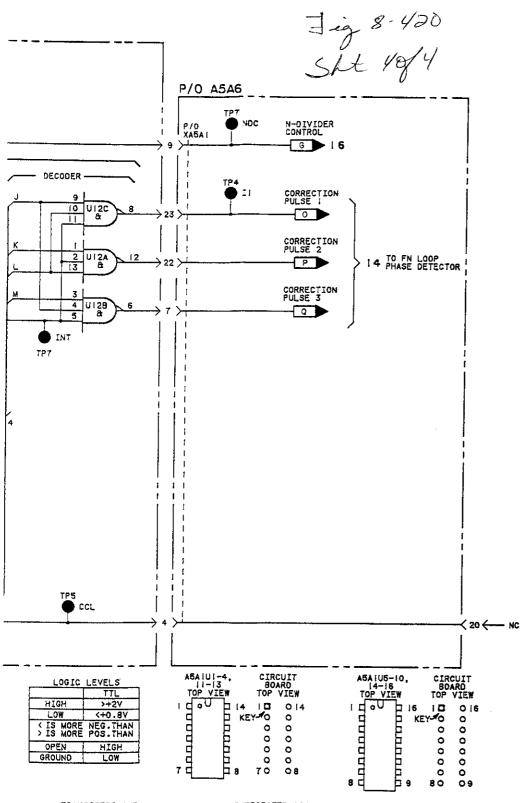

SERVICE SHEET 17 A5A1 FRACTIONAL-N LOOP ACCUMULATOR

REFERENCE BLOCK DIAGRAM 4

Table 4-1. Recommended Performance Tests After Adjustments or Repairs.

Table 5-2. Post-Repair Adjustment Procedures.

#### PRINCIPLES OF OPERATION

#### General

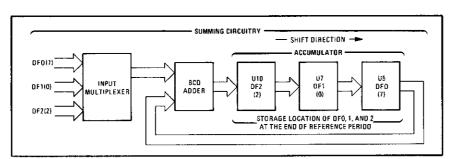

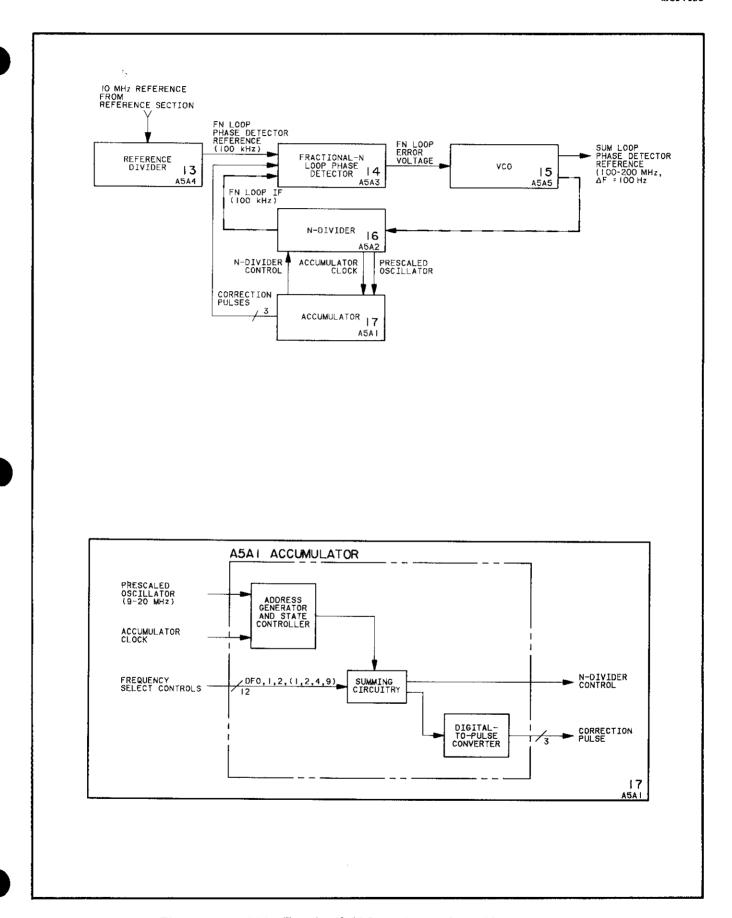

The purpose of the Accumulator (A5A1) is to determine when to divide by N or divide by N-1. The Accumulator computes the phase difference between the VCO/N (FN Loop IF) and the 100 kHz reference (FN Loop Reference). This information is used to develop the N Divider Control signal (NDC) and the Correction Pulses. The Accumulator consists of three major sections which are the Algorithmic State Machine, Summing Circuitry, and the Digital to Pulse Converter.

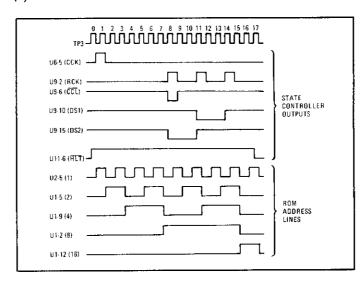

#### Algorithmic State Machine

The Address Generator along with the State Controller form a small Algorithmic State Machine (ASM). The ASM generates a set of control signals or instructions which properly sequences the Summing Circuitry and the Digital to Pulse Converter. The control signals or instructions are determined by the program stored in ROM (U6).

The ASM generates a total of seventeen instructions. The seventeenth instruction is a halt command which resets and disables the Address Generator (U1 and U2). The ASM remains in the halt state until the end of a reference period. A clock pulse, labeled Accumulator Clock, is generated at the end of each reference period. This pulse restarts the Address Generator and the whole sequence is repeated again.

#### Summing Circuitry

The fractional portion of the VCO frequency contains the information needed to develop the N Divider Control (NDC) and the Correction pulses. The fractional portion of the VCO frequency is entered into the Accumulator in BCD form (DFO through DF2). These BCD lines, DFO through DF2, carry information which corresponds to the front panel frequency digits DO through D2. The Summing Circuitry takes the BCD data, adds it to the previous sum, and stores it in the Accumulator Registers (U19, U7, and U5). Each reference period the content of the Accumulator Registers is incremented by the fractional portion. The number stored in the Accumulator Registers corresponds to the difference in phase between the VCO signal and the reference signal. When the accumulated total reaches or exceeds unity an NDC signal is generated.

To better understand the operation of the Summing Circuit, let's go through an example. When analyzing the operating of the Summing Circuitry it is better to view it in terms of reference periods. Let's assume that the Accumulator Registers initially contains the number zero and the fractional portion equals the number 207, that is, DF0=7, DF1=0, and DF2=2. At the beginning of the reference period the Input Multiplexer selects the four BCD lines which corresponds to the DFO and steers the BCD data to the BCD Adder. BCD Adder adds the DFO number (7) to the number stored in U5. U5 contains the number zero, the resulting sum is just the number The sum is then latched into U10. At the same time the previous content stored in U10 is shifted into U7 while the previous content of U7 is shifted into U5 (shift right). This sequence is then repeated for both DF1 and DF2, respectively. Figure 8-416 shows the content of the Accumulator Registers after the end of one reference period. Note at the end of the reference period. DFO is stored in U5, DF1 is stored in U7, and DF2 is stored in U10.

Figure 8-416. Summing Circuitry Simplified Block

Diagram Showing the

Content of the Accumulator after each Reference Period

At the beginning of the next reference period DFO is again selected first and steered to the BCD Adder. DFO is added to the content stored in U5 which now contains the result of the previous addition of DFO. Again this sequence is repeated for DF1 and DF2. The net result is that the content of the Accumulator Registers is incremented by the fractional portion every reference period. Table 8-401 illustrates this point.

the three outputs. The order in which the pulses are outputed is Correction Pulse 3, Correction Pulse 2, and Correction Pulse 1.

The Programmable Counter along with the 15 Decoder determines the pulse width (negative going) of each Correction Pulse. The 15 Decoder circuit causes the counter to reset when it reaches the count of 15. The Programmable Counter is preset by the complemented of the BCD number stored in register U5. The Program Counter is clocked by the Prescaled Oscillator (PSO) signal. During the interval when the Correction Pulses are being developed, the PSO frequency equals the FN Loop VCO frequency divided by ten. The time it takes for the Program Counter to count from its preset value to 15 determines the pulse width. The pulse width can be calculated by the following formula:

Pulse Width = 10 x (number in U5 +1) x VCO Cycle Wide

For example if U5 contains the number 0, a 10 VCO cycle wide pulse is generated. If U5 contains the number 9, a 100 VCO cycle wide pulse is generated. Note if the FN Loop operates with no fractional part, the pulse width of the Correction Pulses remains constant from reference period to reference period. However, if the loop is operating with a fractional part, the Correction Pulses will vary in duration every reference period. Also note, the pulse duration will be the longest when the phase difference is at its maximum value.

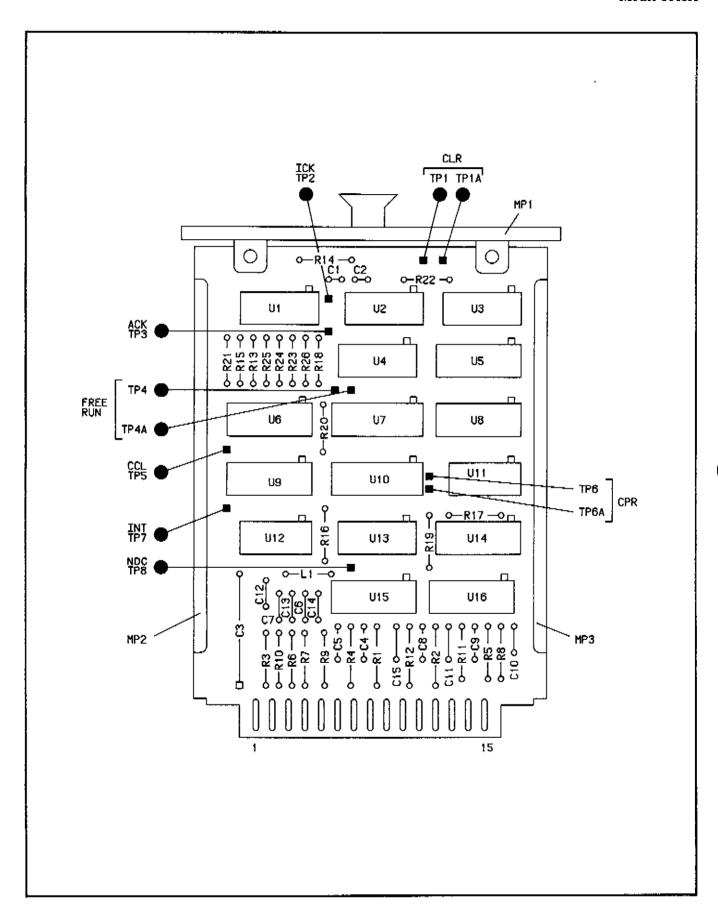

#### TROUBLESHOOTING

When a Fractional-N Loop problem has been traced through the block diagram troubleshooting procedure to this assembly, use the following procedure to isolate the cause of the problem. Signature analysis is used to troubleshoot this assembly. The normal operation of the A4A1 assembly provides the stimulus needed to drive the HP 5004A Signature Analyzer. Any special set-up requirements are listed under the signature tables.

#### Set-up

- 1. Mount the A5A1 assembly on an extender board from the service kit.

- 2. Set the Signature Analyzer switches as follows:

| нр 5004А                        | Pushbuttons |

|---------------------------------|-------------|

| START STOP CLOCK HOLD SELF TEST | _/ (OUT)    |

3. Connect the Signature Analyzer to the A5A1 assembly as follows:

| HP 5004A | A5A1 Assembly |

|----------|---------------|

| STOP     | U11 pin 6     |

| START    | U11 pin 6     |

| CLOCK    | U2 pin 6      |

| GND      | TP4A          |

4. Run a cable from the Signal Generator rear panel 10 MHz reference output to the A5A2J1 connector.

#### Initialization

- 1. Set frequency to 320.0 MHz.

- 2. Short TP1 and TP1A. Remove any other jumpers connected to these test points.

- 3. Remove short and connect jumper from U11 pin 6 to TP1A.

- 4. Set frequency to test value.

#### Test Procedure

1. Touch the SA probe to +5V on the A5A1 assembly.

#### signature: OHA5

If this signature is correct, the set-up is correct so continue troubleshooting with step 2. Otherwise, there is a problem with the set-up or the state controller circuitry on A5A1. SA cannot be used until the +5V signature is correct. Troubleshoot the state controller using the information in the timing diagram (Figure 8-417).

Figure 8-417. State Controller Timing Diagram

2. Check the state controller by verifying the signature at the output of U9. Correct signatures are shown in the signature tables.

If these signatures are correct, continue troubleshooting with step 3. Otherwise, there is a problem in the state controller so check the signatures at U9 (input), U6 and U1 to isolate the cause of the problem.

3. Set the 8663A front panel frequency to 320.0999596 MHz. Short TP1 and TP1A together. Check the signatures at the output of U7 and U10. Correct signatures are shown in the signature tables.

If these signatures are correct, continue troubleshooting with step 4. Otherwise, there is a problem in the summing circuitry so check the signatures at U14, U15 and U16 to isolate the cause of the problem.

4. Perform the initialization procedure for checking U5 specified in the signature table. Check signatures at frequency settings of 320.099960 and 320.099990 MHz. The initialization procedure must be performed each time the frequency setting is changed.

If these signatures are not correct, U5 is the likely cause. Otherwise, the problem is in one of the circuit elements that cannot be checked by signature analysis. Those elements not checked by this procedure are:

| U13A | u8a | U12A |

|------|-----|------|

| U13B | u8B | U12B |

| U11B | U3A | U12C |

|      | USB |      |

5. Set the 8663A front panel frequency to 320.0999596 MHz. This causes all the circuitry on the A5A1 assembly to be active and a logic probe or oscilloscope can be used to check proper circuit operation.

Accumulator (A5A1) Signatures

| U1-   | 123456789                                       | C2C5<br><br>1182<br><br>3409                                     | **U5- | 9<br>10<br>11<br>12<br>13<br>14<br>15           | 2P86<br>7U39<br>729F<br>C16H<br>0000<br>OHA5<br>0000 | <b>U9-</b> | 1 2 3 4 5 6 7 8 9                           | 2P8C<br>P8C9<br>A6H3<br>77F8<br>7A6H         | <b>U14</b> - | 7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 | CFF8<br><br>C16H<br>P560<br>P8F5<br>0000<br>P8F5<br>P560<br>CFF8 |

|-------|-------------------------------------------------|------------------------------------------------------------------|-------|-------------------------------------------------|------------------------------------------------------|------------|---------------------------------------------|----------------------------------------------|--------------|-------------------------------------------------|------------------------------------------------------------------|

|       | 10<br>11<br>12<br>13<br>14                      | 01UF                                                             | U6-   | 2<br>3<br>4<br>5<br>6                           | P8C9<br>A6H3<br>1C79<br>5CA9<br>2C5F<br>000U         |            | 10<br>11<br>12<br>13<br>14<br>15<br>16      | CFF8<br>C16H<br>1C79<br>5CA9<br>P560<br>P8F5 | V15-         | 16<br>1<br>2<br>3<br>4<br>5<br>6                | P560                                                             |

| *U5-  | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | 7U39<br>729F<br>C16H<br>0000<br>OHA5<br>0000<br><br>2P86<br>0000 |       | 7<br>8<br>9<br>10<br>11<br>12<br>13<br>14       | 21H4<br>1182<br>3409<br>C2C5<br>01UF                 | U10-       | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8        | P8F5<br>P560<br>CFF8<br>C16H                 |              | 56789112314                                     | OHA5<br>P8F5<br><br>P560<br>0000<br>OHA5<br>                     |

| **U5- | 11<br>12<br>13<br>14<br>15<br>16                | OHA5<br>0000<br>C16H<br>729F<br>7U39                             | U7 -  | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | <br>CFF8<br>C16H<br>540H<br>59A8                     |            | 9<br>10<br>11<br>12<br>13<br>14<br>15<br>16 | 2P8C<br><br>59A8<br>540H<br>C16H<br>CFF8     | U16-         | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8            | P560<br>OHA5<br>OOO<br>OHA5                                      |

|       | 23456 <b>78</b>                                 | 0000<br>0HA5<br>0000<br>C16H<br>729F<br>7U39                     |       | 10<br>11<br>12<br>13<br>14<br>15<br>16          | 2P8C<br><br>P560<br>P8F5<br>59A8<br>540H             | U14-       | 1<br>2<br>3<br>4<br>5<br>6                  | 0000<br>0000<br>0000<br>C16H                 |              | 8<br>9<br>10<br>11<br>12<br>13<br>14            | C16H<br>0000<br>0HA5<br>0000                                     |

<sup>\*</sup> Test Frequency 320.09996 MHz \*\* Test Frequency 320.09999 MHz

Figure 8-418. A5A1 Fractional-N Loop Accumulator Block Diagrams

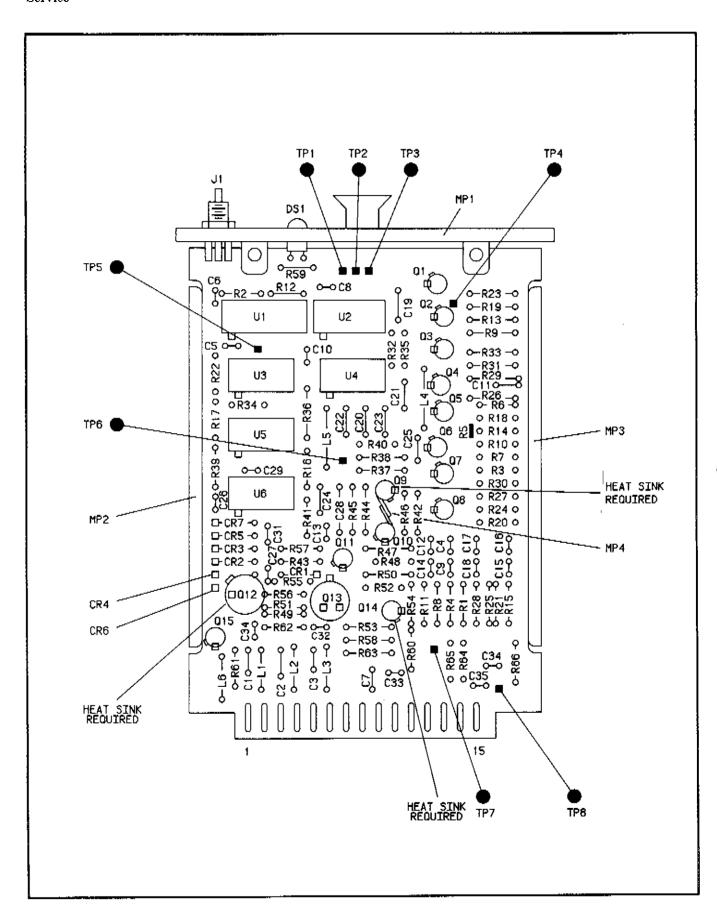

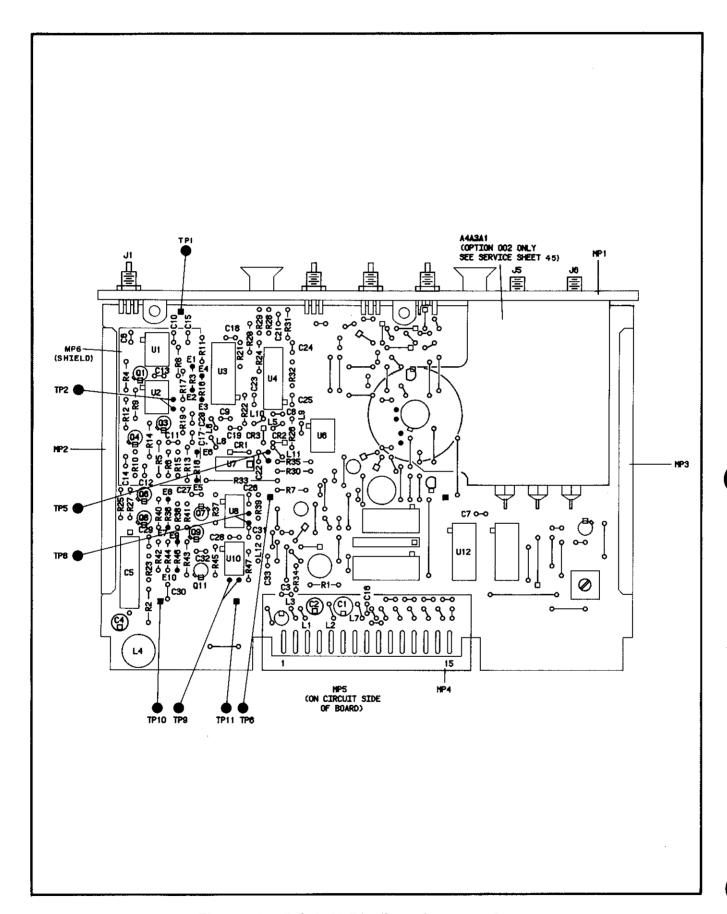

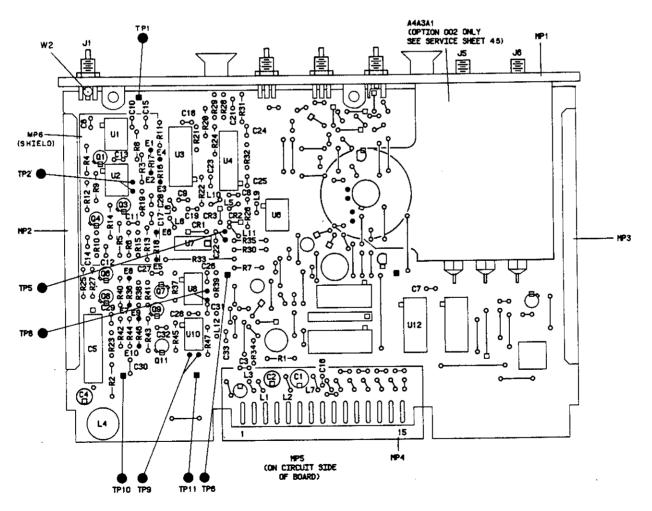

Figure 8-419. A5A1Fractional-N Loop Accumulator Component Locator

TRANSISTOR AND INTEGRATED CIRCUIT PART NUMBERS

| REFERENCE<br>OESIGNATIONS                                                        | PART<br>NUMBERS                                                                                                               |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 01,2<br>03<br>04<br>05,9<br>06,0<br>07,0<br>08<br>011,13<br>012<br>012<br>015,16 | 1820-1251<br>1820-193<br>1820-0686<br>1820-195<br>08662-80002<br>1820-1300<br>1820-0629<br>1820-112<br>1820-1777<br>1820-1244 |

INTEGRATED CIRCUIT

VOLTAGE AND

GROUND CONNECTIONS

| 01100110 99               | MACC: TOMS     |

|---------------------------|----------------|

| REFERENCE<br>DESIGNATIONS | PIN<br>NUMBERS |

| UI-4,11-13                | +5V(F1)- 14    |

| U5-10,14-16               | +5V(F1)- [6    |

# SERVICE SHEET A5A1

Figure 8-420. A5A1 Fractional-N Loop Accumulator Schematic

8-443/444

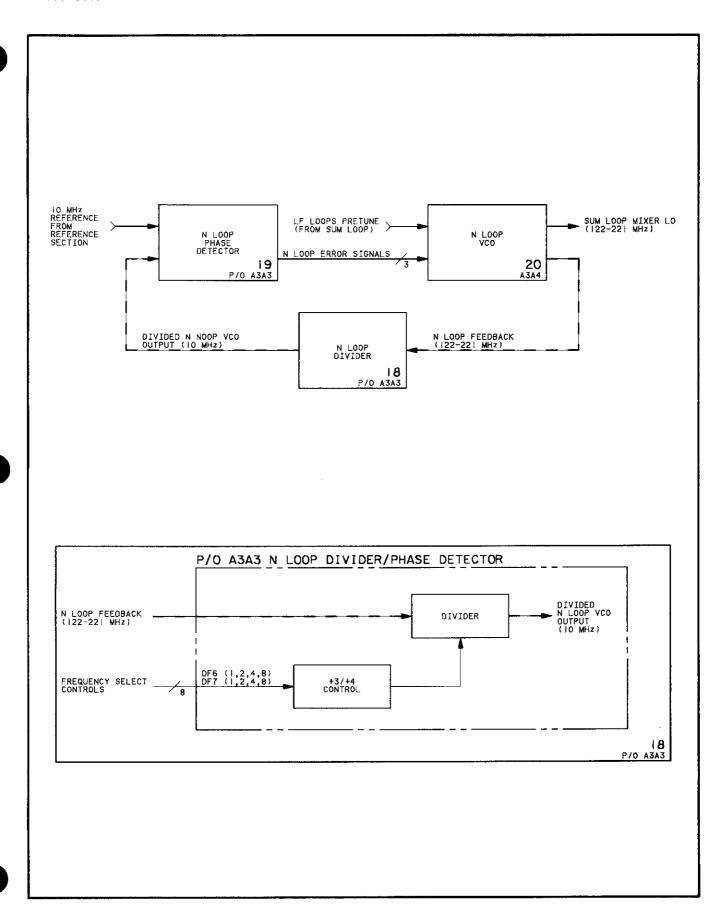

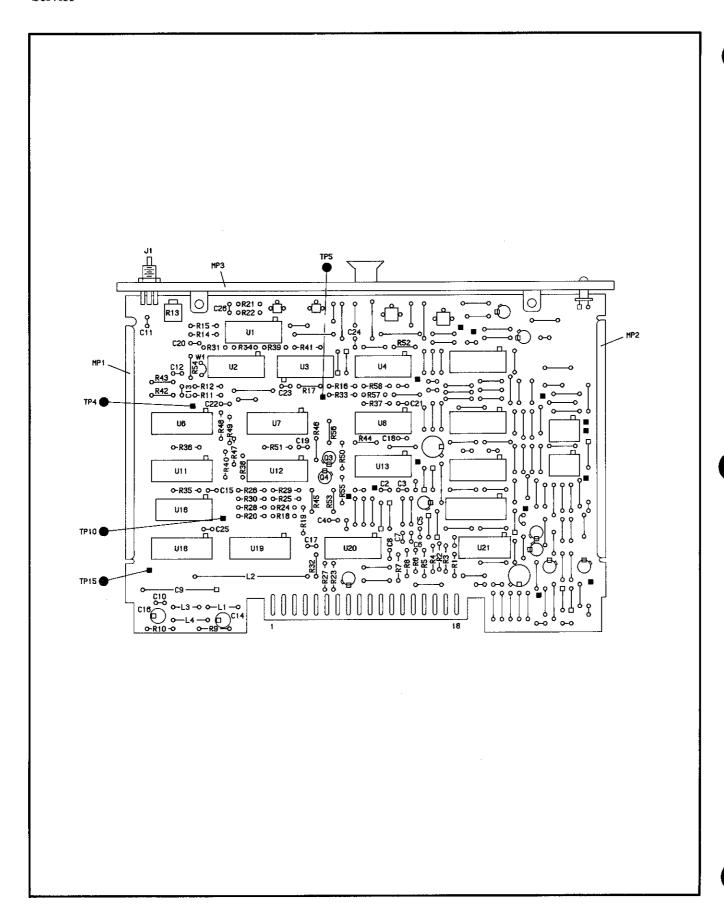

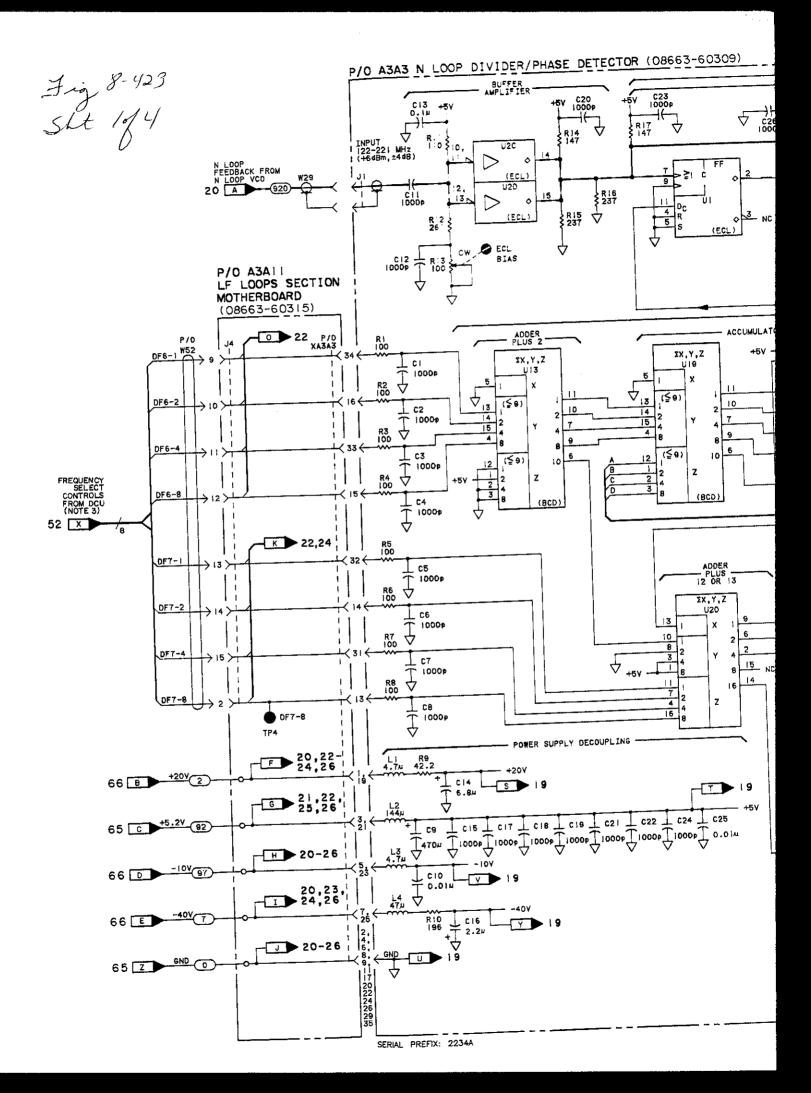

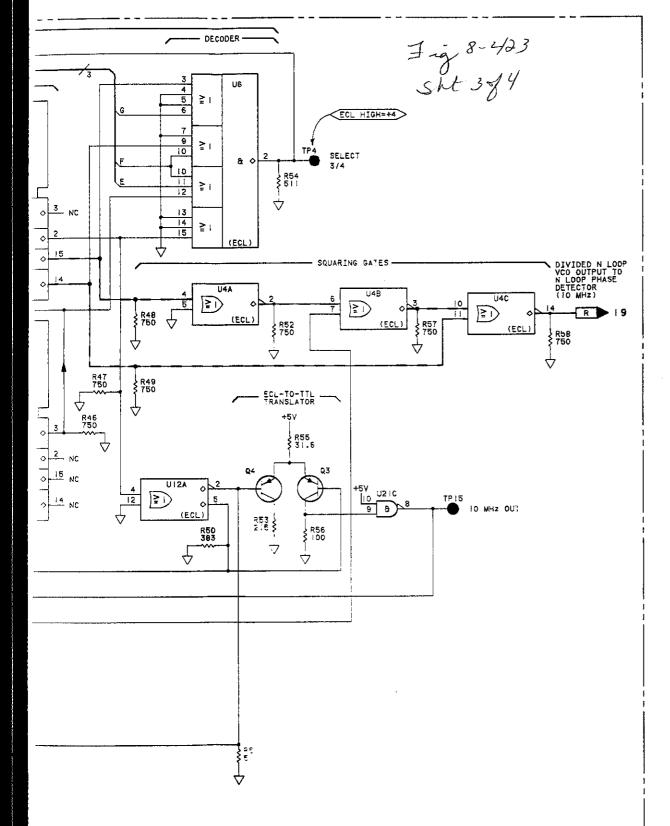

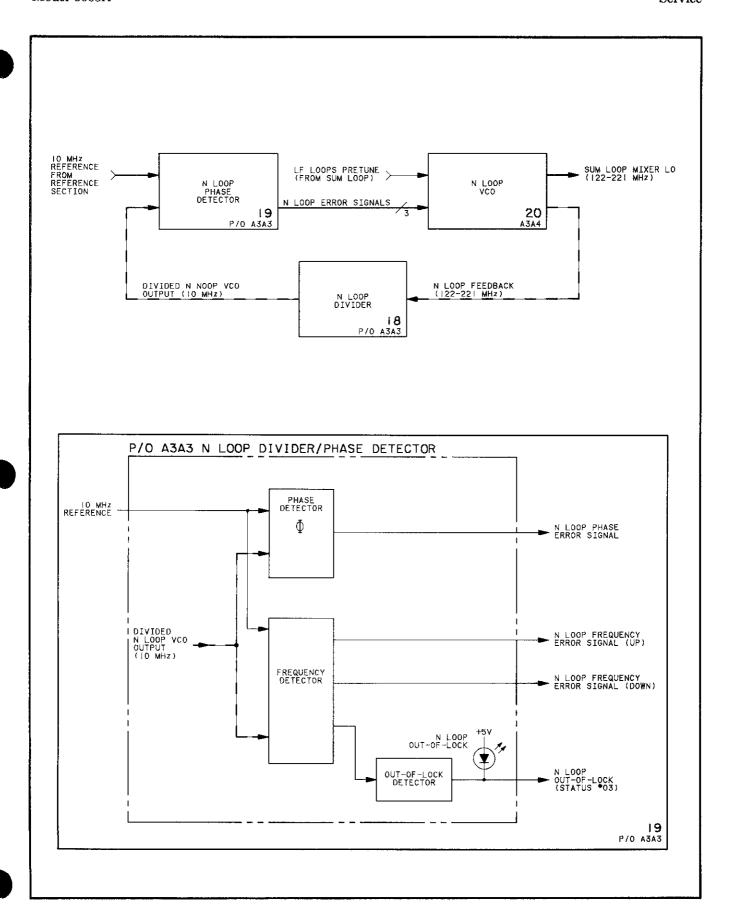

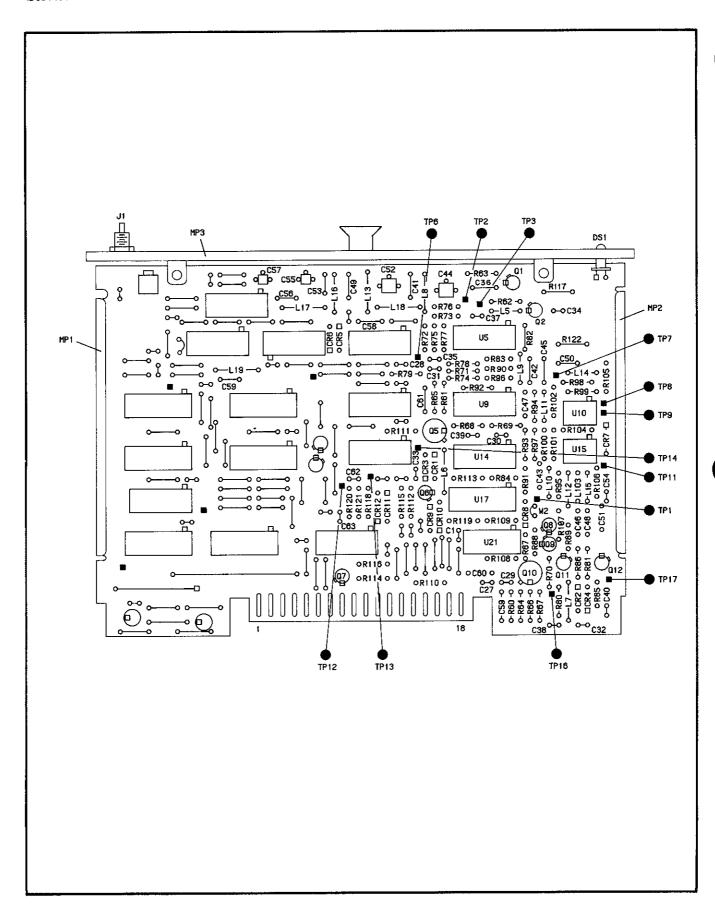

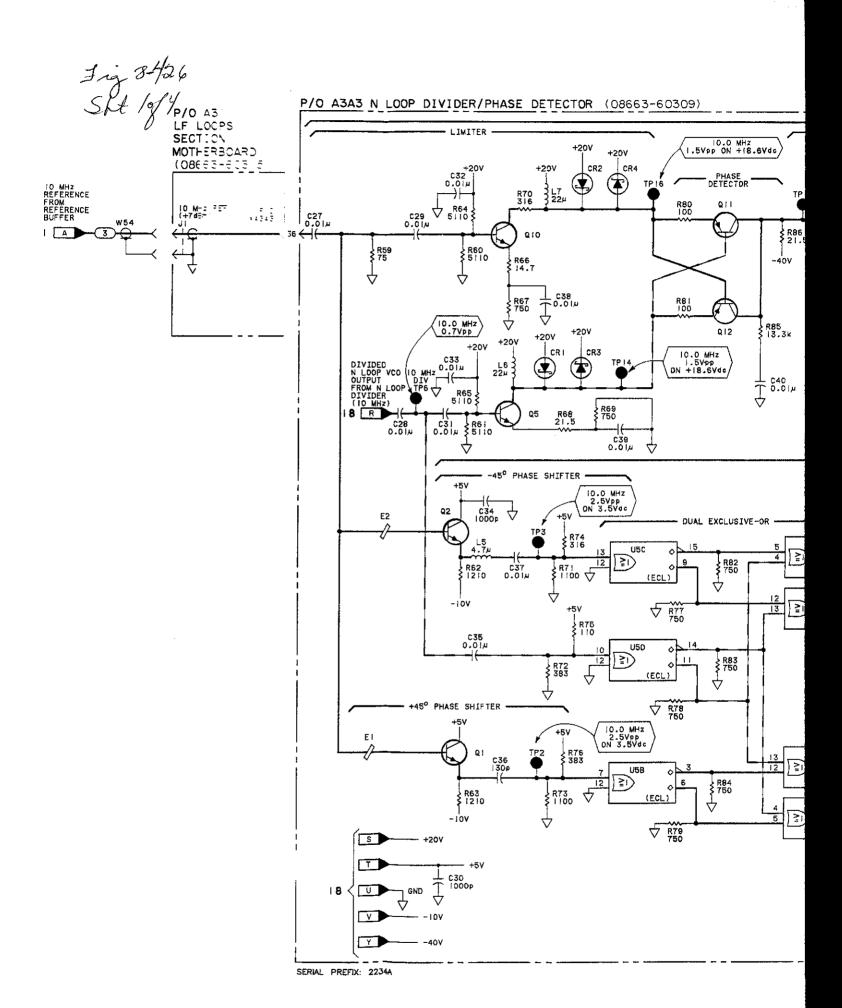

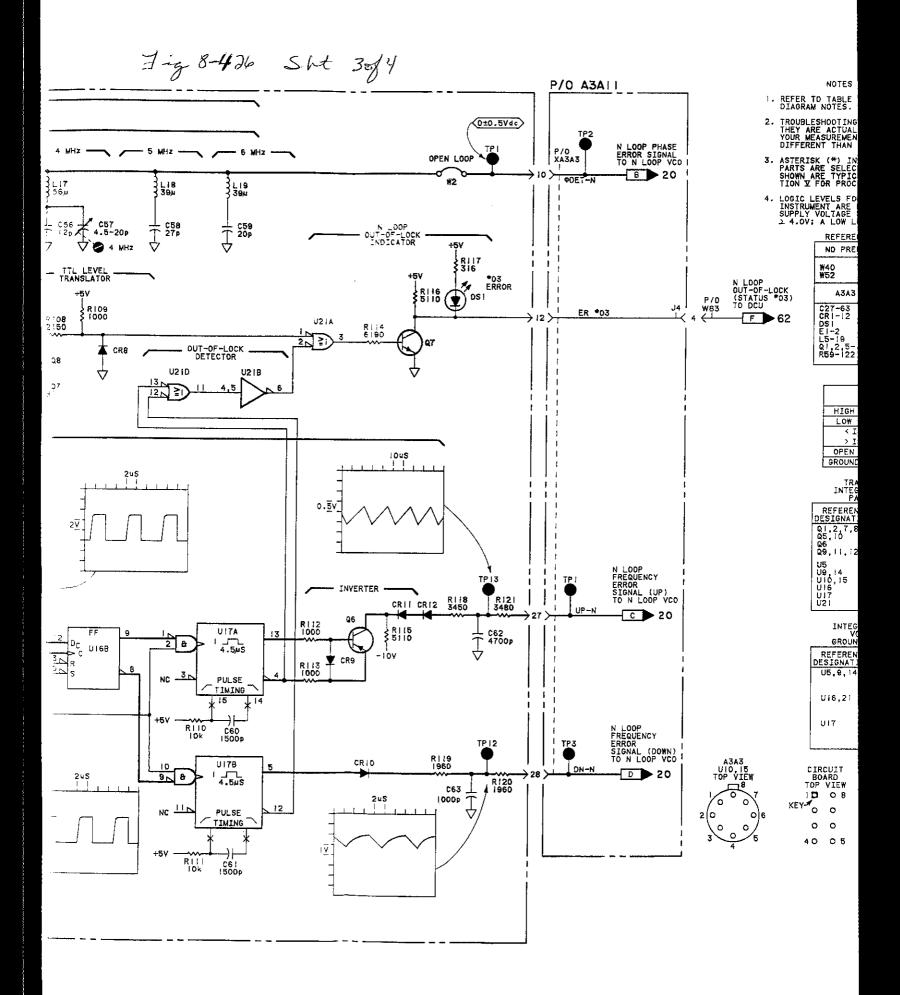

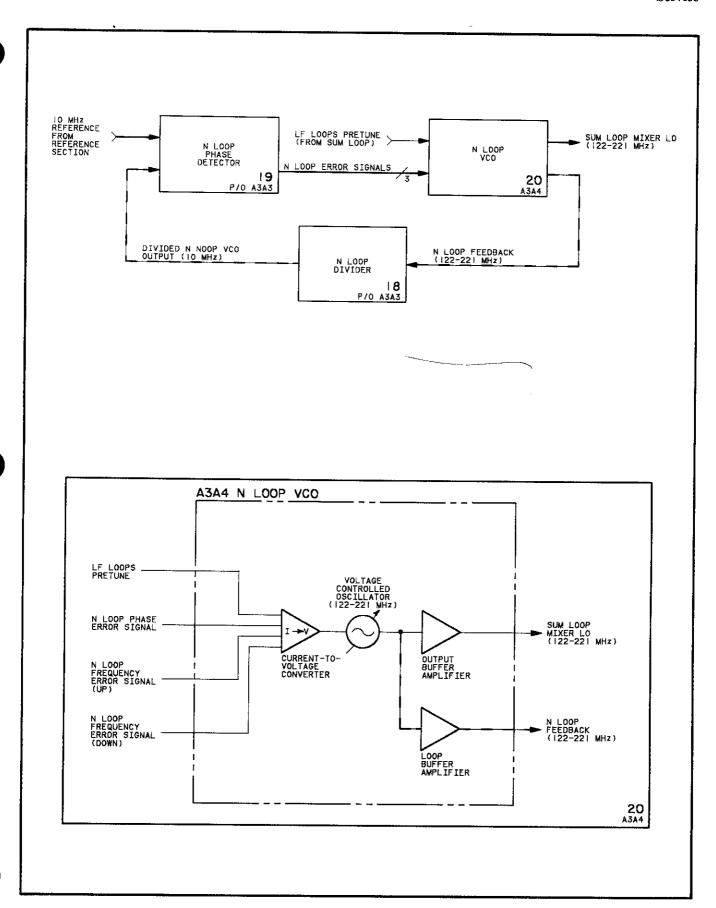

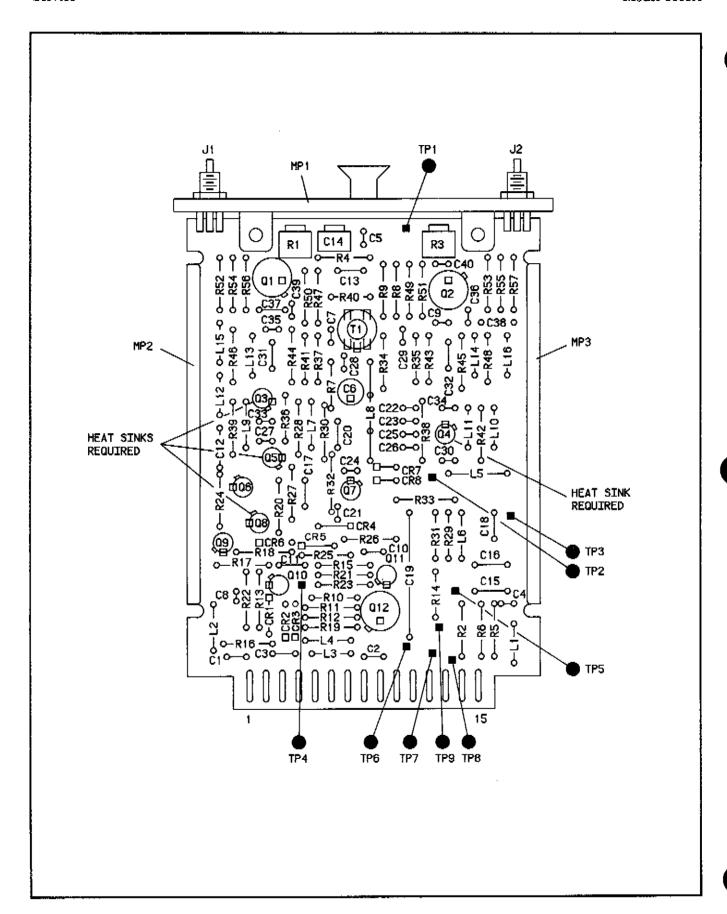

SERVICE SHEET 18 P/O A3A3 N LOOP DIVIDER/PHASE DETECTOR

#### REFERENCE BLOCK DIAGRAM 5

Table 4-1. Recommended Performance Tests After Adjustments or Repairs.

Tabel 5-2. Post-Repair Adjustment Procedures.

#### PRINCIPLES OF OPERATION

#### General

This portion of the N Loop Divider/Phase Detector Assembly contains the N loop programmable divider circuitry. The output (which goes to service sheet 19) is the 10 MHz phase detector variable (VCO frequency divided by N). The inputs consist of the N loop divider drive from the N Loop VCO Assembly (service sheet 20) and the frequency select controls from the Digital Control Unit.

The circuitry on this service sheet takes the 122 MHz to 221 MHz N loop divider drive from the VCO (service sheet 20) and divides it down to 10 MHz by means of the programmable N loop divider. In order to produce the 10 MHz output, the divider circuitry must be capable of dividing the 122 MHz to 221 MHz input by 12.1 to 22.1 in one-tenth of a unit steps.

In order to fractionally divide between 12 and 23, fractional-N circuitry is utilized. The fractional-N divider employs a unique method for generating fractional division. Control circuitry causes the input frequency to be divided by one number for a measured number of cycles and then by another number for a second period of cycles. These two count cycles, when averaged over a period of time, result in a fractional divide count.

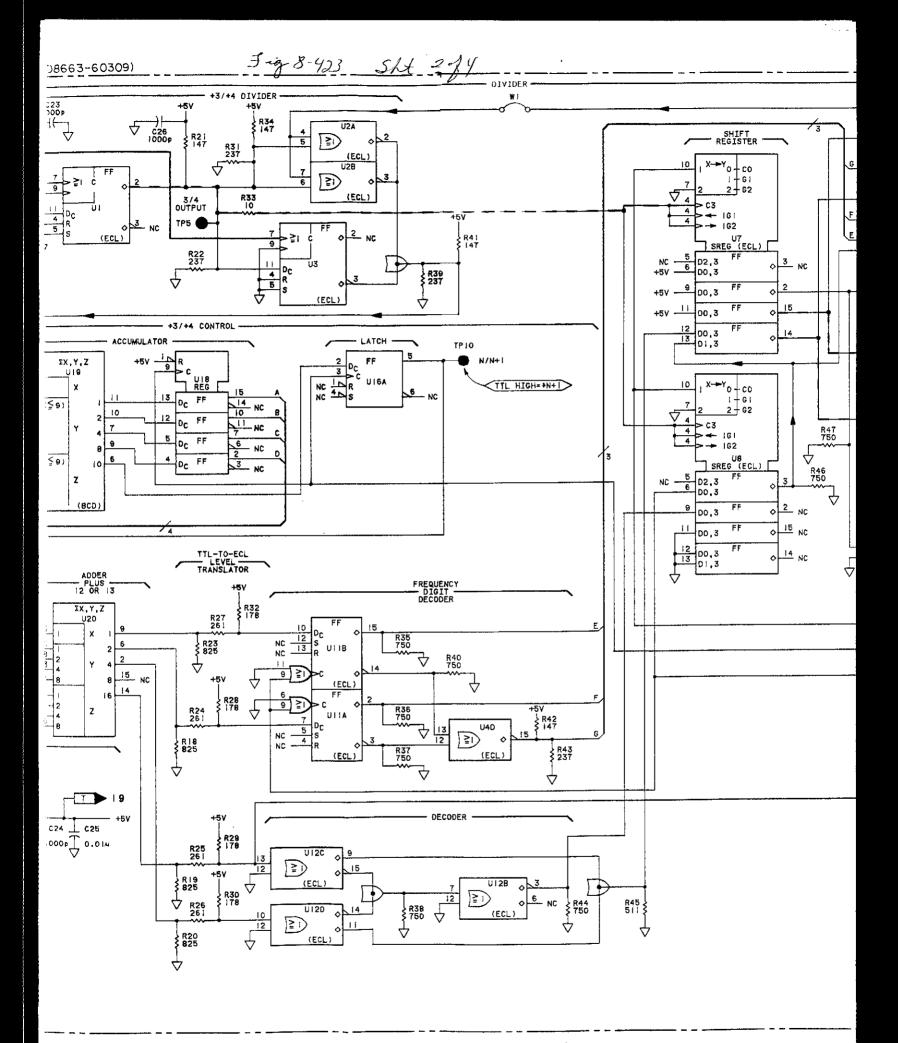

#### Divider Circuitry

The divide by 12 to 23 circuitry is composed of U1-U8 and U12. U1, U2, and U3 make up a divide by 3, divide by 4 circuit. The control circuitry looks at the output of this section and switches back and forth between the two divide modes in order to produce divide values between 12 and 23. For example, suppose a divide value of 17 is desired. The circuit divides by four, two times, and then by three, three times. Thus, for every 17 input pulses, one pulse is produced at the output of U12A.

#### Control Circuitry (For Fractional-N)

U13, U16, U18, U19, and U20 are the fractional-N control circuits. U13-U19 vary the control signal (TP10) to U20 so that fractional division can be accomplished. U13 adds two to the input. U18 and U19 form the accumulator circuit (U18 is a latch; U19 is an adder). The adder's outputs are at pins 6, 7, 9, 10, and 11. Each time there

is an output from the divider (pin 8 of U21), the count sum is added to the least significant digit programmed. Whenever a carry occurs, the divider is triggered to divide by a number that is one greater. In other words, the control circuitry tells the divide by 12 to 23 section when to shift up by one divide number to achieve fractional division.

For example, to obtain a divide by 12.1 value, the divide by 12 to 23 circuit must divide by 12 for 9 divider output cycles and then by 13 for 1 divider output cycle. The U16A output at pin 5 goes to pin 13 of U20. This is the N/N+1 line. It tells the divider whether it should divide by N or N+1. When the line is HI, the circuit is dividing by N+1, when it is LO, the circuit is dividing by N. (See Fractional-N Loops Section for a more detailed description of howFractional-N works.)

#### Shift Register and Decoder Circuitry

The shift register and decoder circuitry in the divider section is composed of U6, U7, and U8. U6 generates the appropriate output to control the divide by 3, divide by 4 circuitry. When TP4 is HI, the 3/4 circuit divides by 4. The 12/23 divide number is changed through pin 12 of U7 and pin 6 and 9 of U8 by data from the control section decoder formed by U12. This decoder decodes information from pin 2 and 14 of U20. Signals from gate U4D and pins 2, 3, 14, and 15 of U11 control U7 and U8, the outputs of which are decoded by U6.

#### ECL to TTL Translator and Squaring Gates

Q3 and Q4 are buffers which convert the ECL output of U12A to TTL levls. The actual output of the divider passes through gates U4A, U4B, and U4C, which square up the output and change the 15% to 20% duty-cycle of the divider output signal to 50%.

#### TROUBLESHOOTING

When a Low Frequency N Loop problem has been traced through the block diagram troubleshooting procedure to this assembly, use the following procedure to isolate the cause of the problem.

#### Procedure

1. Mount the A3A3 assembly on an extender board from the service kit. Use an extender cable in place of the short cable running to this assembly. Look at TP15 with an oscilloscope. The signal should be a 10.0 MHz TTL signal (high 80 ns, low 20 ns). Check that the signal at U4C pin 14 is a 10.0 MHz ECL signal.

If the pulses are there and assume valid logic levels (even though the frequency may be wrong), continue with step 2, below. If there are no pulses (either point stuck high or low, or

doesn't assume valid logic levels), trace the signal back to find where the signal goes bad.

- 2. Set the front panel frequency to 323.3450 MHz. Connect a cable from A5A5J2 (disconnect the cable that is normally connected there) to A3A3J1. This connects the stable output of the fractional N loop to the input of the divider. Measure the frequency of the signal at TP15. The frequency should be 10.0 MHz (±1 count). If the frequency is correct, the divider is functioning normally so continue with step 6, below. Otherwise, there is a problem with the divider so continue troubleshooting with step 3.

- 3. Set the front panel frequency to 327.80 MHz. The frequency at TP15 should be 10.0 MHz. This frequency setting programs a divide number of 20.0 and input frequency (from fractional N loop) of 200.0 MHz. If the frequency at TP15 is correct, the problem is with the accumulator circuitry (U13, U19, U18 or U16). Otherwise, the problem is in the basic divider circuitry so continue troubleshooting with step 4.

- 4. Remove jumper W1 (to the left of U2). The frequency at TP5 should be 66.66667 MHz. The 34 counter is held in the divide-by-3 mode with the jumper removed.

Connect a jumper from +5V to the top pad where the jumper was connected. The frequency at TP5 should be 50.0 MHz. The 3/4 counter is held in the divide-by-4 mode with +5V applied.